## **Microphone Pre-Amplifer with Digital Output**

#### Description

The AAP149B is a chip-scale device with digital output developed specifically for integrating in small form factor two terminal electret condenser microphones.

The AAP149B provides PDM bit stream output and can run with a clock frequency of 1MHz to 3MHz and it has incorporated of 4<sup>th</sup> order Sigma-Delta ADC. The ADC has a 20kHz signal bandwidth. The single bit modulator features an inherently linear output, as well as enabling noise shaping and shifting of quantization noise.

The AAP149B provides ultra-low input capacitance and noise performance,  $5\mu$ Vrms typical with shorted input to ground, and it also provides excellent RFI and EMI immunity.

The AAP149B has 20dB gain and low quiescent current in sleep mode. Sleep mode is automatically detected by the clock frequency falling below 100kHz.

Additionally, the AAP149B is configured to be compatible with stereo audio applications, with provision of a Left and Right channel select.

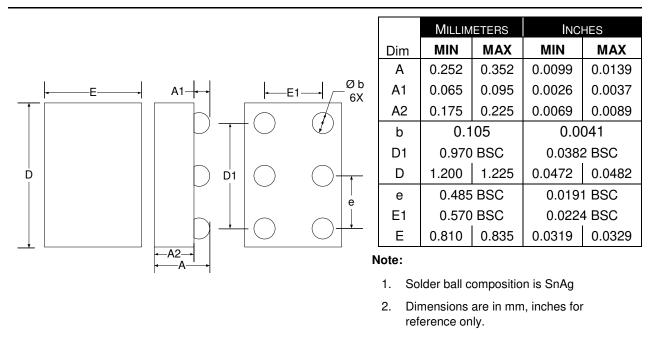

The AAP149B is provided in a chip scale 6pin SMD package. The package size is  $810\mu m \times 1200\mu m$ ; with an overall height of  $350\mu m$  including solder bumps. This extremely small package size and aspect ratio is optimum for use in small diameter microphones.

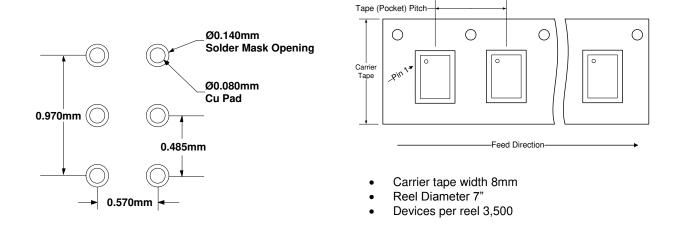

Available in tape & reel package.

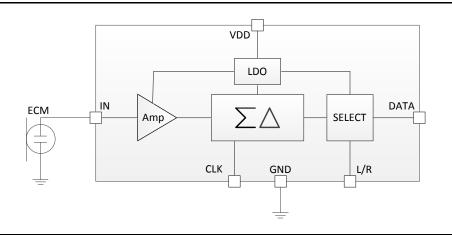

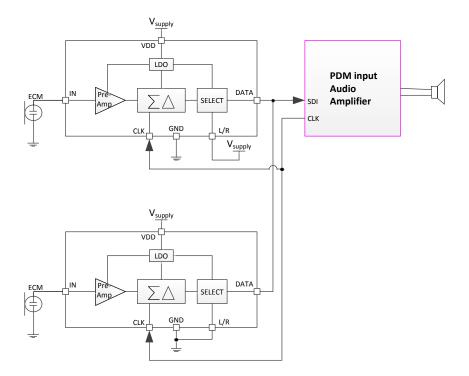

### Functional Block Diagram

#### Features

- Integrated 4<sup>th</sup> Order Sigma-Delta ADC, with 20kHz signal BW, PDM output and clock

- Frequency of 1MHz to 3MHz

- 20dB Gain

- Sleep Mode with low Quiescent Current < 40µA</li>

- Low Input Capacitance 0.2pF typical

- Low Noise 5µV RMS typical Input Noise (Aweighted, input shorted)

- Stereo-Audio Compatible with L/R Channel Select

- RoHS Compliant & Halogen Free

#### **Applications**

Small Diameter Electret Microphones with digital output

Figure 1 · Functional Block Diagram

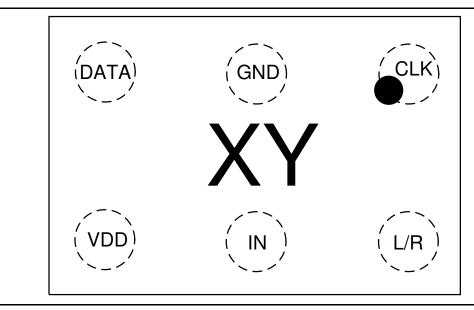

# **Pin Configuration**

Figure 2 · Pinout (Top View)

• Top mark XY and pin 1 indicator (Laser mark) XY= Unique lot code assigned for each assembly order

# Ordering Information

| Ambient<br>Temperature | Туре                                        | Package | Part Number          | Packaging<br>Type | Packing<br>Qty |

|------------------------|---------------------------------------------|---------|----------------------|-------------------|----------------|

| -40°C to 85°C          | RoHS2 compliant,<br>Pb-free<br>Halogen Free | CSP     | AAP149BS-M6B-G-LF-TR | Tape and Reel     | 3500           |

# **Pin Description**

| Pin Designator | Description                                                                        |  |  |

|----------------|------------------------------------------------------------------------------------|--|--|

| CLK            | ADC Clock input of 1MHz to 3MHz                                                    |  |  |

| GND            | Ground                                                                             |  |  |

| DATA           | Data Output pin, selectable by L/R                                                 |  |  |

| VDD            | Power input, 1.6V to 3.6V                                                          |  |  |

| IN             | Analog signal input for Electret Condenser Microphone                              |  |  |

| L/R            | Left or Right Channel Select. L/R sets low for Left channel, VDD for Right channel |  |  |

# Absolute Maximum Ratings

| Parameter                                                            | Min  | Max | Units |

|----------------------------------------------------------------------|------|-----|-------|

| Power Supply (VDD)                                                   | -0.5 | 5   | V     |

| Analog Input (IN)                                                    | -0.5 | 0.5 | V     |

| Voltage on CLK ( without loading clock)                              |      | 5   | V     |

| Voltage on L/R                                                       |      | 5   | V     |

| Maximum Operating Ambient Temperature                                | -40  | 85  | °C    |

| Maximum storage temperature                                          | -65  | 100 | °C    |

| Peak package solder reflow temperature (40 seconds maximum exposure) |      | 260 | °C    |

Note: Exceeding any Absolute Maximum ratings could cause damage to the device. All voltages are with respect to GND. Currents are positive into, negative out of specified terminal. These are stress ratings only and functional operation of the device at these, or any other conditions beyond those indicated under "Recommended Operating Conditions" are not implied. Exposure to "Absolute Maximum Ratings" for extended periods may affect device reliability.

# **Typical Operating Conditions**

| Parameter                   | Symbol         | Min. | Тур. | Max. | Unit |

|-----------------------------|----------------|------|------|------|------|

| Supply Voltage Range        | VDD            | 1.6  | 3.3  | 3.6  | V    |

| Operating Temperature Range | T <sub>A</sub> | -4   |      | 45   | °C   |

| Clock Rise and Fall Time    |                |      |      | 10   | ns   |

## **Electrical Characteristics**

Note: Unless otherwise specified, all limits are guaranteed for  $T_A$  = 25°C, VDD= 3.3V,  $V_{IN}$  = -44dBV\_{RMS,}  $f_{CLK}$ =2.4MHz, 50% duty,  $C_{MIC}$ =5pF

| Parameter                                    | Test Conditions                                                   | Min      | Тур  | Max      | Units         |

|----------------------------------------------|-------------------------------------------------------------------|----------|------|----------|---------------|

| POWER SUPPLY                                 | 1                                                                 |          |      |          |               |

| Supply Voltage (VDD)                         |                                                                   | 1.6      | 3.3  | 3.6      | V             |

| Supply Current                               | IN=GND, CLK=2.4MHz, No Load                                       |          |      |          |               |

| Normal Mode (I <sub>DD</sub> )               | VDD=1.8V                                                          |          | 510  |          | μΑ            |

|                                              | VDD=3.3V                                                          |          | 600  |          | μΑ            |

| Sleep Mode ( $I_{SB}$ )                      | VDD=1.8V, f <sub>CLK</sub> =GND                                   |          | 8.2  | 40       | μΑ            |

|                                              | VDD=3.3V, f <sub>CLK</sub> =GND                                   |          | 15.5 | 40       | μΑ            |

| PERFORMANCE                                  |                                                                   |          |      |          |               |

| Transfer Function (TF)                       |                                                                   |          | 20   |          | dBV/dBFS      |

| Nominal Sensitivity                          | IN=1kHz, -44dBV                                                   |          | -24  |          | dBFS          |

| Signal-to-Noise Ratio (SNR)                  | IN=1kHz, -44dBV, A-weighted                                       |          | 60   |          | dB(A)         |

| Input Referred Noise (EIN)                   | 20Hz to 20kHz, A-weighted,                                        |          | 5    |          | $\mu V_{RMS}$ |

| Dynamic Range                                | Derived from EIN and max<br>acoustic input                        |          | 90   |          | dB            |

| Band Width                                   |                                                                   | 25       |      | 20000    | Hz            |

| Frequency Response                           | Low Frequency -3dB point                                          |          | 33   |          | Hz            |

|                                              | High Frequency -3dB point                                         | 20       |      |          | kHz           |

| THD & Noise ( THD+N)                         |                                                                   |          | 0.21 |          | %             |

| Overload Margin                              | @1% THD+N                                                         |          | 81   |          | mVpk          |

|                                              | @5% THD+N                                                         |          | 91   |          | mVpk          |

| Input Capacitance (CIN)                      |                                                                   |          | 0.2  |          | pF            |

| Input Resistance ( RIN)                      |                                                                   | >20      |      |          | GΩ            |

| Maximum Acoustic Input                       |                                                                   |          | 120  |          | dBSPL         |

| Power Supply Rejection Ratio (PSRR)          | IN=GND, 217Hz, 100mVpp<br>square wave superimposed on<br>VDD=1.8V |          | -70  |          | dBFS          |

| DIGITAL INPUT/OUTPUT CHA                     | RACTERISTICS                                                      |          |      |          |               |

| Input Voltage High (VIH)                     | I <sub>OUT</sub> =1.8mA                                           | 0.65*VDD |      | VDD+0.3  | V             |

| Input Voltage Low $(V_{IL})$                 | I <sub>OUT</sub> =1.8mA                                           | -0.3     |      | 0.35*VDD | V             |

| Output Voltage High (V <sub>OH</sub> )       | I <sub>OUT</sub> =1.8mA                                           | 0.65*VDD |      | VDD+0.3  | V             |

| Output Voltage Low (V <sub>OL</sub> )        | I <sub>OUT</sub> =1.8mA                                           | -0.3     |      | 0.35*VDD | V             |

| Noise Floor                                  | 20Hz to 20kHz, A-weighted                                         |          | -83  |          | dBFS          |

| TIMING CHARACTERISTICS                       |                                                                   |          |      |          |               |

| Start-Up Period (Note1)                      |                                                                   |          |      | 5        | ms            |

| Sleep time (t <sub>SL</sub> ) $^{(Note 3)}$  | Time from CLK Falling < 100kHz                                    |          |      | 10       | ms            |

| Wake-Up time( $t_{WU}$ ) <sup>(Note 2)</sup> | Time from CLK Rising > 100kHz,<br>Power On                        |          |      | 10       | ms            |

| Clock Frequency ( f <sub>CLK</sub> )         |                                                                   | 1        | 2.4  | 3        | MHz           |

| Clock Duty Ratio                             |                                                                   | 40       | 50   | 60       | %             |

| Parameter                                                          | Test Conditions                             | Min | Тур | Max | Units |

|--------------------------------------------------------------------|---------------------------------------------|-----|-----|-----|-------|

| Clock Rise/Fall time (t <sub>CF</sub> , t <sub>CR</sub> )          | $R_L=1M\Omega \& C_L=15pF$                  |     |     | 10  | ns    |

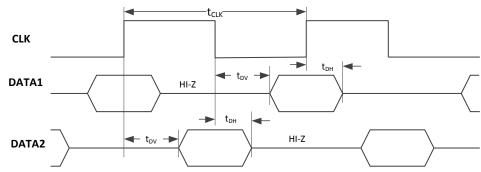

| Time from CLK transition to data becoming valid (T <sub>DV</sub> ) | On falling edge of CLK,<br>L/R=GND, CL=15pF |     | 20  |     | ns    |

| Time from CLK transition to data becoming Hi-Z (T <sub>DH</sub> )  | On Rising edge of CLK,<br>L/R=GND, CL=15pF  |     | 15  |     | ns    |

| Time from CLK transition to data becoming valid (T <sub>DV</sub> ) | On Rising edge of CLK,<br>L/R=VDD, CL=15pF  |     | 26  |     | ns    |

| Time from CLK transition to data becoming Hi-Z (T <sub>DH</sub> )  | On falling edge of CLK,<br>L/R=VDD, CL=15pF |     | 14  |     | ns    |

| Load capacitance on Data $(C_L)$                                   |                                             |     |     | 100 | pF    |

#### Notes:

- (1) Start-up period is measured when VDD becomes 3.3V to the time when transfer function settles within 1dB of its final value. After start-up period, the device can handle equivalent of 1Pa with THD <10%.

- (2) The wake-up period is measured when the clock frequency is higher than 100kHz and the transfer function is settles within 1dB of its final value.

- (3) Fall-sleep period is measured when the clock frequency falls below 100kHz and current drops to the standby current I<sub>SB</sub>.

- (4) The stand-by mode is entered when the clock frequency is below the specified clock frequency.

#### **TIMING DIAGRAM**

Timing diagram of CLK and DATA terminals

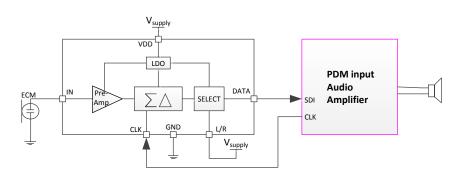

### **Applications Information**

VDD is required to decouple using 0.1µF ceramic capacitor. It should be placed very close to the VDD pin and GND. Due to very high input impedance, careful consideration should be taken to remove all flux used during the reflow soldering process.

A  $100\Omega$  resistance is recommended on the clock output of the device driving AAP149B to minimize ringing and improve signal integrity.

For optimal PSRR, route a trace to the VDD pin. DO not place a VDD plane under the device.

Mono Microphone Application Circuit

Stereo Microphone Application Circuit

### Package Outline Dimensions

The package is halogen free and meets RoHS2 and REACH standards.

Figure 3 · 6 Bump X2CSP Micro SMD Package Dimensions

Figure 4  $\cdot$  PCB Layout Footprint / Tape and Reel Information

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA

Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

E-mail: sales.support@microsemi.com

© 2015 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,400 employees globally. Learn more at **www.microsemi.com**.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.