SLAS837B - APRIL 2013 - REVISED JANUARY 2017

**DAC3174**

# DAC3174 Dual, 14-Bit, 500-MSPS, Digital-to-Analog Converter

#### **Features**

- **Dual-Channel**

- 14-Bit Resolution

- Maximum Sample Rate: 500 MSPS

- Pin Compatible With Dual-Channel DAC3154, DAC3164, and Single-Channel DAC3151, DAC3161, and DAC3171

- Input Interface:

- 14 LVDS Inputs

- Single, 14-Bit Interface or Dual, 7-Bit Interface

- Single or Dual DDR Data Clock

- Internal FIFO

- Chip-to-Chip Synchronization

- Power Dissipation: 460 mW

- Spectral Performance at 20 MHz IF:

SNR: 76 dBFS - SFDR: 78 dBc

**Current-Sourcing DACs**

Compliance Range: -0.5 V to +1 V

Package: 64-Pin VQFN (9 mm × 9 mm)

# **Applications**

- Multi-Carrier, Multi-Mode Cellular Infrastructure **Base Stations**

- Radar

- Signal Intelligence

- Software-Defined Radios

- Test and Measurement Instrumentation

# 3 Description

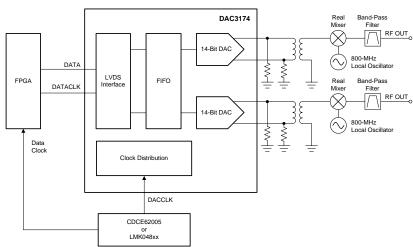

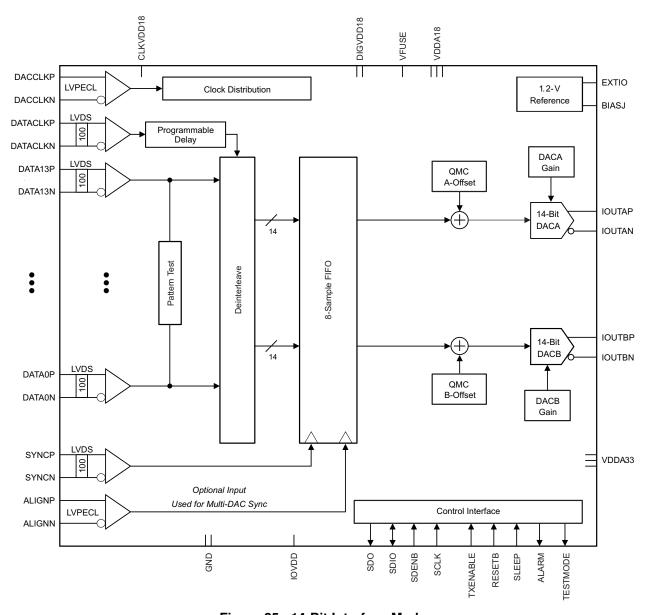

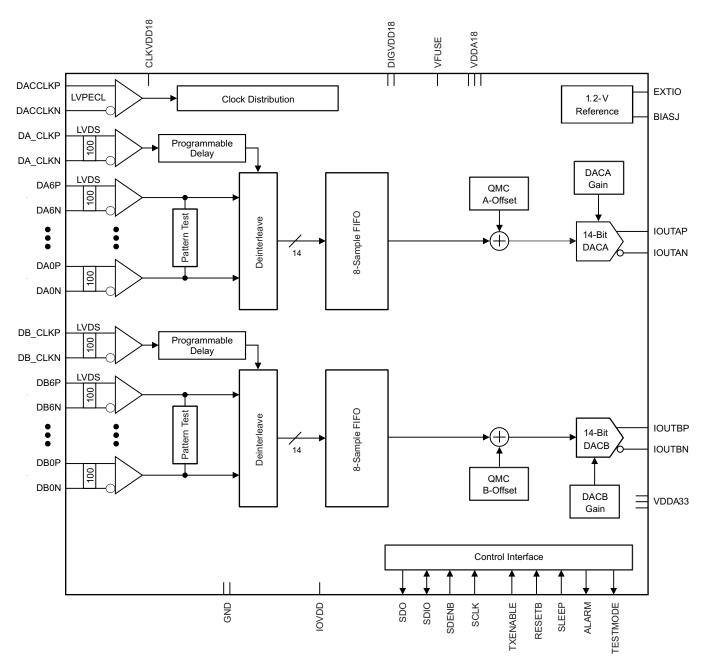

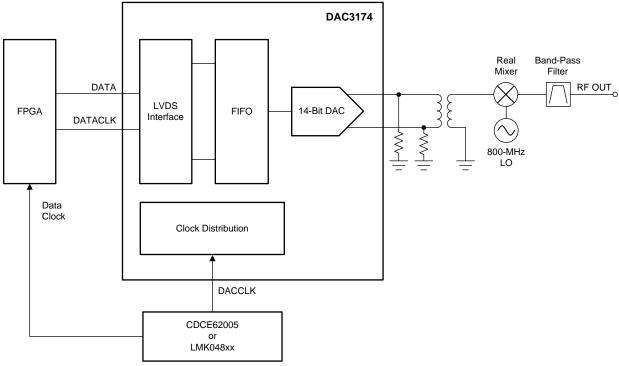

The DAC3174 is a dual-channel, 14-bit, 500-MSPS, digital-to-analog converter (DAC). The DAC3174 uses a 14-bit, low-voltage differential signaling (LVDS) digital bus, with one or two independent dualdata rate (DDR) data clocks for flexibility in providing data from different sources in each channel.

An input first-in first out block (FIFO) allows independent data and sample clocks. FIFO input and output pointers can be synchronized across multiple devices for precise signal synchronization.

The DAC outputs are current sourcing and terminate to GND with a compliance range of -0.5 V to +1 V.

The DAC3174 is pin compatible with the dualchannel, 500-MSPS, 12-bit DAC3164 and 10-bit DAC3154, and the single-channel, 500-MSPS, 14-bit DAC3171, 12-bit DAC3161, and 10-bit DAC3151.

device is available in a 64-pin VQFN PowerPAD™ package. and is specified over the full industrial temperature range of -40°C to +85°C.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| DAC3174     | VQFN (64) | 9.00 mm × 9.00 mm |

(1) For all available packages, see the package option addendum at the end of the data sheet.

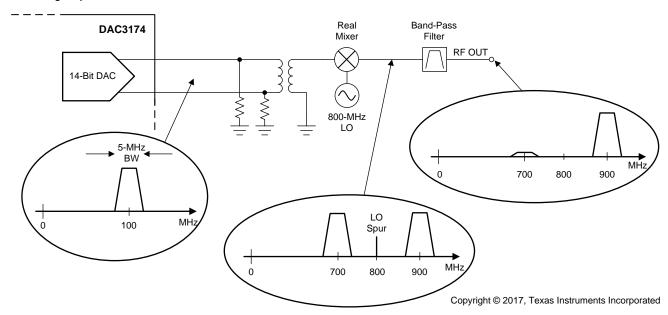

#### **Typical Application**

Copyright @ 2017, Texas Instruments Incorporated

| <b>T</b> - | <b>I</b> - I |   | - 6        | <b>^</b> -   | nte  |       |

|------------|--------------|---|------------|--------------|------|-------|

| 12         | n            | Ω | $\Delta T$ | 1 · O        | nto  | nte   |

| ı a        | _            | ı | VI.        | $\mathbf{v}$ | HILL | 111.0 |

| 1 | Features 1                                                |    | 7.4 Device Functional Modes                          | 21 |

|---|-----------------------------------------------------------|----|------------------------------------------------------|----|

| 2 | Applications                                              |    | 7.5 Programming                                      |    |

| 3 | Description 1                                             |    | 7.6 Register Maps                                    |    |

| 4 | Revision History2                                         | 8  | Application and Implementation                       | 42 |

| 5 | Pin Configuration and Functions                           |    | 8.1 Application Information                          | 42 |

| 6 | Specifications                                            |    | 8.2 Typical Application                              | 42 |

| U | 6.1 Absolute Maximum Ratings                              | 9  | Power Supply Recommendations                         | 44 |

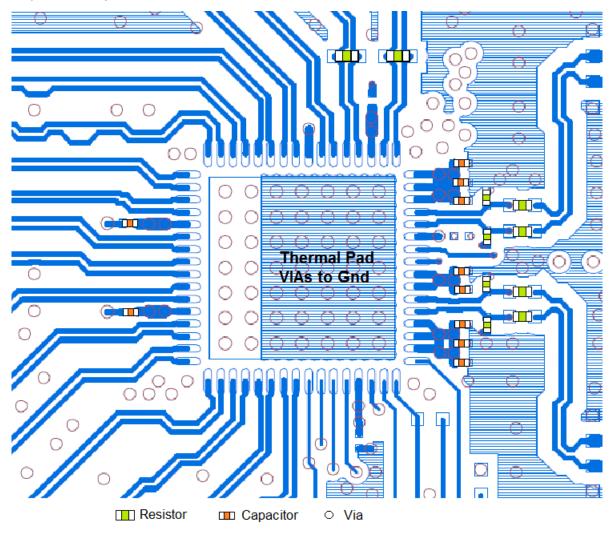

|   | 6.2 ESD Ratings                                           | 10 | Layout                                               | 45 |

|   | 6.3 Recommended Operating Conditions                      |    | 10.1 Layout Guidelines                               | 45 |

|   | 6.4 Thermal Information                                   |    | 10.2 Layout Example                                  | 45 |

|   | 6.5 Electrical Characteristics: DC Specifications 8       | 11 | Device and Documentation Support                     | 46 |

|   | 6.6 Electrical Characteristics: AC Specifications 10      |    | 11.1 Device Support                                  | 46 |

|   | 6.7 Electrical Characteristics: Digital Specifications 10 |    | 11.2 Receiving Notification of Documentation Updates | 46 |

|   | 6.8 Timing Requirements11                                 |    | 11.3 Community Resources                             | 46 |

|   | 6.9 Typical Characteristics                               |    | 11.4 Trademarks                                      | 47 |

| 7 | Detailed Description 18                                   |    | 11.5 Electrostatic Discharge Caution                 | 47 |

|   | 7.1 Overview                                              |    | 11.6 Glossary                                        | 47 |

|   | 7.2 Functional Block Diagrams                             | 12 | Mechanical, Packaging, and Orderable                 |    |

|   | 7.3 Feature Description                                   |    | Information                                          | 47 |

|   | ·                                                         |    |                                                      |    |

# 4 Revision History

| Changes from Revision A (May 2013) to Revision B |

|--------------------------------------------------|

|--------------------------------------------------|

Page

| • | Added Device Information, ESD Ratings, Recommended Operating Conditions, and Timing Requirements tables, and Detailed Description, Application and Implementation, Power Supply Recommendations, Layout, Device and Documentation Support, and Mechanical, Packaging, and Orderable Information sections | 1  |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| • | Added typical application diagram to front page and moved existing block diagrams to <i>Functional Block Diagrams</i> section                                                                                                                                                                            | 1  |

| • | Added GND PAD row to Pin Functions table                                                                                                                                                                                                                                                                 | 4  |

| • | Added GND PAD row to Pin Functions table                                                                                                                                                                                                                                                                 | 6  |

| • | Changed both functional block diagrams for clarity                                                                                                                                                                                                                                                       | 18 |

| • | Added definition for T = DACCLK period                                                                                                                                                                                                                                                                   | 20 |

| • | Added definition for T = DACCLK period                                                                                                                                                                                                                                                                   | 23 |

| • | Changed text in FUSE controlled bullet of Register Maps section for clarity                                                                                                                                                                                                                              | 26 |

### Changes from Original (April 2013) to Revision A

Page

Submit Documentation Feedback

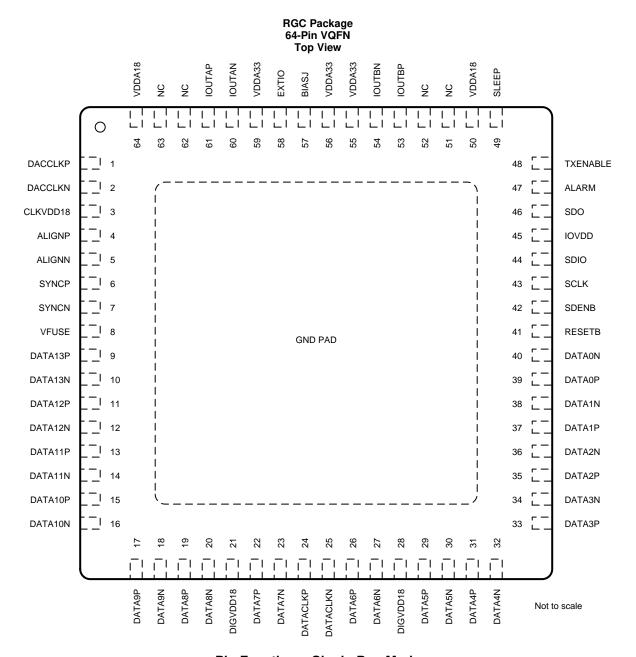

# 5 Pin Configuration and Functions

Pin Functions: Single-Bus Mode

| PIN NAME NO. |        |     |                                                                                                                                                                                                                                                   |

|--------------|--------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |        | I/O | DESCRIPTION                                                                                                                                                                                                                                       |

| CONTROL AND  | SERIAL |     |                                                                                                                                                                                                                                                   |

| ALARM        | 47     | 0   | CMOS output for ALARM condition.                                                                                                                                                                                                                  |

| RESETB       | 41     | ı   | Serial interface reset input, active low. Initialized internal registers during high-to-low transition. Asynchronous. Internal pullup. A reset event after every power cycle may be required to reinitialize all SPI registers to default values. |

| SCLK         | 43     | 1   | Serial interface clock. Internal pulldown.                                                                                                                                                                                                        |

| SDENB        | 42     | 1   | Serial data enable. Internal pullup.                                                                                                                                                                                                              |

| SDIO         | 44     | I/O | Bidirectional serial data in 3-pin mode (default). In 4-pin interface mode (sif4_ena [config0, bit 9]), the SDIO pin in an input only. Internal pulldown.                                                                                         |

# Pin Functions: Single-Bus Mode (continued)

| PIN PIN         |                                                                    |     |                                                                                                                                                                                                                                                                                                                                       |  |  |

|-----------------|--------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME            | NO.                                                                | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                           |  |  |

| SDO             | 46                                                                 | 0   | Unidirectional serial interface data in 4-pin mode (sif4_ena [config0, bit 9]). The SDO pin is made high impedance in 3-pin interface mode (default). Internal pulldown.                                                                                                                                                              |  |  |

| SLEEP           | 49                                                                 | - 1 | Puts device in sleep, active high. Internal pulldown.                                                                                                                                                                                                                                                                                 |  |  |

| TXENABLE        | 48                                                                 | I   | Transmit enable, active high input. TXENABLE must be high for the data to the DAC to be enabled. When TXENABLE is low, the digital logic section is forced to all 0, and any input data are ignored. Internal pulldown.                                                                                                               |  |  |

| DATA INTERFAC   | Ē                                                                  |     |                                                                                                                                                                                                                                                                                                                                       |  |  |

| ALIGNN          | 5                                                                  | ı   | LVPECL FIFO output synchronization. This positive or negative pair is captured with the rising                                                                                                                                                                                                                                        |  |  |

| ALIGNP          | 4                                                                  |     | edge of DACCLKx. This pin is used to reset the clock dividers and for multiple DAC synchronization. If unused, this pin can be left unconnected.                                                                                                                                                                                      |  |  |

| DATA[13:0]N     | 10, 12, 14,<br>16, 18, 20,<br>23, 27, 30,<br>32, 34, 36,<br>38, 40 | ı   | LVDS input data bits for both channels. Each positive and negative LVDS pair has an internal 100-Ω termination resistor. Data format relative to DATACLKx clock is dual data rate (DDR) with two data transfers per DATACLKx clock cycles.  The data format is interleaved with channel A (rising edge) and channel B (falling edge). |  |  |

|                 | 9, 11, 13,                                                         |     | In the default mode (reverse bus not enabled):                                                                                                                                                                                                                                                                                        |  |  |

| D.4.T.4.4.0.03D | 15, 17, 19,                                                        |     | DATA13x is most significant data bit (MSB)                                                                                                                                                                                                                                                                                            |  |  |

| DATA[13:0]P     | 22, 26, 29,<br>31, 33, 35,<br>37, 39                               | I   | DATA0x is least significant data bit (LSB)                                                                                                                                                                                                                                                                                            |  |  |

| DATACLKN        | 25                                                                 | 1   | DDR differential input data clock. Edge to center nominal timing. Ch A rising edge, Ch B falling                                                                                                                                                                                                                                      |  |  |

| DATACLKP        | 24                                                                 | -   | edge in multiplexed output mode.                                                                                                                                                                                                                                                                                                      |  |  |

| SYNCN           | 7                                                                  | -   | This pin resets the FIFO or is used as a syncing source. These two functions are captured with                                                                                                                                                                                                                                        |  |  |

| SYNCP           | 6                                                                  | I   | the rising edge of DATACLKx. The signal captured by the falling edge of DATACLKx.                                                                                                                                                                                                                                                     |  |  |

| OUTPUT AND CL   | оск                                                                |     |                                                                                                                                                                                                                                                                                                                                       |  |  |

| DACCLKN         | 2                                                                  | - 1 | LVPECL clock input for DAC core with a self-bias of approximately CLKVDD18 / 2.                                                                                                                                                                                                                                                       |  |  |

| DACCLKP         | 1                                                                  | -   | EVI EGE GIOCK INPUT OF BACO COTO WILL A SOIL DIAG OF APPROXIMATORY GERVED TO 7 2.                                                                                                                                                                                                                                                     |  |  |

| IOUTAN          | 60                                                                 | 0   | A-Channel DAC current output. An offset binary data pattern of 0x0000 at the DAC input results                                                                                                                                                                                                                                        |  |  |

| IOUTAP          | 61                                                                 | 0   | in a full-scale current source, and the most positive voltage on the IOUTAP pin. Similarly, a 0xFFFF data input results in a 0-mA current source, and the least positive voltage on the IOUTAP pin. The IOUTAN pin is the complement of IOUTAP.                                                                                       |  |  |

| IOUTBN          | 54                                                                 | 0   | B-Channel DAC current output. An offset binary data pattern of 0x0000 at the DAC input results in a full-scale current source, and the most positive voltage on the IOUTBP pin. Similarly, a                                                                                                                                          |  |  |

| IOUTBP          | 53                                                                 | 0   | 0xFFFF data input results in a 0-mA current source, and the least positive voltage on the IOUTBP pin. The IOUTBN pin is the complement of IOUTBP.                                                                                                                                                                                     |  |  |

| REFERENCE       |                                                                    |     |                                                                                                                                                                                                                                                                                                                                       |  |  |

| BIASJ           | 57                                                                 | 0   | Full-scale output current bias. For 20-mA full-scale output current, connect a 960- $\Omega$ resistor to GND.                                                                                                                                                                                                                         |  |  |

| EXTIO           | 58                                                                 | I/O | Used as external reference input when internal reference is disabled. Requires a 0.1-µF decoupling capacitor to GND when used as reference output.                                                                                                                                                                                    |  |  |

| POWER SUPPLY    |                                                                    |     |                                                                                                                                                                                                                                                                                                                                       |  |  |

| CLKVDD18        | 3                                                                  | I   | 1.8-V clock supply.                                                                                                                                                                                                                                                                                                                   |  |  |

| DIGVDD18        | 21, 28                                                             | 1   | 1.8-V digital supply. Also supplies LVDS receivers.                                                                                                                                                                                                                                                                                   |  |  |

| IOVDD           | 45                                                                 | - 1 | Supply voltage for CMOS I/Os. 1.8 V to 3.3 V.                                                                                                                                                                                                                                                                                         |  |  |

| VDDA18          | 50, 64                                                             | ı   | Analog 1.8-V supply.                                                                                                                                                                                                                                                                                                                  |  |  |

| VDDA33          | 55, 56, 59                                                         | ı   | Analog 3.3-V supply.                                                                                                                                                                                                                                                                                                                  |  |  |

| VFUSE           | 8                                                                  | 1   | Digital supply voltage (1.8 V). This supply pin is also used for factory fuse programming. Connect to DVDD pins for normal operation.                                                                                                                                                                                                 |  |  |

| NC              | 51, 52,<br>62, 63                                                  | _   | Not used. These pins can be left open or tied to ground in actual application use.                                                                                                                                                                                                                                                    |  |  |

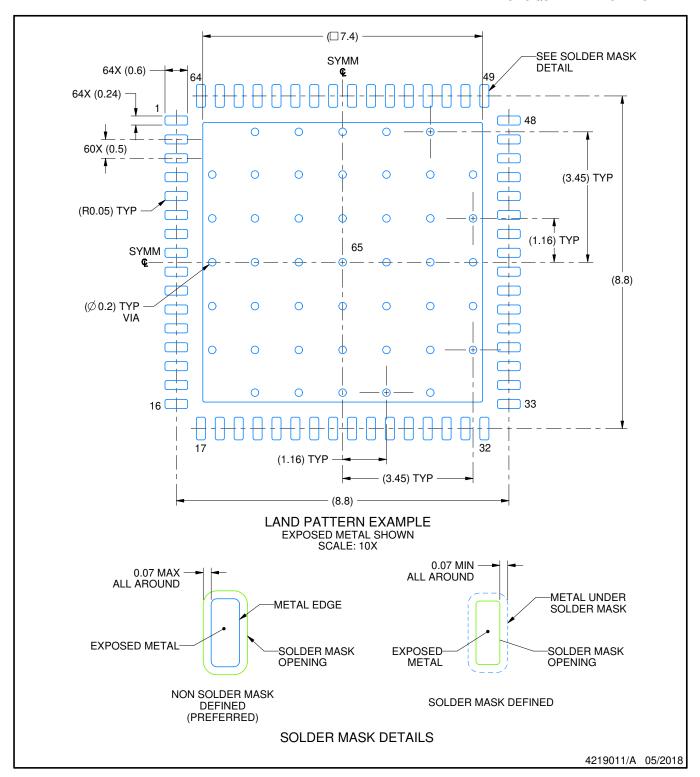

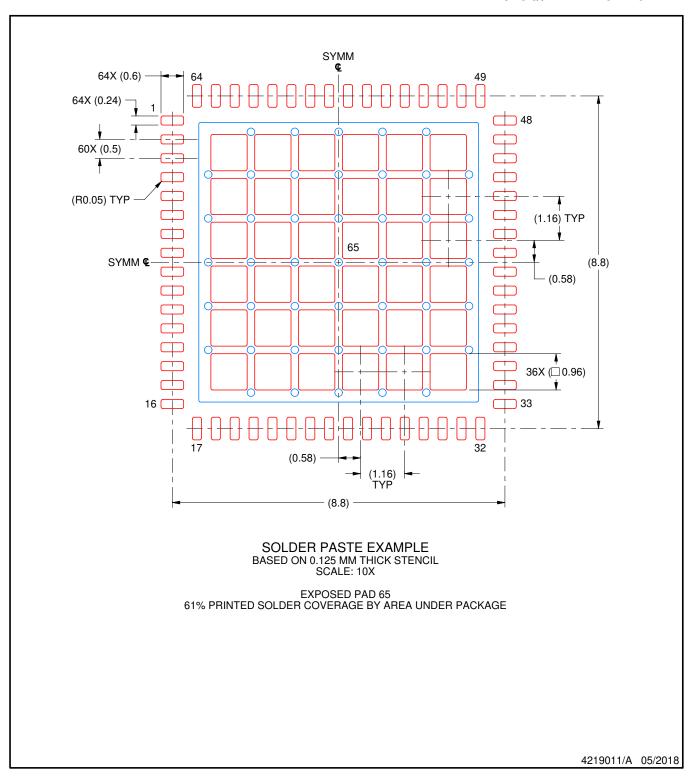

| GND PAD         | _                                                                  | _   | This thermal pad is the electrical ground connection for the device (backside).                                                                                                                                                                                                                                                       |  |  |

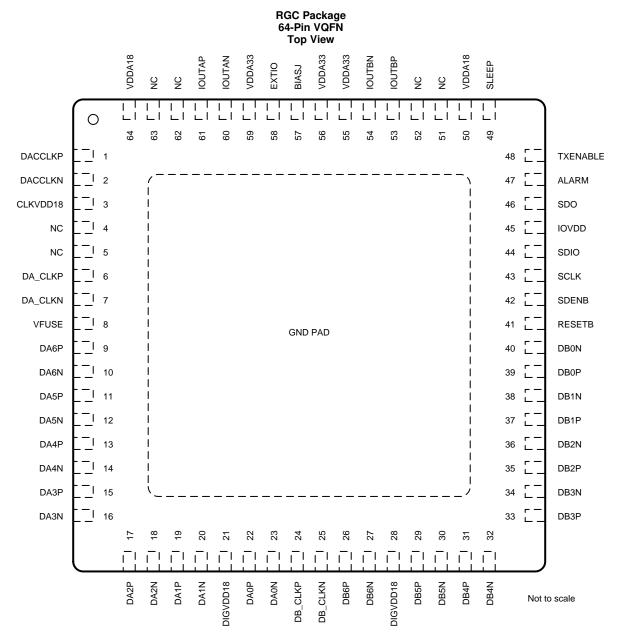

Pin Functions: Dual-Bus Mode

| PIN NAME NO. |        | 1/0 | DESCRIPTION                                                                                                                                                                                                                                       |

|--------------|--------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |        | I/O | DESCRIPTION                                                                                                                                                                                                                                       |

| CONTROL AND  | SERIAL |     |                                                                                                                                                                                                                                                   |

| ALARM        | 47     | 0   | CMOS output for alarm condition.                                                                                                                                                                                                                  |

| RESETB       | 41     | I   | Serial interface reset input, active low. Initializes internal registers during high to low transition. Asynchronous. Internal pullup. A reset event after every power cycle may be required to reinitialize all SPI registers to default values. |

| SCLK         | 43     | - 1 | Serial interface clock. Internal pulldown.                                                                                                                                                                                                        |

| SDENB        | 42     | - 1 | Serial data enable. Internal pullup.                                                                                                                                                                                                              |

| SDIO         | 44     | I/O | Bidirectional serial data in 3-pin mode (default). In 4-pin interface mode (sif4_ena [config0, bit 9]), the SDIO pin in an input only. Internal pulldown.                                                                                         |

# Pin Functions: Dual-Bus Mode (continued)

| PIN            | PIN                              |     |                                                                                                                                                                                                                                                 |  |  |

|----------------|----------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME           | NO.                              | I/O | DESCRIPTION                                                                                                                                                                                                                                     |  |  |

| SDO            | 46                               | 0   | Unidirectional serial interface data in 4-pin mode (sif4_ena [config0, bit 9]). The SDO pin is made high impedance in 3-pin interface mode (default). Internal pulldown.                                                                        |  |  |

| SLEEP          | 49                               | - 1 | Puts device in sleep, active high. Internal pulldown.                                                                                                                                                                                           |  |  |

| TXENABLE       | 48                               | 1   | Transmit enable, active high input. TXENABLE must be high for the data to the DAC to be enabled. When TXENABLE is low, the digital logic section is forced to all 0, and any input data are ignored. Internal pulldown.                         |  |  |

| DATA INTERFACE | E                                |     |                                                                                                                                                                                                                                                 |  |  |

| DA[6:0]N       | 10, 12, 14,<br>16, 18            | I   | LVDS positive input data bits for channel A. Each positive or negative LVDS pair has an internal 100-Ω termination resistor. Data format relative to DA_CLKx clock is dual data rate (DDR) with two data transfers per DA_CLKx clock cycle.     |  |  |

| DA[6:0]P       | 9, 11, 13,<br>15, 17, 19         | I   | The data format is 7 MSBs (rising edge) and 7 LSBs (falling edge).  In the default mode (reverse bus not enabled):  DA6x is most significant data bit (MSB)  DA0x is least significant data bit (LSB)                                           |  |  |

| DB[6:0]N       | 27, 30, 32,<br>34, 36, 38,<br>40 | Ι   | LVDS positive input data bits for channel B. Each positive or negative LVDS pair has an internal 100-Ω termination resistor. Data format relative to DB_CLKx clock is dual data rate (DDR) with two data transfers per DB_CLKx clock cycle.     |  |  |

| DB[6:0]P       | 26, 29, 31,<br>33, 35, 37,<br>39 | I   | The data format is 7 MSBs (rising edge) and 7 LSBs (falling edge). In the default mode (reverse bus not enabled): DB6x is most significant data bit (MSB) DB0x is least significant data bit (LSB)                                              |  |  |

| DA_CLKN        | 7                                | _   | DDR differential input data clock for channel A. Edge to center perminal timing                                                                                                                                                                 |  |  |

| DA_CLKP        | 6                                | _   | DDR differential input data clock for channel A. Edge to center nominal timing.                                                                                                                                                                 |  |  |

| DB_CLKN        | 25                               | _   | DDB differential input data clock for channel B. Edge to center naminal timing                                                                                                                                                                  |  |  |

| DB_CLKP        | 24                               | _   | DDR differential input data clock for channel B. Edge to center nominal timing.                                                                                                                                                                 |  |  |

| OUTPUT AND CL  | ОСК                              |     |                                                                                                                                                                                                                                                 |  |  |

| DACCLKN        | 2                                | 1   | LVPECL clock negative input for DAC core with a self-bias of approximately CLKVDD18 / 2.                                                                                                                                                        |  |  |

| DACCLKP        | 1                                | - 1 | LVPECL clock positive input for DAC core with a self-bias of approximately CLKVDD18 / 2.                                                                                                                                                        |  |  |

| IOUTAN         | 60                               | 0   | A-Channel DAC current output. An offset binary data pattern of 0x0000 at the DAC input results                                                                                                                                                  |  |  |

| IOUTAP         | 61                               | 0   | in a full-scale current source, and the most positive voltage on the IOUTAP pin. Similarly, a 0xFFFF data input results in a 0-mA current source, and the least positive voltage on the IOUTAP pin. The IOUTAN pin is the complement of IOUTAP. |  |  |

| IOUTBN         | 54                               | 0   | B-Channel DAC current output. An offset binary data pattern of 0x0000 at the DAC input results                                                                                                                                                  |  |  |

| IOUTBP         | 53                               | 0   | in a full-scale current source, and the most positive voltage on the IOUTBP pin. Similarly, a 0xFFFF data input results in a 0-mA current source, and the least positive voltage on the IOUTBP pin. The IOUTBN pin is the complement of IOUTBP. |  |  |

| REFERENCE      | II.                              |     |                                                                                                                                                                                                                                                 |  |  |

| BIASJ          | 57                               | 0   | Full-scale output current bias. For 20-mA full-scale output current, connect a 960- $\Omega$ resistor to GND.                                                                                                                                   |  |  |

| EXTIO          | 58                               | I/O | Used as external reference input when internal reference is disabled. Requires a 0.1-μF decoupling capacitor to GND when used as reference output.                                                                                              |  |  |

| POWER SUPPLY   | ı                                |     |                                                                                                                                                                                                                                                 |  |  |

| CLKVDD18       | 3                                | ı   | 1.8-V clock supply.                                                                                                                                                                                                                             |  |  |

| DIGVDD18       | 21, 28                           | ı   | 1.8-V digital supply. Also supplies LVDS receivers.                                                                                                                                                                                             |  |  |

| IOVDD          | 45                               | ı   | Supply voltage for CMOS I/Os. 1.8 V to 3.3 V.                                                                                                                                                                                                   |  |  |

| VDDA18         | 50, 64                           | Ι   | Analog 1.8-V supply.                                                                                                                                                                                                                            |  |  |

| VDDA33         | 55, 56, 59                       | - 1 | Analog 3.3-V supply.                                                                                                                                                                                                                            |  |  |

| VFUSE          | 8                                | I   | Digital supply voltage (1.8 V). This supply pin is also used for factory fuse programming. Connect to DVDD pins for normal operation.                                                                                                           |  |  |

| NC             | 4, 5,<br>51, 52,<br>62, 63       | _   | Not used. In actual application, pins 51, 52, 62, and 63 can be left open or tied to ground. TI recommends tying pins 4 and 5 to DIGVDD18 and ground, respectively.                                                                             |  |  |

| GND PAD        | _                                | _   | This thermal pad is the electrical ground connection for the device (backside).                                                                                                                                                                 |  |  |

# 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                  |                                                                                                                                          | MIN  | MAX            | UNIT |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------|------|----------------|------|

|                  | VDDA33 to GND                                                                                                                            | -0.5 | 4              |      |

|                  | VDDA18 to GND                                                                                                                            | -0.5 | 2.3            |      |

| Supply voltage   | CLKVDD18 to GND                                                                                                                          | -0.5 | 2.3            | V    |

|                  | IOVDD to GND                                                                                                                             | -0.5 | 4              |      |

|                  | DIGVDD18 to GND                                                                                                                          | -0.5 | 2.3            |      |

|                  | CLKVDD18 to DIGVDD18                                                                                                                     | -0.5 | 0.5            |      |

| Terminal voltage | VDDA18 to DIGVDD18                                                                                                                       | -0.5 | 0.5            |      |

|                  | DA[6:0]P, DA[6:0]N, DB[6:0]P, DB[6:0]N, D[13:0]P, D[13:0]N, DATACLKP, DATACLKN, DA_CLKP, DA_CLKPN, DB_CLKP, DB_CLKN, SYNCP, SYNCN to GND | -0.5 | DIGVDD18 + 0.5 | V    |

| reminal voltage  | DACCLKP, DACCLKN, ALIGNP, ALIGNN                                                                                                         | -0.5 | CLKVDD18 + 0.5 | v    |

|                  | TXENABLE, ALARM, SDO, SDIO, SCLK, SDENB, RESETB to GND                                                                                   | -0.5 | IOVDD + 0.5    |      |

|                  | IOUTAP, IOUTAN, IOUTBP, IOUTBN to GND                                                                                                    | -0.7 | 1.4            |      |

|                  | EXTIO, BIASJ to GND                                                                                                                      | -0.5 | VDDA33 + 0.5   |      |

|                  | Operating ambient free-air, T <sub>A</sub>                                                                                               | -40  | 85             |      |

| Temperature      | Maximum junction, T <sub>J</sub>                                                                                                         |      | 125            | °C   |

|                  | Storage, T <sub>stg</sub>                                                                                                                | -65  | 150            |      |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                                            | -                                                                   |       | VALUE                                 | UNIT |

|--------------------------------------------|---------------------------------------------------------------------|-------|---------------------------------------|------|

| V <sub>(ESD)</sub> Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±2000 | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |      |

|                                            | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V                                     |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### 6.3 Recommended Operating Conditions

|                |                                               | MIN  | NOM | MAX  | UNIT |

|----------------|-----------------------------------------------|------|-----|------|------|

| CLKVDD18       | Clock buffer supply                           | 1.71 | 1.8 | 1.89 | V    |

| DIGVDD18       | Digital supply                                | 1.71 | 1.8 | 1.89 | V    |

| VDDA18         | 1.8-V analog supply                           | 1.71 | 1.8 | 1.89 | V    |

| VFUSE          | Fuse bank supply                              | 1.71 | 1.8 | 1.89 | V    |

| IOVDD          | IO supply <sup>(1)</sup>                      | 1.71 |     | 3.45 | V    |

| VDDA33         | 3.3-V analog supply                           | 3.15 | 3.3 | 3.45 | V    |

| T <sub>A</sub> | Operating ambient free-air temperature        | -40  | 25  | 85   | °C   |

| $T_{J}$        | Operating junction temperature <sup>(2)</sup> |      |     | 105  | °C   |

<sup>(1)</sup> Sets CMOS IO voltage levels; nominal 1.8 V, 2.5 V, or 3.3 V.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> Prolonged use at this junction temperature may increase the device failure-in-time (FIT) rate.

#### 6.4 Thermal Information

|                      |                                              | DAC3174    |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RGC (VQFN) | UNIT |

|                      |                                              | 64 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 23         | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 7.6        | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 2.8        | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.1        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 2.8        | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 0.2        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 6.5 Electrical Characteristics: DC Specifications

Typical values at  $T_A$  = 25°C, full temperature range is  $T_{MIN}$  = -40°C to  $T_{MAX}$  = 85°C, DAC sample rate = 500 MSPS, 50% clock duty cycle, VDDA33 = IOVDD = 3.3 V, VDDA18 = CLKVDD18 = DIGVDD18 = 1.8 V, and IOUT<sub>FS</sub> = 20 mA (unless otherwise noted).

|           | PARAMETER                         | TEST CONDITIONS                                                        | MIN  | TYP        | MAX  | UNIT             |

|-----------|-----------------------------------|------------------------------------------------------------------------|------|------------|------|------------------|

|           | Resolution                        |                                                                        | 14   |            |      | Bits             |

| DC ACC    | CURACY                            |                                                                        |      |            |      |                  |

| DNL       | Differential nonlinearity         | 1 LSB = IOUT <sub>FS</sub> / 2 <sup>14</sup>                           |      | ±1         |      | LSB              |

| INL       | Integral nonlinearity             | 1 LSB = IOUT <sub>FS</sub> / 2 <sup>14</sup>                           |      | ±2         |      | LSB              |

| ANALO     | G OUTPUTS                         |                                                                        |      |            |      |                  |

|           | Coarse gain linearity             |                                                                        |      | ±0.4       |      | LSB              |

|           | Offset error                      | Midcode offset                                                         |      | 0.01       |      | %FSR             |

|           | Coin away                         | With external reference                                                |      | <u>+</u> 2 |      | 0/ FCD           |

|           | Gain error                        | With internal reference                                                |      | ±2         |      | %FSR             |

|           | Gain mismatch                     | With internal reference                                                | -2   |            | 2    | %FSR             |

|           | Minimum full-scale output current | Nominal full-scale current,<br>IOUT <sub>FS</sub> = 16 × IBAIS current |      | 2          |      | mA               |

|           | Maximum full-scale output current | Nominal full-scale current,<br>IOUT <sub>FS</sub> = 16 × IBAIS current |      | 20         |      | mA               |

|           | Output compliance                 | IOUT <sub>FS</sub> = 20 mA                                             | -0.5 |            | 1    | ٧                |

|           | Output resistance                 |                                                                        |      | 300        |      | kΩ               |

|           | Output capacitance                |                                                                        |      | 5          |      | pF               |

| REFERI    | ENCE OUTPUT                       |                                                                        | ,    |            |      |                  |

| $V_{REF}$ | Reference output voltage          |                                                                        | 1.14 | 1.2        | 1.26 | ٧                |

|           | Reference output current          |                                                                        |      | 100        |      | nA               |

| REFERI    | ENCE INPUT                        | •                                                                      | •    |            | •    |                  |

|           | VEXTIO input voltage              | External reference mode                                                | 0.1  | 1.2        | 1.25 | V                |

|           | Input resistance                  |                                                                        |      | 1          |      | $M\Omega$        |

|           | Small-signal bandwidth            |                                                                        |      | 500        |      | kHz              |

|           | Input capacitance                 |                                                                        |      | 100        |      | pF               |

| TEMPE     | RATURE COEFFICIENTS               | •                                                                      | ·    |            |      |                  |

|           | Offset drift                      |                                                                        |      | ±1         |      | ppm of<br>FSR/°C |

|           | Gain drift                        | With external reference                                                |      | ±15        |      |                  |

|           | Gain unit                         | With internal reference                                                |      | ±30        |      |                  |

|           | Reference voltage drift           |                                                                        |      | ±8         |      | ppm /°C          |

# **Electrical Characteristics: DC Specifications (continued)**

Typical values at  $T_A$  = 25°C, full temperature range is  $T_{MIN}$  = -40°C to  $T_{MAX}$  = 85°C, DAC sample rate = 500 MSPS, 50% clock duty cycle, VDDA33 = IOVDD = 3.3 V, VDDA18 = CLKVDD18 = DIGVDD18 = 1.8 V, and IOUT<sub>FS</sub> = 20 mA (unless otherwise noted).

|                       | PARAMETER                                            | TEST CONDITIONS                                                                                                        | MIN TYP | MAX   | UNIT   |

|-----------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------|-------|--------|

| POWER C               | ONSUMPTION                                           |                                                                                                                        |         |       |        |

|                       |                                                      | MODE 1, $f_{DAC}$ = 491.52 MSPS, QMC on, IF = 20 MHz                                                                   | 52      | 59    |        |

| h                     | 3.3-V analog supply current                          | $\begin{array}{l} \text{MODE 2, f}_{\text{DAC}} = 320 \text{ MSPS, QMC on,} \\ \text{IF} = 20 \text{ MHz} \end{array}$ | 51      |       | mA     |

| I <sub>VDDA33</sub>   | 3.5-V arialog supply current                         | MODE 3, sleep mode, f <sub>DAC</sub> = 491.52<br>MSPS, DAC in sleep mode                                               | 2.6     |       | ША     |

|                       |                                                      | MODE 4, power-down mode, no clock, DAC in sleep mode                                                                   | 1.6     | 4     |        |

|                       |                                                      | MODE 1, $f_{DAC}$ = 491.52 MSPS, QMC on, IF = 20 MHz                                                                   | 49      | 57    |        |

| la a. mar a           | 1.8-V clock and analog supply current                | $\begin{array}{l} \text{MODE 2, f}_{\text{DAC}} = 320 \text{ MSPS, QMC on,} \\ \text{IF} = 20 \text{ MHz} \end{array}$ | 38      |       | mA     |

| ICLKVDD18             | (CLKVDD18 and VDDA18)                                | MODE 3, sleep mode, f <sub>DAC</sub> = 491.52<br>MSPS, DAC in sleep mode                                               | 43      |       | ША     |

|                       |                                                      | MODE 4, power-down mode, no clock, DAC in sleep mode                                                                   | 1.8     | 4     |        |

|                       | 1.8-V digital supply current<br>(DIGVDD18 and VFUSE) | MODE 1, $f_{DAC}$ = 491.52 MSPS, QMC on, IF = 20 MHz                                                                   | 115     | 130   |        |

|                       |                                                      | MODE 2, $f_{DAC}$ = 320 MSPS, QMC on, IF = 20 MHz                                                                      | 87      |       | mA     |

| I <sub>DIGVDD18</sub> |                                                      | MODE 3, sleep mode, f <sub>DAC</sub> = 491.52<br>MSPS, DAC in sleep mode                                               | 110     |       | ША     |

|                       |                                                      | MODE 4, power-down mode, no clock, DAC in sleep mode                                                                   | 0.7     | 3     |        |

|                       |                                                      | MODE 1, $f_{DAC}$ = 491.52 MSPS, QMC on, IF = 20 MHz                                                                   | 0.002   | 0.015 |        |

|                       | 1.8-V IO supply current                              | MODE 2, $f_{DAC}$ = 320 MSPS, QMC on, IF = 20 MHz                                                                      | 0.002   |       | mA     |

| I <sub>IOVDD</sub>    |                                                      | MODE 3, sleep mode, f <sub>DAC</sub> = 491.52<br>MSPS, DAC in sleep mode                                               | 0.003   |       | ША     |

|                       |                                                      | MODE 4, power-down mode, no clock, DAC in sleep mode                                                                   | 0.003   | 0.015 |        |

|                       |                                                      | MODE 1, $f_{DAC}$ = 491.52 MSPS, QMC on, IF = 20 MHz                                                                   | 464     | 530   |        |

| В                     | Total power dissipation                              | MODE 2, $f_{DAC}$ = 320 MSPS, QMC on, IF = 20 MHz                                                                      | 396     |       | mW     |

| P <sub>dis</sub>      |                                                      | MODE 3, sleep mode, f <sub>DAC</sub> = 491.52 MSPS, DAC in sleep mode                                                  | 284     |       | 11177  |

|                       |                                                      | MODE 4, power-down mode, no clock, DAC in sleep mode                                                                   | 10      | 26    |        |

| PSRR                  | Power-supply rejection ratio                         | DC tested                                                                                                              | -0.4    | 0.4   | %FSR/V |

# 6.6 Electrical Characteristics: AC Specifications

Typical values at T  $_{A}$  = 25°C, full temperature range is T $_{MIN}$  = -40°C to T $_{MAX}$  = 85°C, DAC sample rate = 500 MSPS, 50% clock duty cycle, VDDA33 = IOVDD = 3.3 V, VDDA18 = CLKVDD18 = DIGVDD18 = 1.8 V, and IOUT  $_{FS}$  = 20 mA (unless otherwise noted).

|                      | PARAMETER                         | TEST CONDITIONS                                                                                                     | MIN | TYP MAX | UNIT   |

|----------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------|-----|---------|--------|

| ANALO                | G OUTPUT                          |                                                                                                                     |     |         |        |

| f <sub>DAC</sub>     | Maximum sample rate               |                                                                                                                     | 500 |         | MSPS   |

| t <sub>s(DAC)</sub>  | Output settling time to 0.1%      | Transition: Code 0x0000 to 0x3FFF                                                                                   |     | 11      | ns     |

| t <sub>PD</sub>      | Output propagation delay          | Does not include digital latency                                                                                    |     | 2       | ns     |

| t <sub>r(IOUT)</sub> | Output rise time                  | 10% to 90%                                                                                                          |     | 200     | ps     |

| t <sub>f(IOUT)</sub> | Output fall time                  | 90% to 10%                                                                                                          |     | 200     | ps     |

|                      | Digital latency                   | Length of delay from DAC pin inputs to DATA at output pins. In normal operation mode including the latency of FIFO. |     | 26      | DACCLK |

| AC PER               | RFORMANCE                         |                                                                                                                     |     |         |        |

|                      |                                   | $f_{DAC} = 500 \text{ MSPS}, f_{out} = 10.1 \text{ MHz}$                                                            |     | 82      |        |

| SFDR                 | Spurious free dynamic             | $f_{DAC} = 500 \text{ MSPS}, f_{out} = 20.1 \text{ MHz}$                                                            |     | 78      | dBc    |

|                      |                                   | $f_{DAC} = 500 \text{ MSPS}, f_{out} = 70.1 \text{ MHz}$                                                            |     | 74      |        |

|                      |                                   | f <sub>DAC</sub> = 500 MSPS, f <sub>out</sub> = 10.1 ±0.5 MHz                                                       |     | 84      |        |

| IMD3                 | Intermedulation distortion        | $f_{DAC} = 500 \text{ MSPS}, f_{out} = 20.1 \pm 0.5 \text{ MHz}$                                                    |     | 84      | dDo    |

| IIVID3               | Intermodulation distortion        | $f_{DAC} = 500 \text{ MSPS}, f_{out} = 70.1 \pm 0.5 \text{ MHz}$                                                    |     | 75      | dBc    |

|                      |                                   | f <sub>DAC</sub> = 500 MSPS, f <sub>out</sub> = 150.1 ±0.5 MHz                                                      |     | 63      |        |

|                      |                                   | f <sub>DAC</sub> = 500 MSPS, f <sub>out</sub> = 10.1 MHz                                                            |     | 160     |        |

| NSD                  | Noise spectral density            | f <sub>DAC</sub> = 500 MSPS, f <sub>out</sub> = 20.1 MHz                                                            |     | 157     | dBc/Hz |

|                      |                                   | f <sub>DAC</sub> = 500 MSPS, f <sub>out</sub> = 70.1 MHz                                                            |     | 155     |        |

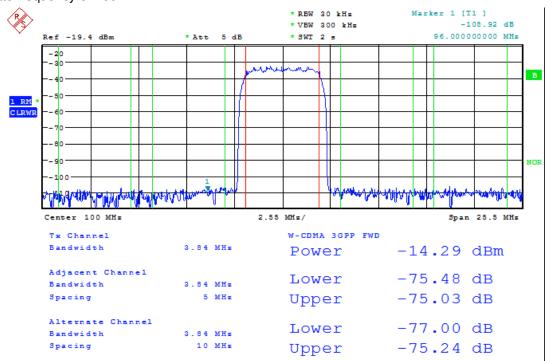

| 4 CL D               | A diagonal about a language matic | f <sub>DAC</sub> = 491.52 MSPS, f <sub>out</sub> = 30.72 MHz, WCDMA TM1                                             |     | 78      | dD.    |

| ACLR                 | Adjacent channel leakage ratio    | f <sub>AC</sub> = 491.52 MSPS, f <sub>out</sub> = 153.6 MHz, WCDMA TM1                                              |     | 74      | dBc    |

# 6.7 Electrical Characteristics: Digital Specifications

Typical values at T  $_{A}$  = 25°C, full temperature range is T  $_{MIN}$  = -40°C to T  $_{MAX}$  = 85°C, DAC sample rate = 500 MSPS, 50% clock duty cycle, VDDA33 = IOVDD = 3.3 V, VDDA18 = CLKVDD18 = DIGVDD18 = 1.8 V, and IOUT  $_{FS}$  = 20 mA (unless otherwise noted).

|                 | PARAMETERS                                                | TEST CONDITIONS                | MIN          | TYP MAX       | UNIT |  |  |  |  |

|-----------------|-----------------------------------------------------------|--------------------------------|--------------|---------------|------|--|--|--|--|

| CMOS            | CMOS DIGITAL INPUTS (RESETB, SDENB, SCLK, SDIO, TXENABLE) |                                |              |               |      |  |  |  |  |

| $V_{IH}$        | High-level input voltage                                  | IOVDD = 3.3 V, 2.5 V, or 1.8 V | IOVDD × 0.6  |               | V    |  |  |  |  |

| $V_{IL}$        | Low-level input voltage                                   | IOVDD = 3.3 V, 2.5 V, or 1.8 V |              | 0.25 × IOVDD  | V    |  |  |  |  |

| I <sub>IH</sub> | High-level input current                                  | IOVDD = 3.3 V, 2.5 V, or 1.8 V | -40          | 40            | μΑ   |  |  |  |  |

| I <sub>IL</sub> | Low-level input current                                   | IOVDD = 3.3 V, 2.5 V, or 1.8 V | -40          | 40            | μΑ   |  |  |  |  |

| DIGITA          | AL OUTPUTS – CMOS INTERFACE (SDOUT                        | , SDIO)                        |              |               |      |  |  |  |  |

| $V_{OH}$        | High-level output voltage                                 | IOVDD = 3.3 V, 2.5 V, or 1.8 V | 0.85 × IOVDD |               | V    |  |  |  |  |

| $V_{OL}$        | Low-level output voltage                                  |                                |              | 0.125 × IOVDD | V    |  |  |  |  |

| LVPEC           | L INPUTS – (DACCLKx, ALIGNx)                              |                                |              |               |      |  |  |  |  |

| $V_{CM}$        | LVPECL input common-mode voltage                          |                                |              | 0.5           | ٧    |  |  |  |  |

| $V_{IDIFF}$     | Differential input peak-to-peak voltage                   |                                | 0.4          | 1             | V    |  |  |  |  |

# **Electrical Characteristics: Digital Specifications (continued)**

Typical values at T  $_{A}$  = 25°C, full temperature range is T  $_{MIN}$  = -40°C to T  $_{MAX}$  = 85°C, DAC sample rate = 500 MSPS, 50% clock duty cycle, VDDA33 = IOVDD = 3.3 V, VDDA18 = CLKVDD18 = DIGVDD18 = 1.8 V, and IOUT  $_{FS}$  = 20 mA (unless otherwise noted).

|                    | ,                                                                                     |                 |     |     |      |      |  |  |  |

|--------------------|---------------------------------------------------------------------------------------|-----------------|-----|-----|------|------|--|--|--|

|                    | PARAMETERS                                                                            | TEST CONDITIONS | MIN | TYP | MAX  | UNIT |  |  |  |

| LVDS               | LVDS INTERFACE (DATA[13:0]x, DA[6:0]x , DB[6:0]x , DA_CLKx, DB_CLKx, DATACLKx, SYNCx) |                 |     |     |      |      |  |  |  |

| $V_{A,B+}$         | Logic high differential input voltage threshold                                       |                 | 175 |     |      | mV   |  |  |  |

| V <sub>A,B</sub> _ | Logic low differential input voltage threshold                                        |                 |     |     | -175 | mV   |  |  |  |

| $V_{COM}$          | LVDS input common-mode voltage                                                        |                 | 1   | 1.2 | 2    | ٧    |  |  |  |

| Z <sub>T</sub>     | Internal termination                                                                  |                 | 85  | 110 | 135  | Ω    |  |  |  |

| C <sub>L</sub>     | LVDS input capacitance                                                                |                 |     | 2   |      | pF   |  |  |  |

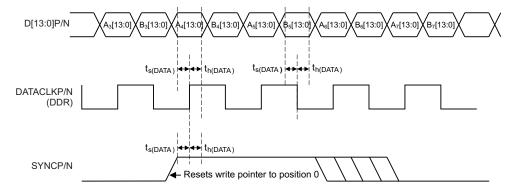

### 6.8 Timing Requirements

Typical values at T  $_{A}$  = 25°C, full temperature range is T  $_{MIN}$  = -40°C to T  $_{MAX}$  = 85°C, DAC sample rate = 500 MSPS, 50% clock duty cycle, VDDA33 = IOVDD = 3.3 V, VDDA18 = CLKVDD18 = DIGVDD18 = 1.8 V, and IOUT  $_{FS}$  = 20 mA (unless otherwise noted).

|                       |                |                                                                                              |         |         | MIN | TYP  | MAX | UNIT |

|-----------------------|----------------|----------------------------------------------------------------------------------------------|---------|---------|-----|------|-----|------|

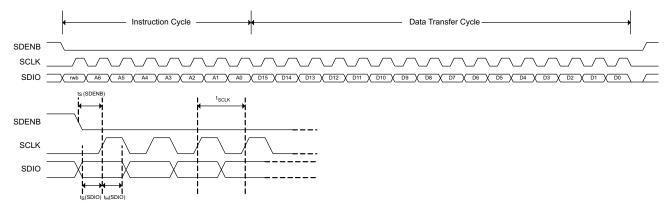

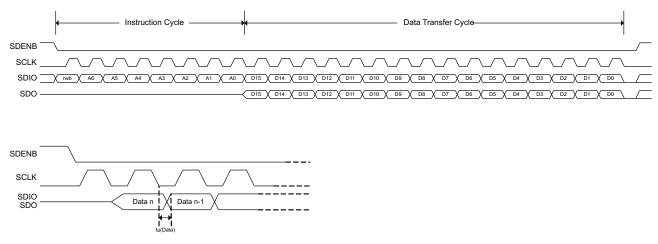

| SERIAL F              | PORT TIMING    |                                                                                              |         |         |     |      |     |      |

| t <sub>s(SENDB)</sub> | Setup time, SI | Setup time, SDENB to rising edge of SCLK                                                     |         |         |     |      |     | ns   |

| $t_{s(SDIO)}$         | Setup time, SI | DIO to rising edge of SCLK                                                                   |         |         | 10  |      |     | ns   |

| $t_{h(SDIO)}$         | Hold time, SD  | IO from rising edge of SCLK                                                                  |         |         | 5   |      |     | ns   |

| t <sub>(SCLK)</sub>   | Period of SCL  | K                                                                                            |         |         | 100 |      |     | ns   |

| t <sub>(SCLKH)</sub>  | High time of S | CLK                                                                                          |         |         | 40  |      |     | ns   |

| t <sub>(SCLKL)</sub>  | Low time of S  | CLK                                                                                          |         |         | 40  |      |     | ns   |

| $t_{d(DATA)}$         | Data output de | elay after falling edge of SCLK                                                              |         |         |     | 10   |     | ns   |

| T <sub>RESET</sub>    | Minimum RES    | TB pulse duration                                                                            |         |         |     | 25   |     | ns   |

| LVDS INF              | PUT TIMING     |                                                                                              |         |         |     |      |     |      |

|                       |                |                                                                                              | config3 | Setting |     |      |     | ı    |

|                       |                |                                                                                              | datadly | clkdly  |     |      |     | ı    |

|                       |                |                                                                                              | 0       | 0       |     | -20  |     | ı    |

|                       |                |                                                                                              | 0       | 1       |     | -120 |     | ı    |

|                       |                |                                                                                              | 0       | 2       |     | -220 |     | ı    |

|                       |                |                                                                                              | 0       | 3       |     | -310 |     | ı    |

|                       |                | D[x0] valid to DATACLK rising or falling edge                                                | 0       | 4       |     | -390 |     | ı    |

|                       |                | for single bus single clock mode; DA/DB[x0] valid to DB_CLK rising or falling                | 0       | 5       |     | -480 |     | ı    |

| t <sub>s(DATA)</sub>  | Setup time     | edge for dual bus single clock mode;                                                         | 0       | 6       |     | -560 |     | ps   |

|                       |                | DA[x0] valid to DA_ČLK rising or falling edge, and DB[x0] valid for DB_CLK rising or falling | 0       | 7       |     | -630 |     | ı    |

|                       |                | edge for dual bus dual clock mode                                                            | 1       | 0       |     | 70   |     | ı    |

|                       |                |                                                                                              | 2       | 0       |     | 150  |     | ı    |

|                       |                |                                                                                              | 3       | 0       |     | 230  |     | ı    |

|                       |                |                                                                                              | 4       | 0       |     | 330  |     | i    |

|                       |                |                                                                                              | 5       | 0       |     | 430  |     | i    |

|                       |                |                                                                                              | 6       | 0       |     | 530  |     | i    |

|                       |                |                                                                                              | 7       | 0       |     | 620  |     | ı    |

### **Timing Requirements (continued)**

Typical values at T  $_{A}$  = 25°C, full temperature range is T  $_{MIN}$  = -40°C to T  $_{MAX}$  = 85°C, DAC sample rate = 500 MSPS, 50% clock duty cycle, VDDA33 = IOVDD = 3.3 V, VDDA18 = CLKVDD18 = DIGVDD18 = 1.8 V, and IOUT  $_{FS}$  = 20 mA (unless otherwise noted).

|                      |           |                                                                                              |         |         | MIN | TYP  | MAX | UNIT |

|----------------------|-----------|----------------------------------------------------------------------------------------------|---------|---------|-----|------|-----|------|

|                      |           |                                                                                              | config3 | Setting |     |      |     |      |

|                      |           |                                                                                              | datadly | clkdly  |     |      |     |      |

|                      |           |                                                                                              | 0       | 0       |     | 310  |     |      |

|                      |           |                                                                                              | 0       | 1       |     | 390  |     |      |

|                      |           |                                                                                              | 0       | 2       |     | 480  |     |      |

|                      |           |                                                                                              | 0       | 3       |     | 560  |     |      |

|                      |           |                                                                                              | 0       | 4       |     | 650  |     | ps   |

|                      |           |                                                                                              | 0       | 5       |     | 740  |     |      |

| t <sub>h(DATA)</sub> | Hold time |                                                                                              | 0       | 6       |     | 850  |     |      |

|                      |           | DA[x0] valid to DA_CLK rising or falling edge, and DB[x0] valid for DB_CLK rising or falling | 0       | 7       |     | 930  |     |      |

|                      |           | edge for dual bus dual clock mode.                                                           | 1       | 0       |     | 200  |     |      |

|                      |           |                                                                                              | 2       | 0       |     | 100  |     |      |

|                      |           |                                                                                              | 3       | 0       |     | 20   |     |      |

|                      |           |                                                                                              | 4       | 0       |     | -60  |     |      |

|                      |           |                                                                                              | 5       | 0       |     | -140 |     |      |

|                      |           |                                                                                              | 6       | 0       |     | -220 |     | 1    |

|                      |           |                                                                                              | 7       | 0       |     | -290 |     |      |

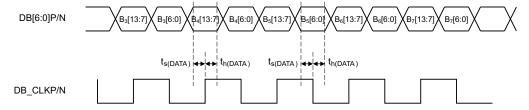

Figure 1. Input Data Timing for Single-Bus, Single-Clock Mode

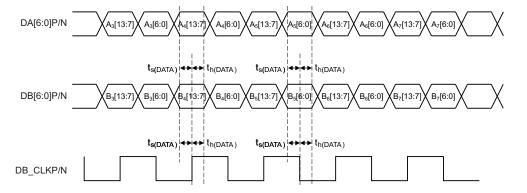

between DA\_CLK and DB\_CLK

Figure 2. Input Data Timing for Dual-Bus, Dual-Clock Mode

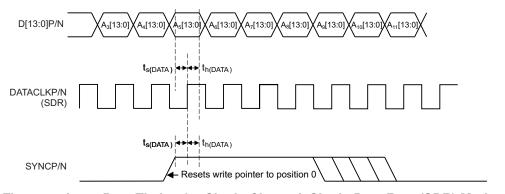

Figure 3. Input Data Timing for Dual-Bus, Single-Clock Mode

Figure 4. Input Data Timing for Single-Channel, Single Data Rate (SDR) Mode

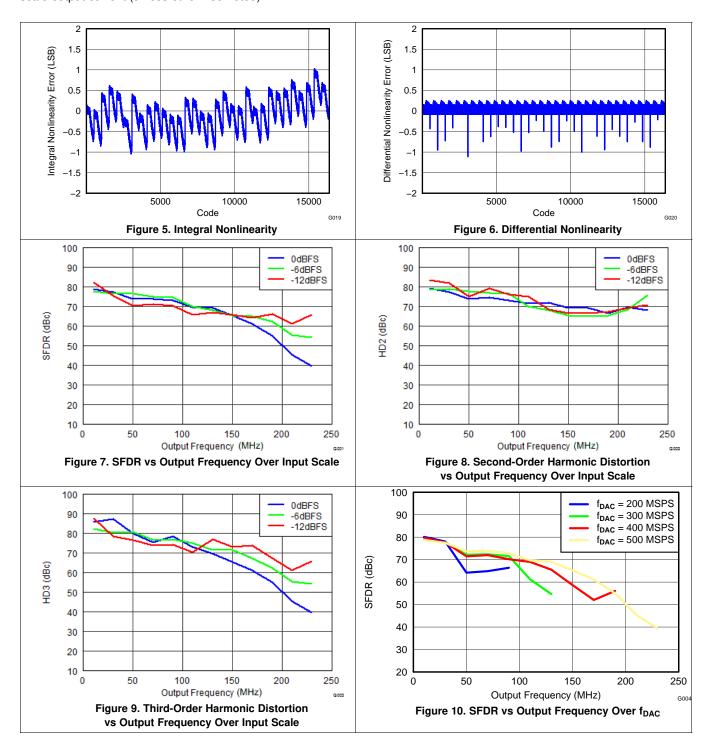

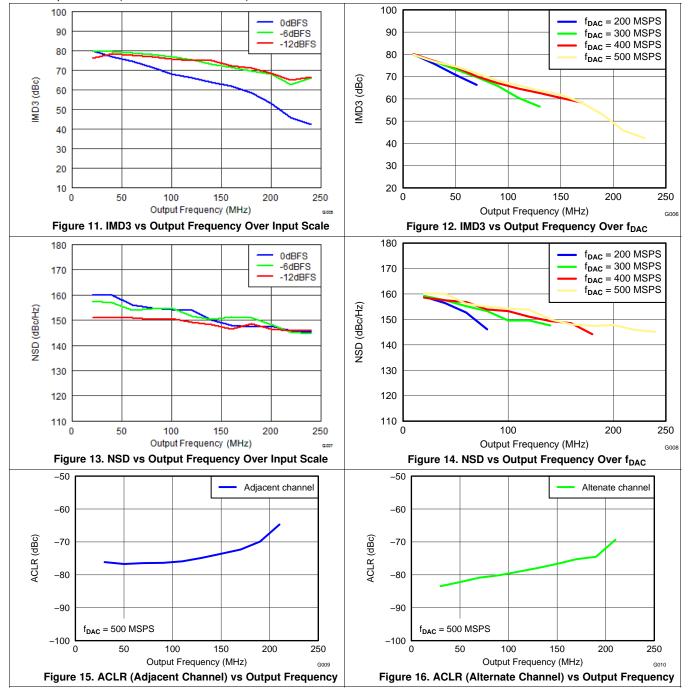

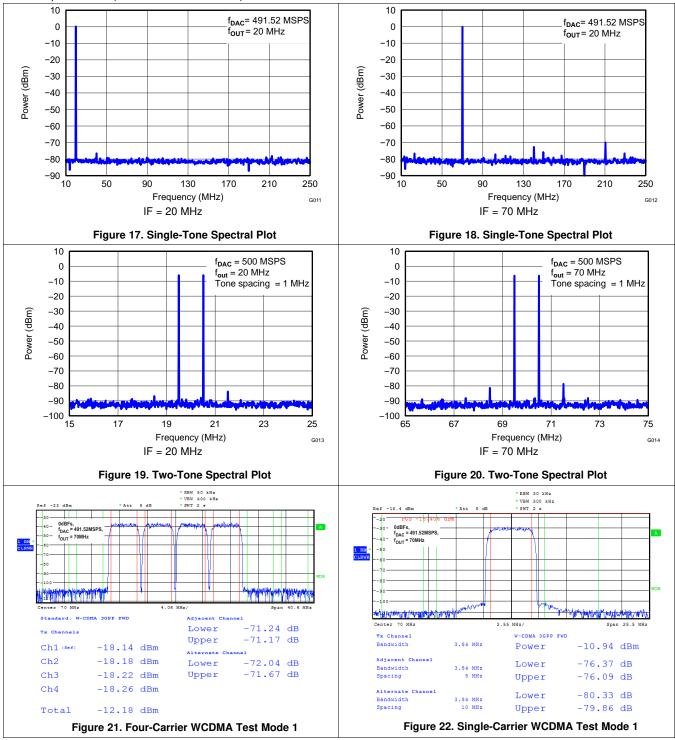

#### 6.9 Typical Characteristics

All plots are at 25°C, nominal supply voltages,  $f_{DAC} = 500$  MSPS, 50% clock duty cycle, 0-dBFS input signal, and 20-mA full-scale output current (unless otherwise noted).

Submit Documentation Feedback

Copyright © 2013–2017, Texas Instruments Incorporated

### **Typical Characteristics (continued)**

All plots are at 25°C, nominal supply voltages,  $f_{DAC}$  = 500 MSPS, 50% clock duty cycle, 0-dBFS input signal, and 20-mA full-scale output current (unless otherwise noted).

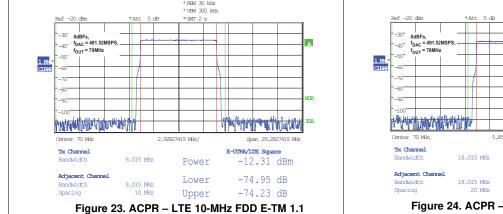

### **Typical Characteristics (continued)**

All plots are at 25°C, nominal supply voltages,  $f_{DAC}$  = 500 MSPS, 50% clock duty cycle, 0-dBFS input signal, and 20-mA full-scale output current (unless otherwise noted).

Submit Documentation Feedback

Copyright © 2013–2017, Texas Instruments Incorporated

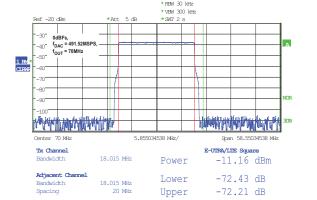

# **Typical Characteristics (continued)**

All plots are at 25°C, nominal supply voltages,  $f_{DAC} = 500$  MSPS, 50% clock duty cycle, 0-dBFS input signal, and 20-mA full-scale output current (unless otherwise noted).

Figure 24. ACPR – LTE 20-MHz FDD E-TM 1.1

Copyright © 2013–2017, Texas Instruments Incorporated

### 7 Detailed Description

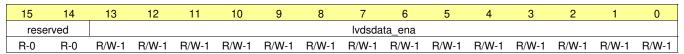

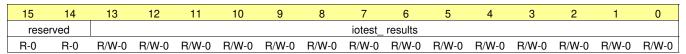

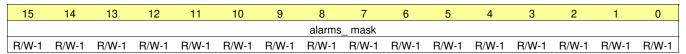

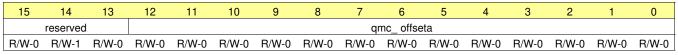

#### 7.1 Overview