## PLCHIP-P13-51220

32-bit PLC on a Chip Integrated Circuit with up to 256KB Flash, Ethernet, USB, LCD, Digital I/O, Analog I/O, PWM

Rev. 6 - 1/27/2021

# DATA SHEET

## **Datasheet Contents**

|    | General Description                            |      |

|----|------------------------------------------------|------|

| 2. | Features and Benefits                          | 2    |

| 3. | Ordering Information                           | 3    |

|    | Pin Summary                                    | 3    |

|    | Pin Details 9                                  |      |

| 6. | Functional Descriptions & Circuit Examples     |      |

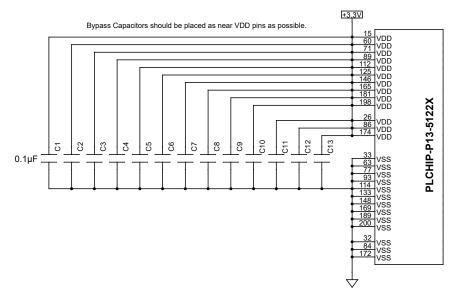

|    | 6.1 VDD Power Pins                             |      |

|    | 6.2 VSS Power Pins (GND)                       | . 35 |

|    | 6.3 Oscillator Input                           |      |

|    | 6.4 General Purpose I/O (GPIO)                 |      |

|    | 6.5 Pulse Width Modulation (PWM) Outputs       | . 38 |

|    | 6.6 Analog I/O                                 | . 39 |

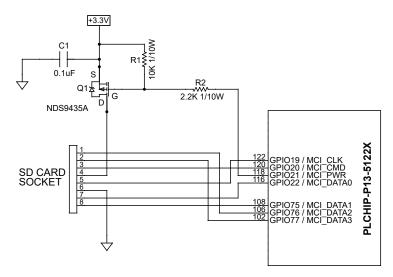

|    | 6.7 SD Card Interface                          | . 41 |

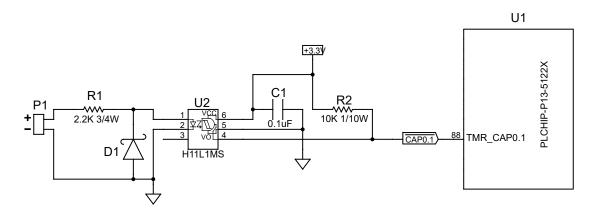

|    | 6.8 Timer / Capture Inputs                     | . 42 |

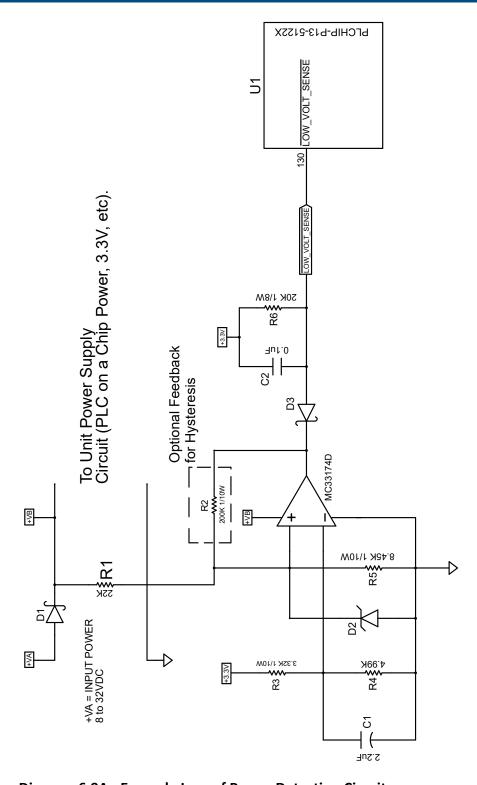

|    | 6.9 Retentive Memory / Loss of Power Detection | . 44 |

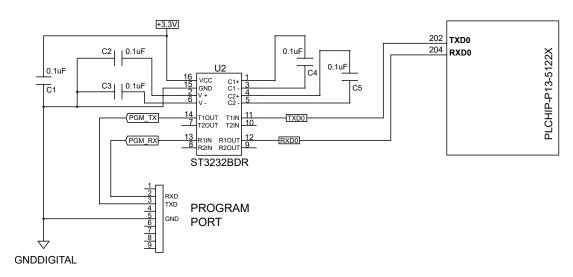

|    | 6.10 Programming Port                          |      |

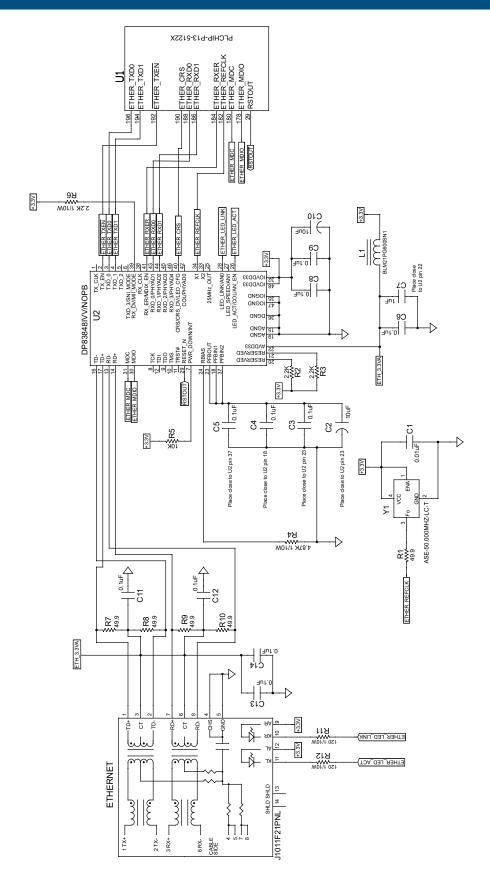

|    | 6.11 Ethernet Port                             | . 46 |

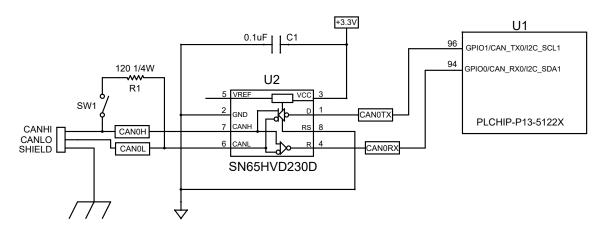

|    | 6.12 Controller Area Network (CAN) Ports       | . 50 |

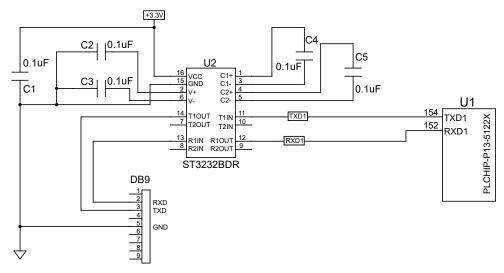

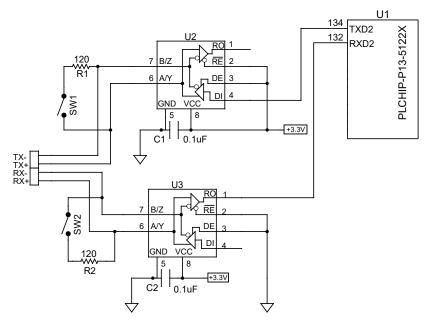

|    | 6.13 Serial (UART) Ports                       | . 50 |

|    | 6.14 SPI Ports                                 | . 53 |

|    | 6.15 I <sup>2</sup> C Ports                    | . 54 |

|    | 6.16 Quadrature Encoder Interface              | . 55 |

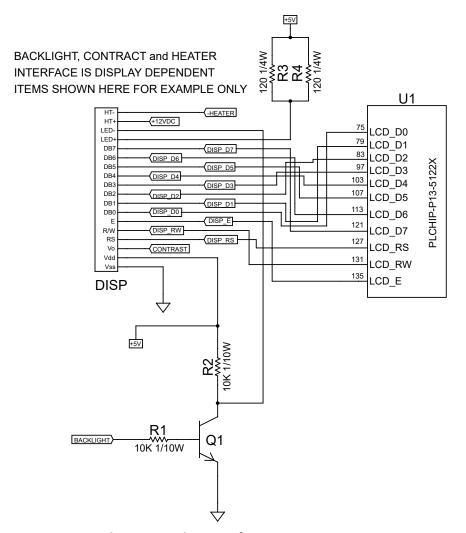

|    | 6.17 Liquid Crystal Display (LCD) Interface    |      |

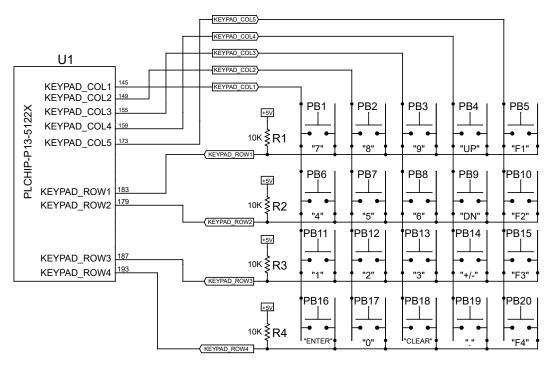

|    | 6.18 Keypad Interface                          |      |

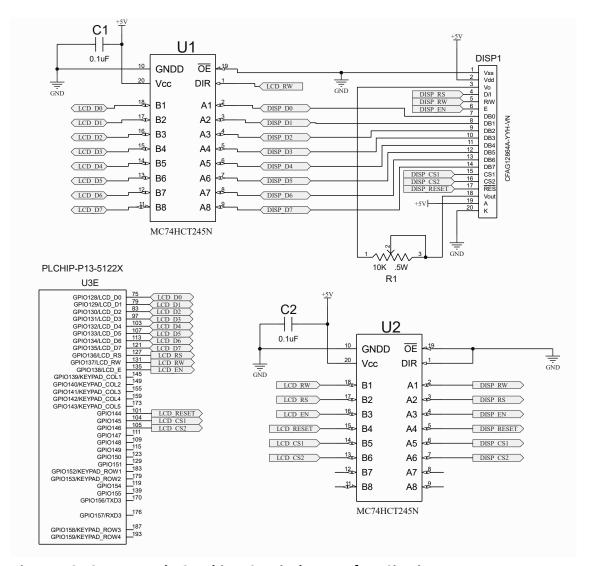

|    | 6.19 Graphics LCD Display Interface            |      |

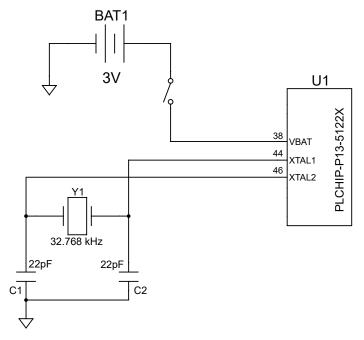

|    | 6.20 Real Time Clock Circuit                   |      |

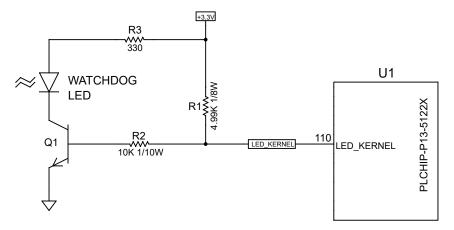

|    | 6.21 Watchdog LED Circuit                      |      |

| 7. | Electrical Characteristics                     |      |

| 8. | Thermal Characteristics                        | . 62 |

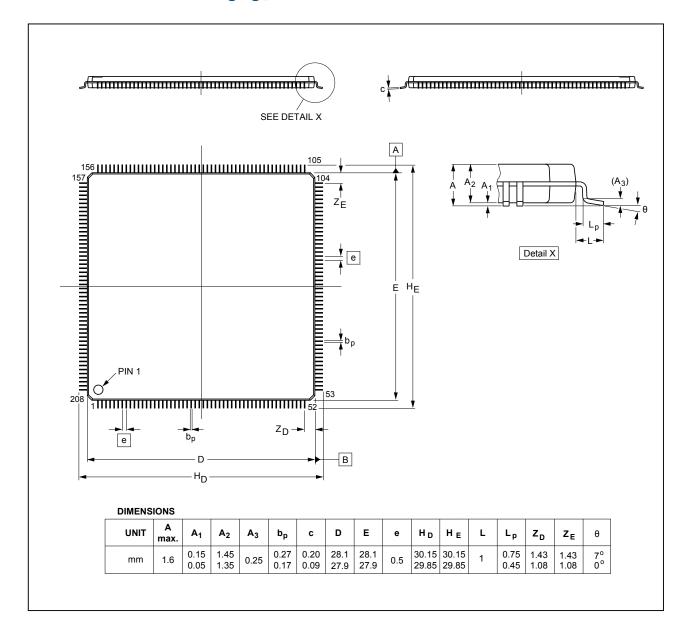

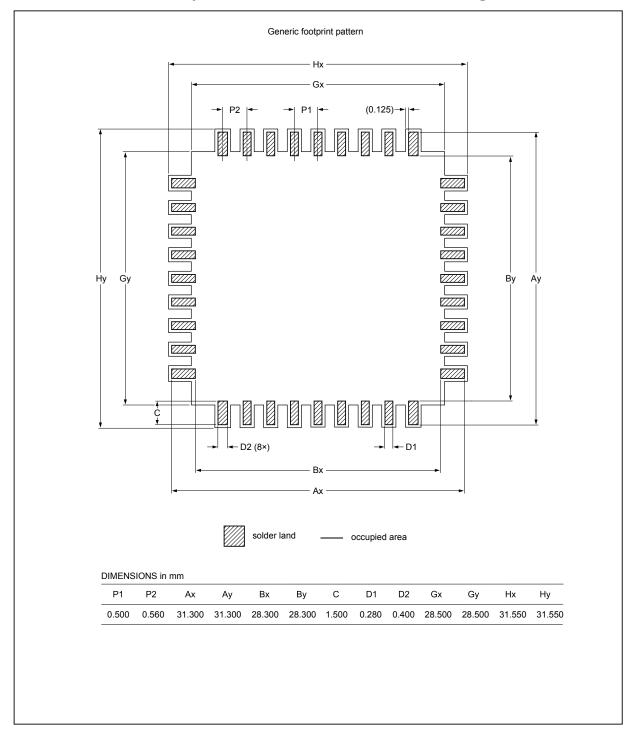

| 9. | Package & Soldering Details                    | . 63 |

| 10 | . Software Information                         | . 65 |

|    | 10.1 EZ LADDER Tookit                          | . 65 |

|    | 10.2 Target Kernel                             | . 65 |

| 11 | . Revision History                             | . 65 |

#### **WARNING!!**

The PLC on a Chip, must not be used alone in applications which could be hazardous to personnel in the event of failure of this device. Precautions must be taken by the user to provide mechanical and/or electrical safeguards external to this device. This device is NOT APPROVED for domestic or human medical use. All PLC on a Chip Specifications and Requirements subject to change without notice.

## 1. General Description

The PLCHIP-P13-51220 is a 32 bit microcontroller for embedded applications with full PLC functionality. The P-Series combines powerful peripherals with industry standard I/O for a complete package that provides the advanced features required while providing an easy-to-use ladder diagram programming interface; EZ LADDER Toolkit.

The PLCHIP-P13-51220 provides up to 256K of Program Flash Storage, 32K of RAM, up to 164 general purpose digital I/O, up to 3 I2C ports, up to 2 SPI Ports, up to 2 CAN Network Ports, up to 4 Serial Ports, up to 8 Analog Inputs, up to 1 Analog Output, up to 16 Pulse Width Modulation Outputs, 1 Ethernet Port, Internal Real Time Clock, SD Card Interface, up to 6 counter/timer inputs, up to 1 quadrature counter input, LCD Display Support and Keypad Support.

The PLCHIP-P13-51220 is programmed exclusively using EZ LADDER Toolkit.

### 2. Features and Benefits

#### ■ Memory:

- Up to 256K Flash memory for Ladder Program storage.

- Up to 32K RAM memory program execution and variables.

- Up to 3500 bytes EEPROM memory for Set Point Storage and Retentive Variable Storage.

#### ■ Serial Interfaces:

- Up to three I<sup>2</sup>C Ports. 1Mbit/s Data Rate

- Up to four TTL Serial Ports. One Supports full handshaking while 3 support RX/TX. Supports Modbus Master & Slave.

- TTL Ethernet Port, Supports Modbus over TCP

- Up to two Controller Area Network (CAN) Ports. Supports Divelbiss OptiCAN, SAE J1939

- Up to two SPI Ports.

#### **■ HMI Support:**

- Supports HD44780 Controller Compatible LCD Displays with up to 4 rows and up to 40 columns.

- Supports a Keypad matrix of 5 columns by 4 rows for numbers 0-9, decimal, function keys

#### **■** Digital Interfaces:

- SD/MMC Memory Card Interface

- Up to six inputs that may be utilized as counters or timers.

- Up to three inputs when configured properly will interface to a quadrature encoder.

- Up to 164 General Purpose I/O (GPIO) that may be individually configured as inputs or outputs.

- Up to Sixteen Pulse Width Modulated Outputs

- Real Time Clock (requires external clock and power source).

#### ■ Analog Interfaces:

- Up to 8 Channels, 12 bit Analog to Digital Converter (ADC).

- Up to 1 Channel, 10 bit Digital to Analog Converter (DAC).

## 3. Ordering Information

PLCHIP-P13-51220 P-Series Integrated Circuits may be ordered by Part number. Pricing varies base on part number and quantity.

| Part Number         | Description                                                                                                                                                                                                                                                                                                                |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLCHIP-P13-51220    | PLC on a Chip P-Series, 208 Pin Low Profile, Quad Flat Package (LQFP208), 256 Flash, 32K RAM, 164 GPIO, 16 PWM Channels, 8 ADC Channels, 1 DAC Channel, 6 Timer/Counter Channels, Quadrature Encoder Input, LCD / Keypad Support, Ethernet, USB, 4 Serial Ports, 2 CAN Ports, SD/MMC Card Support. Shipped in Trays of 36. |

| PLCHIP-P13-51220X1  | PLC on a Chip P-Series, P13 (PLCHIP-P13-512210). Shipped as Single piece.                                                                                                                                                                                                                                                  |

| PLCHIP-P13-51220X5  | PLC on a Chip P-Series, P13 (PLCHIP-P13-512210). Shipped as 5 Pack.                                                                                                                                                                                                                                                        |

| PLCHIP-P13-51220X10 | PLC on a Chip P-Series, P13 (PLCHIP-P13-512210). Shipped as 10 Pack.                                                                                                                                                                                                                                                       |

## 4. Pin Summary

The PLCHIP-P13-51220 provides great flexibility in features by allowing pins to be assigned multple functions. While each Pin may only be configured to be a single function, many pins provide multiple configuration options for functionality. These options are listed as Function 1 through Function 4 for each pin in TABLE 1.

| TABLE | TABLE 1 - Pin Summary |            |            |            |  |

|-------|-----------------------|------------|------------|------------|--|

| Pin#  | Function 1            | Function 2 | Function 3 | Function 4 |  |

| 1     | GPIO108               |            |            |            |  |

| 2     | RES11                 |            |            |            |  |

| 3     | GPIO99                |            |            |            |  |

| 4     | RES7                  |            |            |            |  |

| 5     | GPIO124               | PWM4       |            |            |  |

| 6     | RES8                  |            |            |            |  |

| 7     | GPIO109               |            |            |            |  |

| 8     | RES6                  |            |            |            |  |

| 9     | GPIO160               |            |            |            |  |

| 10    | RES9                  |            |            |            |  |

| 11    | GPIO125               | PWM5       |            |            |  |

| TABLE | TABLE 1 - Pin Summary |            |            |            |  |

|-------|-----------------------|------------|------------|------------|--|

| Pin # | Function 1            | Function 2 | Function 3 | Function 4 |  |

| 12    | GPIO26                | Al3        | A00        |            |  |

| 13    | GPIO100               |            |            |            |  |

| 14    | GPIO25                | AI2        |            |            |  |

| 15    | VDD4                  |            |            |            |  |

| 16    | GPIO24                | Al1        |            |            |  |

| 17    | GPIO101               |            |            |            |  |

| 18    | GPIO23                | AI0        |            |            |  |

| 19    | GPIO126               |            |            |            |  |

| 20    | VDD_AN                |            |            |            |  |

| 21    | GPIO110               |            |            |            |  |

| 22    | VSS_AN                |            |            |            |  |

| 23    | GPIO102               |            |            |            |  |

| 24    | VREF_AN               |            |            |            |  |

| 25    | GPIO127               |            |            |            |  |

| 26    | VDD1                  |            |            |            |  |

| 27    | GPIO103               |            |            |            |  |

| 28    | GPIO111               |            |            |            |  |

| 29    | RSTOUT                |            |            |            |  |

| 30    | GPIO161               |            |            |            |  |

| 31    | GPIO94                |            |            |            |  |

| 32    | VSS11                 |            |            |            |  |

| 33    | VSS1                  |            |            |            |  |

| 34    | RTCX1                 |            |            |            |  |

| 35    | ~RESET                |            |            |            |  |

| 36    | RTCX2                 |            |            |            |  |

| 37    | RES2                  |            |            |            |  |

| 38    | VBAT                  |            |            |            |  |

| 39    | GPIO95                |            |            |            |  |

| 40    | GPIO63                | AI5        |            |            |  |

| 41    | GPIO12                | AI6        |            |            |  |

| 42    | GPI012                | Al4        |            |            |  |

|       | GPIO62<br>GPIO93      |            |            |            |  |

| 43    | XTAL1                 |            |            |            |  |

| 45    | GPIO13                | <br>Λ17    |            |            |  |

|       |                       | AI7        |            |            |  |

| 46    | XTAL2                 |            |            |            |  |

| 47    | GPIO91                |            |            |            |  |

| 48    | GPIO28                | I2C_SCL0   |            |            |  |

| 49    | GPIO92                |            |            |            |  |

| 50    | GPIO27                | I2C_SDA0   |            |            |  |

| 51    | GPIO31                |            |            |            |  |

| TABLE | TABLE 1 - Pin Summary |                |            |            |  |

|-------|-----------------------|----------------|------------|------------|--|

| Pin # | Function 1            | Function 2     | Function 3 | Function 4 |  |

| 52    |                       |                |            |            |  |

| 53    | GPIO88                |                |            |            |  |

| 54    | GPIO89                |                |            |            |  |

| 55    | GPIO122               | PWM2           |            |            |  |

| 56    | GPIO121               | PWM1           |            |            |  |

| 57    | GPIO90                |                |            |            |  |

| 58    | GPIO120               | PWM0           |            |            |  |

| 59    | GPIO82                |                |            |            |  |

| 60    | VDD5                  |                |            |            |  |

| 61    | GPIO29                |                |            |            |  |

| 62    | GPIO30                |                |            |            |  |

| 63    | VSS2                  |                |            |            |  |

| 64    | GPIO87                |                |            |            |  |

| 65    | GPIO119               |                |            |            |  |

| 66    | GPIO50                | TMR_CAP1.0     |            |            |  |

| 67    | GPIO83                |                |            |            |  |

| 68    | GPIO51                | TMR_CAP1.1     |            |            |  |

| 69    | GPIO14                |                |            |            |  |

| 70    | GPIO52                | QEI_PHA        |            |            |  |

| 71    | VDD6                  |                |            |            |  |

| 72    | GPIO53                |                |            |            |  |

| 73    | GPIO84                |                |            |            |  |

| 74    | GPIO54                | TMR_MAT1       |            |            |  |

| 75    | GPIO128               | LCD_D0         |            |            |  |

| 76    | GPIO55                | QEI_PHB        |            |            |  |

| 77    | VSS3                  |                |            |            |  |

| 78    | GPIO56                | QEI_IDX        |            |            |  |

| 79    | GPIO129               | LCD_D1         |            |            |  |

| 80    | GPI057                |                |            |            |  |

| 81    | GPIO85                |                |            |            |  |

| 82    | GPIO58                | TMR_CAP0.0     |            |            |  |

| 83    | GPIO130               | LCD_D2         |            |            |  |

| 84    | VSS12                 |                |            |            |  |

| 85    | GPIO86                |                |            |            |  |

| 86    | VDD2                  |                |            |            |  |

| 87    | GPIO80                |                |            |            |  |

|       |                       | <br>TMP_CADO 1 |            |            |  |

| 88    | GPIO59                | TMR_CAP0.1     |            |            |  |

| 89    | VDD7                  | <br>TNAD NAATO |            |            |  |

| 90    | GPIO60                | TMR_MATO       |            |            |  |

| 91    | GPIO78                | TMR_CAP2.0     |            |            |  |

| Pin # | Function 1 | Function 2       | Function 3 | Function 4 |

|-------|------------|------------------|------------|------------|

| 92    | GPIO61     | MCI_CARD_PRESENT |            |            |

| 93    | VSS4       |                  |            |            |

| 94    | GPIO0      | CAN_RX0          | I2C_SDA1   |            |

| 95    | GPIO81     |                  |            |            |

| 96    | GPI01      | CAN_TX0          | I2C_SCL1   |            |

| 97    | GPIO131    | LCD D3           |            |            |

| 98    | GPIO10     | I2C_SDA2         |            |            |

| 99    | GPIO79     | TMR_CAP2.1       |            |            |

| 100   | GPI011     | 12C_SCL2         |            |            |

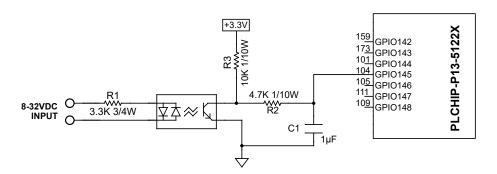

| 101   | GPIO144    |                  |            |            |

| 102   | GPI077     | MCI_DATA3        |            |            |

| 103   | GPIO132    | LCD_D4           |            |            |

| 104   | GPIO145    |                  |            |            |

| 105   | GPIO146    |                  |            |            |

| 106   | GPI076     | MCI_DATA2        |            |            |

| 107   | GPIO133    | LCD_D5           |            |            |

| 108   | GPI075     | MCI_DATA1        |            |            |

| 109   | GPIO148    |                  |            |            |

| 110   | LED_KERNEL | Pull to 3.3V     |            |            |

| 111   | GPIO147    |                  |            |            |

| 112   | VDD8       |                  |            |            |

| 113   | GPIO134    | LCD_D6           |            |            |

| 114   | VSS5       |                  |            |            |

| 115   | GPIO149    |                  |            |            |

| 116   | GPIO22     | MCI_DATA0        |            |            |

| 117   | GPIO162    |                  |            |            |

| 118   | GPIO21     | MCI_PWR          |            |            |

| 119   | GPIO154    |                  |            |            |

| 120   | GPIO20     | MCI CMD          |            |            |

| 121   | GPIO135    | LCD_D7           |            |            |

| 122   | GPIO19     | MCI_CLK          |            |            |

| 123   | GPIO150    |                  |            |            |

| 124   | GPIO18     | SPI_MOSI0        |            |            |

| 125   | VDD9       |                  |            |            |

| 126   | GPIO17     | SPI_MISO0        |            |            |

| 127   | GPIO136    | LCD_RS           |            |            |

| 128   | GPIO15     | SPI_SCK0         |            |            |

| 129   | GPIO151    |                  |            |            |

| 130   | GPIO16     | LOW_VOLT_SENSE   |            |            |

| TABLE | TABLE 1 - Pin Summary |             |            |            |  |

|-------|-----------------------|-------------|------------|------------|--|

| Pin#  | Function 1            | Function 2  | Function 3 | Function 4 |  |

| 131   | GPIO137               | LCD_RW      |            |            |  |

| 132   | GPIO73                | RXD2        |            |            |  |

| 133   | VSS6                  |             |            |            |  |

| 134   | GPIO72                | TXD2        |            |            |  |

| 135   | GPIO138               | LCD_E       |            |            |  |

| 136   | GPIO71                | RTS1        |            |            |  |

| 137   | GPIO112               | PWM6        |            |            |  |

| 138   | GPIO70                | RI1         |            |            |  |

| 139   | GPIO155               |             |            |            |  |

| 140   | GPIO69                | DTR1        |            |            |  |

| 141   | GPIO163               | RXD4        |            |            |  |

| 142   | GPIO68                | DSR1        |            |            |  |

| 143   | GPIO113               | PWM7        |            |            |  |

| 144   | GPIO67                | DCD1        |            |            |  |

| 145   | GPIO139               | KEYPAD_COL1 |            |            |  |

| 146   | VDD10                 |             |            |            |  |

| 147   | GPIO45                |             |            |            |  |

| 148   | VSS7                  |             |            |            |  |

| 149   | GPIO140               | KEYPAD_COL2 |            |            |  |

| 150   | GPIO66                | CTS1        |            |            |  |

| 151   | GPIO114               | PWM8        |            |            |  |

| 152   | GPIO65                | RXD1        |            |            |  |

| 153   | GPIO39                |             |            |            |  |

| 154   | GPIO64                | TXD1        |            |            |  |

| 155   | GPIO141               | KEYPAD_COL3 |            |            |  |

| 156   | GPIO37                |             |            |            |  |

| 157   | GPIO44                |             |            |            |  |

| 158   | GPIO9                 | SPI_MOSI1   |            |            |  |

| 159   | GPIO142               | KEYPAD_COL4 |            |            |  |

| 160   | GPIO8                 | SPI_MISO1   |            |            |  |

| 161   | GPIO115               | PWM9        |            |            |  |

| 162   | GPIO7                 | SPI_SCK1    |            |            |  |

| 163   | GPIO43                |             |            |            |  |

| 164   | GPIO6                 | TMR_MAT2    |            |            |  |

| 165   | VDD11                 |             |            |            |  |

| 166   | GPIO5                 | CAN_TX1     |            |            |  |

| 167   | GPIO116               | PWM10       |            |            |  |

| 168   | GPIO4                 | CAN_RX1     |            |            |  |

| 169   | VSS8                  |             |            |            |  |

| 170   | GPIO156               | TXD3        |            |            |  |

| in # | Function 1 | Function 2   | Function 3 | Function 4 |

|------|------------|--------------|------------|------------|

| 171  | GPIO38     |              |            |            |

| 172  | VSS13      |              |            |            |

| 173  | GPIO143    | KEYPAD_COL5  |            |            |

| 174  | VDD3       |              |            |            |

| 175  | GPIO117    | PWM11        |            |            |

| 176  | GPIO157    | RXD3         |            |            |

| 177  | GPIO35     |              |            |            |

| 178  | GPIO49     | ETHER_MDIO   |            |            |

| 179  | GPIO153    | KEYPAD_ROW2  |            |            |

| 180  | GPIO48     | ETHER_MDC    |            |            |

| 181  | VDD12      |              |            |            |

| 182  | GPIO47     | ETHER_REFCLK |            |            |

| 183  | GPIO152    | KEYPAD_ROW1  |            |            |

| 184  | GPIO46     | ETHER_RXER   |            |            |

| 185  | GPIO34     |              |            |            |

| 186  | GPIO42     | ETHER_RXD1   |            |            |

| 187  | GPIO158    | KEYPAD_ROW3  |            |            |

| 188  | GPIO41     | ETHER_RXD0   |            |            |

| 189  | VSS9       |              |            |            |

| 190  | GPIO40     | ETHER_CRS    |            |            |

| 191  | GPIO104    |              |            |            |

| 192  | GPIO36     | ETHER_TXEN   |            |            |

| 193  | GPIO159    | KEYPAD_ROW4  |            |            |

| 194  | GPIO33     | ETHER_TXD1   |            |            |

| 195  | GPIO118    |              |            |            |

| 196  | GPIO32     | ETHER_TXD0   |            |            |

| 197  | GPIO96     |              |            |            |

| 198  | VDD13      |              |            |            |

| 199  | GPIO105    |              |            |            |

| 200  | VSS10      |              |            |            |

| 201  | GPIO97     |              |            |            |

| 202  | TXD0       |              |            |            |

| 203  | GPIO123    | PWM3         |            |            |

| 204  | RXD0       |              |            |            |

| 205  | GPIO106    |              |            |            |

| 206  | GPIO164    | TXD4         |            |            |

| 207  | GPIO98     |              |            |            |

| 208  | GPIO107    |              |            |            |

## 5. Pin Details

TABLE 2 lists details for each pins individual supported functions. Required pins and related pins are also listed.

| TABLE | 2 - Pin Details                                                                                                                       |

|-------|---------------------------------------------------------------------------------------------------------------------------------------|

| Pin # | Description                                                                                                                           |

| 1     | GPI108  General Purpose Digital I/O. May be configured as General Purpose Input 108 (GPI108) or General Purpose Output 108 (GPO108).  |

| 2     | Not Connected Do Not Connect this pin.                                                                                                |

| 3     | GPIO99 General Purpose Digital I/O. May be configured as General Purpose Input 99 (GPI99) or General Purpose Output 99 (GPO99).       |

| 4     | Not Connected Do Not Connect this pin.                                                                                                |

| 5     | GPIO124  General Purpose Digital I/O. May be configured as General Purpose Input 124 (GPI124) or General Purpose Output 124 (GPO124). |

|       | PWM4 Pulse Width Modulation Output 4 (PWM4).                                                                                          |

| 6     | Not Connected Do Not Connect this pin.                                                                                                |

| 7     | GPIO109  General Purpose Digital I/O. May be configured as General Purpose Input 109 (GPI109) or General Purpose Output 109 (GPO109). |

| 8     | Not Connected Do Not Connect this pin.                                                                                                |

| 9     | GPIO160 General Purpose Digital I/O. May be configured as General Purpose Input 160 (GPI160) or General Purpose Output 160 (GPO160).  |

| 10    | Not Connected Do Not Connect this pin.                                                                                                |

| 11    | GPIO125 General Purpose Digital I/O. May be configured as General Purpose Input 125 (GPI125) or General Purpose Output 125 (GPO125).  |

|       | PWM5 Pulse Width Modulation Output 5 (PWM5).                                                                                          |

| TABLE | 2 - Pin Details                                                                                                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin # | Description                                                                                                                                                                                         |

|       | GPIO26 General Purpose Digital I/O. May be configured as General Purpose Input 26 (GPI26) or General Purpose Output 26 (GPO26).                                                                     |

| 12    | Al3 Analog Input 3. Not to exceed 3.3VDC. Resolution: 12 bit. The following pins are required for Analog Input functionality: 20, 22, 24. Related Analog Input Pins: 41, 45, 18, 16, 14, 12, 42, 40 |

|       | AOO Analog Output 0. 3.3VDC Maximum Output. Resolution 10 bit. The following pins are required for Analog Output functionality: 20, 22.                                                             |

| 13    | GPIO100  General Purpose Digital I/O. May be configured as General Purpose Input 100 (GPI100) or General Purpose Output 100 (GPO100).                                                               |

| 1.4   | GPIO25 General Purpose Digital I/O. May be configured as General Purpose Input 25 (GPI25) or General Purpose Output 25 (GPO25).                                                                     |

| 14    | Al2 Analog Input 2. Not to exceed 3.3VDC. Resolution: 12 bit. The following pins are required for Analog Input functionality: 20, 22, 24. Related Analog Input Pins: 41, 45, 18, 16, 14, 12, 42, 40 |

| 15    | VDD4 Connect to 3.3VDC Supply. The recommended bypass capacitor must be installed near this pin (this pin to GND / 3.3V COMMON).                                                                    |

| 16    | GPIO24 General Purpose Digital I/O. May be configured as General Purpose Input 24 (GPI24) or General Purpose Output 24 (GPO24).                                                                     |

| 10    | Al1 Analog Input 1. Not to exceed 3.3VDC. Resolution: 12 bit. The following pins are required for Analog Input functionality: 20, 22, 24. Related Analog Input Pins: 41, 45, 18, 16, 14, 12, 42, 40 |

| 17    | GPIO101 General Purpose Digital I/O. May be configured as General Purpose Input 101 (GPI101) or General Purpose Output 101 (GPO101).                                                                |

| 18    | GPIO23 General Purpose Digital I/O. May be configured as General Purpose Input 23 (GPI23) or General Purpose Output 23 (GPO23).                                                                     |

| 10    | Alo Analog Input 0. Not to exceed 3.3VDC. Resolution: 12 bit. The following pins are required for Analog Input functionality: 20, 22, 24. Related Analog Input Pins: 41, 45, 18, 16, 14, 12, 42, 40 |

| 19    | GPIO126 General Purpose Digital I/O. May be configured as General Purpose Input 126 (GPI126) or General Purpose Output 126 (GPO126).                                                                |

| TABLE | 2 - Pin Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin # | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 20    | VDD_AN +V Power Supply for on-board analog circuitry. Connect to 3.3VDC supply. This pin can be connected to the same 3.3VDC logic supply for the PLC on a Chip™ or a separate supply as required to minimize noise and error. This pin is used to power the on-board ADC and DAC components. The recommended bypass capacitor must be installed near this pin (this pin to the VSS_AN pin). If the ADC and DAC are not used, this pin should be connected to 3.3VDC. The following pins are required for Analog Input functionality: 20, 22, 24. Related Analog Input Pins: 41, 45, 18, 16, 14, 12, 42, 40 |

| 21    | GPIO110  General Purpose Digital I/O. May be configured as General Purpose Input 110 (GPI110) or General Purpose Output 110 (GPO110).                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 22    | VSS_AN Analog Ground. OV Power Supply / Reference for the on-board ADC and DAC components. This should be the same potential as VSS (GND) or isolated as required to minimize noise and error. The following pins are required for Analog Input functionality: 20, 22, 24. Related Analog Input Pins: 41, 45, 18, 16, 14, 12, 42, 40                                                                                                                                                                                                                                                                        |

| 23    | GPIO102  General Purpose Digital I/O. May be configured as General Purpose Input 102 (GPI102) or General Purpose Output 102 (GPO102).                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 24    | VREF_AN On-board ADC Positive Reference Voltage. This should be the same voltage as VDD. It can be connected to VDD or isolated as required to minimize noise and error. The voltage level on this pin is used as a reference for the ADC and DAC. If the ADC and DAC are not used, this pin should be connected to 3.3VDC. The recommended bypass capacitor must be installed near this pin (this pin to the VSS_AN pin). The following pins are required for Analog Input functionality: 20, 22, 24. Related Analog Input Pins: 41, 45, 18, 16, 14, 12, 42, 40                                            |

| 25    | GPIO127 General Purpose Digital I/O. May be configured as General Purpose Input 127 (GPI127) or General Purpose Output 127 (GPO127).                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 26    | VDD1 Connect to 3.3VDC Supply. The recommended bypass capacitor must be installed near this pin (this pin to GND / 3.3V COMMON).                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 27    | GPIO103  General Purpose Digital I/O. May be configured as General Purpose Input 103 (GPI103) or General Purpose Output 103 (GPO103).                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 28    | GPIO111  General Purpose Digital I/O. May be configured as General Purpose Input 111 (GPI111) or General Purpose Output 111 (GPO111).                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 29    | RESTOUT  Reset Output. This pin is used to connect to other smart integrated circuits and provides the status of the PLC on a Chip™. When LOW, the PLC on a Chip™ is in the reset state.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Pin # | 2 - Pin Details  Description                                                                                                                                                                                                                                                                                                                                                           |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30    | GPIO161  General Purpose Digital I/O. May be configured as General Purpose Input 161 (GPI161) or General Purpose Output 161 (GPO161).                                                                                                                                                                                                                                                  |

| 31    | GPIO94 General Purpose Digital I/O. May be configured as General Purpose Input 94 (GPI94) or General Purpose Output 94 (GPO94).                                                                                                                                                                                                                                                        |

| 32    | VSS11 Connect to GND / 3.3V COMMON.                                                                                                                                                                                                                                                                                                                                                    |

| 33    | VSS1 Connect to GND / 3.3V COMMON.                                                                                                                                                                                                                                                                                                                                                     |

| 34    | RTXC1 Real Time Cloock Power Oscillator Circuit Input. Ultra-low power. 32KHz oscillator required. The following pins are required for Real Time Clock (RTC) functionality: 34, 36, 38. See Section 6.19 - Real Time Clock for details.                                                                                                                                                |

| 35    | RESET  Reset Input Pin. A Low on this pin places the PLC on a ChipTM in the reset state, causing all I/O and peripherals to return to their default states. This pin includes a 20 ns input glitch filter. This pin should be connected to an extenal power-on reset device.                                                                                                           |

| 36    | RTXC2  Real Time Cloock Power Oscillator Circuit Output. The following pins are required for Real Time Clock (RTC) functionality: 34, 36, 38. See Section 6.19 - Real Time Clock for details.                                                                                                                                                                                          |

| 37    | Not Connected Do Not Connect this pin.                                                                                                                                                                                                                                                                                                                                                 |

| 38    | VBAT  Real Time Cloock Power Supply (3.3V nominal). Voltage on this pin supplies power to the Real  Time Clock and provides a source of power to maintain RTC functionality when PLC on a Chip™ is not powered. If no RTC function is enabled (no battery), this pin should be connected to 3.3V. The following pins are required for Real Time Clock (RTC) functionality: 34, 36, 38. |

| 39    | GPIO95 General Purpose Digital I/O. May be configured as General Purpose Input 95 (GPI95) or General Purpose Output 95 (GPO95).                                                                                                                                                                                                                                                        |

| 40    | GPIO63  General Purpose Digital I/O. May be configured as General Purpose Input 63 (GPI63) or General Purpose Output 63 (GPO63).                                                                                                                                                                                                                                                       |

|       | A15 Analog Input 5. Not to exceed 3.3VDC. Resolution: 12 bit. The following pins are required for Analog Input functionality: 20, 22, 24. Related Analog Input Pins: 41, 45, 18, 16, 14, 12, 42, 40                                                                                                                                                                                    |

| TABLE | TABLE 2 - Pin Details                                                                                                                                                                                                      |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin # | Description                                                                                                                                                                                                                |  |

| 41    | GPIO12  General Purpose Digital I/O. May be configured as General Purpose Input 12 (GPI12) or General Purpose Output 12 (GPO12).                                                                                           |  |

|       | Al6 Analog Input 6. Not to exceed 3.3VDC. Resolution: 12 bit. The following pins are required for Analog Input functionality: 20, 22, 24. Related Analog Input Pins: 41, 45, 18, 16, 14, 12, 42, 40                        |  |

| 42    | GPIO62 General Purpose Digital I/O. May be configured as General Purpose Input 62 (GPI62) or General Purpose Output 62 (GPO62).                                                                                            |  |

| 42    | Al4 Analog Input 4. Not to exceed 3.3VDC. Resolution: 12 bit. The following pins are required for Analog Input functionality: 20, 22, 24. Related Analog Input Pins: 41, 45, 18, 16, 14, 12, 42, 40                        |  |

| 43    | GPIO93 General Purpose Digital I/O. May be configured as General Purpose Input 93 (GPI93) or General Purpose Output 93 (GPO93).                                                                                            |  |

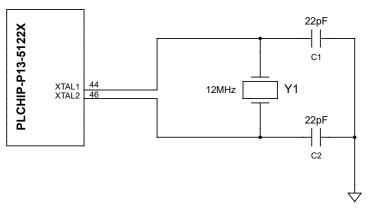

| 44    | XTAL1 Oscillator and internal clock generator circuit input. See Section 6.3 - Oscillator for details.                                                                                                                     |  |

| 45    | GPIO13 General Purpose Digital I/O. May be configured as General Purpose Input 13 (GPI13) or General Purpose Output 13 (GPO13).                                                                                            |  |

|       | Al7 Analog Input 7. Not to exceed 3.3VDC. Resolution: 12 bit. The following pins are required for Analog Input functionality: 20, 22, 24. Related Analog Input Pins: 41, 45, 18, 16, 14, 12, 42, 40                        |  |

| 46    | XTAL2 On-board Oscillator Amplifier output. See Section 6.3 - Oscillator for details.                                                                                                                                      |  |

| 47    | GPIO91 General Purpose Digital I/O. May be configured as General Purpose Input 91 (GPI91) or General Purpose Output 91 (GPO91).                                                                                            |  |

| 48    | GPIO28 General Purpose Digital I/O. May be configured as General Purpose Input 28 (GPI28) or General Purpose Output 28 (GPO28). Pin is Open Drain. When used as GPIO, a pull-up resistor is required for proper operation. |  |

| 70    | I2C_SCL0 I2C Port 0 Clock Line. This line is used to communicate to I2C devices. Pull-up resistors (1.4K Ohm) are required for proper operation. The following pins are required for Port 0 I2C functionality: 50, 48.     |  |

| 49    | GPIO92 General Purpose Digital I/O. May be configured as General Purpose Input 92 (GPI92) or General Purpose Output 92 (GPO92).                                                                                            |  |

| <b>TABLE</b> | TABLE 2 - Pin Details                                                                                                                                                                                                                                               |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin#         | Description                                                                                                                                                                                                                                                         |  |

| 50           | GPIO27 General Purpose Digital I/O. May be configured as General Purpose Input 27 (GPI27) or General Purpose Output 27 (GPO27). Pin is Open Drain. When used as GPIO, a pull-up resistor is required for proper operation.  I2C_SDA0                                |  |

|              | I <sup>2</sup> C Port 0 Data Line. This line is used to communicate to I <sup>2</sup> C devices. Pull-up resistors (1.4K Ohm) are required for proper operation. The following pins are required for Port 0 I <sup>2</sup> C functionality: <u>50</u> , <u>48</u> . |  |

| 51           | GPIO31 General Purpose Digital I/O. May be configured as General Purpose Input 31 (GPI31) or General Purpose Output 31 (GPO31).                                                                                                                                     |  |

| 52           | No Connect                                                                                                                                                                                                                                                          |  |

| 53           | GPIO88  General Purpose Digital I/O. May be configured as General Purpose Input 88 (GPI88) or General Purpose Output 88 (GPO88).                                                                                                                                    |  |

| 54           | GPIO89  General Purpose Digital I/O. May be configured as General Purpose Input 89 (GPI89) or General Purpose Output 89 (GPO89).                                                                                                                                    |  |

| 55           | GPIO122 General Purpose Digital I/O. May be configured as General Purpose Input 122 (GPI122) or General Purpose Output 122 (GPO122).                                                                                                                                |  |

|              | PWM2 Pulse Width Modulation Output 2 (PWM2).                                                                                                                                                                                                                        |  |

| 56           | GPIO121 General Purpose Digital I/O. May be configured as General Purpose Input 121 (GPI121) or General Purpose Output 121 (GPO121).                                                                                                                                |  |

|              | PWM1 Pulse Width Modulation Output 1 (PWM1).                                                                                                                                                                                                                        |  |

| 57           | GPIO90 General Purpose Digital I/O. May be configured as General Purpose Input 90 (GPI90) or General Purpose Output 90 (GPO90).                                                                                                                                     |  |

| 58           | GPIO120 General Purpose Digital I/O. May be configured as General Purpose Input 120 (GPI120) or General Purpose Output 120 (GPO120).                                                                                                                                |  |

|              | PWM0 Pulse Width Modulation Output 0 (PWM0).                                                                                                                                                                                                                        |  |

| 59           | GPIO82 General Purpose Digital I/O. May be configured as General Purpose Input 82 (GPI82) or General Purpose Output 82 (GPO82).                                                                                                                                     |  |

| TABLE 2 - Pin Details |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin #                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 60                    | VDD5 Connect to 3.3VDC Supply. The recommended bypass capacitor must be installed near this pin (this pin to GND / 3.3V COMMON).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 61                    | GPIO29 General Purpose Digital I/O. May be configured as General Purpose Input 29 (GPI29) or General Purpose Output 29 (GPO29). Note: GPIO29 and GPIO30 must both be input or output as a pair. One cannot be input while the other is an output.                                                                                                                                                                                                                                                                                                                                                                         |

| 62                    | GPIO30  General Purpose Digital I/O. May be configured as General Purpose Input 30 (GPI30) or General Purpose Output 30 (GPO30). Note: GPIO29 and GPIO30 must both be input or output as a pair. One cannot be input while the other is an output.                                                                                                                                                                                                                                                                                                                                                                        |

| 63                    | VSS2 Connect to GND / 3.3V COMMON.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 64                    | GPIO87 General Purpose Digital I/O. May be configured as General Purpose Input 87 (GPI87) or General Purpose Output 87 (GPO87).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 65                    | GPIO119  General Purpose Digital I/O. May be configured as General Purpose Input 119 (GPI119) or General Purpose Output 119 (GPO119).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 66                    | GPIO50 General Purpose Digital I/O. May be configured as General Purpose Input 50 (GPI50) or General Purpose Output 50 (GPO50).  TMR_CAP1.0 Capture input for Timer Module 1, Channel 0. Timer Module 1 supports two input pins: Channel 0 and Channel 1. Only one channel may be used as a timer capture pin in any Timer Module. This setting must match the configuration in EZ LADDER Toolkit. Based on the software configuration, either pin (when selected) will operate as a counter or will caculate the time/ frequency of pulses. The following pins are related for Timer Module 1 functionality: 66, 68, 74. |

| 67                    | GPIO83  General Purpose Digital I/O. May be configured as General Purpose Input 83 (GPI83) or General Purpose Output 83 (GPO83).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 68                    | GPIO51 General Purpose Digital I/O. May be configured as General Purpose Input 51 (GPI51) or General Purpose Output 51 (GPO51).  TMR_CAP1.1 Capture input for Timer Module 1, Channel 1. Timer Module 1 supports two input pins: Channel 0 and Channel 1. Only one channel may be used as a timer capture pin in any Timer Module. This setting must match the configuration in EZ LADDER Toolkit. Based on the software configuration, either pin (when selected) will operate as a counter or will caculate the time/frequency of pulses. The following pins are related for Timer Module 1 functionality: 66, 68, 74.  |

| TABLE | TABLE 2 - Pin Details                                                                                                                                                                                                                                                                                                                                                                                          |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin # | Description                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 69    | GPIO14 General Purpose Digital I/O. May be configured as General Purpose Input 14 (GPI14) or General Purpose Output 14 (GPO14).                                                                                                                                                                                                                                                                                |  |

| 70    | GPIO52 General Purpose Digital I/O. May be configured as General Purpose Input 52 (GPI52) or General Purpose Output 52 (GPO52).  QEI_PHA Qudrature Encoder Encoder Phase A (A Channel) input. The P13-Series supports an on-board quadrature encoder that provides inputs for Phase A, Phase B and Index. The following pins are required for on-board Quadrature Encoder Interface functionality: 70, 76, 78. |  |

| 71    | VDD6 Connect to 3.3VDC Supply. The recommended bypass capacitor must be installed near this pin (this pin to GND / 3.3V COMMON).                                                                                                                                                                                                                                                                               |  |

| 72    | GPIO53 General Purpose Digital I/O. May be configured as General Purpose Input 53 (GPI53) or General Purpose Output 53 (GPO53).                                                                                                                                                                                                                                                                                |  |

| 73    | GPIO84 General Purpose Digital I/O. May be configured as General Purpose Input 84 (GPI84) or General Purpose Output 84 (GPO84).                                                                                                                                                                                                                                                                                |  |

| 74    | GPIO54 General Purpose Digital I/O. May be configured as General Purpose Input 54 (GPI54) or General Purpose Output 54 (GPO54).  TMR_MAT1 NOTE 1 Timer/Capture Channel 1 Match output. This output is HIGH based on Timer/Capture Channel 1's configuration and when the captured or timed value equals a predetermined set point. The following pins are related for TMR_MAT1 functionality: 66, 68, 74.      |  |

| 75    | GPIO128 General Purpose Digital I/O. May be configured as General Purpose Input 128 (GPI128) or General Purpose Output 128 (GPO128).  LCD_DO Data 0 Line for LCD Display Port. Supports up to 4 Line, 20 Character Liquid Crystal Display (LCD). See LCD under Section 5: Functional Descriptions. The following pins are required for LCD functionality: 75, 79, 83, 97, 103, 107, 113, 121, 127, 131, 135    |  |

| 76    | GPIO55 General Purpose Digital I/O. May be configured as General Purpose Input 55 (GPI55) or General Purpose Output 55 (GPO55).  QEI_PHB Qudrature Encoder Encoder Phase B (B Channel) input. The P13-Series supports an on-board quadrature encoder that provides inputs for Phase A, Phase B and Index. The following pins are required for on-board Quadrature Encoder Interface functionality: 70, 76, 78. |  |

| 77    | VSS3 Connect to GND / 3.3V COMMON.                                                                                                                                                                                                                                                                                                                                                                             |  |

| Pin # Description |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 78                | GPIO56 General Purpose Digital I/O. May be configured as General Purpose Input 56 (GPI56) or General Purpose Output 56 (GPO56).                                                                                                                                                                                                                                                                                                                                                           |

|                   | QEI_IDX Qudrature Encoder Encoder Phase Index input. The P13-Series supports an on-board quadrature encoder that provides inputs for Phase A, Phase B and Index. The index input must be pulled high or low based on desired functionality if the connected encoder does not support the index channel. The following pins are required for on-board Quadrature Encoder Interface functionality: 70, 76, 78.                                                                              |

| 79                | GPIO129 General Purpose Digital I/O. May be configured as General Purpose Input 129 (GPI129) or General Purpose Output 129 (GPO129).                                                                                                                                                                                                                                                                                                                                                      |

|                   | LCD_D1  Data 1 Line for LCD Display Port. Supports up to 4 Line, 20 Character Liquid Crystal Display (LCD). See LCD under Section 5: Functional Descriptions. The following pins are required for LCD functionality: 75, 79, 83, 97, 103, 107, 113, 121, 127, 131, 135                                                                                                                                                                                                                    |

| 80                | GPIO57 General Purpose Digital I/O. May be configured as General Purpose Input 57 (GPI57) or General Purpose Output 57 (GPO57).                                                                                                                                                                                                                                                                                                                                                           |

| 81                | GPIO85 General Purpose Digital I/O. May be configured as General Purpose Input 85 (GPI85) or General Purpose Output 85 (GPO85).                                                                                                                                                                                                                                                                                                                                                           |

| 82                | GPIO58  General Purpose Digital I/O. May be configured as General Purpose Input 58 (GPI58) or General Purpose Output 58 (GPO58).                                                                                                                                                                                                                                                                                                                                                          |

|                   | TMR_CAP0.0  Capture input for Timer Module 0, Channel 0. Timer Module 0 supports two input pins: Channel 0 and Channel 1. Only one channel may be used as a timer capture pin in any Timer Module. This setting must match the configuration in EZ LADDER Toolkit. Based on the software configuration, either pin (when selected) will operate as a counter or will caculate the time/ frequency of pulses. The following pins are related for Timer Module 0 functionality: 82, 88, 90. |

| 83                | GPIO130 General Purpose Digital I/O. May be configured as General Purpose Input 130 (GPI130) or General Purpose Output 130 (GPO130).                                                                                                                                                                                                                                                                                                                                                      |

|                   | LCD_D2 Data 2 Line for LCD Display Port. Supports up to 4 Line, 20 Character Liquid Crystal Display (LCD). See LCD under Section 5: Functional Descriptions. The following pins are required for LCD functionality: 75, 79, 83, 97, 103, 107, 113, 121, 127, 131, 135                                                                                                                                                                                                                     |

| 84                | VSS12 Connect to GND / 3.3V COMMON.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TABLE 2 - Pin Details |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin #                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 85                    | GPIO86 General Purpose Digital I/O. May be configured as General Purpose Input 86 (GPI86) or General Purpose Output 86 (GPO86).                                                                                                                                                                                                                                                                                                                                                           |

| 86                    | VDD2 Connect to 3.3VDC Supply. The recommended bypass capacitor must be installed near this pin (this pin to GND / 3.3V COMMON).                                                                                                                                                                                                                                                                                                                                                          |

| 87                    | GPIO80  General Purpose Digital I/O. May be configured as General Purpose Input 80 (GPI80) or General Purpose Output 80 (GPO80).                                                                                                                                                                                                                                                                                                                                                          |

|                       | GPIO59  General Purpose Digital I/O. May be configured as General Purpose Input 59 (GPI59) or General Purpose Output 59 (GPO59).                                                                                                                                                                                                                                                                                                                                                          |

| 88                    | TMR_CAP0.1 Capture input for Timer Module 0, Channel 1. Timer Module 0 supports two input pins: Channel 0 and Channel 1. Only one channel may be used as a timer capture pin in any Timer Module. This setting must match the configuration in EZ LADDER Toolkit. Based on the software configuration, either pin (when selected) will operate as a counter or will caculate the time/frequency of pulses. The following pins are related for Timer Module 0 functionality: 82, 88, 90.   |

| 89                    | VDD7 Connect to 3.3VDC Supply. The recommended bypass capacitor must be installed near this pin (this pin to GND / 3.3V COMMON).                                                                                                                                                                                                                                                                                                                                                          |

|                       | GPIO60 General Purpose Digital I/O. May be configured as General Purpose Input 60 (GPI60) or General Purpose Output 60 (GPO60).                                                                                                                                                                                                                                                                                                                                                           |

| 90                    | TMR_MATO NOTE 1 Timer/Capture Channel 0 Match output. This output is HIGH based on Timer/Capture Channel 0's configuration and when the captured or timed value equals a predetermined set point. The following pins are related for TMR_MATO functionality: 82, 88, 90.                                                                                                                                                                                                                  |

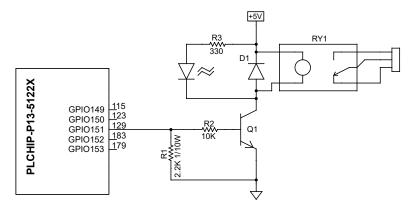

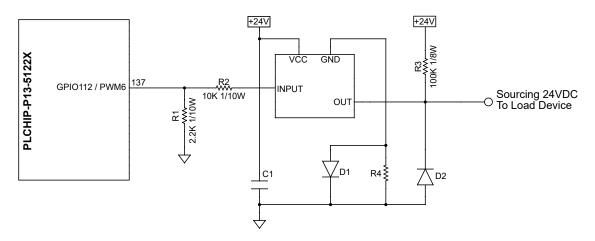

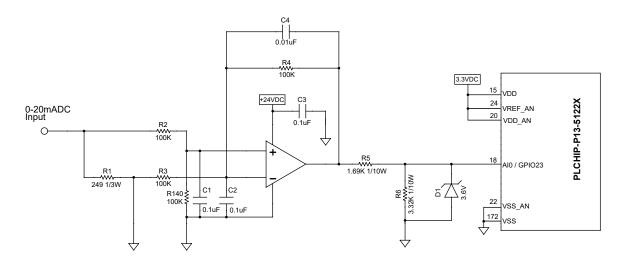

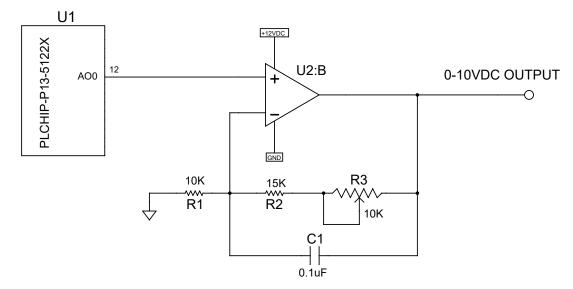

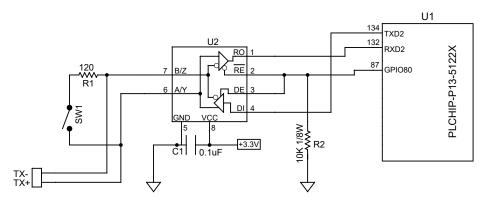

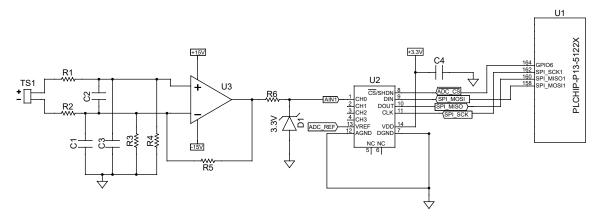

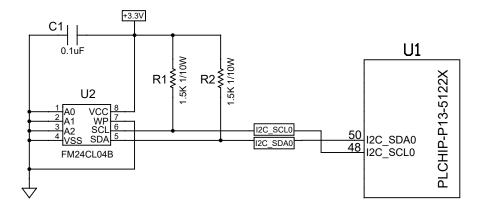

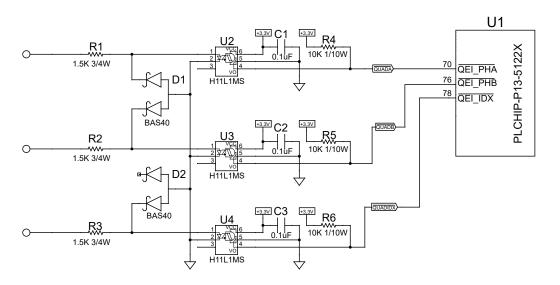

| 91                    | GPIO78  General Purpose Digital I/O. May be configured as General Purpose Input 78 (GPI78) or General Purpose Output 78 (GPO78).                                                                                                                                                                                                                                                                                                                                                          |