# onsemi

# Power Ballast and Dual LED Driver for Automotive Front Lighting 2<sup>nd</sup> Generation NCV78763

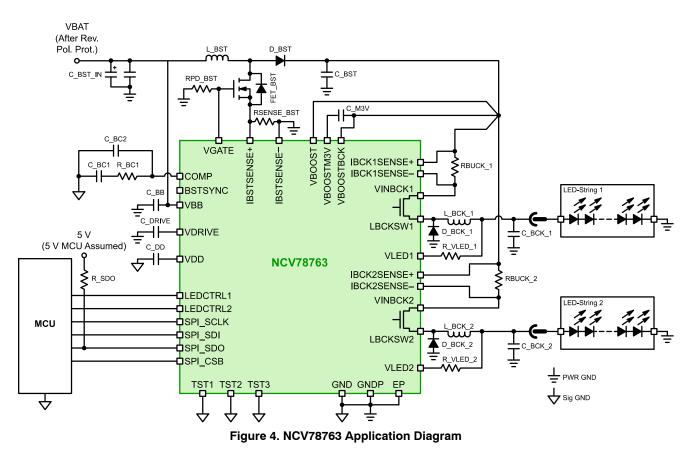

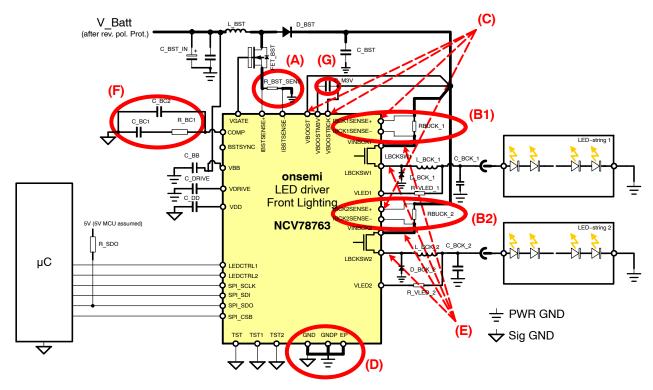

The NCV78763 is a single-chip and high efficient smart Power ballast and Dual LED DRIVER designed for automotive front lighting applications like high beam, low beam, daytime running light (DRL), turn indicator, fog light, static cornering and so on.

The NCV78763 is a best fit for high current LEDs and provides a complete solution to drive two strings up to 60 V, by means of two internal independent buck switch channel outputs, with a minimum of external components. For each individual LED channel, the output current and voltage can be customized according to the application requirements. An on-chip diagnostic feature for automotive front lighting is provided, easing the safety monitoring from the microcontroller. The device integrates a current-mode voltage booster controller, realizing a unique input current filter with a limited BOM.

When more than two LED channels are required on one module, then two, three or more NCV78763 devices can be combined, with the possibility for the booster circuits to operate in multiphase-mode. This helps to further optimize the filtering effect of the booster circuit and allows a cost effective dimensioning for mid to high power LED systems.

Due to the SPI programmability, one single hardware setup can support multiple system configurations for a flexible platform solution approach.

# Features

- Single Chip Boost-Buck Solution

- Two LED Strings up to 60 V

- High Current Capability up to 1.6 A DC per Output

- High Overall System Efficiency

- Minimum of External Components

- Active Input Filter with Low Current Ripple from Battery

- Integrated Switched Mode Buck Current Regulator

- Integrated Boost Current-mode Controller

- Programmable Input Current Limitation

- Average Current Regulation Through the LEDs

- High Operating Frequencies to Reduce Inductor Sizes

- Integrated PWM Dimming with Wide Frequency Range

- Low EMC Emission for LED switching and dimming

- SPI Interface for Dynamic Control of System Parameters

- Please Look Further in the Document for the NV78763–9 Device Regarding its New Features

- These are Pb–Free Devices

# **Typical Applications**

- Front Lighting High Beam and Low Beam

- Day time Running Light (DRL)

- Position or Park light

- Turn Indicator

- Fog Light and Static Cornering

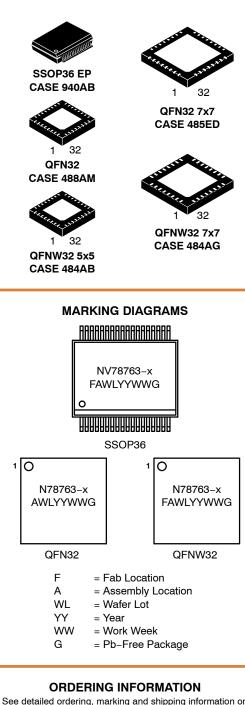

See detailed ordering, marking and shipping information on page 46 of this data sheet.

1

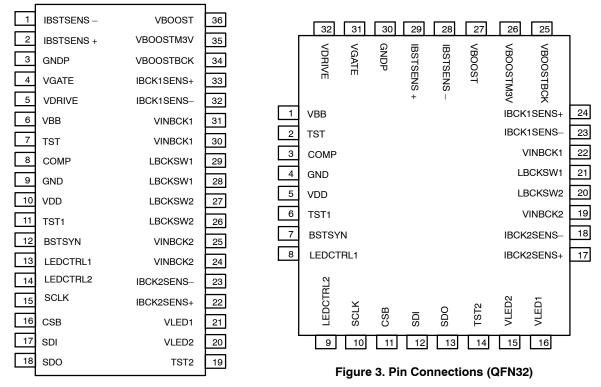

Figure 2. Pin Connections (SSOP36 EP)

# Table 1. PIN DESCRIPTION

| Pin No.<br>SSOP36-EP | Pin No.<br>QFN32 | Pin Name    | Function                                | I/O Type        |

|----------------------|------------------|-------------|-----------------------------------------|-----------------|

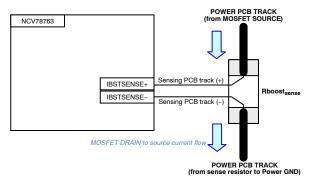

| 1                    | 28               | IBSTSENSE-  | Battery current negative feedback input | LV in/out       |

| 2                    | 29               | IBSTSENSE+  | Battery current positive feedback input | LV in/out       |

| 3                    | 30               | GNDP        | Power ground                            | Ground          |

| 4                    | 31               | VGATE       | Booster MOSFET gate pre-driver          | MV out          |

| 5                    | 32               | VDRIVE      | 10V supply                              | MV supply       |

| 6                    | 1                | VBB         | Battery supply                          | HV supply       |

| 7                    | 2                | TST         | Internal function. To be tied to GND.   | LV in/out       |

| 8                    | 3                | COMP        | Compensation for the Boost regulator    | LV in/out       |

| 9                    | 4                | GND         | Ground                                  | Ground          |

| 10                   | 5                | VDD         | 3V logic supply                         | LV supply       |

| 11                   | 6                | TST1        | Internal function. To be tied to GND.   | LV in/out       |

| 12                   | 7                | BSTSYN      | External clock for the boost regulator  | MV in           |

| 13                   | 8                | LEDCTRL1    | LED string 1 enable                     | MV in           |

| 14                   | 9                | LEDCTRL2    | LED string 2 enable                     | MV in           |

| 15                   | 10               | SCLK        | SPI clock                               | MV in           |

| 16                   | 11               | CSB         | SPI chip select (chip select bar)       | MV in           |

| 17                   | 12               | SDI         | SPI data input                          | MV in           |

| 18                   | 13               | SDO         | SPI data output                         | MV open-drain   |

| 19                   | 14               | TST2        | Internal function. To be tied to GND.   | LV in/out       |

| 20                   | 15               | VLED2       | LED string 2 forward voltage input      | HV in           |

| 21                   | 16               | VLED1       | LED string 1 forward voltage input      | HV in           |

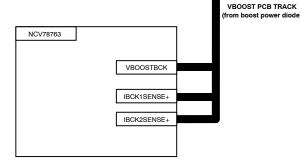

| 22                   | 17               | IBCK2SENSE+ | Buck 2 positive sense input             | HV in           |

| 23                   | 18               | IBCK2SENSE- | Buck 2 negative sense input             | HV in           |

| 24                   | 19               | VINBCK2     | Buck 2 high voltage supply              | HV in           |

| 25                   | Х                | VINBCK2     | Buck 2 high voltage supply              | HV in           |

| 26                   | 20               | LBCKSW2     | Buck 2 switch output                    | HV out          |

| 27                   | Х                | LBCKSW2     | Buck 2 switch output                    | HV out          |

| 28                   | 21               | LBCKSW1     | Buck 1 switch output                    | HV out          |

| 29                   | Х                | LBCKSW1     | Buck 1 switch output                    | HV out          |

| 30                   | 22               | VINBCK1     | Buck 1 high voltage supply              | HV in           |

| 31                   | Х                | VINBCK1     | Buck 1 high voltage supply              | HV in           |

| 32                   | 23               | IBCK1SENSE- | Buck 1 negative sense input             | HV in           |

| 33                   | 24               | IBCK1SENSE+ | Buck 1 positive sense input             | HV in           |

| 34                   | 25               | VBOOSTBCK   | High voltage for the BUCK switches      | HV supply       |

| 35                   | 26               | VBOOSTM3V   | VBOOST-3V regulator output              | HV out (supply) |

| 36                   | 27               | VBOOST      | Boost voltage feedback input            | HV in           |

Note A: as reported in the application diagram, the device pins TST, TST2 & TST1 must be connected to the signal ground GND. Note B: external capacitors or RC may be added to these SPI lines for stable communication in case of application noise. The selection of these components must be done so that the resulting waveforms are respecting the limits reported in Table 19. Note C: recommended values for the external MOSFET pull down resistor RPD\_BST range from 10 k $\Omega$  to 33 k $\Omega$ . Note D: the minimum value for the LED feedback resistors R\_VLED\_1 and R\_VLED\_2 is 1 k $\Omega$ .

### **Table 2. ABSOLUTE MAXIMUM RATINGS**

| Characteristic                                                                    | Symbol                    | Min       | Мах       | Unit |

|-----------------------------------------------------------------------------------|---------------------------|-----------|-----------|------|

| Battery Supply voltage (Note 1)                                                   | V <sub>BB</sub>           | -0.3      | 60        | V    |

| LED supply voltage (Note 2)                                                       | V <sub>BOOST</sub>        | -0.3      | 68        | V    |

| Logic Supply voltage (Note 3)                                                     | V <sub>DD</sub>           | -0.3      | 3.6       | V    |

| MOSFET Gate driver supply voltage (Note 4)                                        | V <sub>DRIVE</sub>        | -0.3      | 12        | V    |

| Input current sense voltage pins                                                  | IBSTSENSE+,<br>IBSTSENSE- | -1.0      | 12        | V    |

| Medium voltage IO pins (Note 5)                                                   | IOMV                      | -0.3      | 7.0       | V    |

| Relative voltage IO pins (Note 6)                                                 | ΔV_IO                     | VBOOSTM3V | VBOOSTBCK | V    |

| Buck switch low side (Note 7)                                                     | LBCKSW1,<br>LBCKSW2       | -2.0      | VBOOSTBCK | V    |

| Current into or out of the VLED pin                                               | I <sub>VLEDpin</sub>      | -30       | 30        | mA   |

| Series resistor on the VLED pin                                                   | R <sub>VLEDx</sub>        | 1         |           | kΩ   |

| Storage Temperature (Note 8)                                                      | T <sub>strg</sub>         | -50       | 150       | °C   |

| Lead Temperature Soldering Reflow (SMD Styles Only), Pb-Free<br>Versions (Note 9) | T <sub>SLD</sub>          |           | 260       | °C   |

| Electrostatic discharge on component level (Note 10)                              | V <sub>ESD</sub>          | -2        | +2        | kV   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. Absolute maximum rating for pin VBB.

- 2. Absolute maximum rating for pins: VBOOST, VBOOSTM3V, IBCK1SENSE+, IBCK1SENSE-, VINBCK1, VLED1, IBCK2SENSE+, IBCK2SENSE-, VINBCK2, VLED2.

- 3. Absolute maximum rating for pins: VDD, TEST1, TEST2, COMP.

- 4. Absolute maximum rating for pins: VDRIVE, VGATE.

- 5. Absolute maximum rating for pins: SCLK, CSB, SDI, SDO, LEDCTRL1, LEDCTRL2, BSTSYNC. The device tolerates 5 V coming from the external logics (MCU) when in off state.

- 6. Relative maximum rating for pins: VINBCK1, VINBCK2, IBCK1SENSE+, IBCK2SENSE+, IBCK1SENSE-, IBCK2SENSE-,

- 7. Requirement: V(VINBCKx LBCKSWx) < 70 V.

- 8. For limited time up to 100 hours, otherwise the max. storage temperature < 85°C.

- 9. For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

- 10. This device series incorporates ESD protection and is tested by the following methods:

- ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114)

- ESD Machine Model tested per AEC-Q100-003 (EIA/JESD22-A115)

- Latch-up Current Maximum Rating: ≤150 mA per JEDEC standard: JESD78

# **Table 3. RECOMMENDED OPERATING RANGES**

The recommended operating ranges define the limits for functional operation and parametric characteristics of the device. Note that the functionality of the device outside the operating ranges described in this section is not warranted. Operating outside the recommended operating ranges for extended periods of time may affect device reliability. A mission profile (Note 11) is a substantial part of the operation conditions; hence the Customer must contact onsemi in order to mutually agree in writing on the allowed missions profile(s) in the application.

| Characteristic                                      | Symbol                 | Min | Max | Unit |

|-----------------------------------------------------|------------------------|-----|-----|------|

| Battery Supply voltage                              | V <sub>BB</sub>        | 4   | 40  | V    |

| Gate driver supply current (Note 12)                | IDRIVE                 |     | 40  | mA   |

| Functional operating junction temperature (Note 13) | T <sub>JF</sub>        | -45 | 155 | °C   |

| Parametric operating junction temperature range     | T <sub>JP</sub>        | -40 | 150 | °C   |

| Buck switch output current peak                     | I <sub>LBUCKpeak</sub> |     | 1.9 | А    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

11. The parametric characteristics of the circuit are not guaranteed outside the Parametric operating junction temperature range. A mission profile describes the application specific conditions such as, but not limited to, the cumulative operating conditions over life time, the system power dissipation, the system's environmental conditions, the thermal design of the customer's system, the modes, in which the device is operated by the customer, etc.

12.1<sub>DRIVE</sub> = Q<sub>Tgate x</sub> F<sub>BOOST</sub> (external MOSFET total gate charge multiplied by booster driving frequency). 13. The circuit functionality is not guaranteed outside the functional operating junction temperature range. The maximum functional operating range can be limited by thermal shutdown "Tsd" (ADC Tsd, see Table 10). Also please note that the device is verified on bench for operation up to 170°C but that the production test guarantees 155°C only.

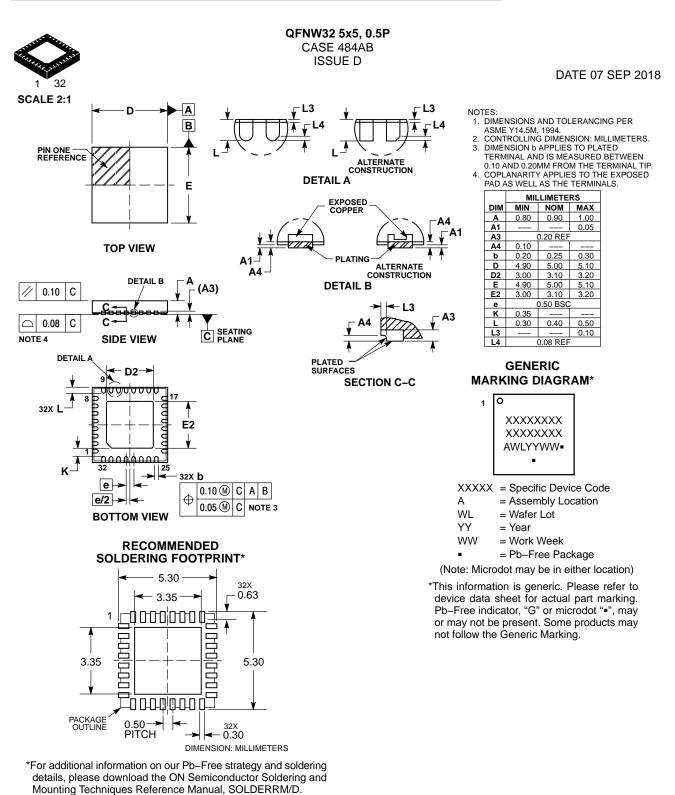

# Table 4. THERMAL RESISTANCE

| Characteristic                                      | Package   | Symbol | Value | Unit |

|-----------------------------------------------------|-----------|--------|-------|------|

| Thermal resistance package to Exposed Pad (Note 14) | SSOP36-EP | θJcbot | 3.5   | °C/W |

| Thermal resistance package to Exposed Pad (Note 14) | QFN32 7x7 | θJcbot | 3.4   | °C/W |

| Thermal resistance package to Exposed Pad (Note 14) | QFN32 5x5 | θJcbot | 3.4   | °C/W |

14. Includes also typical solder thickness under the Exposed Pad (EP).

**ELECTRICAL CHARACTERISTICS** NOTE: Unless differently specified, all device Min and Max parameters boundaries are given for the full supply operating ranges and junction temperature ( $T_{JP}$ ) range ( $-40^{\circ}C$ ;  $+150^{\circ}C$ ).

# Table 5. VBB: BATTERY SUPPLY INPUT

| Characteristic                    | Symbol            | Conditions                                            | Min | Тур | Max | Unit |

|-----------------------------------|-------------------|-------------------------------------------------------|-----|-----|-----|------|

| Nominal Operating<br>Supply Range | V <sub>BB</sub>   |                                                       | 5   |     | 40  | V    |

| Device Current<br>Consumption     | I <sub>BB_0</sub> | buck regulators off, gate drive off, outputs unloaded |     |     | 8   | mA   |

### Table 6. VDRIVE: SUPPLY FOR BOOSTER MOSFET GATE DRIVE CIRCUIT

| Characteristic                                           | Symbol                   | Con                                                                          | ditions                        | Min | Тур  | Max  | Unit |

|----------------------------------------------------------|--------------------------|------------------------------------------------------------------------------|--------------------------------|-----|------|------|------|

| VDRIVE reg. voltage                                      | V <sub>DRV_BB_15</sub>   | V <sub>BB</sub> – V <sub>DRIVE</sub> > 1.65 V<br>@I <sub>DRIVE</sub> = 25 mA | VDRIVE_SETPOINT[3:0] =<br>1111 | 9.7 | 10.1 | 10.7 | V    |

| from VBB (Note 15)                                       | V <sub>DRV_BB_00</sub>   | V <sub>BB</sub> – V <sub>DRIVE</sub> > 1.65 V<br>@I <sub>DRIVE</sub> = 25 mA | VDRIVE_SETPOINT[3:0] =         | 4.8 | 5    | 5.3  | V    |

| VDRIVE from VBB<br>increase per code<br>(Note 15)        | $\Delta V_{DRV_{BB}}$    | Linear increase, 4Bits                                                       |                                |     | 0.34 |      | V    |

| VDRIVE reg. voltage<br>from VBOOST                       | V <sub>DRV_BST_15</sub>  | V <sub>BOOST</sub> - V <sub>DRIVE</sub> > 3 V<br>@I <sub>DRIVE</sub> = 40 mA | VDRIVE_SETPOINT[3:0] =<br>1111 | 9.5 | 10.1 | 10.7 | V    |

| (Note 15)                                                | V <sub>DRV_BST_00</sub>  | $V_{BOOST} - V_{DRIVE} > 3 V$<br>@I <sub>DRIVE</sub> = 40 mA                 | VDRIVE_SETPOINT[3:0] =<br>0000 | 4.7 | 5    | 5.3  | V    |

| VDRIVE from<br>VBOOST increase per<br>code (Note 15)     | $\Delta_{\rm VDRV\_BST}$ | Linear inc                                                                   | crease, 4 Bits                 |     | 0.34 |      | V    |

| VDRIVE Output<br>current limitation from<br>VBB input    | V <sub>DRV_BB_IL</sub>   |                                                                              |                                | 40  |      | 400  | mA   |

| VDRIVE Output<br>current limitation from<br>VBOOST input | V <sub>DRV_BB_IL</sub>   |                                                                              |                                | 40  |      | 200  | mA   |

| VDRIVE decoupling<br>capacitor                           | C <sub>VDRIVE</sub>      |                                                                              |                                |     | 470  |      | nF   |

| VDRIVE decoupling<br>capacitor ESR                       | C <sub>VDRIVE_ESR</sub>  |                                                                              |                                |     |      | 100  | mΩ   |

15. The VDRIVE voltage setpoint is in the same range if the current is either provided by VBB or VBOOST pin. The voltage headroom between VBB and VDRIVE or VDRIVE and VBOOST needs to be sufficient. For what concerns VDRIVE from VBB, in case of 25 mA current, the worst case headroom is 1.65V. The VBOOST\_AUX regulator can be enabled by SPI (bit VDRIVE\_BST\_EN[0]).

# Table 7. VDD: 3V LOW VOLTAGE ANALOG AND DIGITAL SUPPLY

| Characteristic                                      | Symbol                 | Conditions            | Min  | Тур  | Max  | Unit |

|-----------------------------------------------------|------------------------|-----------------------|------|------|------|------|

| VBB to VDD switch disconnection                     | V <sub>BB_LOW</sub>    |                       | 3.65 |      | 3.9  | V    |

| VDD regulator output voltage                        | V <sub>DD</sub>        | V <sub>BB</sub> > 4 V | 3.15 |      | 3.4  | V    |

| DC total current<br>consumption including<br>output | V <sub>DD_IOUT</sub>   | V <sub>BB</sub> > 4 V |      |      | 15   | mA   |

| DC current limitation                               | V <sub>DD_ILIM</sub>   | V <sub>BB</sub> > 4 V | 15   |      | 240  | mA   |

| VDD external decoupling cap.                        | C <sub>VDD</sub>       |                       | 0.3  | 0.47 | 2.2  | μF   |

| VDD ext. decoupling cap. ESR                        | C <sub>VDD_ESR</sub>   |                       |      |      | 200  | mΩ   |

| POR Toggle level on<br>VDD rising                   | POR <sub>3V_H</sub>    |                       | 2.7  |      | 3.05 | V    |

| POR Toggle level on<br>VDD falling                  | POR <sub>3V_L</sub>    |                       | 2.45 |      | 2.8  | V    |

| POR Hysteresis                                      | POR <sub>3V_HYST</sub> |                       |      | 0.2  |      | V    |

# Table 8. VBOOSTM3: HIGH SIDE MOSFETS AUXILIARY SUPPLY

| Characteristic                                                 | Symbol                   | Conditions | Min  | Тур  | Max  | Unit |

|----------------------------------------------------------------|--------------------------|------------|------|------|------|------|

| VBSTM3 regulator<br>output voltage                             | V <sub>BSTM3</sub>       |            | -3.6 | -3.3 | -3.0 | V    |

| VBSTM3 DC output<br>current consumption                        | V <sub>BSTM3_IOUT</sub>  |            |      | 5    |      | mA   |

| VBSTM3 DC output<br>current consumption<br>on NV78763–9 device | V <sub>BSTM3</sub> LIOUT |            |      | 30   |      | mA   |

| VBSTM3 Output<br>current limitation                            | V <sub>BSTM3_ILIM</sub>  |            |      |      | 200  | mA   |

| VBSTM3 external decoupling capacitor                           | C <sub>VBSTM3</sub>      |            | 0.3  | 0.47 | 2.2  | μF   |

| VBSTM3 external decoupling cap. ESR                            | C <sub>VBSTM3_ESR</sub>  |            |      |      | 200  | mΩ   |

# Table 9. OSC8M: SYSTEM OSCILLATOR CLOCK

| Characteristic                 | Symbol | Conditions                    |     | Тур | Max | Unit |

|--------------------------------|--------|-------------------------------|-----|-----|-----|------|

| System oscillator<br>frequency | FOSC8M | After device factory trimming | 7.1 | 8.0 | 8.9 | MHz  |

# Table 10. ADC FOR MEASURING VBOOST, VBB, VLED1, VLED2, VTEMP

| Characteristic                                                        | Symbol                   | Conditions | Min   | Тур | Max  | Unit |

|-----------------------------------------------------------------------|--------------------------|------------|-------|-----|------|------|

| ADC Resolution                                                        | ADC <sub>RES</sub>       |            |       | 8   |      | Bits |

| Integral Nonlinearity<br>(INL)                                        | ADC <sub>INL</sub>       |            | -1.5  |     | +1.5 | LSB  |

| Differential<br>Nonlinearity (DNL)                                    | ADC <sub>DNL</sub>       |            | -2.0  |     | +2.0 | LSB  |

| Full path gain error for<br>measurements via<br>VBB, VLEDx,<br>VBOOST | ADC <sub>GAINERR</sub>   |            | -3.25 |     | 3.25 | %    |

| Offset at output of ADC                                               | ADC <sub>OFFSET</sub>    |            | -2    |     | 2    | LSB  |

| Time for 1 SAR conversion                                             | ADC <sub>CONV_TIME</sub> |            |       | 8   |      | μs   |

# Table 10. ADC FOR MEASURING VBOOST, VBB, VLED1, VLED2, VTEMP (continued)

| Characteristic                                                     | Symbol                 | Conditions | Min | Тур  | Max | Unit |

|--------------------------------------------------------------------|------------------------|------------|-----|------|-----|------|

| ADC full scale for VBB measurement                                 | ADC <sub>FS_VBB</sub>  |            |     | 39.7 |     | V    |

| ADC full scale for<br>VLED                                         | ADC <sub>FS_VLED</sub> |            |     | 69.5 |     | V    |

| ADC full scale for<br>Vboost                                       | $ADC_{FS_VBST}$        |            |     | 69.5 |     | V    |

| ADC internal<br>temperature<br>measurement for<br>thermal shutdown | ADC <sub>TSD</sub>     |            | 163 | 169  | 175 | °C   |

| VLED input impedance                                               | VLED <sub>R_IN</sub>   |            | 255 |      | 710 | kΩ   |

## Table 11. BOOSTER CONTROLLER – VOLTAGE REGULATION PARAMETERS

| Characteristic                                            | Symbol      | Conditions                                                   | SPI Setting                    | Min  | Тур   | Max     | Unit |

|-----------------------------------------------------------|-------------|--------------------------------------------------------------|--------------------------------|------|-------|---------|------|

|                                                           | BST_OV_07   | $\Delta V$ to the reg. level, DC level                       | [BOOST_OV_SD = 111]            | 5.3  | 5.8   | 6.3     | V    |

|                                                           | BST_OV_06   | $\Delta V$ to the reg. level, DC level                       | [BOOST_OV_SD = 110]            | 4.3  | 4.85  | 5.3     | V    |

|                                                           | BST_OV_05   | $\Delta V$ to the reg. level, DC level                       | [BOOST_OV_SD = 101]            | 3.4  | 3.9   | 4.3     | V    |

| Booster overvoltage                                       | BST_OV_04   | $\Delta V$ to the reg. level, DC level                       | [BOOST_OV_SD = 100]            | 2.4  | 2.9   | 3.3     | V    |

| shutdown (Note 16)                                        | BST_OV_03   | $\Delta V$ to the reg. level, DC level                       | [BOOST_OV_SD = 011]            | 1.9  | 2.4   | 2.8     | V    |

|                                                           | BST_OV_02   | $\Delta V$ to the reg. level, DC level                       | [BOOST_OV_SD = 010]            | 1.5  | 2     | 2.3     | V    |

|                                                           | BST_OV_01   | $\Delta V$ to the reg. level, DC level                       | [BOOST_OV_SD = 001]            | 1.2  | 1.5   | 1.8     | V    |

|                                                           | BST_OV_00   | $\Delta V$ to the reg. level, DC level                       | [BOOST_OV_SD = 000]            | 0.6  | 1     | 1.3     | V    |

| Booster overvoltage<br>shutdown increase per<br>code      | ∆BST_OV     | Linear increase, 2 bits,<br>DC level                         |                                |      | 0.5/1 | 0.6/1.2 | V    |

| Booster overvoltage<br>re-activation                      | BST_RA_3    | ΔV to the VBOOST reg.<br>overvoltage protection,<br>DC level | [BOOST_OV_REACT = 11]          | -1.8 | -1.4  | -1      | V    |

| Booster overvoltage<br>re-activation                      | BST_RA_0    | ΔV to the VBOOST reg.<br>overvoltage protection,<br>DC level | [BOOST_OV_REACT = 00]          |      | 0     |         | V    |

| Booster overvoltage<br>re-activation decrease<br>per code | ∆BST_RA     | Linear decrease, 2 bits,<br>DC level                         |                                | -0.6 | -0.5  |         | V    |

| VBOOST undervoltage<br>shutdown on<br>NV78763-9 device    | BST_UV_THR  |                                                              |                                | 1.17 | 1.215 | 1.26    | V    |

|                                                           | BST_REG_127 | DC level                                                     | [BOOST_VSETPOINT =<br>1111111] | 62.8 | 64.1  | 66      | V    |

| Booster regulation setpoint voltage                       | BST_REG_001 | DC level                                                     | [BOOST_VSETPOINT = 0000001]    | 14.4 | 15    | 15.6    | V    |

|                                                           | BST_REG_000 | DC level                                                     | [BOOST_VSETPOINT =<br>0000000] | 10.5 | 11    | 11.5    | V    |

| Booster regulation<br>setpoint increase step<br>per code  | ∆BST_REG    | Linear increase, 7 bits                                      |                                |      | 0.39  | 0.55    | V    |

# Table 11. BOOSTER CONTROLLER – VOLTAGE REGULATION PARAMETERS

| Characteristic                                                                 | Symbol               | Conditions                                                                 | SPI Setting                                    | Min | Тур             | Max  | Unit |

|--------------------------------------------------------------------------------|----------------------|----------------------------------------------------------------------------|------------------------------------------------|-----|-----------------|------|------|

|                                                                                | EA_Gm_3              | Seen from VBOOST pin<br>input, DC value                                    | [BOOST_OTA_GAIN = 11]                          | 63  | 90              | 117  | μS   |

| Booster Error Amplifier                                                        | EA_Gm_2              | Seen from VBOOST pin<br>input, DC value                                    | [BOOST_OTA_GAIN = 10]                          | 42  | 60              | 78   | μS   |

| (EA)<br>Trans–conductance<br>Gain G <sub>m</sub>                               | EA_Gm_1              | Seen from VBOOST pin<br>input, DC value                                    | [BOOST_OTA_GAIN = 01]                          | 21  | 30              | 39   | μS   |

|                                                                                | EA_ <sub>Gm_0</sub>  | Seen from VBOOST pin<br>input, High impedance<br>tri-state                 | [BOOST_OTA_GAIN = 00]                          |     | 0               |      | μS   |

|                                                                                | EA_lout_pos_max_03   | EA_ <sub>Gm_03</sub> is set                                                | [BOOST_OTA_GAIN = 11]                          | 150 | 180             |      | μA   |

| EA max output current<br>(positive/source)                                     | EA_lout_pos_max_02   | EA_ <sub>Gm_02</sub> is set                                                | [BOOST_OTA_GAIN = 10]                          | 100 | 120             |      | μA   |

| u , ,                                                                          | EA_lout_pos_max_01   | EA_ <sub>Gm_01</sub> is set                                                | [BOOST_OTA_GAIN = 01]                          | 50  | 60              |      | μA   |

|                                                                                | EA_lout_neg_max_03   | EA_ <sub>Gm_03</sub> is set                                                | [BOOST_OTA_GAIN = 11]                          |     | -180            | -150 | μΑ   |

| EA max output current<br>(negative/sink)                                       | EA_lout_neg_max_02   | EA_ <sub>Gm_02</sub> is set                                                | [BOOST_OTA_GAIN = 10]                          |     | -120            | -100 | μΑ   |

| (nogativo/onity                                                                | EA_lout_neg_max_01   | EA_ <sub>Gm_01</sub> is set                                                | [BOOST_OTA_GAIN = 01]                          |     | -60             | -50  | μA   |

| EA max output<br>leakage current in<br>tri-state                               | EA_lout_leak         | EA <sub>Gm 00</sub> is set (EA<br>disabled, high impedance<br>tri–state)   | [BOOST_OTA_GAIN = 00]                          | -1  |                 | 1    | μΑ   |

| EA equivalent output resistance                                                | EA_ <sub>ROUT</sub>  |                                                                            |                                                | 0.7 |                 | 2.9  | MΩ   |

|                                                                                | COMP_CLH3            | (BST_SLPCTRL_3 or<br>BST_SLPCTRL_2) &<br>(BST_VLIMTH_3 or<br>BST_VLIMTH_2) | [BOOST_SLP_CTRL = 1x] &<br>[BOOST_VLIMTH = 1x] | 2.1 | 2.26            |      | V    |

| EA max output voltage                                                          | COMP_CLH2            | BST_SLPCTRL_3 or<br>BST_SLPCTRL_2) &<br>(BST_VLIMTH_1 or<br>BST_VLIMTH_0)  | [BOOST_SLP_CTRL = 1x] &<br>[BOOST_VLIMTH = x1] | 1.8 | 1.98            |      | v    |

| (at VCOMP pin)                                                                 | COMP_CLH1            | BST_SLPCTRL_1 or<br>BST_SLPCTRL_0) &<br>(BST_VLIMTH_3 or<br>BST_VLIMTH_2)  | [BOOST_SLP_CTRL = x1] &<br>[BOOST_VLIMTH = 1x] | 1.5 | 1.64            |      | v    |

|                                                                                | COMP_CLH0            | BST_SLPCTRL_1 or<br>BST_SLPCTRL_0 ) &<br>(BST_VLIMTH_1 or<br>BST_VLIMTH_0) | [BOOST_SLP_CTRL = x1] &<br>[BOOST_VLIMTH = x1] | 1.2 | 1.35            |      | v    |

| EA min output voltage<br>(at VCOMP pin)                                        | COMP_CLL             |                                                                            |                                                |     |                 | 0.4  | V    |

| Division factor of<br>VCOMP voltage<br>towards the Current<br>comparator input | COMP_DIV             |                                                                            |                                                |     | 7               |      |      |

| Voltage shift (offset)<br>on VCOMP on Current<br>comparator input              | COMP_ <sub>VSF</sub> |                                                                            |                                                |     | 0.5             |      | V    |

|                                                                                | BST_SKCL_3           |                                                                            | [BOOST_SKCL = 11]                              |     | 0.7 or<br>0.8   |      | V    |

| Booster skip cycle for<br>low currents (Note 17)                               | BST_SKCL_2           |                                                                            | [BOOST_SKCL = 10]                              |     | 0.625<br>or 0.7 |      | V    |

|                                                                                | BST_SKCL_1           |                                                                            | [BOOST_SKCL = 01]                              |     | 0.55 or<br>0.6  |      | V    |

| VGATE comparator to                                                            | BST_VGATE_THR_1      |                                                                            | [VBOOST_VGATE_THR = 1]                         |     | 1.2             |      | V    |

| start BST_TOFF time                                                            | BST_VGATE_THR_0      |                                                                            | [VBOOST_VGATE_THR = 0]                         |     | 0.4             |      | V    |

# Table 11. BOOSTER CONTROLLER - VOLTAGE REGULATION PARAMETERS

| Characteristic                         | Symbol                            | Conditions                 | SPI Setting           | Min | Тур   | Max  | Unit |

|----------------------------------------|-----------------------------------|----------------------------|-----------------------|-----|-------|------|------|

| Booster PWM                            | BST_FREQ_31                       | FOSC8M / 38                | [BOOST_FREQ = 11111]  | 187 | 210   | 234  | kHz  |

| frequency (when from                   | BST_FREQ_01                       | FOSC8M / 8                 | [BOOST_FREQ = 00001]  | 890 | 1000  | 1110 | kHz  |

| internal generation)                   | BST_FREQ_00                       | PWM clock disabled         | [BOOST_FREQ = 00000]  |     | 0     |      | kHz  |

| Booster PWM freq.<br>increase per code | $\Delta \text{BST}_{\text{FREQ}}$ | Nonlinear increase, 5 bits |                       |     | 5–112 |      | kHz  |

|                                        | BST_TOFF_MIN_3                    |                            | [VBOOST_TOFFMIN = 11] | 100 | 155   | 210  | ns   |

| Booster minimum OFF                    | BST_TOFF_MIN_2                    |                            | [VBOOST_TOFFMIN = 10] | 140 | 195   | 250  | ns   |

| time (Note 18)                         | BST_TOFF_MIN_1                    |                            | [VBOOST_TOFFMIN = 01] | 30  | 75    | 120  | ns   |

|                                        | BST_TOFF_MIN_0                    |                            | [VBOOST_TOFFMIN = 00] | 70  | 115   | 160  | ns   |

|                                        | BST_ <sub>TON_MIN_3</sub>         |                            | [VBOOST_TONMIN = 11]  | 235 | 300   | 365  | ns   |

| Booster minimum ON                     | BST_TON_MIN_2                     |                            | [VBOOST_TONMIN = 10]  | 200 | 260   | 320  | ns   |

| time (Note 18)                         | BST_TON_MIN_1                     |                            | [VBOOST_TONMIN = 01]  | 150 | 200   | 250  | ns   |

|                                        | BST_TON_MIN_0                     |                            | [VBOOST_TONMIN = 00]  | 100 | 150   | 200  | ns   |

16. The following condition must always be respected: BST\_REG\_XX + BST\_OV\_X < 68 V. 17. The higher levels indicated in the cells are valid for BST\_VLIMTH\_2 and BST\_VLIMTH\_3 selection (BOOST\_VLIMTH<1> = 1). 18. Rise and fall time of the VGATE is not included.

#### Table 12. BOOSTER CONTROLLER - CURRENT REGULATION PARAMETERS

| Characteristic                                                 | Symbol        | Conditions         | SPI setting          | Min  | Тур  | Max | Unit   |

|----------------------------------------------------------------|---------------|--------------------|----------------------|------|------|-----|--------|

| Current comparator for                                         | BST_VLIMTH_3  |                    | [BOOST_VLIMTH = 11]  | 95   | 100  | 105 | mV     |

| Imax detection                                                 | BST_VLIMTH_2  |                    | [BOOST_VLIMTH = 10]  | 75   | 80   | 85  | mV     |

|                                                                | BST_VLIMTH_1  |                    | [BOOST_VLIMTH = 01]  | 57   | 62.5 | 67  | mV     |

| -                                                              | BST_VLIMTH_0  |                    | [BOOST_VLIMTH = 00]  | 45   | 50   | 55  | mV     |

| Current comparator for<br>VBOOST regulation,<br>offset voltage | BST_OFFS      |                    |                      | -5   | 0    | 5   | mV     |

| Booster slope                                                  | BST_SLPCTRL_3 |                    | [BOOST_SLPCTRL = 11] |      | 20   |     | mV/ μs |

| compensation                                                   | BST_SLPCTRL_2 |                    | [BOOST_SLPCTRL = 10] |      | 10   |     | mV/ μs |

|                                                                | BST_SLPCTRL_1 |                    | [BOOST_SLPCTRL = 01] |      | 5    |     | mV/ μs |

|                                                                | BST_SLPCTRL_0 | (no slope control) | [BOOST_SLPCTRL = 00] |      | 0    |     | mV/ μs |

| Booster Current<br>Sense voltage<br>common mode range          | CMVSENSE      |                    |                      | -0.1 |      | 1   | V      |

# Table 13. BOOSTER CONTROLLER – MOSFET GATE DRIVER

| Characteristic                | Symbol            | Conditions | Min | Тур | Max | Unit |

|-------------------------------|-------------------|------------|-----|-----|-----|------|

| High-side switch<br>impedance | RON <sub>HI</sub> |            |     | 2.5 | 4   | Ω    |

| Low-side switch<br>impedance  | RON <sub>LO</sub> |            |     | 2.5 | 4   | Ω    |

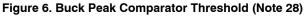

#### Table 14. BUCK REGULATOR - INTERNAL SWITCHES CHARACTERISTICS

| Characteristic             | Symbol                  | Conditions                                                               | Min | Тур | Max  | Unit |

|----------------------------|-------------------------|--------------------------------------------------------------------------|-----|-----|------|------|

| Buck switch On resistance  | R <sub>DS(on)</sub>     | At room-temperature, I(VINBCKx) pin = 1.5 A,<br>(VBOOST-VINBCKx) = 0.2 V |     |     | 0.65 | Ω    |

|                            | R <sub>DS(on)_hot</sub> | At Tj = 150°C, I(VINBCKx) pin = 1.5 A,<br>(VBOOST-VINBCKx) = 0.2 V       |     |     | 0.9  | Ω    |

| Buck Overcurrent detection | OCD                     |                                                                          | 1.9 |     | 3    | A    |

# Table 14. BUCK REGULATOR – INTERNAL SWITCHES CHARACTERISTICS

| Characteristic                                                  | Symbol   | Conditions        | Min | Тур | Max | Unit |

|-----------------------------------------------------------------|----------|-------------------|-----|-----|-----|------|

| Buck Switching slope<br>(ON phase)                              | Trise    |                   |     | 3   |     | V/ns |

| Buck Switching slope<br>(OFF phase)                             | Tfall    |                   |     | 2   |     | V/ns |

| Slow Buck Switching<br>Slope on NV78763–9<br>device (ON phase)  | Trise_Is | BUCK_DRV_SLOW = 1 |     | 1.5 |     | V/ns |

| Slow Buck Switching<br>Slope on NV78763–9<br>device (OFF phase) | Tfall_Is | BUCK_DRV_SLOW = 1 |     | 1.5 |     | V/ns |

# Table 15. BUCK REGULATOR – CURRENT REGULATION PARAMETERS

| Characteristic                                                    | Symbol                   | Cor                                                                | ditions                 | Min          | Тур   | Max          | Unit                 |

|-------------------------------------------------------------------|--------------------------|--------------------------------------------------------------------|-------------------------|--------------|-------|--------------|----------------------|

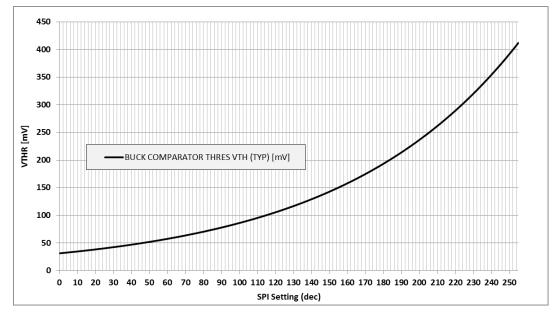

| Buck current sense threshold voltage                              | VTHR_255                 |                                                                    | [BUCKx_VTHR = 11111111] |              | 412   |              | mV                   |

| Buck current sense threshold voltage                              | VTHR_000                 |                                                                    | [BUCKx_VTHR = 00000000] |              | 31.5  |              | mV                   |

| Buck current sense<br>threshold voltage<br>increase per code      | ΔVTHR                    | exponential increase,<br>7.5 bits equivalent, DC<br>level          |                         |              | 1.013 | 1.5          | %                    |

| Buck threshold voltage temperature stability                      | VTHR_TEMP                | Without chopper function                                           |                         | -1.5 &<br>-2 |       | +1.5 &<br>+2 | % &<br>mV /<br>100°C |

| Buck threshold voltage accuracy (Note 21)                         | VTHR_ <sub>ERR</sub>     | Without chopper function                                           |                         | -3 &<br>-6   |       | +3 &<br>+6   | % &<br>mV            |

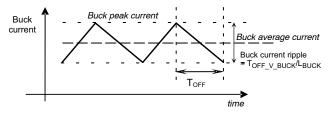

| Buck TOFFxVLED<br>constant setting for<br>shortest OFF time       | T <sub>OFF_VLED_15</sub> |                                                                    | [BUCKx_TOFFVLED = 1111] |              | 10    |              | μs V                 |

| Buck TOFFxVLED<br>constant setting for<br>longest OFF time        | T <sub>OFF_VLED_00</sub> |                                                                    | [BUCKx_TOFFVLED = 0000] |              | 50    |              | μs V                 |

| Buck OFF time<br>relative error                                   | BCK_TOFF_ERR_REL         | T <sub>OFF</sub> xVLED @VLED ><br>2 V & T <sub>OFF</sub> > 0.35 μs |                         | -10          | 0     | 10           | %                    |

| Buck OFF time<br>absolute error                                   | BCK_TOFF_ERR_ABS         | T <sub>OFF</sub> xVLED @VLED ><br>2 V & T <sub>OFF</sub> ≤ 0.35 μs |                         | -35          | 0     | 35           | ns                   |

| Buck OFF time setting<br>decrease per code                        | ΔTC                      | exponential increase,<br>4 bits, DC level                          |                         |              | 11.33 |              | %                    |

| Detection level for low<br>VLED voltages                          | VLED_LMT                 |                                                                    |                         | 1.62         | 1.8   | 1.98         | V                    |

| Buck ON too long time<br>detection (OPEN<br>LOAD)                 | BCK_TON_OPEN             |                                                                    |                         | 44.3         | 50    | 55.7         | μs                   |

| Buck minimum ON<br>time mask in<br>regulation (Note 20)           | BCK_ <sub>TON_MIN</sub>  |                                                                    |                         | 50           |       | 250          | ns                   |

| Buck OFF time for<br>short circuit detected<br>on VLEDx (Note 22) | BCK_TOFF_SHORT           | VLEDx < VLED_LMT                                                   |                         | 63           |       | 90           | μs                   |

| The zero-cross<br>detection threshold<br>level (Note 23)          | ZCD_TH                   |                                                                    |                         | -100         | -60   | -15          | mV                   |

| The zero-cross detection filter time                              | ZCD_FT                   |                                                                    |                         | 15           |       | 170          | ns                   |

# Table 15. BUCK REGULATOR – CURRENT REGULATION PARAMETERS

| Characteristic                                                                     | Symbol                  | Con                                                 | ditions | Min | Тур | Max | Unit |

|------------------------------------------------------------------------------------|-------------------------|-----------------------------------------------------|---------|-----|-----|-----|------|

| Delay from BUCK<br>ISENS comparator<br>input to BUCK switch<br>going OFF (Note 21) | BCK_ <sub>CMP_DEL</sub> | ISENS comparator<br>over-drive ramp ><br>1 mV/10 ns |         |     | 70  |     | ns   |

19. Without use of buck chopper function (for sufficient coil current ripple, see buck section in the datasheet). With the buck chopper function, the offset is reduced to a level lower than ±|3 mV|.

20. The buck ISENSE comparator is active at the end of this mask time.

21. BCK\_CMP\_DEL < 120 ns, guaranteed by laboratory measurement, not tested in production.

22. Unless zero-cross detection stops the TOFF time on NV78763-9 device.

23. The voltage at LBCKSWx pin when the comparator toggles, rising edge.

# Table 16. 5V TOLERANT DIGITAL INPUTS (SCLK, CSB, SDI, LEDCTRL1, LEDCTRL2, BSTSYNC)

| Characteristic                                  | Symbol            | Conditions | Min | Тур | Max | Unit |

|-------------------------------------------------|-------------------|------------|-----|-----|-----|------|

| High-level input<br>voltage                     | VINHI             |            | 2   |     |     | V    |

| Low-level input<br>voltage                      | VINLO             |            |     |     | 0.8 | V    |

| Input digital in leakage<br>current (Note 24)   | R <sub>PULL</sub> |            | 40  |     | 160 | kΩ   |

| LEDCTRLx to PWM<br>dimming propagation<br>delay | BUCKx_SW_DEL      |            | 3.6 | 4   | 4.9 | μs   |

24. Pull down resistor (R<sub>pulldown</sub>) for LEDCTRLx, BSTSYNC, SDI and SCLK, pull up resistor (R<sub>pullup</sub>) for CSB to VDD.

# Table 17. 5V TOLERANT OPEN-DRAIN DIGITAL OUTPUT (SDO)

| Characteristic                               | Symbol              | Conditions                                             | Min | Тур | Max | Unit |

|----------------------------------------------|---------------------|--------------------------------------------------------|-----|-----|-----|------|

| Low-voltage output<br>voltage                | VOUTLO              | I <sub>out</sub> = -10 mA (current flows into the pin) |     |     | 0.4 | V    |

| Equivalent output resistance                 | R <sub>DS(on)</sub> | Low-side switch                                        |     | 20  | 40  | Ω    |

| SDO pin leakage<br>current                   | SDO_ILEAK           |                                                        |     |     | 2   | μΑ   |

| SDO pin capacitance<br>(Note 25)             | SDO_C               |                                                        |     | 10  |     | pF   |

| CLK to SDO<br>propagation delay<br>(Note 26) | SDO_DL              | Low-side switch activation/deactivation time           |     |     | 320 | ns   |

25. Guaranteed by bench measurement, not tested in production.

26. Values valid for 1 kΩ external pull-up connected to 5 V and 100 pF to GND, when in case of falling edge the voltage on the SDO pin goes below 0.5 V. This delay is internal to the chip and does not include the RC charge at pin level when the output goes to high impedance.

# Table 18. 3V TOLERANT DIGITAL PINS (TST1, TST2)

| Characteristic                    | Symbol         | Conditions                    | Min | Тур | Max | Unit |

|-----------------------------------|----------------|-------------------------------|-----|-----|-----|------|

| High-level input<br>voltage       | VINHI          |                               | 2   |     |     | V    |

| Low-level input<br>voltage        | VINLO          |                               |     |     | 0.8 | V    |

| Input leakage current<br>TST1 pin | TST1_Rpulldown | Internal pull-down resistance | 19  | 32  | 47  | kΩ   |

| Input leakage current<br>TST2 pin | TST2_Rpulldown | Internal pull-down resistance | 1.6 | 4   | 5.9 | kΩ   |

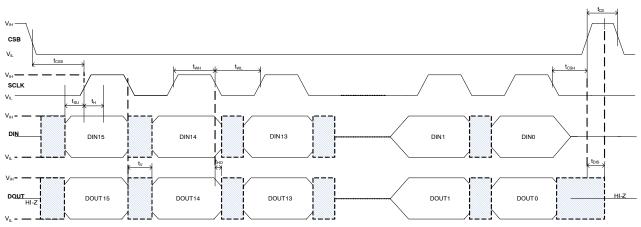

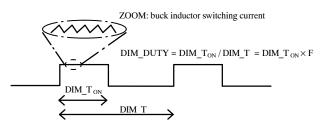

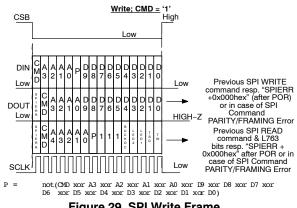

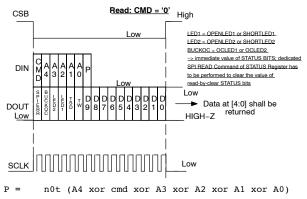

# Table 19. SPI INTERFACE

| Characteristic                                       | Symbol              | Conditions | Min  | Тур | Max            | Unit |

|------------------------------------------------------|---------------------|------------|------|-----|----------------|------|

| CSB setup time                                       | tcss                |            | 500  |     |                | ns   |

| CSB hold time                                        | tсsн                |            | 250  |     |                | ns   |

| SCLK low time                                        | twL                 |            | 500  |     |                | ns   |

| SCLK high time                                       | twн                 |            | 500  |     |                | ns   |

| Data-in (DIN) setup<br>time                          | ts∪                 |            | 250  |     |                | ns   |

| Data-in (DIN) hold<br>time                           | tн                  |            | 275  |     |                | ns   |

| SDO disable time                                     | tois                |            | 110  |     | 320            | ns   |

| SDO valid for high lo low transition                 | <sup>t</sup> sdo_hl |            |      |     | 320            | ns   |

| SDO valid for low lo<br>high transition<br>(Note 27) | <sup>t</sup> SDO_LH |            |      |     | 320 +<br>t(RC) | ns   |

| SDO hold time                                        | tно                 |            | 110  |     |                | ns   |

| CSB high time                                        | tcs                 |            | 1000 |     |                | ns   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions. 27. Time depends on the SDO load and pull–up resistor.

Figure 5. NCV78763 SPI Communication Timing

# **TYPICAL CHARACTERISTICS**

28. Curve obtained by applying the typical exponential increase from the min value VTHR\_000. Please see Table 15 for details.

#### DETAILED OPERATING AND PIN DESCRIPTION

#### SUPPLY CONCEPT IN GENERAL

Low operating voltages become more and more required due to the growing use of start stop systems. In order to respond to this necessity, the NCV78763 is designed to support power–up starting from  $V_{BB} = 5$  V.

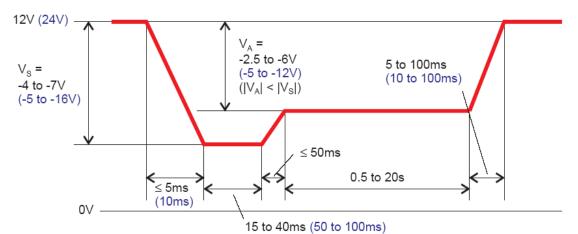

Figure 8. Cranking Pulse (ISO7637-1): System has to be Fully Functional (Grade A) from Vs = 5 V to 28 V

### **VDRIVE Supply**

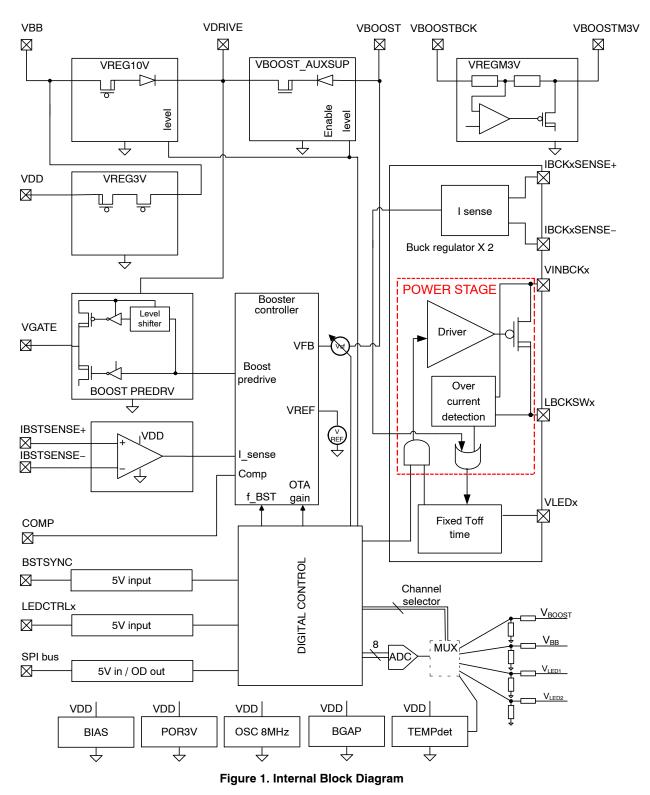

The VDRIVE supply voltage represents the power for the complete the BOOST PREDRV block, which generates the VGATE, used to switch the booster MOSFET. The voltage is programmable via SPI in 16 different values (register VDRIVE\_SETPOINT[3:0], ranging from a minimum of 5 V typical to 10 V typical: see Table 6). This feature allows having the best switching losses vs. resistive losses trade off, according to the MOSFET selection in the application, also versus the minimum required battery voltage. The lowest settings can be exploited to drive logic gate drive MOSFETs. In order to support low VBB battery voltages and long crank pulse drops, the VDRIVE supply can take its energy from the source with the highest output voltage, either from (refer to Figure 1):

- the VREG10V supply, which derives its energy from the VBB input.

- the VBOOST\_AUXSUP, which gets its energy from the VBOOST path. In order to enable this condition the bit VDRIVE\_BST\_EN[0] = 1. It is highly recommended to enable this function at module running mode in order to insure proper MOSFET gate drive even in case of large battery drop transients.

Under normal operating conditions, when the voltage headroom between VBB and VREG10V is sufficient, the gate driver energy is entirely supplied via the VBB path. In case the VBOOST\_AUX regulator is enabled, it will start to draw part of the required current starting as from when the headroom reduces below the minimum requirement, then linearly increasing, until bearing 100% of the IDRIVE current when the VBB drops close or below the VDRIVE target and still enough energy can be supplied by the booster circuit. Please note that the full device functionality is not guaranteed for VBB voltages lower than 4 V and that for very low voltages a reset will be generated (see Table 7).

<u>Note</u>: powering the device via the VBOOST\_AUXSUP will produce an extra power dissipation linked to the related linear drop (VBOOST – VBOOST\_AUXSUP), which must be taken into account during the thermal design.

# **VDD Supply**

The VDD supply is the low voltage digital and analog supply for the chip and derives energy from VBB. Due to the low dropout regulator design, VDD is guaranteed already from low VBB voltages. The Power–On–Reset circuit (POR) monitors the VDD voltage and the VBB voltage to control the out–of–reset and reset entering state: an internal switch disconnects the VDD regulator from the VBB input as its voltage drops below the admitted threshold VBB\_LOW (Table 7); this originates a VDD discharge that will result in a device reset either if the voltage falls below the PORL level or in general, if due to the drop, the VDD regulation target cannot be kept for more than typically 100 µs. At power-up, the chip will exit from reset state when VBB > VBB\_LOW and VDD > PORH.

#### VBOOSTM3V Supply

The VBOOSTM3V is the high side auxiliary supply for the gate drive of the buck regulators' integrated high-side P-MOSFET switches. This supply receives energy directly from the VBOOSTBCK pin.

# **INTERNAL CLOCK GENERATION – OSC8M**

An internal RC clock named OSC8M is used to run all the digital functions in the chip. The clock is trimmed in the factory prior to delivery. Its accuracy is guaranteed under full operating conditions and is independent from external component selection (refer to Table 9 for details).

# ADC

# General

The built–in analog to digital converter (ADC) is an 8–bit capacitor based successive approximation register (SAR). This embedded peripheral can be used to provide the following measurements to the external Micro Controller Unit (MCU):

- V<sub>BOOST</sub> voltage: sampled at the VBOOST pin;

- V<sub>BB</sub> voltage (linked to the battery line);

- VLED1<sub>ON</sub>, VLED2<sub>ON</sub> voltages;

- VLED1 and VLED2 voltages;

- VTEMP measurement (chip temperature).

The internal NCV78763 ADC state machine samples all the above channels automatically, taking care for setting the analog MUX and storing the converted values in memory. The external MCU can readout all ADC measured values via the SPI interface, in order to take application specific decisions. Please note that none of the MCU SPI commands interfere with the internal ADC state machine sample and conversion operations: the MCU will always get the last available data at the moment of the register read.

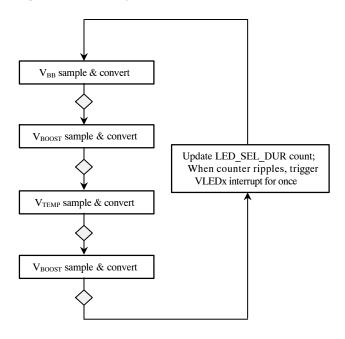

The state machine sampling and conversion scheme is represented in the figure below.

Figure 9. ADC Sample and Conversion Main Sequence

Referring to the figure above, the typical rate for a full SAR plus digital conversion per channel is 8  $\mu$ s (Table 10). For instance, each new V<sub>BOOST</sub> ADC converted sample occurs at 16  $\mu$ s typical rate, whereas for both the V<sub>BB</sub> and V<sub>TEMP</sub> channel the sampling rate is typically 32  $\mu$ s, that is to say a complete cycle of the depicted sequence. This time is referred to as T<sub>ADC</sub> SEQ.

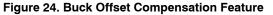

If the SPI setting LED\_SEL\_DUR[8:0] is not zero, then interrupts for the VLEDx measurements are allowed at the points marked with a rhombus, with a minimum cadence corresponding to the number of the elapsed ADC sequences (forced interrupt). In formulas:

$T_{VLEDx INT forced} = LED_SEL_DUR[8:0] \times T_{ADC SEQ}$

In general, prior to the forced interrupt status, the VLEDx<sub>ON</sub> ADC interrupts are generated when a falling edge on the control line for the buck channel "x" is detected by the device. In case of external dimming, this interrupt start signal corresponds to the LEDCTRLx falling edge together with a controlled phase delay (Table 16). When in internal dimming, the phase delay is also internally created, in relation with the falling edge of the dimming signal. The purpose of the phase delay is to allow completion the ongoing ADC conversion before starting the one linked to the VLEDx interrupt: if at the moment of the conversion LEDCTRLx pin is logic high, then the updated registers are VLEDxON[7:0] and VLEDx[7:0]; otherwise, if LEDCTRLx pin is logic low, the only register refreshed is VLEDx[7:0]. This mechanism is handled automatically by the NCV78763 logic without need of intervention from the user, thus drastically reducing the MCU cycles and embedded firmware and CPU cycles overhead that would be otherwise required.

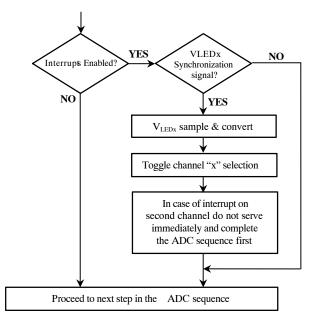

To avoid loss of data linked to the ADC main sequence, one LED channel is served at a time also when interrupt requests from both channels are received in a row and a full sequence is required to go through to enable a new interrupt VLEDx. In addition, possible conflicts are solved by using a defined priority (channel pre–selection). Out of reset, the default selection is given to channel "1". Then an internal flag keeps priority tracking, toggling at each time between channels pre–selection. Therefore, up to two dimming periods will be required to obtain a full measurement update of the two channels. This not considered however a limitation, as typical periods for dimming signals are in the order of 1 ms period, thus allowing very fast failure detection. A flow chart referring to the ADC interrupts is also displayed (Figure 10).

Figure 10. ADC VLEDx Interrupt Sequence

All NCV78763 ADC registers data integrity is protected by ODD parity on the bit 8 (that is to say the 9th bit if counting from the LSbit named "0"). Please refer to the SPI map section for further details.

# Battery voltage ADC: V<sub>BB</sub>

The battery voltage is sampled making use of the device supply  $V_{BB}$  pin. The (8-bit) conversion ratio is 40/255 (V/dec) = 0.157 (V/dec) typical. The converted value can be found in the SPI register VBB[7:0], with ODD parity protection bit in VBB[8]. The external MCU can make use of the measured VBB value to monitor the status of the module supply, for instance for a power de-rating algorithm.

### Boost voltage ADC: VBOOST

This measure refers to the boost voltage at the VBOOST pin, with an 8 bit conversion ratio of 70/255 (V/dec) = 0.274 (V/dec) typical, inside the SPI register VBOOST[7:0]. This measurement can be used by the MCU for diagnostics and booster control loop monitoring. The measurement is protected by parity (ODD) in bit VBOOST[8].

# Device Temperature ADC: V<sub>TEMP</sub>

By means of the VTEMP measurement, the MCU can monitor the device junction temperature  $(T_J)$  over time. The conversion formula is:

$T_{J} = (VTEMP[7:0](dec) - 20)[^{\circ}C]$

VTEMP[7:0] is the value read out directly from the related 8bit–SPI register (please refer to the SPI map). The value is also used internally by the device to for the *thermal warning* and *thermal shutdown* functions. More details on these two can be found in the dedicated sections in this document. The parity protection (ODD) is found on bit VTEMP[8].

# LED String Voltages ADC: V<sub>LEDx</sub>, V<sub>LEDxON</sub>

The voltage at the pins VLEDx (1, 2) is measured. Their conversion ratio is 70/255 (V/dec) = 0.274 (V/dec) typical. This information, found in registers VLEDxON[7:0] and VLEDx[7:0], can be used by the MCU to infer about the LED string status. For example, individual shorted LEDs, or dedicated Open string and short to GND or short to battery algorithms. As for the other ADC registers, the values are protected by ODD parity, respectively in VLEDxON[8] and VLEDx[8].

Please note that in the case of constant LEDCTRLx inputs and no dimming (in other words dimming duty cycle equals to 0% or 100%) the VLEDx interrupt is forced with a rate equal to  $T_{VLEDx\_INT\_forced}$ , given in the ADC general section. This feature can be exploited by MCU embedded algorithm diagnostics to read the LED channels voltage even when in OFF state, before module outputs activation (module startup pre-check).

# **BOOSTER REGULATOR**

# General

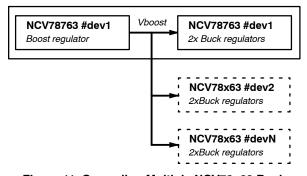

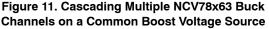

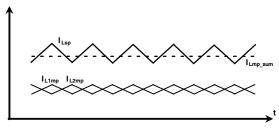

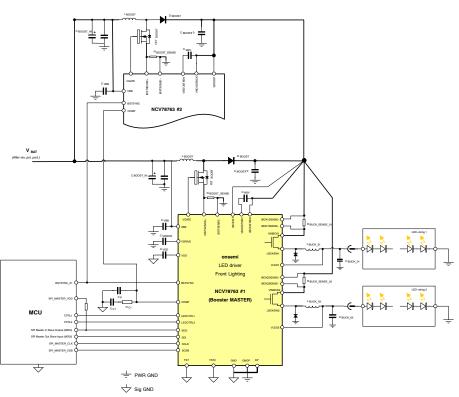

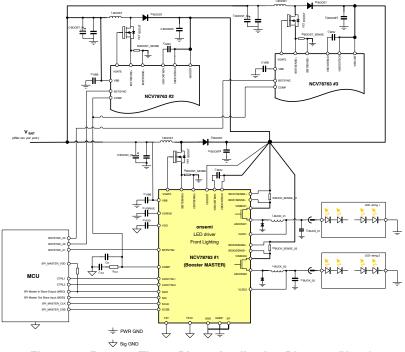

The NCV78763 features one common booster stage for the two high-current integrated buck current regulators. In addition, optional external buck regulators, belonging to other NCV78x63 devices, can be cascaded to the same boost voltage source as exemplified in the picture below.

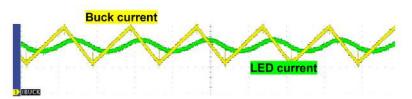

The booster stage provides the required voltage source for the LED string voltages out of the available battery voltage. Moreover, it filters out the variations in the battery input current in case of LED strings PWM dimming.

For nominal loads, the boost controller will regulate in *continuous mode* of operation, thus maximizing the system power efficiency at the same time having the lowest possible input ripple current (with "continuous mode" it is meant that the supply current does not go to zero while the load is activated). Only in case of very low loads or low dimming duty cycle values, *discontinuous mode* can occur: this means the supply current can swing from zero when the load is off, to the required peak value when the load is on, while keeping the required input average current through the cycle. In such situations, the total efficiency ratio may be lower than the theoretical optimal. However, as also the total losses will at

the same time be lower, there will be no impact on the thermal design.

On top of the cascaded configuration shown in the previous figure, the booster can be operated in *multi-phase mode* by combining more NCV78763 in the application. More details about the multiphase mode can be found in the dedicated section.

#### **Booster Regulation Principles**

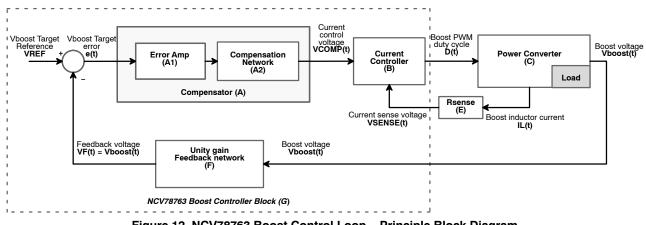

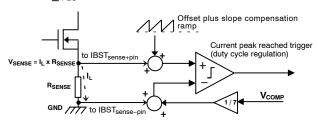

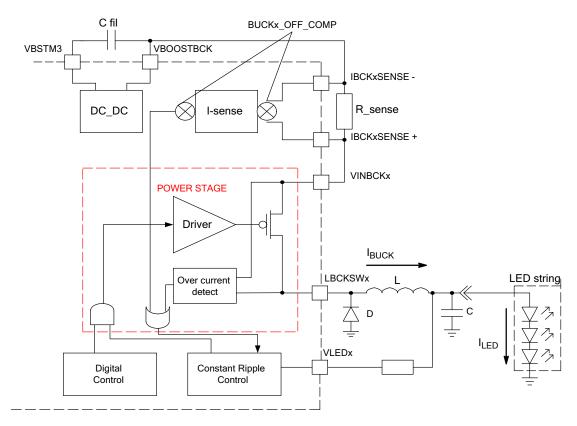

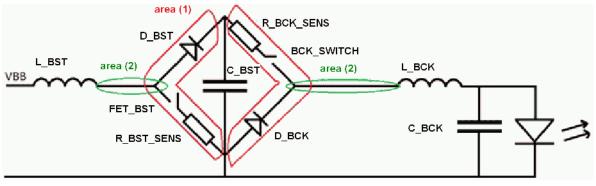

The NCV78763 features a *current-mode* voltage controller, which regulates the  $V_{BOOST}$  line used by the buck converters. The regulation loop principle is shown in the following picture. The loop compares the reference voltage ( $V_{BOOST}$ \_SETPOINT) with the actual measured voltage at the  $V_{BOOST}$  pin, thus generating an error signal which is treated internally by the error trans-conductance amplifier (block A1). This amplifier transforms the error voltage into current by means of the trans-conductance gain G<sub>m</sub>. The amplifier's output current is then fed into the external compensation network impedance (A2), so that it originates a voltage at the  $V_{COMP}$  pin, this last used as a reference by the current control block (B).

The current controller regulates the duty cycle as a consequence of the  $V_{COMP}$  reference, the sensed inductor peak current via the external resistor  $R_{SENSE}$  and the slope compensation used. The power converter (block C) represents the circuit formed by the boost converter externals (inductor, capacitors, MOSFET and forward diode). The load power (usually the LED power going via the buck converters) is applied to the converter.

The controlled variable is the boost voltage, measured directly at the device VBOOST pin with a unity gain feedback (block F). The picture highlights as block G all the elements contained inside the device. The regulation parameters are flexibly set by a series of SPI commands indicated in Tables 11 and 12. A detailed internal boost controller block diagram is presented in the next section.

Figure 12. NCV78763 Boost Control Loop – Principle Block Diagram

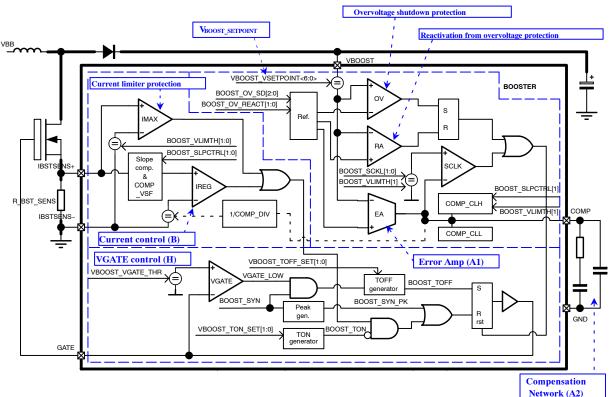

# **Boost Controller Detailed Internal Block Diagram**

A detailed NCV78763 boost controller block diagram is provided in this section. The main signals involved are indicated, with a particular highlight on the SPI programmable parameters. The blocks referring to the principle block diagram are also indicated. In addition, the *protection specific* blocks can be found (see dedicated sections for details).

Figure 13. NCV78763 Boost Controller Internal Detailed Block Diagram

# Booster Regulator Setpoint (VBOOST SETPOINT)

The booster voltage  $V_{BOOST}$  is regulated around the target programmable by the 7-bit SPI setting VBOOST\_SETPOINT[6:0], ranging from a minimum of 11 V to a maximum of typical 64.1 V (please refer to Table 11 for details). Due to the step-up only characteristic of any boost converter, the boost voltage cannot obviously be lower than the supply battery voltage provided. Therefore a target of 11 V would be used only for systems that require the activation of the booster in case of battery drops below the nominal level.

At power-up, the booster is disabled and the setpoint is per default the minimum (all zeroes).

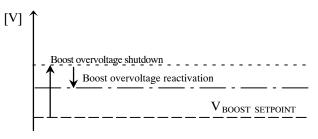

#### **Booster Overvoltage Shutdown Protection**

An integrated comparator monitors  $V_{BOOST}$  in order to protect the external booster components and the led driver device from overvoltage. When the voltage rises above the threshold defined by the sum of the  $V_{BOOST\_SETPOINT}$ (VBOOST\_SETPOINT[6:0]) and the overvoltage shutdown value (BOOST\_OV\_SD[2:0]), the MOSFET gate is switched-off at least for the current PWM cycle and at the same time, the boost overvoltage flag in the status register will be set (BOOST\_OV = 1), together with the BOOST\_STATUS flag equals to zero. The PWM runs again as from the moment the V<sub>BOOST</sub> will fall below the reactivation hysteresis defined by the BOOST\_OV\_REACT[1:0] SPI parameter. Therefore, depending on the voltage drop and the PWM frequency, it might be that more than one cycle will be skipped. A graphical interpretation of the protection levels is given in the figure below, followed by a summary table (Table 20).

Figure 14. Booster Voltage Protection Levels with Respect to the Setpoint

|    |                                                                                  |                                            | SPI FLAGS    |                                                             |  |  |  |

|----|----------------------------------------------------------------------------------|--------------------------------------------|--------------|-------------------------------------------------------------|--|--|--|

| ID | Description                                                                      | PWM VGATE Condition                        | BOOST_STATUS | BOOST_OV                                                    |  |  |  |

| А  | $V_{BOOST} < V_{BOOST}_{SETPOINT}$                                               | Normal (not disabled)                      | 1            | 0                                                           |  |  |  |

| В  | V <sub>BOOST</sub> > V <sub>BOOST_SETPOINT</sub> +<br>BOOST_OV_SD                | Disabled until case "C"                    | 0            | 1<br>(latched)                                              |  |  |  |

| С  | V <sub>BOOST</sub> < V <sub>BOOST</sub> SETPOINT +<br>BOOST OV SD BOOST OV REACT | Re-enables the PWM, normal mode resumed if | 1            | 1                                                           |  |  |  |

|    | BOOST_OV_SD BOOST_OV_REACT                                                       | from case "B"                              |              | (latched, if read in this condition it will go back to "0") |  |  |  |

Table 20. NCV78763 BOOSTER OVERVOLTAGE PROTECTION LEVELS AND RELATED SPI DIAGNOSTICS

After POR, the BOOST\_OV flag may be set at first read out. Please note that the booster overvoltage detection is also active when Booster is OFF (booster disabled by SPI related bit). Please note that the tolerances of the booster setpoint level and the booster overvoltage and reactivation are given in Table 11. When too low voltage is detected on VBOOST pin on NV78763–9 device, overvoltage will be flagged and booster stopped. It is protection in situation when VBOOST feedback is lost and undetected overvoltage could happen.

#### **Booster Current Regulation Loop**

The peak–current level of the booster is set by the voltage of the compensation pin COMP (output of the trans–conductance error amplifier, "block B" of Figure 13). This reference voltage is fed to the current comparator through a divider by 7 and compared to the voltage  $V_{SENSE}$ on the external sense resistor  $R_{SENSE}$ , connected to the pins IBSTSENSE+ and IBSTSENSE–. The sense voltage is created by the booster inductor coil current when the MOSFET is switched on and is summed up to an additional offset of +0.5 V (see COMP\_VSF in Table 11) and on top of that a slope compensation ramp voltage is added. The slope compensation is programmable by SPI via the setting (BOOST\_SLP\_CTRL[1:0]) and can also be disabled. Due to the offset, current can start to flow in the circuit as  $V_{COMP}$ > COMP\_VSF.

Figure 15. Booster Peak Current Regulator Involved in Current Control Loop

The maximum booster peak-current is limited by a dedicated comparator, presented in the next section.

#### **Booster Current Limitation Protection**

On top of the normal current regulation loop comparator, an additional comparator clamps the maximum physical current that can flow in the booster input circuit while the MOSFET is driven. The aim is to protect all the external components involved (boost inductor from saturation, boost diode and boost MOSFET from overcurrent, etc...). The protection is active PWM cycle–by–cycle and switches off the MOSFET GATE as  $V_{SENSE}$  reaches its maximum threshold  $V_{SENSE\_MAX}$  defined by the BST\_VLIMTH[1:0] register (see IMAX comparator in Figure 13 and Table 12 for more details). Therefore, the maximum allowed peak current will be defined by the ratio  $I_{PEAK\_MAX} = V_{SENSE\_MAX} / R_{SENSE}$ . The maximum current must be set in order to allow the total desired booster power for the lowest battery voltage. Warning: setting the current limit too low may generate unwanted system behavior as uncontrolled de–rating of the LED light due to insufficient power.

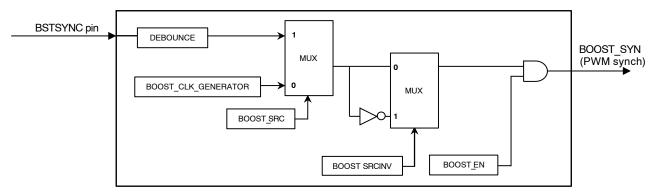

#### **Booster PWM Frequency and Disable**

The NCV78763 allows a flexible set of the booster PWM frequency. Two modes are available: internal generation or external drive, selectable by SPI bit setting BOOST\_SRC[0]. In either case, the booster must be enabled via the dedicated SPI bit to allow PWM generation (BOOST\_EN = 1). When BOOST\_EN = 0, the peripheral is off and the GATE drive is disabled. Please note that the error amplifier is not shut off automatically and to avoid voltage generation on the VCOMP pin the  $G_m$  gain must be put to zero as well.

#### **Booster PWM Internal Generation**

This mode activated by BOOST\_SRC = 0, creates the PWM frequency starting from the internal clock FOSC8M. A fine selection of frequencies is enabled by the register BOOST\_FREQ[4:0], ranging from typical 210 kHz to typical 1 MHz (Table 11). The frequency generation is disabled by selecting the value "zero"; this is also the POR default value.

#### **Booster PWM External Generation**

When BOOST\_SRC = 1, the booster PWM external generation mode is selected and the frequency is taken directly from the BOOST\_SYNC device pin. There is no actual limitation in the resolution, apart from the system clock for the sampling and a debounce of two clock cycles on the signal edges. The gate PWM is synchronized with either the rising or falling edge of the external signal depending on the BOOST\_SRCINV bit value. The default POR value is "0" and corresponds to synchronization to the rising flank. BOOST\_SRCINV equals "1" selects falling edge synchronization.

Figure 16. NCV78763 Booster Frequency Generation Block

#### **Booster PWM Min TOFF and Min TON protection**

As additional protection, the PWM duty cycle is constrained between a minimum and a maximum, defined per means of two parameters available in the device. The PWM *minimum on-time* is programmable via BOOST\_TONMIN[1:0]: its purpose is to guarantee a minimum activation interval for the booster MOSFET GATE, to insure full drive of the component and avoiding switching in the linear region. Please note that this does not imply that the PWM is always running even when not required by the control loop, but means that whenever the MOSFET should be activated, then its on time would be at least the one specified. At the contrary When no duty cycle at all is required, then it will be zero.

The PWM *minimum off-time* is set via the parameter BOOST\_TOFFMIN[1:0]: this parameter is limiting the maximum duty cycle that can be used in the regulation loop for a defined period  $T_{PWM}$ :

$$\mathsf{Duty}_{\mathsf{MAX}} = \frac{\left(\mathsf{T}_{\mathsf{PWM}} - \mathsf{T}_{\mathsf{OFFMIN}}\right)}{\mathsf{T}_{\mathsf{PWM}}}$$

The main aim of a maximum duty cycle is preventing MOSFET shoot-through in cases the (transient) duty cycle would get too close to 100% of the MOSFET real switch-off characteristics. In addition, as a secondary effect, a limit on the duty cycle may also be exploited to minimize the inrush current when the load is activated.

<u>Warning</u>: a wrong setting of the duty cycle constraints may result in unwanted system behavior. In particular, a too big  $T_{OFFMIN}$  may prevent the system to regulate the  $V_{BOOST}$ with low battery voltages ( $V_{BAT}$ ). This can be explained by the simplified formula for booster *steady state continuous mode*:

$$\mathsf{V}_{\mathsf{BOOST}} \cong \frac{\mathsf{V}_{\mathsf{BAT}}}{(1-\mathsf{Duty})} \Leftrightarrow \mathsf{Duty} \cong \frac{\mathsf{V}_{\mathsf{BOOST}} - \mathsf{V}_{\mathsf{BAT}}}{\mathsf{V}_{\mathsf{BOOST}}}$$

So in order to reach a desired  $V_{BOOST}$  for a defined supply voltage, a certain duty cycle must be guaranteed.

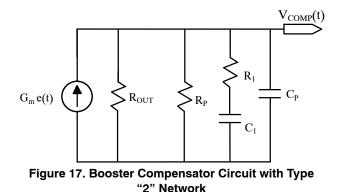

#### **Booster Compensator Model**

A linear model of the booster controller compensator (block "A" Figure 13) is provided in this section. The protection mechanisms around are not taken into account. A type "2" network is taken into account at the VCOMP pin. The equivalent circuit is shown below:

In the Figure, e(t) represents the control error, equals to the difference  $V_{BOOST\_SETPOINT}(t) - V_{BOOST}(t)$ . "G<sub>m</sub>" is the trans–conductance error amplifier gain, while "R<sub>OUT</sub>" is the amplifier internal output resistance. The values of these two parameters can be found in Table 11 in this datasheet.

By solving the circuit in Laplace domain the following error to  $V_{COMP}$  transfer function is obtained:

$$\begin{split} H_{\text{COMP}}(s) &= \frac{V_{\text{COMP}}(s)}{e(s)} \\ &= G_{\text{COMP}} \frac{\left(1 + \tau_1 s\right)}{\left(1 + \left(\tau_P + \tau_{1P}\right)s + \left(\tau_1 \times \tau_P\right)s^2\right)} \end{split}$$

The explanation of the parameters stated in the equation above follows:

$$G_{COMP} = G_m R_T$$

$$R_T = \frac{R_P \times R_{OUT}}{R_P + R_{OUT}}$$

$$\tau_1 = R_1 C_1$$

$$\tau_P = R_T C_P$$

$$\tau_{1P} = (R_1 + R_T)C_1$$

This transfer function model can be used for closed loop stability calculations.

### **Booster PWM skip cycles**

In case of light booster load, it may be useful to reduce the number of effective PWM cycles in order to get a decrease of the input current inrush bursts and a less oscillating boost voltage. This can be obtained by using the "skip cycles" feature, programmable by SPI via BOOST\_SKCL[1:0] (see Table 11 and SPI map). BOOST\_SKCL[1:0] = '00' means skip cycle disabled.