# AN INFINEON TECHNOLOGIES COMPANY

#### **Features**

- GEN5 Non Punch Through (NPT) Technology

- Low V<sub>CE(on</sub>

- 10µs Short Circuit Capability

- Square RBSOA

- Positive V<sub>CE(on)</sub> Temperature Coefficient

#### **Benefits**

- Benchmark Efficiency for Motor Control Applications

- Rugged Transient Performance

- Excellent Current Sharing in Parallel Operation

- Qualified for Industrial Market

# Die in Wafer Form

$V_{CES}$  = 600V  $I_{C(Noml)}$  = 100A  $V_{CE(on)}$  typ = 1.8V @  $I_{C(nom)}$  @ 25°C Motor Control IGBT Short Circuit Rated 150mm Wafer

## Electrical Characteristics (Wafer Form)①

| Parameter        | Description                             | Min. | Тур. | Max.  | Units | Test Conditions                                         |

|------------------|-----------------------------------------|------|------|-------|-------|---------------------------------------------------------|

| $V_{CE(ON)}$     | Collector-to-Emitter Saturation Voltage |      | 1.8  | 2.1   |       | $V_{GE} = 15V, I_{C} = 100A, T_{J} = 25^{\circ}C$       |

| $V_{(BR)CES}$    | Collector-to-Emitter Breakdown Voltage  | 600  |      |       | V     | $V_{GE} = 0V$ , $I_{CES} = 1mA$ , $T_J = 25$ °C         |

| $V_{GE(th)}$     | Gate-Emitter Threshold Voltage          | 3.5  |      | 5.5   |       | $V_{GE} = V_{CE, I_C} = 250 \mu A, T_J = 25 ^{\circ} C$ |

| I <sub>CES</sub> | Zero Gate Voltage Collector Current     |      |      | 35    | μΑ    | $V_{CE} = 600V, V_{GE} = 0V, T_{J} = 25^{\circ}C$       |

| $I_{GES}$        | Gate Emitter Leakage Current            |      |      | ± 200 | nΑ    | $V_{CE} = 0V, V_{GE} = \pm 20V, T_{J} = 25^{\circ}C$    |

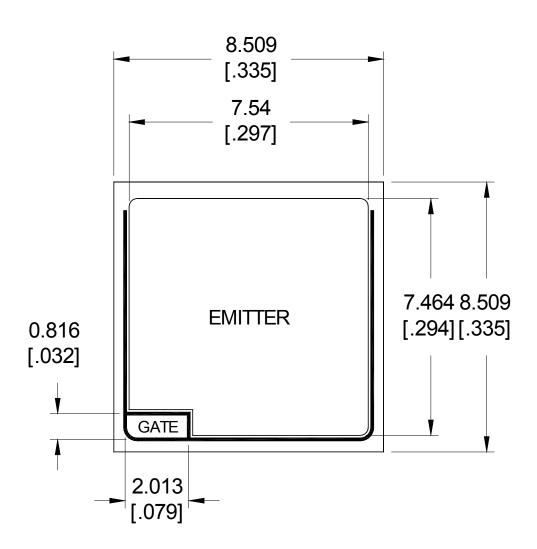

#### **Mechanical Parameter**

| Nominal Backside Metal Composition, (Thickness) | Al - Ti - Ni/V - Ag (1kA -1kA - 4kA - 6kA)                                      |  |  |  |

|-------------------------------------------------|---------------------------------------------------------------------------------|--|--|--|

| Nominal Front Metal Composition, (Thickness)    | 99% Al 1% Si (4µm)                                                              |  |  |  |

| Dimensions                                      | 0.335" x 0.335"                                                                 |  |  |  |

| Wafer Diameter                                  | 150mm, with std. < 100> flat                                                    |  |  |  |

| Wafer Thickness, Tolerance                      | 85μm, +/-7μm                                                                    |  |  |  |

| Relevant Die Mechanical Dwg. Number             | 01-5564                                                                         |  |  |  |

| Minimum Street Width                            | 100μm                                                                           |  |  |  |

| Reject Ink Dot Size                             | 0.25 mm diameter minimum                                                        |  |  |  |

| Ink Dot Location                                | Consistent throughout same wafer lot                                            |  |  |  |

| Recommended Storage Environment                 | Store in original container, in desiccate nitrogen, with no contamination       |  |  |  |

| Recommended Die Attach Conditions               | For optimum electrical results, die attach temperature should not exceed 300°C. |  |  |  |

## Note:

- ① This IR product is 100% tested at wafer level and is manufactured using established, mature and well characterized processes. Due to restrictions in die level processing, die may not be equivalent to standard package products and are therefore offered with a conditional performance guarantee. The above data sheet is based on IR sample testing under certain predetermined and assumed conditions, and are provided for illustration purposes only. Customers are encouraged to perform testing in actual proposed packaged and use conditions. IR die products are tested using IR-based quality assurance procedures and are manufactured using IR's established processes. Programs for customer-specified testing are available upon request. IR has experienced assembly yields of generally 95% or greater for individual die; however, customer's results will vary. Estimates such as those described and set forth in this data sheet for semiconductor die will vary depending on a number of packaging, handling, use and other factors. Sold die may not perform on an equivalent basis to standard package products and are therefore offered with a limited warranty as described in IR's applicable standard terms and conditions of sale. All IR die sales are subject to IR's applicable standard terms and conditions of sale, which are available upon request. For customers requiring a particular parameter to be guaranteed, special testing can be carried out or product can be purchased as known good die.

- ② Part number shown is for die in wafer. Contact factory for these other options.

#### **Die Outline**

### NOTES:

- 1. ALL DIMENSIONS ARE SHOWN IN MILLIMETERS [INCHES].

- 2. CONTROLLING DIMENSION: [INCH].

- 3. LETTER DESIGNATION:

4. DIMENSIONAL TOLERANCES:

WIDTH < [.0250] TOLERANCE = +/- [.0005]

& > 0.635 TOLERANCE = +/- 0.025

LENGTH > [.0250] TOLERANCE = +/- [.0010]

OVERALL DIE: < 1.270 TOLERANCE = +/- 0.102

WIDTH < [.050] TOLERANCE = +/- [.004]

& > 1.270 TOLERANCE = +/- 0.203

LENGTH > [.050] TOLERANCE = +/- [.008]

BONDING PADS: < 0.635 TOLERANCE = +/- 0.013

## Additional Testing and Screening

For Customers requiring product supplied as Known Good Die (KGD) or requiring specific die level testing, please contact your local IR Sales

### Shipping

Sawn Wafer on Film. Please contact your local IR sales office for non-standard shipping options

### Handling

- Product must be handled only at ESD safe workstations. Standard ESD precautions and safe work environments are as defined in MIL-HDBK-263.

- Product must be handled only in a class 10,000 or better-designated clean room environment.

- Singulated die are not to be handled with tweezers. A vacuum wand with a non-metallic ESD protected tip should be used.

# Wafer/Die Storage

- Proper storage conditions are necessary to prevent product contamination and/or degradation after shipment.

- Note: To reduce the risk of contamination or degradation, it is recommended that product not being used in the assembly process be returned to their original containers and resealed with a vacuum seal process.

- Sawn wafers on a film frame are intended for immediate use and have a limited shelf life.

# **Further Information**

For further information please contact your local IR Sales office.

**Revision History**

| Date       | Comments                                                                                                                       |  |  |  |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 07/06/2015 | <ul> <li>Updated IFX logo on all pages</li> <li>Removed Vceon @ I<sub>C</sub> = 10A, V<sub>GE</sub> = 15V on page1.</li> </ul> |  |  |  |  |  |

|            | Corrected Iges from +/-1.1uA to +/-200nA on page1.                                                                             |  |  |  |  |  |

IR WORLD HEADQUARTERS: 101 N. Sepulveda Blvd., El Segundo, California 90245, USA To contact International Rectifier, please visit http://www.irf.com/whoto-call/