# 5V-0.5A VERY LOW DROP REGULATOR WITH RESET

- PRECISE OUTPUT VOLTAGE (5V ± 4%) OVER FULL TEMPERATURE RANGE (-40 / 125 °C)

- VERY LOW VOLTAGE DROP (0.75Vmax) OVER FULL T RANGE

- OUTPUT CURRENT UP TO 500mA

- RESET FUNCTION

- POWER-ON RESET DELAY PULSE DE-FINED BY THE EXTERNAL CAPACITOR

- +80V LOAD DUMP PROTECTION

- 80V LOAD DUMP PROTECTION

- REVERSE VOLTAGE PROTECTION

- SHORT CIRCUIT PROTECTION AND THER-MAL SHUT-DOWN (with hysteresis)

- LOW START UP CURRENT

### **DESCRIPTION**

The L4947/L4947R is a monolithic integrated circuit in Pentawatt package specially designed to provide a stabilized supply voltage for automotive and industrial electronic systems. Thanks to its very low voltage drop, in automotive applications the L4947/L4947R can work correctly even during the cranking phase, when the battery voltage

could fall as low as 6V. Furthermore, it incorporates a complete range of protection circuits against the dangerous overvoltages always present on the battery rail of the car. The reset function makes the device particularly suited to supply microprocessor based systems: a signal is available (after an externally programmable delay) to reset the microprocessor at power-on phase; at power-off, this signal becomes low inhibiting the microprocessor.

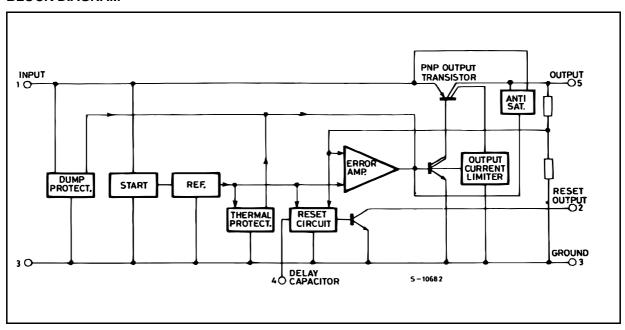

#### **BLOCK DIAGRAM**

June 2000 1/6

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol                            | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Value                             | Unit                                  |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------------------|

| Vi                                | DC Input Voltage DC Reverse Input Voltage Transient Input Overvoltages : Load Dump : $5\text{ms} \leq t_{\text{rise}} \leq 10\text{ms}$ $\tau_f \text{ Fall Time Constant} = 100\text{ms}$ $R_{\text{SOURCE}} \geq 0.5\Omega$ Field Decay : $5\text{ms} \leq t_{\text{fall}} \leq 10\text{ms}, \ R_{\text{SOURCE}} \geq 10\Omega$ $\tau_r \text{ Rise Time Constant} = 33\text{ms}$ $\text{Low Energy Spike}:$ $t_{\text{rise}} = 1\mu\text{s}, \ t_{\text{fall}} = 500\mu\text{s}, \ R_{\text{SOURCE}} \geq 10\Omega$ $f_r \text{ Repetition Frequency} = 5\text{Hz}$ | 35<br>- 18<br>80<br>- 80<br>± 100 | > > > > > > > > > > > > > > > > > > > |

| $V_{R}$                           | Reset Output Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 35                                | V                                     |

| T <sub>J</sub> , T <sub>stg</sub> | Junction and Storage Temperature Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | - 55 to 150                       | °C                                    |

Note: The circuit is ESD protected according to MIL-STD-883C.

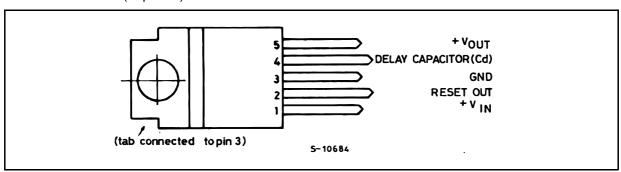

# PIN CONNECTION (Top view)

## **THERMAL DATA**

| Symbol                 | Parameter                            | Value | Unit |

|------------------------|--------------------------------------|-------|------|

| R <sub>th j-case</sub> | Thermal Resistance Junction-case Max | 3.5   | °C/W |

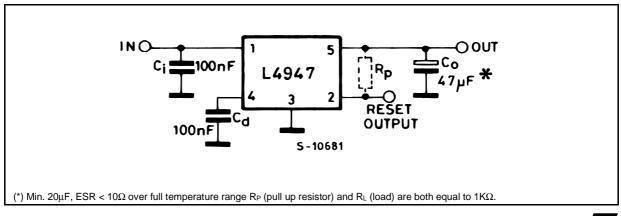

## **TEST CIRCUIT**

2/6

**ELECTRICAL CHARACTERISTICS** (refer to the test circuit,  $V_i = 14.4V$ ,  $C_o = 47\mu F$ , ESR <  $10\Omega$ ,  $R_p = 1K\Omega$ ,  $R_L = 1K\Omega$ ,  $-40^{\circ}C \le T_J \le 125^{\circ}C$ , unless otherwise specified)

| Symbol                 | Parameter Test Conditions                                         |                                                                                             | Min.                        | Тур.             | Max.                  | Unit           |

|------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------|------------------|-----------------------|----------------|

| Vo                     | Output Voltage I <sub>o</sub> = 0mA to 500mA<br>Over Full T Range |                                                                                             | 4.80                        | 5.00             | 5.20                  | V              |

|                        |                                                                   | $T_J = 25^{\circ}C$                                                                         | 4.90                        | 5.00             | 5.10                  | V              |

| Vi                     | Operating Input Voltage                                           | $I_0 = 0mA \text{ to (*) } 500mA$                                                           | 6                           |                  | 26                    | V              |

| $\Delta V_o$           | Line Regulation                                                   | $V_i$ = 6V to 26V ; $I_o$ = 5mA                                                             |                             | 2                | 10                    | mV             |

| $\Delta V_{o}$         | Load Regulation                                                   | $I_0 = 5mA$ to $500mA$                                                                      |                             | 15               | 60                    | mV             |

| $V_i - V_o$            | Dropout Voltage                                                   | $I_0 = 500$ mA, $T_J = 25$ °C<br>Over Full T Range                                          |                             | 0.40             | 0.55<br>0.75          | V<br>V         |

| Iq                     | Quiescent Current                                                 | $I_0 = 0$ mA, $T_J = 25$ °C<br>$I_0 = 0$ mA Over Full T<br>$I_0 = 500$ mA Over Full T       |                             | 5<br>6.5<br>110  | 10<br>13<br>180       | mA<br>mA<br>mA |

| $\frac{\Delta V_o}{T}$ | Temperature Output Voltage Drift                                  |                                                                                             |                             | - 0.5            |                       | mV/°C          |

| SVR                    | Supply Volt. Rej.                                                 | $I_0 = 350 mA$ ; $f = 120 Hz$ 5<br>$C_0 = 100 \mu F$ ;<br>$V_1 = 12 V \pm 5 V_{pp}$         |                             | 60               |                       | dB             |

| I <sub>sc</sub>        | Output Short Circuit Current                                      |                                                                                             | 0.50                        | 0.80             | 1.50                  | Α              |

| $V_{R}$                | Reset Output Saturation Voltage                                   | $1.5V < V_0 < V_{RT (off)},$ $I_R = 1.6mA$                                                  |                             |                  | 0.40                  | V              |

|                        |                                                                   | $3.0V < V_0 < V_{RT (off)},$ $I_R = 8mA$                                                    |                             |                  | 0.40                  | V              |

| $I_R$                  | Reset Output Leakage Current                                      | $V_O$ in Regulation, $V_R = 5V$                                                             |                             |                  | 50                    | μΑ             |

| $V_{RTpeak}$           | Power On-Off Reset out Peak<br>Voltage                            | 1K $\Omega$ Reset Pull-up to V <sub>o</sub> , T <sub>J</sub> = 25°C                         |                             | 0.50             | 0.80                  | V              |

| V <sub>RT (off)</sub>  | Power OFF V <sub>o</sub> Threshold                                | $T_J = 25^{\circ}\text{C}$<br><b>L4947:</b> V <sub>o</sub> @ Reset Out H to L<br>Transition | 4.70<br>4.75                | Vo <i>-</i> 0.15 |                       | V              |

|                        |                                                                   | <b>L4947R:</b> V <sub>0</sub> @ Reset Out H to L Transition                                 | 4.55                        | Vo <i>-</i> 0.30 |                       | V              |

| V <sub>RT (on)</sub>   | Power ON V <sub>o</sub> Threshold                                 | $V_o$ @ Reset Out L to H Transition                                                         | V <sub>RT (o</sub><br>+ 0.0 |                  | V <sub>o</sub> – 0.04 | V              |

| $V_{Hyst}$             | Power ON-Off Hysteresis                                           | V <sub>RT (on)</sub> –V <sub>RT (off)</sub>                                                 |                             | 0.05             |                       | V              |

| $V_{d}$                | Delay Comparator Threshold                                        | $V_d$ @ Reset Out L to H Transition                                                         | 3.65                        | 4.00             | 4.35                  | V              |

|                        |                                                                   | $V_d$ @ Reset Out H to L Transition                                                         | 3.20                        | 3.55             | 3.90                  | V              |

| $V_{dH}$               | Delay Comparator Hysteresis                                       |                                                                                             |                             | 0.45             |                       | V              |

| l <sub>d</sub>         | Delay Capacitor Charging Current                                  | $V_d = 3V$ , $T_J = 25$ °C                                                                  |                             | 20               |                       | /μΑ            |

| $V_{\text{disch}}$     | Delay Capacitor Discharge<br>Voltage                              | $V_{o} < V_{RT (off)}$                                                                      |                             | 0.55             | 1.20                  | V              |

| T <sub>d</sub>         | Power on Reset Delay Time $C_d = 100nF, T_J = 25^{\circ}C$        |                                                                                             | 10                          | 20               | 30                    | ms             |

(\*) For a DC voltage  $26 < V_i < 37V$  the device is not operating

#### **FUNCTIONAL DESCRIPTION**

The L4947/L4947R is a very low drop 5V/0.5A voltage regulator provided with a reset function and therefore particularly suited to meet the requirements of supplying the microprocessor systems used in automotive and industrial applications.

The block diagram shows the basic structure of the device : the reference, the error amplifier, the driver, the power PNP, the protection and reset functions.

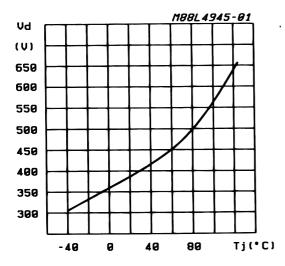

The power stage is a Lateral PNP transistor which allows a very low dropout voltage (typ. 400mV at  $T_J=25^\circ\text{C}$ , max. 750mV over the full temperature range @  $I_O=500\text{mA}$ ). The typical curve of the dropout voltage as a function of the junction temperature is shown in Fig. 1 : that is the worst case, where  $I_O=500\text{mA}$ .

The current consumption of the device (quiescent current) is maximum 13mA - over full T - when no load current is required.

The internal antisaturation circuit allows a drastic reduction in the current peak which takes place during the start up.

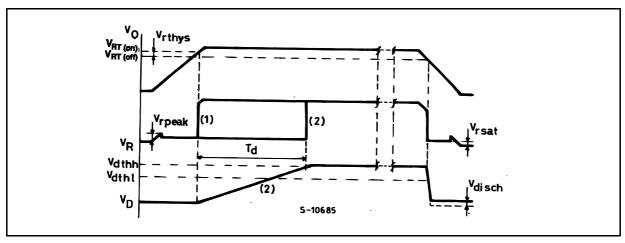

The reset function supervises the regulator output voltage inhibiting the microprocessor when the device is out of regulation and resetting it at the power-on after a settable delay. The reset is LOW when the output voltage value is lower than the reset threshold voltage. At the power-on phase the output voltage increases (see Fig. 2) and when it reaches the power-on Vo threshold VRT (On) - the reset output becomes HIGH after a delay time set by the external capacitor  $C_d$ . At the power-off the output voltage decreases : at the VRT(Off) threshold value (Vo-0.15V typ. for L4947 and Vo-0.3V typ. for L4947R value) the reset out-

Figure 1: Typical Dropout Voltage vs.  $T_j$  ( $I_0 = 500 \text{mA}$ ).

Figure 2: Reset Waveforms:

- (1) Without External Capacitor C<sub>d</sub>.

- (2) With External Capacitor Cd.

put instantaneously goes down (LOW status) inhibiting the microprocessor. The typical power onoff hysteresis is 50mV.

The three gain stages (operational amplifier, driver and power PNP) require the external capacitor ( $C_{omin}=20\mu F$ ) to guarantee the global stability of the system.

Load dump and field decay protections (± 80V), reverse voltage (– 18V) and short circuit protection, thermal shutdown are the main features that make the L4947/L4947R specially suitable for applications in the automotive environment.

#### **EXTERNAL COMPENSATION**

Since the purpose of a voltage regulator is to supply and load variations, the open loop gain of the regulator must be very high at low frequencies. This may cause instability as a result of the various poles present in the loop. To avoid this instability dominant pole compensation is used to reduce phase shift due to other poles at the unity gain frequency. The lower the frequency of these others poles at the unity gain frequency. The lower the frequency of these other poles, the greater must be capacitor esed to create the dominant pole for the same DC gain.

Where the output transistor is a lateral PNP type there is a pole in the regulation loop at a frequencybtoo low to be compensated by a capacitor which can be integrated. An external compensation is therefore necessary so a very high value capacitor must be connected from the output to ground.

The paeassitic equivalent series resistance of the capacitor used adds a zero to the regulation loop. This zero may compromise the stability of the system since its effect tends to cancel the effect of the pole added. In regulators this ESR must be less than  $3\Omega$  and the minimum capacitor value is  $47\mu F$ .

4/6

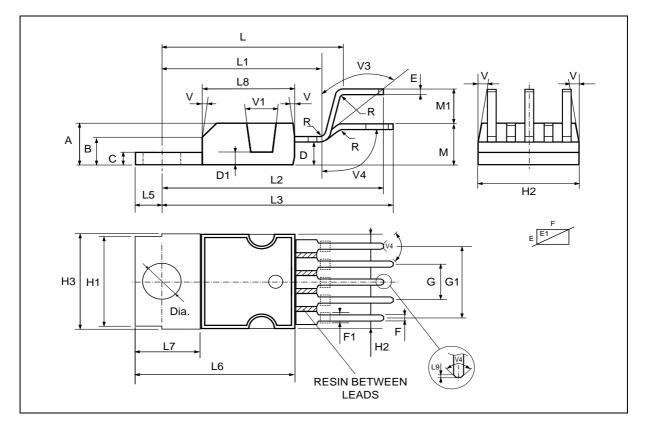

| DIM. | mm         |       |       | inch  |       |       |

|------|------------|-------|-------|-------|-------|-------|

| DIW. | MIN.       | TYP.  | MAX.  | MIN.  | TYP.  | MAX.  |

| Α    |            |       | 4.8   |       |       | 0.189 |

| С    |            |       | 1.37  |       |       | 0.054 |

| D    | 2.4        |       | 2.8   | 0.094 |       | 0.110 |

| D1   | 1.2        |       | 1.35  | 0.047 |       | 0.053 |

| Е    | 0.35       |       | 0.55  | 0.014 |       | 0.022 |

| E1   | 0.76       |       | 1.19  | 0.030 |       | 0.047 |

| F    | 0.8        |       | 1.05  | 0.031 |       | 0.041 |

| F1   | 1          |       | 1.4   | 0.039 |       | 0.055 |

| G    | 3.2        | 3.4   | 3.6   | 0.126 | 0.134 | 0.142 |

| G1   | 6.6        | 6.8   | 7     | 0.260 | 0.268 | 0.276 |

| H2   |            |       | 10.4  |       |       | 0.409 |

| НЗ   | 10.05      |       | 10.4  | 0.396 |       | 0.409 |

| L    | 17.55      | 17.85 | 18.15 | 0.691 | 0.703 | 0.715 |

| L1   | 15.55      | 15.75 | 15.95 | 0.612 | 0.620 | 0.628 |

| L2   | 21.2       | 21.4  | 21.6  | 0.831 | 0.843 | 0.850 |

| L3   | 22.3       | 22.5  | 22.7  | 0.878 | 0.886 | 0.894 |

| L4   |            |       | 1.29  |       |       | 0.051 |

| L5   | 2.6        |       | 3     | 0.102 |       | 0.118 |

| L6   | 15.1       |       | 15.8  | 0.594 |       | 0.622 |

| L7   | 6          |       | 6.6   | 0.236 |       | 0.260 |

| L9   |            | 0.2   |       |       | 0.008 |       |

| М    | 4.23       | 4.5   | 4.75  | 0.167 | 0.177 | 0.187 |

| M1   | 3.75       | 4     | 4.25  | 0.148 | 0.157 | 0.167 |

| V4   | 40° (typ.) |       |       |       |       |       |

# OUTLINE AND MECHANICAL DATA

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

@ 2000 STMicroelectronics – Printed in Italy – All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.

http://www.st.com