# WIDE BANDWIDTH AND MOS INPUT SINGLE OPERATIONAL AMPLIFIER

- LOW DISTORTION

- GAIN BANDWIDTH PRODUCT: 300MHz

- GAIN OF 2 STABILITY ■ SLEW RATE: 400V/µs

- VERY FAST SETTLING TIME: 60ns (0.1%)

- VERY HIGH INPUT IMPEDANCE

## **DESCRIPTION**

The TSH321 is a wideband monolithic operational amplifier, requiring a minimum close loop gain of 2 for stability.

The TSH321 features extremely high input impedance (typically greater than  $10^{12}\Omega$ ) allowing direct interfacing with high impedance sources.

Low distortion, wide bandwidth and high linearity make this amplifier suitable for RF and video applications. Short circuit protection is provided by an internal current-limiting circuit.

The TSH321 has internal electrostatic discharge (ESD) protection circuits and fulfills MILSTD883C-Class2.

#### ORDER CODE

| Part Number | Ton porature Range | Packane |

|-------------|--------------------|---------|

| TSH321I     | -40°C, +125°C      | •       |

D = Smai. O ול'הויף וּ ackage (SO) - alsף יי v vilal 'e in Tape & Reel (DT)

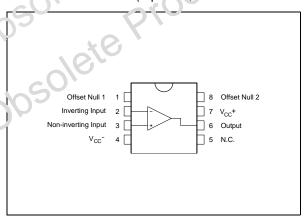

## PIN CONNECTIONS (top view)

October 2000 1/5

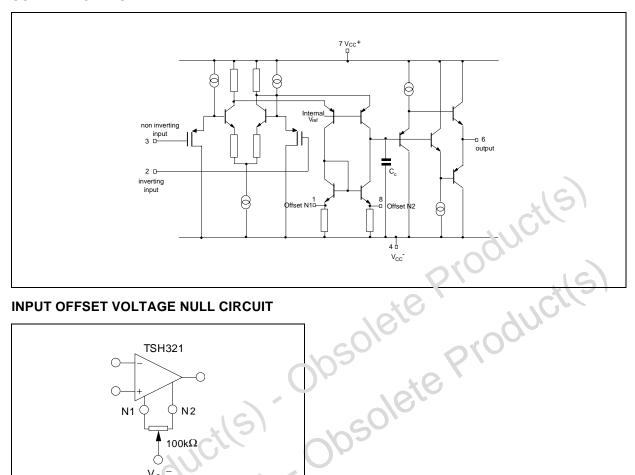

# **SCHEMATIC DIAGRAM**

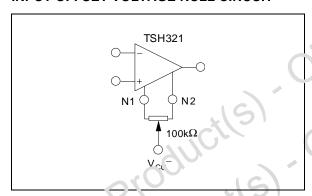

## INPUT OFFSET VOLTAGE NULL CIRCUIT

# MAXIMUM PATINGS

| Symbo             | Parameter                            | Value       | Unit |

|-------------------|--------------------------------------|-------------|------|

| ,\cc              | Supply Voltage                       | ±7          | V    |

| V <sub>id</sub>   | Differential Input Voltage           | ±5          | V    |

| V <sub>i</sub>    | Input Voltage                        | ±5          | V    |

| I <sub>in</sub>   | Current On Offset Null Pins          | ±20         | V    |

| T <sub>oper</sub> | Operating Free-Air Temperature range | -40 to +125 | °C   |

## **OPERATING CONDITIONS**

| Symbol          | Parameter                       | Value                                                           | Unit |

|-----------------|---------------------------------|-----------------------------------------------------------------|------|

| V <sub>cc</sub> | Supply Voltage                  | ±3 to ±6                                                        | V    |

| V <sub>ic</sub> | Common Mode Input Voltage Range | V <sub>CC</sub> <sup>-</sup> to V <sub>CC</sub> <sup>+</sup> -3 | V    |

**57** 2/5

# **ELECTRICAL CHARACTERISTICS**

$V_{CC} = \pm 5V$ ,  $T_{amb} = 25$ °C (unless otherwise specified)

| Symbol                          | Parameter                                                                                                            | Min.         | Тур.                 | Max.      | Unit    |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------|----------------------|-----------|---------|

| V <sub>io</sub>                 | Input Offset Voltage                                                                                                 |              | 0.5                  | 10        | mV      |

|                                 | $T_{min} \le T_{amb} \le T_{max}$                                                                                    |              |                      | 12        |         |

| $DV_{io}$                       | Input Offset Voltage Drift                                                                                           |              | 10                   |           | μV/°C   |

|                                 | $T_{min} \le T_{amb} \le T_{max}$ Input Bias Current                                                                 |              | 10                   | 200       |         |

| l <sub>ib</sub>                 | •                                                                                                                    |              | 2                    | 300       | pΑ      |

| l <sub>io</sub>                 | Input Offset Current                                                                                                 |              | 2                    | 200       | pA      |

| I <sub>cc</sub>                 | Supply Current, no load $ V_{CC} = \pm 5V $ $ V_{CC} = \pm 3V $                                                      |              | 23<br>21             | 30<br>28  | mA      |

|                                 | $V_{CC} = \pm 6V$ $T_{min} \le T_{amb} \le T_{max}$ $V_{CC} = \pm 5V$                                                |              | 25                   | 40<br>3.7 | 5)      |

|                                 | Large Signal Voltage Gain Vo = ±2.5V                                                                                 |              |                      | 10,       |         |

| Avd                             | R <sub>L</sub> = ∞                                                                                                   | 800          | 1300                 | <b>)</b>  | V/V     |

| Avu                             | $R_L = 100\Omega$                                                                                                    | 300          | 850                  |           | V/V     |

|                                 | $R_L = 50\Omega$                                                                                                     | 200          | 350                  |           | 16)     |

| $V_{icm}$                       | Input Common Mode Voltage Range                                                                                      | -5 to +2     | 5.5 to +2.5          |           | V       |

| CMR                             | Common-mode Rejection Ratio $V_{ic} = V_{icm min.}$                                                                  | 60           | 100                  | 1,10      | dB      |

| SVR                             | Supply Voltage Rejection Ratio $V_{CC} = \pm 5V$ to $\pm 3V$                                                         | 50           | 70                   | 70.       | dB      |

|                                 | Output Voltage $R_L = 100\Omega$                                                                                     | ±3           | +3.5                 |           |         |

| $V_{o}$                         | R <sub>L</sub> = 5002                                                                                                | ±2.8         | -3.7<br>+3.3         |           | V       |

| ۰0                              | 11( = 33)                                                                                                            | 12.0         | -3.5                 |           | v       |

|                                 | $T_{min} \le T_{amb} \le T_{max}$ $R_L = 100\Omega$ $R_L = 50\Omega$                                                 | ±2.9<br>±2.7 |                      |           |         |

| I <sub>o</sub>                  | Output Short Circuit Current Via = ±1V, Vo = 0V                                                                      | ±50          | ±100                 |           | mA      |

| GBP                             | Gain Bandwidth Pr. Q.ICI $A_{VCL} = 100 \ R_L = 100 \Omega$ , $C_L = 15pF$ , $f = 7.5MHz$                            |              | 300                  |           | MHz     |

| SR                              | Slew Rate $V_{in}$ =1V, $A_{VCL}$ = 2, $R_L$ = 100 $\Omega$ , $C_L$ = 15pF                                           | 200          | 400                  |           | V/μs    |

|                                 | Equivalent Input Voltage Noise $R_s = 50\Omega$ $f_o = 1 \text{kHz}$                                                 |              | 20                   |           | ->///   |

| e <sub>n</sub>                  | $f_o = 1k0Hz$ $f_o = 100kHz$ $f_o = 1MHz$                                                                            |              | 18.2<br>18.1<br>18.2 |           | nV/√Hz  |

| K <sub>ov</sub>                 | Overshoot $V_{in} = \pm 1V$ , $A_{VCL} = 2$ , $R_L = 100\Omega$ , $C_L = 15pF$                                       |              | 15                   |           | %       |

| t <sub>s</sub>                  | Settling Time 0.1% <sup>1)</sup> $V_{in} = \pm 1V, A_{VCL} = -1$                                                     |              | 60                   |           | ns      |

| t <sub>r</sub> , t <sub>f</sub> | Rise and Fall Time (see note 1) $V_{in} = \pm 100 \text{mV}, A_{VCL} = 2$                                            |              | 2                    |           | ns      |

| t <sub>d</sub>                  | Delay Time (see note 1) $V_{in} = \pm 100 \text{mV}, A_{VCL} = 2$                                                    |              | 2                    |           | ns      |

| φm                              | Phase Margin $A_{VM} = 2$ , $R_L = 100\Omega$ , $C_L = 15pF$                                                         |              | 45                   |           | Degrees |

| THD                             | Total Harmonic Distortion $A_{VCL} = 10$ , $f = 1$ kHz, $V_0 = \pm 2.5$ V, no load                                   |              | 0.02                 |           | %       |

| FPB                             | Full Power Bandwidth $^{2)}$<br>Vo = 5Vpp, R <sub>L</sub> = 100 $\Omega$<br>Vo = 2Vpp, R <sub>L</sub> = 100 $\Omega$ |              | 26<br>64             |           | MHz     |

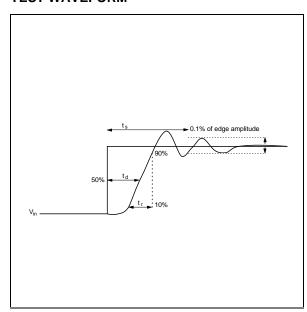

See test waveform figure

<sup>2.</sup> Full power bandwidth =

SR

Π Vopp

## **TEST WAVEFORM**

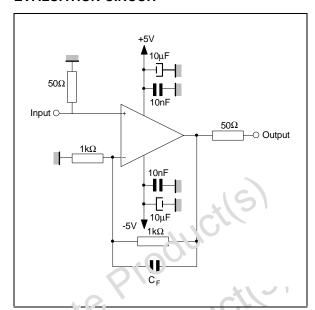

#### PRINTED CIRCUIT LAYOUT

As for any high frequency device, a few rules must be observed when designing the PCB to get the best performances from this high speed op amp.

From the most to the least important points :

- Each power supply lead has to be bypassed to ground with a 10n. ceramic capacitor very close to the Gevice and a 10μF tantalum capacitor.

- ☐ To provide low inductance and low resistance common teturn, use a ground plane or common point return for power and signal.

- □ All เอลช์s must be wide and as short as poss ible especially for op amp inputs. This is in

## **EVALUATION CIRCUIT**

order to decrease parasitic capacitance and inductance.

- ☐ Use small resistor values to decrease time constant with parasitic capacitance.

- ☐ Choose component sizes as small as possible (SMD).

- On output, decrease capacitor load so as to avoid circuit stability being degraded which may cause oscillation. You can also add a serial resistor in order to minimise its influence.

- One can add in parallel with feedback resistor a few pF ceramic capacitor C<sub>F</sub> adjusted to optimize the settling time.

4/5

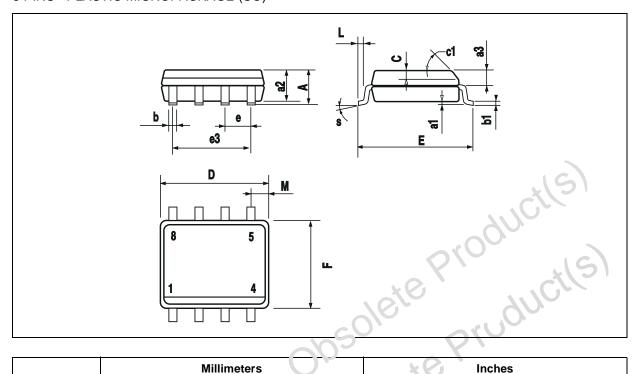

## **PACKAGE MECHANICAL DATA**

8 PINS - PLASTIC MICROPACKAGE (SO)

| Dim   | Millimeters |        |       | Inches |       |       |

|-------|-------------|--------|-------|--------|-------|-------|

| Dim.  | Min.        | Тур.   | Max.  | Min.   | Тур.  | Max.  |

| Α     |             | 1(5)   | 1.75  |        |       | 0.069 |

| a1    | 0.1         | . C.L. | 0.25  | 0.004  |       | 0.010 |

| a2    | 41          |        | 1.65  |        |       | 0.065 |

| a3    | 0.65        |        | 0.85  | 0.026  |       | 0.033 |

| b     | (1.35       | 115    | 0.48  | 0.014  |       | 0.019 |

| b1    | 0.19        |        | 0.25  | 0.007  |       | 0.010 |

| C * 6 | 0.25        | 110    | 0.5   | 0.010  |       | 0.020 |

| C     |             |        | 45° ( | (typ.) |       |       |

| D.    | 4.8         |        | 5.0   | 0.189  |       | 0.197 |

| E     | 5.8         |        | 6.2   | 0.228  |       | 0.244 |

| е     | 2, '        | 1.27   |       |        | 0.050 |       |

| e3    | )           | 3.81   |       |        | 0.150 |       |

| F     | 3.8         |        | 4.0   | 0.150  |       | 0.157 |

| 57    | 0.4         |        | 1.27  | 0.016  |       | 0.050 |

| М     |             |        | 0.6   |        |       | 0.024 |

| S     | 8° (max.)   |        |       |        |       |       |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

© The ST logo is a registered trademark of STMicroelectronics

© 2000 STMicroelectronics - Printed in Italy - All Rights Reserved STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco Singapore - Spain - Sweden - Switzerland - United Kingdom © http://www.st.com