# Sno Edge $50^{\circ}$

# Intel MAX 10 FPGA System on Module

User's Manual and Release Notes

April 11, 2022

| Version | Date           | Author         | Changes                |

|---------|----------------|----------------|------------------------|

| 0.7     | April 6, 2022  | Steve Phillips | Initial Version        |

| 1.0     | April 11, 2022 | Steve Phillips | First official release |

|         |                |                |                        |

|         |                |                |                        |

# **Table of Contents**

| 1      | INTRODUCTION                                                                                     | .5          |

|--------|--------------------------------------------------------------------------------------------------|-------------|

| 2      | PROGRAMMING SNO EDGE                                                                             | .6          |

| 2      | Microcontroller Programming         1.1       USB Programming         1.2       FTDI Programming | 6           |

| 2<br>2 | FPGA Programming                                                                                 | 7<br>8<br>9 |

| 3      | GENERAL TECHNICAL SPECIFICATIONS                                                                 | 11          |

| 3.1    | 3.3V I/O                                                                                         | 11          |

| 3.2    | ADC                                                                                              | 11          |

| 3.3    | Analog Compare                                                                                   | 12          |

| 3.4    | Power                                                                                            | 12          |

| 3.5    | Pin 13 LED                                                                                       | 12          |

| 4      | XCELERATOR BLOCKS (XBS)                                                                          |             |

| 4.1    | Floating Point                                                                                   | 13          |

| 4.2    | Servo Control                                                                                    |             |

| 4.3    | Quadrature                                                                                       |             |

| 5      | PIN MAPPING                                                                                      | 15          |

| 6      | EXTENDED INTERRUPTS                                                                              | 18          |

| 6.1    | GPIO Port Pin Change Detection                                                                   | 18          |

| 6.2    | Pin Change Interrupts                                                                            | 18          |

| 6.3    | OpenXLR8 Interrupts                                                                              | 19          |

| 6.4    | Extended IRQs                                                                                    | 20          |

| 6.5          | Setup and Usage                                                | 21 |

|--------------|----------------------------------------------------------------|----|

| 6.6          | Example Interrupt Sketch                                       | 21 |

| 7 F          | REGISTER SUMMARY                                               | 24 |

| 7.1          | Sno Edge and XB Register Descriptions                          |    |

| 7.1.         | 1 Register Access Definitions                                  |    |

| 7.1.         | 2 Ports A, E and G                                             |    |

| 7.1.         |                                                                |    |

| 7.1.         |                                                                |    |

| 7.1.         |                                                                |    |

| 7.1.         |                                                                |    |

| 7.1.         | 1 0                                                            |    |

| 7.1.         |                                                                |    |

| 7.1.         |                                                                |    |

| 7.1.         |                                                                |    |

| 7.1.         | 0 0                                                            |    |

| 7.1.         | 1 0                                                            |    |

| 7.1.         | , , , , , , , , , , , , , , , , , , , ,                        |    |

| 7.1.<br>7.1. | , , , , , , , , , , , , , , , , , , , ,                        |    |

| 7.1.         | • •                                                            |    |

| 7.1.         |                                                                |    |

| /.1.         | $17 \qquad 5VFWH, 5VFWL, 5VCK - 5e1VO XD Registels$            |    |

| 7.2          | Using the Sno Edge Registers in Software                       |    |

| 8 9          | SCHEMATICS AND OTHER RESOURCES                                 | 41 |

|              |                                                                |    |

| 9 (          | CREDITS                                                        |    |

| 10 A         | APPENDIX A – ARDUINO IDE INSTALLATION AND RUNNING TEST PROGRAM | 43 |

| 10.1         | Installing Arduino IDE                                         |    |

|              | 1.1 Microsoft Windows                                          |    |

| 10.1         |                                                                |    |

| 10.3         |                                                                |    |

| 10.2         | FTDI Driver Installation                                       | 43 |

| 10.3         | Installing Sno Edge Board Package and Libraries                |    |

| 10.3         |                                                                |    |

| 10.3         | 3.2 Sno Edge Libraries                                         |    |

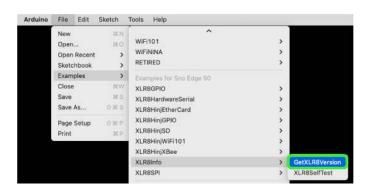

| 10.4         | Running an Example Sketch/Program                              | 47 |

# **1** Introduction

Sno Edge 50 is is an Intel MAX 10 FPGA System on Module (SOM) that includes an 8-bit AVR compatible microcontroller integrated on the FPGA for easy programmability and optimized access to the FPGA fabric for custom hardware functionality.

Based on Alorium Technology's very popular embeddable Snō FPGA module, the Sno Edge 50 enhances the powerful features and functionality of Snō with significantly increased digital I/O, additional ADCs, and more FPGA logic gates for custom Xcelerator Block development.

All of this functionality is packaged in a 200-pin SODIMM form factor for the ultimate in low-profile physical integration.

## Note:

Sno Edge 50 is the first release in a planned roadmap of "Sno Edge" boards and is named based on the fact that it has a 50K LE MAX 10 FPGA. Additional variations of the design may be produced based on customer demand and FPGA availability.

For the remainder of this document, Sno Edge 50 is referred to as simply as "Sno Edge", and this label can be considered synonomous for the purposes of this manual.

# 2 Programming Sno Edge

## 2.1 Microcontroller Programming

The embedded microcontroller on Sno Edge is easily programmable with the Aruino IDE. Refer to the Appendix in Section 10 of this document for Arduino IDE installation instructions if you don't already have it installed on your development machine.

Other programming tools such as Atmel Studio, PlatformIO/VSCode, and others may also work for programming Sno Edge. However, Arduino is the only officially supported programming environment for Sno Edge.

#### 2.1.1 USB Programming

Sno Edge is designed to be programmed via a USB connection.

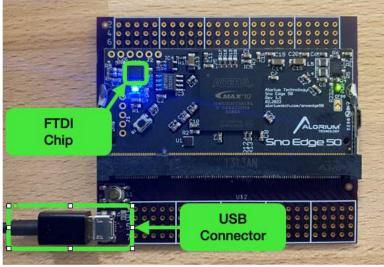

There is an on-board FTDI USB-to-Serial translator chip that converts USB signals from the edge connector pins to serial UART commands used for programming the microcontroller.

**Note:** There is NO USB connector directly on Sno Edge. The physical USB connection will be made on the carrier board that is being used with Sno Edge.

For example, this image shows the USB connector on Alorium's Sno Edge test breakout board:

Figure 2: USB Connections

## 2.1.2 FTDI Programming

Sno Edge also has a 6-pin FTDI header at the top of Sno Edge that is used for initial microcontroller programming and test during the manufacturing process.

Figure 3: FTDI Vias

The FTDI interface can be used for general serial programming of microcontroller, as well; however, it does require using A USB-to-FTDI adapter of some kind. One of our favorites is the <u>SparkFun Beefy 3 Basic FTDI Breakout</u>.

## 2.2 FPGA Programming

The FPGA on Sno Edge comes pre-programmed with an image that includes the microcontroller as well as a pre-configured set of Xcelerator Blocks developed by Alorium Technology.

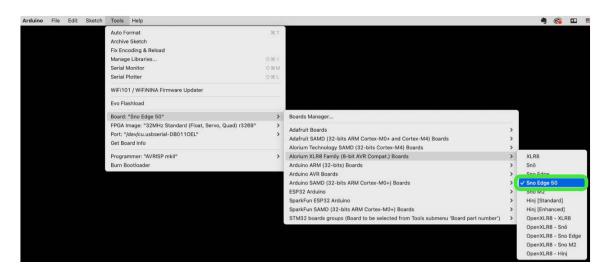

Alternate images can be uploaded directly through the Arduino IDE or accessed via our GitHub repo and flashed to the FPGA using a command-line program as described below.

#### 2.2.1 Updating the FPGA Image

Sno Edge ships with a standard FPGA image that includes the 8-bit microcontroller and a small set of built-in Xcelerator Blocks.

This image can be updated with other images provided by Alorium Technology by using the "Burn Bootloader" command in the Arduino or by running a standalone command-line program.

Video Demonstration Examples

#### NOTE:

The following videos were originally created for our XLR8 board as demonstrations for how to upload new FPGA images from the Arduino IDE or with our command line program. The process for Sno Edge 50 can be accomplished by selecting Sno Edge 50 as the board, instead of XLR8.

Demonstration videos using Sno Edge will be available soon on our YouTube channel, and this manual will be updated to reflect the new tutorials.

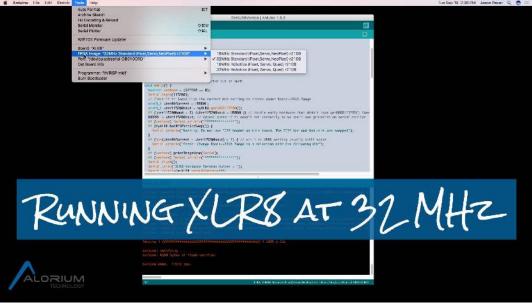

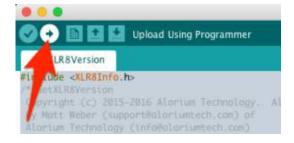

2.2.1.1 Flashing A New FPGA Image via Arduino IDE

Figure 4: Arduino IDE Video

#### 2.2.1.2 Flashing A New FPGA Image Using the Command-Line

| ScreenFlow File Edit Mark Insert Font Actions Arrange View Window Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| <pre>reserve: 1 junu 1447 14338 60 10 203 148 213 248 148 248 248 248 248 248 248 248 248 248 2</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |

| <ul> <li>2): portydevice.asterial=0002008</li> <li>Prayas dea: solid (): (): (): (): (): (): (): (): (): ():</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1-00011000   |

| Roard Type: 3188<br>PPGA Image: 36 Witz -78008                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |

| How to Upload FPGA Images Using the state of | Command Line |

| With a Four Quadrature FPGA Image                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 7 1 77 1   |

#### Figure 5: Command Line Video

## 2.2.2 Restoring Factory FPGA Image

The FPGA on Sno Edge can hold two different FPGA images. One of those, the User Image, can be reconfigured with new images to take advantage of increased functionality as new features are

introduced and released. The other image, the Factory Image, is never changed, and is typically unused unless the primary image 1 becomes corrupted.

If necessary, a "factory reset" of Sno Edge can be performed by bridging the two sides of the split CFG0 pad while applying power to the board. It only takes a momentary grounding to cause this to happen. See Figure 6 for the location of the CFG0 pad.

After power-up, the Factory Image will be loaded. However, any loss of power to the board will result in the corrupted image being reloaded. Therefore, the user will want to flash a known-good image into the User Image before proceeding.

2.2.2.1 Locating CFG0

## 2.2.3 Creating Custom FPGA Images with OpenXLR8

As with all of our products, the FPGA can be programmed with your own custom FPGA image by using our OpenXLR8 FPGA process. OpenXLR8 is the methodology that allows users of all our XLR8 products to develop their own custom <u>Xcelerator Blocks</u> and integrate them into the FPGA.

You can learn more about how to use OpenXLR8 here:

Introduction to OpenXLR8 <https://aloriumtech.com/openxlr8/>

## 2.2.4 Bare-Metal FPGA Programming

For advanced FPGA users, Sno Edge does have a JTAG header that can be used for creating baremetal FPGA designs and directly flashing a new image to the FPGA.

Use of the JTAG interface will require that user has the appropriate JTAG programming hardware such as the JTAG Blaster programmer from Intel.

Figure 7: JTAG Vias

## **IMPORTANT NOTE!!**

If the JTAG interface is used to load the MAX10 FPGA with a custom image, it is possible to erase the production Sno Edge functionality, deleting the factory production image and the integrated 8-bit microcontroller subsystem. In this scenario, loading images through the Arduino IDE would no longer be possible.

The Sno Edge FPGA has been designed to be modified and extended by using Alorium's OpenXLR8 Methodology. This flow provides a path to create custom XBs in the FPGA fabric that can easily interface to the on-chip microcontroller and preserve full factory functionality.

Learn More about OpenXLR8 here: https://www.aloriumtech.com/openxlr8

# **3** General Technical Specifications

# 3.1 3.3V I/O

Sno Edge is a 3.3V device, and users are cautioned to only connect to other 3.3V devices.

The Sno Edge does not come equipped with pull-up resistors so the user is required to add them physically as needed, except for the dedicated SDA and SCL pins which have 1K ohm pull-ups.

# 3.2 ADC

Sno Edge supports 16 ADC inputs via two eight input ADC modules. The ADCSRB register now supports the MUX5 bit (bit 5) which is used to select which ADC input is read.

The exact mapping of the ADC inputs is show in Figure 8.

| ADC Input | ADCSRB[5] | ADMUX[2:0] | FPGA Input | Edge      | Arduino Label |

|-----------|-----------|------------|------------|-----------|---------------|

|           | MUX5      | MUX[2:0]   |            | Connector |               |

| 0         | 0         | 0          | ADC1[1]    | 26        | A0            |

| 1         | 0         | 1          | ADC1[2]    | 24        | A1            |

| 2         | 0         | 2          | ADC1[3]    | 31        | A2            |

| 3         | 0         | 3          | ADC1[4]    | 29        | A3            |

| 4         | 0         | 4          | ADC1[5]    | 25        | A4            |

| 5         | 0         | 5          | ADC1[6]    | 23        | A5            |

| 6         | 0         | 6          | ADC1[7]    | 19        | A6            |

| 7         | 0         | 7          | ADC1[8]    | 17        | A7            |

| 8         | 1         | 0          | ADC2[1]    | 16        | A8            |

| 9         | 1         | 1          | ADC2[2]    | 13        | A9            |

| 10        | 1         | 2          | ADC2[3]    | 20        | A10           |

| 11        | 1         | 3          | ADC2[4]    | 22        | A11           |

| 12        | 1         | 4          | ADC2[5]    | 7         | A12           |

| 13        | 1         | 5          | ADC2[6]    | 5         | A13           |

| 14        | 1         | 6          | ADC2[7]    | 11        | A14           |

| 15        | 1         | 7          | ADC2[8]    | 14        | A15           |

Figure 8: Dual ADC Input Mapping

An Arduino variant has been defined for the Sno Edge so the user does not need to be concerned with the mapping of ADC inputs to ADCSRB/ADMUX register fields. The user can simply reference the Arduino Label in their sketch. For example: analogRead(A12), to read the ADC input on Edge Connector pin 7.

Sno Edge is only able to measure against an internal 3.3V reference. The ADC inputs themselves are limited to a max input voltage of 2.5 volts.

The temperature sensor are not implemented (ADMUX=1000). Using the ADC to read the bandgap (ADMUX=1110) does not actually do a measurement but returns a calculated value equivalent to 1.1/Aref.

Using the ADC to read ground (ADMUX=1111) does not actually do a measurement and instead returns a fixed value of 0.

# 3.3 Analog Compare

Sno Edge does not support the Analog Compare function that is found in the ATmega328p. The ACME bit and analog compare triggering (ADTS=001) of the ADCSRB (0x7B) register, the ACSR (0x30) register, and the DIDR1 (0x7F) register are not implemented.

If an analog compare function is desired, using the OpenXLR8 platform, a user could implement an analog compare function that is very similar to the ATMega328's, although the pin voltage would need to be limited to 3.3V.

# 3.4 Power

There are 3 ways to power the Sno Edge module:

- Connect a 3.3V FTDI breakout board or cable to the FTDI interface

- Supply 5V via pin 2 of the SODIMM connector (this is intended to come from a USB connector on the system board). This will use an on-board 3.3V regulator to supply power to the FPGA and other components on the board, and is limited to 500mA

- Supply 3.3V via the dedicated power pins on the SODIMM connector (this is the most robust way to power the Sno Edge board)

# 3.5 Pin 13 LED

As with many other Arduino-compatible boards, digital pin 13 is used for both the on-board LED as well as the SPI clock, SCK. On Sno Edge, SCK and the LED are driven from separate FPGA pins which are logically equivalent but physically separate, in order to avoid the extra loading the LED can cause.

# 4 Xcelerator Blocks (XBs)

Xcelerator Blocks are custom hardware blocks implemented within the Sno Edge FPGA chip and are tightly integrated with the ATmega328 clone that is also implemented inside the FPGA chip.

These custom hardware blocks can implement almost any functionality you can dream up, and can then be loaded into the Sno Edge with the Arduino toolset. Since an FPGA can be reprogrammed many times, a single Sno Edge can be reconfigured to incorporate different XBs depending on the project requirements.

Sno Edge ships with three sample XBs: Floating Point, Quadrature, and Servo Control. The software libraries are delivered as .zip files from our github site (<u>https://github.com/AloriumTechnology</u>). They are installed like other Arduino .zip libraries as described here (<u>https://www.arduino.cc/en/Guide/Libraries</u>).

# 4.1 Floating Point

As an 8 bit microcontroller, the ATmega328p struggles with floating point math. The Floating Point XB provides functions that will give you floating point results in about ¼ the time that it takes software floating point to get the same answer. Available functions include add, subtract, multiply, and divide.

# 4.2 Servo Control

It is common for the standard Servo.h library to cause jitter in the servo control due to timing uncertainties caused by interrupt processing. The Servo Control XB completely eliminates this jitter by putting a dedicated hardware timer behind Port K pins. The XLR8Servo.h library is a drop-in replacement for the standard Servo.h library, so taking advantage of this XB is as simple as changing one line in your sketch from #include <Servo.h> to #include <XLR8Servo.h>

The servos are connected to the physical pins starting with Port KA, pin 0, going through port KD, pin 7, with each servo connected to the one sequential pins in order. So, servo 0 is tied to KA[0], sevo 1 is tied to KA[1], servo 31 is tied to KD[7], etc. You can instantiate an array like this: Servo servo[32];

# 4.3 Quadrature

The Sno Edge builtin Quadrature XB provides up to 16 Quadrature encoders. These are connected to Port J, which is the concatination of ports {JD,JC,JB,JA}.

As quadrature objects are instantiated, they are created sequentially. I.e., the first quadrature object will control quadrature 0 in the fabric, the second will control quadrature 1, etc., through quadrature 16.

The quadratures are connected to the physical pins starting with Port JA, pin 0, going through port JD, pin 7, with each quadrature connected to the two sequential pins in order. So, quadrature 0 is tied to JA[1:0], quadrature 15 is tied to JD[7:6], etc. The simplest way to manage multiple quadratures in an application is to create an array of quadrature objects. You can instantiate an array like this:

Quadrature quadratures[16];

The XLR8Quadrature library is included with the line

#include <XLR8Quadrature.h>

Once you instantiate an quadrature object, the quadrature is enabled by default. The software library then allows you to disable & re-enable the quadratures, and read the count and rate values of the quadrature. By default, the quadrature samples every 200ms to get the rate, but can be set to sample every 20ms instead.

# 5 Pin Mapping

With a handful of exceptions, the pins are arranged into 18 ports, each of which can be up to 8 bits wide. They can be organized into four groups:

- 1. First there are the standard Arduino Uno ports: D, B, and C. Note that ports B and C are only 6 bits wide. In the case of Port C this creates a gap in the "D" pin numbering since there is no C[7:6] which would correspond to D pins [21:20].

- 2. Then there are the standard Sno extended ports A, E, and G. All boards in the Sno family implement these three extended ports.

- 3. Following the Sno extended ports are the J and K ports. There are four J ports (JA, JB, JC, and JD) and four K ports (KA, KB, KC, and KD). These can be treated in software either as 32 bit ports or as four 8 bit ports. The Sno Edge variant provides support for both.

- 4. Finally, the PL port provide four pins that can also be used as two differential PLL inputs

Aside from the port pins, there are various non-port pins that provide specific functionality:

- Clock

- Reset

- ADC

- ADC Reference

- I2C

- Serial

In the following figures a Color Key is used to indicate how the various types of pins are organized:

| Color Key                 |

|---------------------------|

| Ground                    |

| Power                     |

| Special Functions         |

| ADC1                      |

| ADC2                      |

| Port D - Non-Differential |

| Port B - Non-Differential |

| GPIO Port - Differential  |

| GPIO Port - Differential  |

| PLL Port - Differential   |

Figure 9: Pin Map Color Key

In Figure 10 the ports are enumerated and the bit ranges are specified. Of special interest is the numbering gap in the D Nums column at [21:20], as discussed above. The XB Busses, which are used in the OpenXLR8 module, do not have a gap at [21:20] and so are offset by 2 from the D Nums for pins above 19.

The Int Bit column indicates which bit in the SPCIFR register will get set when there is a pin change interrupt for that port.

The GPIO column indicates whether the pins in that port are differential pairs or not. A "D" indicates a differential pair port. By default all pins are normal non-differential GPIO pins in these ports, but it is possible in the OpenXLR8 methodology to change the configuration of those pins to be differential.

| Port Name | Port Bits | D Nun | ıs  | XB Busses | Int Bit | GPIO |

|-----------|-----------|-------|-----|-----------|---------|------|

| D         | 8         | 7:    | 0   | [7:0]     |         | S    |

| В         | 6         | 13:   | 8   | [13:8]    |         | S    |

| С         | 6         | 19:   | 14  | [19:14]   |         | D    |

| А         | 6         | 27:   | 22  | [25:20]   | 0       | D    |

| E         | 6         | 33:   | 28  | [31:26]   | 1       | D    |

| G         | 8         | 41:   | 34  | [39:32]   | 2       | D    |

| JA        | 8         | 49:   | 42  | [47:40]   | 3       | D    |

| JB        | 8         | 57:   | 50  | [55:48]   | 3       | D    |

| JC        | 8         | 65:   | 58  | [63:56]   | 3       | D    |

| JD        | 8         | 73:   | 66  | [71:64]   | 3       | D    |

| KA        | 8         | 81:   | 74  | [79:72]   | 4       | D    |

| KB        | 8         | 89:   | 82  | [87:80]   | 4       | D    |

| KC        | 8         | 97:   | 90  | [95:88]   | 4       | D    |

| KD        | 8         | 105:  | 98  | [103:96]  | 4       | D    |

| PL        | 4         | 109:  | 106 | [107:104] | 5       | D    |

**Figure 10: Port Numbering**

In Figure 10, the mapping between the FPGA pins and the Sno Edge connector pins is shown. The table is split two halves representing the odd side and the even side of the connector. For each connector pin, the following information is shown:

| Column             | Description                                                                                                                        |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Edge Connector Pin | The pin number of the edge connector                                                                                               |

| FPGA D Pin         | The "D" pins are numbered from 0 up to 109. These numbers can be used directly to specify pins in functions such as digitalWrite() |

| FPGA Port Bit      | The pins are all arranged into ports of up to 8 bits. The Port Bit                                                                 |

|                    | indicats which pin in a port                                                                                                       |

| FPGA Pad           | The FPGA Pad specifies which physical pin on the FPGA the                                                                          |

|                    | corresponding signal is using.                                                                                                     |

| FPGA Pin Type      | The Pin Type indicates any important type desciptor for FPGA Pad,                                                                  |

|                    | such as Diff pair, GND, or VCC                                                                                                     |

| Special Function   | Special Function uiindicates any special note about that pin                                                                       |

| <b>5</b> I         | such as Diff pair, GND, or VCC                                                                                                     |

**Figure 11: Edge Connector Table Information**

In Figure 12, each differential pair is indicated by a box around the two pins. For instance, edge pins 30 and 32 are a differential pair.

| Special             | FPGA                |             | FPGA                | FPGA        | Edge       | Edge       | FPGA       | FPGA               | FPGA       | FPGA             | Specia             |

|---------------------|---------------------|-------------|---------------------|-------------|------------|------------|------------|--------------------|------------|------------------|--------------------|

| Function<br>ADC_REF | Pin Type<br>ADC_REF | PAD<br>E4 / | Port Bit<br>ADC_REF | D Bit<br>na | Pin<br>1   | Pin<br>2   | D Bit      | Port Bit           | PAD        | Pin Type<br>5.0V | Function           |

|                     | GND                 |             |                     |             | 3          | 4          |            |                    |            | USB-             | Serial             |

| ADC2in6<br>ADC2in5  | L6P<br>L6N          |             | ADC2[6]<br>ADC2[5]  | na<br>na    | 5          | 6<br>8     |            |                    |            | USB+<br>GND      | Serial             |

|                     | GND                 |             |                     |             | 9          | 10         | na         | RESET_N            | B10        | RESETN           | RESET_N            |

| ADC2in7<br>ADC2in2  | L8N<br>L8P          |             | ADC2[7]<br>ADC2[2]  | na<br>na    | 11         | 12         | na         | ADC2[8]            | C3         | GND<br>L2P       | ADC2in8            |

|                     | GND                 |             |                     |             | 15         | 16         | na         | ADC2[1]            |            | L2N              | ADC2in1            |

| ADC1in8<br>ADC1in7  | L7P<br>L7N          |             | ADC1[8]<br>ADC1[7]  | na<br>na    | 17         | 18<br>20   | na         | ADC2[3]            | E3         | GND<br>L4N       | ADC2in:            |

|                     | GND                 |             |                     |             | 21         | 22         | na         | ADC2[4]            | F2         | L4P              | ADC2in4            |

| ADC1in6<br>ADC1in5  | LSP<br>LSN          |             | ADC1[6]<br>ADC1[5]  | na<br>na    | 23         | 24<br>26   | na<br>na   | ADC1[2]<br>ADC1[1] | F4<br>F5   | L1P<br>L1N       | ADC1in2<br>ADC1in1 |

|                     | GND                 |             |                     |             | 27         | 28         |            |                    |            | GND              |                    |

| ADC1in4<br>ADC1in3  | L3P<br>L3N          |             | ADC1[4]<br>ADC1[3]  | na<br>na    | 29         | 30<br>32   | 14<br>15   | C[0]<br>C[1]       | J2<br>J3   | L22P<br>L22N     |                    |

| - Dellins           | GND                 |             |                     |             | 33         | 34         |            |                    |            | GND              |                    |

|                     | L20P<br>L20N        | H6<br>35    | C[2]<br>C[3]        | 16<br>17    | 35         | 36<br>38   | 18<br>19   | C[4]<br>C[5]       | K2<br>L1   | L29P<br>L29N     |                    |

|                     | GND                 |             | e[3]                | 11          | 39         | 40         | 1.5        | (J)                |            | GND              |                    |

|                     | Connecto<br>GND     | r Gap       |                     |             | 41         | 42         |            |                    | Cor        | GND GND          |                    |

|                     | L36N                | J6          | A[0]                | 22          | 43         | 44         | 24         | A[2]               | К5         | L41N             |                    |

|                     | L36P<br>GND         | K6          | A[1]                | 23          | 45         | 46         | 25         | A[3]               | L6         | L41P<br>GND      |                    |

|                     | L37P                | L2          | A[4]                | 26          | 49         | 50         | na         | Clock              | L3         | FPGA_CLK_F       | CL                 |

|                     | L37N<br>GND         | M2          | A[5]                | 27          | 51<br>53   | 52<br>54   | na         | Clock_n            | M3         | FPGA_CLK_N       | CLI                |

|                     | B2P                 | R1          | E[0]                | 28          | 55         | 56         | 30         | E[2]               | P1         | L38P             |                    |

|                     | B2N<br>GND          | P2          | E[1]                | 29          | 57<br>59   | 58<br>60   | 31         | E[3]               | N2         | L38N<br>GND      |                    |

|                     | B6P                 | T2          | E[4]                | 32          | 61         | 62         | 34         | G[0]               | R2         | B4P              |                    |

|                     | B6N<br>GND          | T3          | E[5]                | 33          | 63         | 64         | 35         | G[1]               | R3         | B4N<br>GND       |                    |

| PLL                 | L59N                | N3          | PL[0]               | 106         | 65<br>67   | 66<br>68   | 36         | G[2]               | R4         | B5N              |                    |

| PLL                 | L59P                | N4          | PL[1]               | 107         | 69         | 70         | 37         | G[3]               | P5         | B5P              |                    |

|                     | GND<br>B1N          | P4          | G[4]                | 38          | 71         | 72         | 40         | G[6]               | T4         | GND<br>B14P      |                    |

|                     | B1P                 | N5          | G[5]                | 39          | 75         | 76         | 41         | G[7]               | Т5         | B14N             |                    |

| no diff pair        | GND<br>B13P         | R5          | D[0]                | 8           | 77         | 78<br>80   | 1          | D[1]               | R6         | GND<br>B13N      | no diff pair       |

|                     | 3.3V                |             |                     |             | 81         | 82         |            |                    |            | 3.3V             |                    |

|                     | B16P<br>B16N        | P6<br>R7    | J[0]<br>J[1]        | 42<br>43    | 83         | 84<br>86   | 44<br>45   | J[2]<br>J[3]       | R8<br>T8   | B17P<br>B17N     |                    |

|                     | 3.3V                |             |                     |             | 87         | 88         |            |                    |            | 3.3V             |                    |

| no diff pair        | B15P<br>B3N         | L8<br>M6    | D[2]<br>J[4]        | 2<br>46     | 89<br>91   | 90<br>92   | 3          | D[3]<br>J[6]       | M7<br>M8   | B15N<br>B20N     | no diff pair       |

|                     | B3P                 | L7          | J[4]                | 40          | 93         | 94         | 40         | 3[7]               | M9         | B20P             |                    |

| no diff pain        | 3.3V<br>B18P        | P8          | D[4]                | 4           | 95<br>97   | 96<br>98   | 5          | D[5]               | P9         | 3.3V<br>B18N     | no diff pair       |

| no diff pair        | B16P<br>B36P        | L9          | J[8]                | 50          | 99         | 100        | 52         | J[10]              | R9         | B19P             | no diff pair       |

|                     | B36N<br>3.3V        | M10         | J[9]                | 51          | 101        | 102        | 53         | J[11]              | Т9         | B19N<br>3.3V     |                    |

|                     | B22P                | R10         | J[12]               | 54          | 105        | 104        | 56         | J[14]              | P10        | B34N             |                    |

| <b>CD 1</b>         | B22N                | T11         | J[13]               | 55          | 107        | 108<br>110 | 57         | J[15]              | P11        | B34P<br>B57P     |                    |

| SDA                 | B57N<br>3.3V        | M11         | SDA                 | na          | 109        | 110        | na         | SCL                | L10        | 3.3V             | SCI                |

|                     | B35N                | R11         | J[16]               | 58          | 113        | 114        | 60         | J[18]              | P12        | B37P             |                    |

|                     | B35P<br>3.3V        | R12         | J[17]               | 59          | 115        | 116<br>118 | 61         | J[19]              | P13        | B37N<br>3.3V     |                    |

|                     | R2P                 | T14         | D[6]                | 6           | 119        | 120        | 7          | D[7]               | T15        | R2N              | no diff pair       |

|                     | GND<br>R1N          | R14         | J[20]               | 62          | 121        | 122        | 64         | 3[22]              | N14        | GND<br>R27P      |                    |

|                     | R1P                 | P14         | J[21]               | 63          | 125        | 126        | 65         | J[23]              | P15        | R27N             |                    |

|                     | GND<br>R29N         | P16         | J[24]               | 66          | 127<br>129 | 128<br>130 | 8          | B[0]               | L12        | GND<br>R25N      | no diff pair       |

|                     | R29P                | N16         | J[25]               | 67          | 131        | 132        |            |                    |            | GND              | no uzrr puzr       |

|                     | GND<br>R33P         | M16         | J[28]               | 70          | 133<br>135 | 134<br>136 | 68<br>69   | J[26]              | M14<br>M15 | R28N<br>R28P     |                    |

|                     | R33P<br>R33N        | M16<br>L16  | J[28]<br>J[29]      | 70          | 135        | 136        |            | J[27]              |            | GND              |                    |

|                     | GND                 |             |                     |             | 139        | 140        | 72         | J[30]              | K14        | R32P             |                    |

|                     | R30P<br>R30N        | K11<br>K12  | κ[0]<br>κ[1]        | 74<br>75    | 141<br>143 | 142        | 73         | J[31]              | L15        | R32N<br>GND      |                    |

|                     | GND                 |             |                     |             | 145        | 146        | 76         | K[2]               | J11        | R38P             |                    |

| no diff pair        | R39N<br>GND         | K15         | B[1]                | 9           | 147<br>149 | 148<br>150 | 77         | K[3]               | J12        | R38N<br>GND      |                    |

|                     | R40P                | J15         | K[4]                | 78          | 151        | 152        | 80         | K[6]               | H15        | R41P             |                    |

|                     | R40N<br>GND         | J16         | K[5]                | 79          | 153<br>155 | 154<br>156 | 81         | K[7]               | H16        | R41N<br>GND      |                    |

|                     | R44P                | H11         | K[8]                | 82          | 157        | 158        | 84         | K[10]              | G11        | R50P             |                    |

|                     | R44N<br>GND         | H12         | K[9]                | 83          | 159<br>161 | 160<br>162 | 85         | K[11]              | G12        | R50N<br>GND      |                    |

| pair w/170          | R46N                | G15         | B[2]                | 10          | 161        | 162        | 86         | K[12]              | G16        | R47P             |                    |

|                     | GND                 |             |                     |             | 165        | 166        | 87         | K[13]              | F16        | R47N             |                    |

|                     | R51P<br>R51N        | F14<br>E14  | K[14]<br>K[15]      | 88<br>89    | 167<br>169 | 168<br>170 | 11         | B[3]               | G14        | GND<br>R46P      | pair w/163         |

|                     | GND                 |             |                     |             | 171        | 172        |            |                    |            | GND              |                    |

|                     | R52P<br>R52N        | E15<br>E16  | K[16]<br>K[17]      | 90<br>91    | 173<br>175 | 174<br>176 | 108<br>109 | PL[2]<br>PL[3]     | D14<br>C14 | R69P<br>R69N     | PLI                |

|                     | GND                 |             |                     |             | 177        | 178        |            |                    |            | GND              |                    |

|                     | R42P<br>R42N        | D16<br>C16  | K[18]<br>K[19]      | 92<br>93    | 179<br>181 | 180<br>182 | 94<br>95   | K[20]<br>K[21]     | D15<br>C15 | R70P<br>R70N     |                    |

|                     | R42N<br>GND         | C10         | K[19]               | 33          | 181        | 182        | 20         | N[21]              | C15        | GND              |                    |

| no diff pair        | T17N                | F12         | B[4]                | 12          | 185        | 186        | 96         | K[22]              | C13        | T2P              |                    |

|                     | GND<br>T30P         | B13         | K[24]               | 98          | 187<br>189 | 188<br>190 | 97         | K[23]              | C12        | T2N<br>GND       |                    |

|                     | T30N                | A13         | K[24]               | 99          | 191        | 192        | 100        | K[26]              | D12        | T1P              |                    |

|                     | GND<br>T28P         | F10         | K[28]               | 102         | 193<br>195 | 194<br>196 | 101        | K[27]              | E11        | T1N<br>GND       |                    |

|                     | T28P<br>T28N        | F10<br>E10  | K[28]<br>K[29]      | 102         | 195        | 196        | 104        | K[30]              | B12        | GND<br>T41P      |                    |

| no diff pair        | T43P                | A11         | B[5]                | 13          | 199        | 200        | 105        | K[31]              | B11        | T41N             |                    |

Copyright 2022 Alorium Technology, LLC

# 6 Extended Interrupts

The Sno Edge extends the AVR architecture to implement additional interrupts for extended GPIO pin change interrupts and for user-defined interrupts in the OpenXLR8 methodology.

## 6.1 GPIO Port Pin Change Detection

The Sno Edge extended GPIO ports support pin change detection in a way similar to the standard ports. Port pins are monitored and if a pin change is detected, an interrupt can be generated.

Each GPIO port has a PCMSK that can be used to enable pin change interrupts on a per-pin basis. The Sno Edge extended GPIO PCMSKs are:

PCMSKA

PCMSKJA

• PCMSKJA PCMSKJB

PCMSKE • PCMSKG

- PCMSKJB • PCMSKIC

- PCMSKID

PCMSKPL •

PCMSKID

• PCMSKIC

The PCMSK register contains a bit for each pin in the port. A PCMSK bit value of zero will prevent a pin change on the corresponding port pin from causing an interrupt signal to be generated. The PCMSK does not support bit set or bit clear operations, so a read-modify-write operation should be used to change individual bits.

## 6.2 Pin Change Interrupts

Pin Change notifications from the ports are collected and controlled by three registers:

| Register | Description                                   |

|----------|-----------------------------------------------|

| SPCIFR   | Sno Pin Change Interrupt Flag Register        |

| SPCICR   | Sno Pin Change Interrupt Control Register     |

| SPCIMSK  | Sno Pin Change Interrupt Mask Register        |

|          | Figure 13: Sno Pin Change Interrunt Registers |

Figure 13: Sno Pin Change Interrupt Registers

The bits in the above registers correspond to the ports in the following way. Notice that the four Ix ports and the four Kx ports are combined into single bits:

| Bit | Interrupt Source              |

|-----|-------------------------------|

| 0   | Port A                        |

| 1   | Port E                        |

| 2   | Port G                        |

| 3   | Port J (JA or JB or JC or JD) |

| 4   | Port K (KA or KB or KC or KD) |

| 5   | Port PL                       |

Figure 14: Sno Pin Change Interrupt Fields

A bit in the Flag register (SPCIFR) will be set when a pin change notification is received if the corresponding bit in the Mask register (SPCIMSK) is set.

A bit in the Flag register is cleared via software by writing a one to the bit.

A bit set in the Flag register will cause an IRQ to be generated if the corresponding bit in the Control register (SPCICR) is set.

Neither the Mask register nor the Control register support bit operations, so a read-modify-write operation should be used to change individual bits.

# 6.3 OpenXLR8 Interrupts

Interrupts from XBs instantiated within the OpenXLR8 Module are collected and saved in the `xlr8\_pcint` module.

| Register                                | Description                               |  |

|-----------------------------------------|-------------------------------------------|--|

| OX8IFR                                  | Sno Pin Change Interrupt Flag Register    |  |

| OX8ICR                                  | Sno Pin Change Interrupt Control Register |  |

| OX8MSK                                  | Sno Pin Change Interrupt Mask Register    |  |

| Figure 15: OpenXLR8 Interrupt Registers |                                           |  |

The bits in the above registers are defined by the OpenXLR8 developer and are specific to that particular implementation.

A bit in the Flag register (OX8IFR) will be set when a pin change notification is received if the corresponding bit in the Mask register (OX8MSK) is set.

A bit in the Flag register is cleared via software by writing a one to the bit.

A bit set in the Flag register will cause an IRQ to be generated if the corresponding bit in the Control register (OX8ICR) is set.

Neither the Mask register nor the Control register support bit operations, so a read-modify-write operation should be used to change individual bits.

## 6.4 Extended IRQs

The IRQs from the GPIO pin change interrupts and the OpenXLR8 interrupts are managed by the following registers

| Description                       |                                                                                           |

|-----------------------------------|-------------------------------------------------------------------------------------------|

| eXtended IRQ Flag Register        |                                                                                           |

| eXtended IRQ Control Register     |                                                                                           |

| eXtended IRQ Mask Register        |                                                                                           |

| eXtended IRQ Acknowledge Register |                                                                                           |

| _                                 | eXtended IRQ Flag Register<br>eXtended IRQ Control Register<br>eXtended IRQ Mask Register |

Figure 16: Extended IRQ Registers

The bits in the above registers correspond to the interrupt sources in the following way:

| Bit | Interrupt Source | IRQ Num | AVR Name         | XLR8/Sno Alias        |

|-----|------------------|---------|------------------|-----------------------|

| 0   | SPCIFR           | 23      | EE_READY_vect    | XGPIO_vect, BIXB_vect |

| 1   | OX8IFR           | 24      | ANALOG_COMP_vect | OPENXLR8_vect         |

| 7:2 | Unused           |         |                  |                       |

Figure 17: Extended IRQ Fields

The AVR supports a specified set of IRQ vectors, specified by integers. The Sno Edge, and XLR8 boards in general, reassign two of the defined IRQ vectors to support the new extended GPIO pin change interrupts and the OpenXLR8 interrupts. Those reassigned vectors are indicated above.

A bit in the Flag register (XIFR) will be set when an IRQ is received if the corresponding bit in the Mask register (XMSK) is set and the corresponding bit in the Acknowledge (XACK) register is not set.

A bit in the Flag register is cleared either by the corresponding bit in the Acknowledge register being set, or by the source of the IRQ being cleared.

A bit set in the Flag register will cause an IRQ to be generated if the corresponding bit in the Control register (XICR) is set.

When an IRQ is generated to the AVR core it will respond by setting a bit in the acknowledge register. This will block the corresponding bit in the Flag register from being set, preventing further IRQs of that type from being sent to the AVR core. The bit in the Acknowledge must be cleared by software once the interrupt has been serviced and control is returned to the original program. Bits in the Acknowledge register can be cleared by writing a one to the corresponding bit location in the Acknowledge register

Neither the Mask register nor the Control register support bit operations, so a read-modify-write operation should be used to change individual bits.

#### 6.5 Setup and Usage

The default values for the interrupt related registers are all zeros. This disables all interrupts. In order to enable interrupts for a pin they must be configured:

- 1. Set the mask bits for the pin and port that is to be enabled by writing PCMSKxx for that port.

- 2. Set the SPCICR enable bit that corresponds to the port that is being enabled.

- 3. Set the SPCIMSK mask bit that corresponds to the port that is being enabled.

- 4. Set the XICR enable bit that corresponds to the port that is being enabled.

- 5. Set the XMSK mask bit that corresponds to the port that is being enabled.

When an IRQ is received by the AVR core it will trigger an Interrupt Service Routine (ISR) associated with the interrupt to be called. It will also set the bit in XACK corresponding to the interrupt vector.

After the interrupt has been handled by the ISR the interrupts should be re-enabled by:

- 1. Clear the SPCIFR bit or OX8IFR bit by writing a one to it

- 2. Clear the XACK bit by writing a one to it

Interrupt Service Routine functions can be specified using the XLR8 IRQ aliases specified in Figure 17. Simply specify the desired XLR8 IRQ alias name in the ISR() function call.

```

ISR(XGPIO_vect) { // Extended GPIO Port Pin Change Interrupts

// Enter ISR code

}

ISR(OPENXLR8_vect) { // OpenXLR8 Interrupts

// Enter ISR code

}

```

## 6.6 Example Interrupt Sketch

The following example sketch sets up Port G, Pin 0, for a pin change interrupt. To test this in hardware simply start the sketch and then simply ground Port G, Pin 0 momentarily. This should cause a pin change interrupt and the sketch will print " loop(): Interrupt detected... " each time the pin changes.

```

// Description : Demonstrate pin change interrupts on Sno Edge

11

extended GPIO port

11

// Variables to use in the ISR routine. Use volatile to make sure

// value is maintained across ISR calls

volatile bool isr found = false;

void setup() {

Serial.begin(115200);

Serial.println("======= Start snoedge int example.ino ========"");

Serial.println(" Enter setup(): Configure pin change interrupt on Port G, Pin 0");

// Enable Port G, pin 0 for pin change interrupts

PCMSKG |= (1 \ll MSKG0);

// Enable the SPCIFR bit for Port G to be enabled for pin change interrupts

SPCIMSK |= (1 << SPCIPG); // Set the bit for Port G in the mask req

SPCICR = (1 << SPCIPG); // Set the bit for Port G in the control reg

// Enable the XIFR bit for pin change interrupts

|= (1 << XIGPIO); // Set the bit for Pin Change IRQ in the mask reg

|= (1 << XIGPIO); // Set the bit for Pin Change IRQ in the control reg</pre>

XMSK

XICR

Serial.println(" Enter loop(): Check for interrupt and reset after response");

}

void loop() {

// Check for ISR

if (isr_found) {

Serial.print(" loop():

Interrupt detected... ");

// Code for interrupt response goes here

11

// After Interrupt response, clear interrupt flag and re-enable

// IRQ by clearing the XACK bit

SPCIFR = (1 << SPCIPG); // Write one to flag bit for Port G

XACK = (1 << XIGPIO); // Write one to clear the ACK

// Reset the isr found flag so that we break out of the loop

isr found = false;

Serial.println(" Interrupt handled");

}

// Wait a bit before checking the isr found flag again

delay(1);

}

ISR(XGPIO_vect) { // Extended GPIO Port Pin Change Interrupts

// This ISR will be involked when a pin change interrupt

// is triggered. Keep the interrupt service routine short

// by just setting a flag and returning. The flag will be

// checked in the main loop() function.

isr found = true;

}

```

Sample output:

======= Start snoedge\_int\_example.ino =========

| Enter setup(): | Configure | pin change interrupt on Port G, Pin 0 |  |

|----------------|-----------|---------------------------------------|--|

| Enter loop():  | Check for | interrupt and reset after response    |  |

| loop():        | Interrupt | detected Interrupt handled"           |  |

| loop():        | Interrupt | detected Interrupt handled"           |  |

|                |           |                                       |  |

# 7 Register Summary

The registers used in Sno Edge are listed below. The table is color coded to indicate whether the registers are as defined for the ATmega328p, or whether they have been changed in some way. The color key can be found at the bottom of the table.

| Address          | Name                 | Bit 7     | Bit 6                          | Bit 5     | Bit 4          | Bit 3         | Bit 2        | Bit 1        | Bit O | Notes                                       |  |  |

|------------------|----------------------|-----------|--------------------------------|-----------|----------------|---------------|--------------|--------------|-------|---------------------------------------------|--|--|

| (0xFF)           | XDINFO               |           |                                |           | XBIN           | FOAD          |              |              |       | Error!<br>Reference<br>source not<br>found. |  |  |

| (OxFE)           | Reserved             | -         | -                              | -         | -              | -             | -            | -            | -     |                                             |  |  |

| (0xFD)           | SVPWH                | -         | -                              | -         | -              |               | vo Pulse Wid | lth High Reg | ister | 7.1.17<br>7.1.17                            |  |  |

| (0xFC)           | SVPWL                |           | Servo Pulse Width Low Register |           |                |               |              |              |       |                                             |  |  |

| (OxFB)           | SVCR                 | SVEN      | SVEN SVDIS SVUP SVCHAN         |           |                |               |              |              |       |                                             |  |  |

| (0xFA)           | Reserved<br>Reserved |           | _                              | -         | -              | -             | _            | -            | -     |                                             |  |  |

| (0xF9)<br>(0xF8) | Reserved             |           | _                              | _         | -              | _             | _            | _            | -     |                                             |  |  |

| (0xF8)<br>(0xF7) | Reserved             |           |                                |           |                |               | _            |              |       |                                             |  |  |

| (0xF6)           | PID OP L             |           |                                |           | Low Byt        | e output      |              |              |       | 7.1.16                                      |  |  |

| (0xF5)           | PID OP H             |           |                                |           |                | e output      |              |              |       | 7.1.16                                      |  |  |

| (0xF4)           | PID PV L             |           |                                |           | Process varia  |               | 2            |              |       | 7.1.16                                      |  |  |

| (0xF3)           | PID_PV_H             |           |                                |           | Process varia  |               |              |              |       | 7.1.16                                      |  |  |

| (0xF2)           | PID_SP_L             |           |                                |           | Set point      |               | -            |              |       | 7.1.16                                      |  |  |

| (0xF1)           | PID_SP_H             |           |                                |           | Set point      |               |              |              |       | 7.1.16                                      |  |  |

| (0xF0)           | PID_KP_L             |           |                                |           | KP coefficie   |               |              |              |       | 7.1.16                                      |  |  |

| (OxEF)           | PID_KP_H             |           |                                |           | KD coefficie   | nt high byte  |              |              |       | 7.1.16                                      |  |  |

| (OxEE)           | PID_KI_L             |           |                                |           | KI coefficie   | nt low byte   |              |              |       | 7.1.16                                      |  |  |

| (0xED)           | PID_KI_H             |           |                                |           | KI coefficie   | nt high byte  |              |              |       | 7.1.16                                      |  |  |

| (0xEC)           | PID_KD_L             |           |                                |           | KD coefficie   | ent low byte  |              |              |       | 7.1.16                                      |  |  |

| (OxEB)           | PID_KD_H             |           |                                |           | KD coefficie   | nt high byte  |              |              |       | 7.1.16                                      |  |  |

| (OxEA)           | PIDCR                | PEDEN     | PIDDIS                         | PIDUPD    |                |               | PIDCHAN      |              |       | 7.1.16                                      |  |  |

| (0xE9)           | QERAT3               |           |                                |           | r 8 bits of qu |               |              |              |       | 7.1.15                                      |  |  |

| (0xE8)           | QERAT2               |           |                                |           | iddle 8 bits o |               |              |              |       | 7.1.15                                      |  |  |

| (0xE7)           | QERAT1               |           |                                |           | ddle 8 bits o  |               |              |              |       | 7.1.15                                      |  |  |

| (0xE6)           | QERAT0               |           |                                |           | r 8 bits of qu |               |              |              |       | 7.1.15                                      |  |  |

| (0xE5)           | QECNT3               |           |                                |           | 8 bits of qua  |               |              |              |       | 7.1.15                                      |  |  |

| (0xE4)           | QECNT2               |           |                                |           | ddle 8 bits of |               |              |              |       | 7.1.15                                      |  |  |

| (0xE3)           | QECNT1               |           |                                |           | dle 8 bits of  |               |              |              |       | 7.1.15                                      |  |  |

| (0xE2)           | QECNT0               |           |                                | Lower     | 8 bits of qua  | drature cou   | nt data      |              |       | 7.1.15                                      |  |  |

| (0xE1)<br>(0xE0) | Reserved<br>QECR     | –<br>QEEN | QEDIS                          | <br>QECLR | QERATE         | _             | - 050        | HAN          | -     | 7.1.15                                      |  |  |

| (0xE0)<br>(0xDF) | Reserved             | QEEN      |                                | QECLK     | QERATE         |               |              |              | _     | 7.1.15                                      |  |  |

| (0xDF)<br>(0xDE) | Reserved             | _         | _                              | _         | _              | _             | _            | _            | _     |                                             |  |  |

| (0xDL)           | Reserved             | _         | _                              | _         | _              | _             | _            | _            | _     | TWAMR1                                      |  |  |

| (0xDC)           | Reserved             | _         | _                              | _         | _              | _             | _            | _            | _     | TWCR1                                       |  |  |

| (0xDC)<br>(0xDB) | Reserved             | _         | _                              | _         | _              | _             | _            | _            | _     | TWDR1                                       |  |  |