### **General Description**

The MAX5876 is an advanced 12-bit, 250Msps, dual digital-to-analog converter (DAC). This DAC meets the demanding performance requirements of signal synthesis applications found in wireless base stations and other communications applications. Operating from +3.3V and +1.8V supplies, this dual DAC offers exceptional dynamic performance such as 75dBc spurious-free dynamic range (SFDR) at f<sub>OUT</sub> = 16MHz and supports update rates of 250Msps, with a power dissipation of only 287mW.

The MAX5876 utilizes a current-steering architecture that supports a 2mA to 20mA full-scale output current range, and allows a 0.1VP-P to 1VP-P differential output voltage swing. The device features an integrated +1.2V bandgap reference and control amplifier to ensure high-accuracy and low-noise performance. A separate reference input (REFIO) allows for the use of an external reference source for optimum flexibility and improved gain accuracy.

The clock inputs of the MAX5876 accept both LVDS and LVPECL-compatible voltage levels. The device features an interleaved data input that allows a single LVDS bus to support both DACs. The MAX5876 is available in a 68-pin QFN package with an exposed pad (EP) and is specified for the extended temperature range (-40°C to +85°C).

Refer to the MAX5877 and MAX5878 data sheets for pin-compatible 14-bit and 16-bit versions of the MAX5876, respectively. Refer to the MAX5873 data sheet for a CMOS-compatible version of the MAX5876.

### **Applications**

Base Stations: Single-Carrier UMTS, CDMA, GSM Communications: Fixed Broadband Wireless Access, Point-to-Point Microwave Direct Digital Synthesis (DDS) Cable Modem Termination Systems (CMTS)

Automated Test Equipment (ATE)

Instrumentation

#### Selector Guide

| PART    | RESOLUTION<br>(BITS) | UPDATE<br>RATE (Msps) | LOGIC<br>INPUTS |

|---------|----------------------|-----------------------|-----------------|

| MAX5873 | 12                   | 200                   | CMOS            |

| MAX5874 | 14                   | 200                   | CMOS            |

| MAX5875 | 16                   | 200                   | CMOS            |

| MAX5876 | 12                   | 250                   | LVDS            |

| MAX5877 | 14                   | 250                   | LVDS            |

| MAX5878 | 16                   | 250                   | LVDS            |

#### **Features**

- ◆ 250Msps Output Update Rate

- ♦ Noise Spectral Density = -154dBFS/Hz at fout = 16MHz

- ◆ Excellent SFDR and IMD Performance SFDR = 75dBc at f<sub>OUT</sub> = 16MHz (to Nyquist) SFDR = 71dBc at f<sub>OUT</sub> = 80MHz (to Nyquist) IMD = -87dBc at f<sub>OUT</sub> = 10MHz

- IMD = -73dBc at f<sub>OUT</sub> = 80MHz

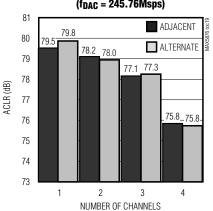

- ♦ ACLR = 75dB at fout = 61MHz

- ♦ 2mA to 20mA Full-Scale Output Current

- **♦ LVDS-Compatible Digital and Clock Inputs**

- ♦ On-Chip +1.20V Bandgap Reference

- ♦ Low 287mW Power Dissipation

- ♦ Compact 68-Pin QFN-EP Package (10mm x 10mm)

- ♦ Evaluation Kit Available (MAX5878EVKIT)

### **Ordering Information**

| PART         | TEMP RANGE     | PIN-<br>PACKAGE | PKG<br>CODE |

|--------------|----------------|-----------------|-------------|

| MAX5876EGK-D | -40°C to +85°C | 68 QFN-EP*      | G6800-4     |

| MAX5876EGK+D | -40°C to +85°C | 68 QFN-EP*      | G6800-4     |

<sup>\*</sup>EP = Exposed pad.

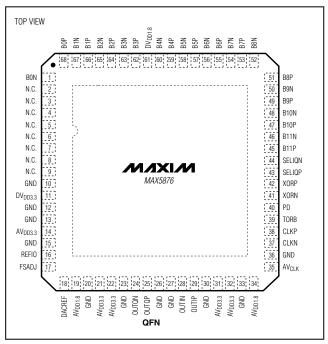

### **Pin Configuration**

#### NIXIN

Maxim Integrated Products

<sup>+=</sup> Lead-free package. D = Dry pack.

#### **ABSOLUTE MAXIMUM RATINGS**

| AV <sub>DD1.8</sub> , DV <sub>DD1.8</sub> to GND, DACRE<br>AV <sub>DD3.3</sub> , DV <sub>DD3.3</sub> , AV <sub>CLK</sub> to GND,<br>REFIO, FSADJ to |                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| GND, DACREFOUTIP, OUTIN, OUTQP.                                                                                                                     | 0.3V to (AV <sub>DD3.3</sub> + 0.3V) |

| OUTQN to GND, DACREF                                                                                                                                |                                      |

| B11P/B11N-B0P/B0N, XORN, XORF<br>SELIQP to GND, DACREF<br>TORB, PD to GND, DACREF                                                                   | 0.3V to (DV <sub>DD1.8</sub> + 0.3V) |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

|-------------------------------------------------------|----------------|

| 68-Pin QFN-EP                                         |                |

| (derate 41.7mW/°C above +70°C) (Note 1)               | 3333.3mW       |

| Thermal Resistance θ <sub>JA</sub> (Note 1)           | +24°C/W        |

| Operating Temperature Range                           | 40°C to +85°C  |

| Junction Temperature                                  | +150°C         |

| Storage Temperature Range                             | 60°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C         |

|                                                       |                |

Note 1: Thermal resistance based on a multilayer board with 4 x 4 via array in exposed paddle area.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(AV_{DD3.3} = DV_{DD3.3} = AV_{CLK} = +3.3V, AV_{DD1.8} = DV_{DD1.8} = +1.8V, GND = 0, f_{CLK} = 2 \times f_{DAC}$ , external reference  $V_{REFIO} = +1.25V$ , output load  $50\Omega$  double-terminated, transformer-coupled output,  $I_{OUTFS} = 20$ mA,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25$ °C.) (Note 2)

| PARAMETER                 | SYMBOL           | C                         | ONDITIONS                         | MIN    | TYP    | MAX    | UNITS      |

|---------------------------|------------------|---------------------------|-----------------------------------|--------|--------|--------|------------|

| STATIC PERFORMANCE        | •                |                           |                                   |        |        |        |            |

| Resolution                |                  |                           |                                   |        | 12     |        | Bits       |

| Integral Nonlinearity     | INL              | Measured differer         | ntially                           |        | ±0.2   |        | LSB        |

| Differential Nonlinearity | DNL              | Measured differer         | ntially                           |        | ±0.1   |        | LSB        |

| Offset Error              | OS               |                           |                                   | -0.025 | ±0.001 | +0.025 | %FS        |

| Offset-Drift Tempco       |                  |                           |                                   |        | ±10    |        | ppm/°C     |

| Full-Scale Gain Error     | GE <sub>FS</sub> | External reference        | Э                                 | -4.6   | -0.6   | +4.6   | %FS        |

| Cain Drift Taranaa        |                  | Internal reference        |                                   |        | ±100   |        | 10 to 10 C |

| Gain-Drift Tempco         |                  | External reference        | Э                                 |        | ±50    |        | ppm/°C     |

| Full-Scale Output Current | loutes           | (Note 3)                  |                                   | 2      |        | 20     | mA         |

| Output Compliance         |                  | Single-ended              |                                   | -0.5   |        | +1.1   | V          |

| Output Resistance         | Rout             |                           |                                   |        | 1      |        | МΩ         |

| Output Capacitance        | Cout             |                           |                                   |        | 5      |        | pF         |

| DYNAMIC PERFORMANCE       |                  |                           |                                   |        |        |        |            |

| Clock Frequency           | fCLK             |                           |                                   | 2      |        | 500    | MHz        |

| Output Update Rate        | fDAC             | fDAC = fCLK / 2           |                                   | 1      |        | 250    | Msps       |

| Noise Chaetral Density    |                  | f <sub>DAC</sub> = 150MHz | f <sub>OUT</sub> = 16MHz, -12dBFS |        | -154   |        | dBFS/      |

| Noise Spectral Density    |                  | f <sub>DAC</sub> = 250MHz | f <sub>OUT</sub> = 80MHz, -12dBFS |        | -153   |        | Hz         |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD3.3} = DV_{DD3.3} = AV_{CLK} = +3.3V, AV_{DD1.8} = DV_{DD1.8} = +1.8V, GND = 0, f_{CLK} = 2 \times f_{DAC}$ , external reference  $V_{REFIO} = +1.25V$ , output load  $50\Omega$  double-terminated, transformer-coupled output,  $I_{OUTFS} = 20$ mA,  $I_{A} = I_{MIN}$  to  $I_{MAX}$ , unless otherwise noted. Typical values are at  $I_{A} = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                                                  | SYMBOL             | C                                                           | ONDITIONS                                                               | MIN   | TYP    | MAX   | UNITS          |

|----------------------------------------------------------------------------|--------------------|-------------------------------------------------------------|-------------------------------------------------------------------------|-------|--------|-------|----------------|

|                                                                            |                    |                                                             | f <sub>OUT</sub> = 1MHz, 0dBFS                                          |       | 98     |       |                |

|                                                                            |                    | f <sub>DAC</sub> = 100MHz                                   | fout = 1MHz, -6dBFS                                                     |       | 88     |       |                |

|                                                                            |                    |                                                             | f <sub>OUT</sub> = 1MHz, -12dBFS                                        |       | 81     |       |                |

|                                                                            |                    |                                                             | fout = 10MHz, -12dBFS                                                   |       | 77     |       |                |

|                                                                            |                    |                                                             | fout = 30MHz, -12dBFS                                                   |       | 77     |       |                |

|                                                                            |                    |                                                             | fout = 10MHz, -12dBFS                                                   |       | 75     |       |                |

| Spurious-Free Dynamic Range to Nyquist                                     | SFDR               | fo                                                          | four = 16MHz, -12dBFS                                                   | 66    | 75     |       | dBc            |

| to nyquist                                                                 |                    | $f_{DAC} = 200MHz$                                          | $f_{OUT} = 50MHz, -12dBFS$                                              |       | 73     |       |                |

|                                                                            |                    |                                                             | fout = 80MHz, -12dBFS                                                   |       | 71     |       |                |

|                                                                            |                    |                                                             | fout = 10MHz, -12dBFS                                                   |       | 77     |       |                |

|                                                                            |                    | f OFOMU-                                                    | fout = 50MHz, -12dBFS                                                   |       | 73     |       |                |

|                                                                            |                    | $f_{DAC} = 250MHz$                                          | fout = 80MHz, -12dBFS                                                   |       | 70     |       | 1              |

|                                                                            |                    |                                                             | $f_{OUT} = 100MHz, -12dBFS$                                             |       | 68     |       |                |

| Spurious-Free Dynamic Range,<br>25MHz Bandwidth                            | SFDR               | f <sub>DAC</sub> = 150MHz                                   | f <sub>OUT</sub> = 16MHz, -12dBFS                                       |       | 80     |       | dBc            |

|                                                                            | TTIMD              | f <sub>DAC</sub> = 100MHz                                   | f <sub>OUT1</sub> = 9MHz, -7dBFS;<br>f <sub>OUT2</sub> = 10MHz, -7dBFS  | -87   |        | dDa   |                |

| Two-Tone IMD                                                               |                    | f <sub>DAC</sub> = 200MHz                                   | f <sub>OUT1</sub> = 79MHz, -7dBFS;<br>f <sub>OUT2</sub> = 80MHz, -7dBFS |       | -73    |       | - dBc          |

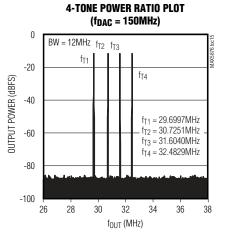

| Four-Tone IMD, 1MHz<br>Frequency Spacing, GSM Model                        | FTIMD              | f <sub>DAC</sub> = 150MHz                                   | f <sub>OUT</sub> = 16MHz, -12dBFS                                       |       | -91    |       | dBc            |

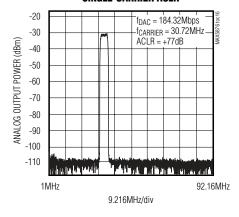

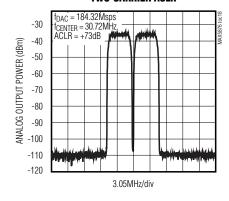

| Adjacent Channel Leakage Power<br>Ratio 3.84MHz Bandwidth,<br>W-CDMA Model | ACLR               | fDAC =<br>184.32MHz                                         | f <sub>OUT</sub> = 61.44MHz                                             |       | 75     |       | dB             |

| Output Bandwidth                                                           | BW <sub>-1dB</sub> | (Note 4)                                                    |                                                                         |       | 240    |       | MHz            |

| INTER-DAC CHARACTERISTICS                                                  |                    |                                                             |                                                                         |       |        |       |                |

| O : M : I :                                                                |                    | fout = DC - 80MH                                            | Hz                                                                      |       | ±0.2   |       | ID.            |

| Gain Matching                                                              | ∆Gain              | f <sub>OUT</sub> = DC                                       |                                                                         | -0.25 | +0.01  | +0.25 | dB             |

| Gain-Matching Tempco                                                       | ∆Gain/°C           |                                                             |                                                                         |       | ±20    |       | ppm/°C         |

| Phase Matching                                                             | ∆Phase             | f <sub>OUT</sub> = 60MHz                                    |                                                                         |       | ±0.25  |       | Degrees        |

| Phase-Matching Tempco                                                      | <b>∆</b> Phase/°C  | fout = 60MHz                                                |                                                                         |       | ±0.002 |       | Degrees/<br>°C |

| Channel-to-Channel Crosstalk                                               |                    | f <sub>DAC</sub> = 200Msps, f <sub>OUT</sub> = 50MHz, 0dBFS |                                                                         |       | 90     |       | dB             |

| REFERENCE                                                                  |                    |                                                             |                                                                         |       |        |       |                |

| Internal Reference Voltage Range                                           | VREFIO             |                                                             |                                                                         | 1.14  | 1.2    | 1.26  | V              |

|                                                                            | •                  |                                                             |                                                                         |       |        |       | •              |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD3.3} = DV_{DD3.3} = AV_{CLK} = +3.3V, AV_{DD1.8} = DV_{DD1.8} = +1.8V, GND = 0, f_{CLK} = 2 x f_{DAC}$ , external reference  $V_{REFIO} = +1.25V$ , output load  $50\Omega$  double-terminated, transformer-coupled output,  $I_{OUTFS} = 20$ mA,  $I_{A} = I_{MIN}$  to  $I_{MAX}$ , unless otherwise noted. Typical values are at  $I_{A} = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                | SYMBOL            | CONDITIONS                                  | MIN                          | TYP   | MAX                          | UNITS            |

|------------------------------------------|-------------------|---------------------------------------------|------------------------------|-------|------------------------------|------------------|

| Reference Input Compliance Range         | VREFIOCR          |                                             | 0.125                        |       | 1.260                        | V                |

| Reference Input Resistance               | RREFIO            |                                             |                              | 10    |                              | kΩ               |

| Reference Voltage Drift                  | TCOREF            |                                             |                              | ±25   |                              | ppm/°C           |

| ANALOG OUTPUT TIMING (See I              | igure 4)          |                                             |                              |       |                              |                  |

| Output Fall Time                         | tfall             | 90% to 10% (Note 5)                         |                              | 0.7   |                              | ns               |

| Output Rise Time                         | t <sub>RISE</sub> | 10% to 90% (Note 5)                         |                              | 0.7   |                              | ns               |

| Output-Voltage Settling Time             | tSETTLE           | Output settles to 0.025% FS (Note 5)        |                              | 14    |                              | ns               |

| Output Propagation Delay                 | t <sub>PD</sub>   | Excluding data latency (Note 5)             |                              | 1.1   |                              | ns               |

| Glitch Impulse                           |                   | Measured differentially                     |                              | 1     |                              | pV∙s             |

| Output Naisa                             | 2011              | IOUTFS = 2mA                                |                              | 30    |                              | pA/√Hz           |

| Output Noise                             | nout              | IOUTFS = 20mA                               |                              | 30    |                              | pa/vnz           |

| TIMING CHARACTERISTICS                   |                   |                                             |                              |       |                              |                  |

| Data to Clock Setup Time                 | tSETUP            | Referenced to rising edge of clock (Note 6) | -1.2                         |       |                              | ns               |

| Data to Clock Hold Time                  | thold             | Referenced to rising edge of clock (Note 6) | 2.0                          |       |                              | ns               |

| Data Latanay                             |                   | Latency to I output                         |                              | 9     |                              | Clock            |

| Data Latency                             |                   | Latency to Q output                         |                              | 8     |                              | Cycles           |

| Minimum Clock Pulse-Width High           | tch               | CLKP, CLKN                                  |                              | 0.9   |                              | ns               |

| Minimum Clock Pulse-Width Low            | tcL               | CLKP, CLKN                                  |                              | 0.9   |                              | ns               |

| LVDS LOGIC INPUTS (B11P/B11              | N-B0P/B0N,        | , XORN, XORP, SELIQN, SELIQP)               |                              |       |                              |                  |

| Differential Input-Logic High            | VIH               |                                             |                              |       | 100                          | mV               |

| Differential Input-Logic Low             | VIL               |                                             | -100                         |       |                              | mV               |

| Common-Mode Voltage Range                | VCMR              |                                             | 1.125                        |       | 1.375                        | V                |

| Differential Input Resistance            | RIN               | (Note 7)                                    |                              | 110   |                              | Ω                |

| Input Capacitance                        | C <sub>IN</sub>   |                                             |                              | 2.5   |                              | рF               |

| CMOS LOGIC INPUTS (PD, TORE              | 3)                |                                             |                              |       |                              |                  |

| Input-Logic High                         | VIH               |                                             | 0.7 x<br>DV <sub>DD3.3</sub> |       |                              | V                |

| Input-Logic Low                          | VIL               |                                             |                              |       | 0.3 x<br>DV <sub>DD3.3</sub> | V                |

| Input Leakage Current                    | I <sub>IN</sub>   |                                             | -20                          | 1     | +20                          | μΑ               |

| PD, TORB Internal Pulldown<br>Resistance |                   | V <sub>PD</sub> = V <sub>TORB</sub> = 3.3V  |                              | 1.5   |                              | МΩ               |

| Input Capacitance                        | CIN               |                                             |                              | 2.5   |                              | рF               |

| CLOCK INPUTS (CLKP, CLKN)                |                   |                                             |                              |       |                              |                  |

| Differential Input                       |                   | Sine wave                                   |                              | > 1.5 |                              | \/               |

| Voltage Swing                            |                   | Square wave                                 |                              | > 0.5 |                              | V <sub>P-P</sub> |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD3.3} = DV_{DD3.3} = AV_{CLK} = +3.3V, AV_{DD1.8} = DV_{DD1.8} = +1.8V, GND = 0, f_{CLK} = 2 x f_{DAC}$ , external reference  $V_{REFIO} = +1.25V$ , output load  $50\Omega$  double-terminated, transformer-coupled output,  $I_{OUTFS} = 20$ mA,  $I_{A} = I_{MIN}$  to  $I_{MAX}$ , unless otherwise noted. Typical values are at  $I_{A} = +25^{\circ}C$ .) (Note 2)

| PARAMETER                          | SYMBOL                                    | CONDITIONS                                                                             | MIN   | TYP                           | MAX   | UNITS                                 |

|------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------|-------|-------------------------------|-------|---------------------------------------|

| Differential Input Slew Rate       | SR <sub>CLK</sub>                         | (Note 8)                                                                               |       | >100                          |       | V/µs                                  |

| External Common-Mode Voltage Range | V <sub>COM</sub>                          |                                                                                        |       | AV <sub>CLK</sub> / 2<br>±0.3 | 2     | V                                     |

| Input Resistance                   | RCLK                                      |                                                                                        |       | 5                             |       | kΩ                                    |

| Input Capacitance                  | CCLK                                      |                                                                                        |       | 2.5                           |       | рF                                    |

| POWER SUPPLIES                     |                                           |                                                                                        |       |                               |       |                                       |

| Analog Cupply Voltage Dange        | AV <sub>DD3.3</sub>                       |                                                                                        | 3.135 | 3.3                           | 3.465 | V                                     |

| Analog Supply Voltage Range        | AV <sub>DD1.8</sub>                       |                                                                                        | 1.710 | 1.8                           | 1.890 | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

| B: :: 10                           | DV <sub>DD3.3</sub>                       |                                                                                        | 3.135 | 3.3                           | 3.465 | V                                     |

| Digital Supply Voltage Range       | DV <sub>DD1.8</sub>                       |                                                                                        | 1.710 | 1.8                           | 1.890 | ]                                     |

| Clock Supply Voltage Range         | AVCLK                                     |                                                                                        | 3.135 | 3.3                           | 3.465 | V                                     |

|                                    | I <sub>AVDD3.3</sub> + I <sub>AVCLK</sub> | f <sub>DAC</sub> = 250Msps, f <sub>OUT</sub> = 16MHz                                   |       | 52                            | 58    | mA                                    |

| Analog Cupply Current              |                                           | Power-down                                                                             |       | 1                             |       | μΑ                                    |

| Analog Supply Current              | IAVDD1.8                                  | f <sub>DAC</sub> = 250Msps, f <sub>OUT</sub> = 16MHz                                   |       | 31                            | 36    | mA                                    |

|                                    |                                           | Power-down                                                                             |       | 1                             |       | μΑ                                    |

|                                    |                                           | f <sub>DAC</sub> = 250Msps, f <sub>OUT</sub> = 16MHz                                   |       | 0.15                          | 1     | mA                                    |

| District Coursel of Course         | IDVDD3.3                                  | Power-down                                                                             |       | 1                             |       | μΑ                                    |

| Digital Supply Current             |                                           | f <sub>DAC</sub> = 250Msps, f <sub>OUT</sub> = 16MHz                                   |       | 33                            | 40    | mA                                    |

|                                    | IDVDD1.8                                  | Power-down                                                                             |       | 4                             |       | μΑ                                    |

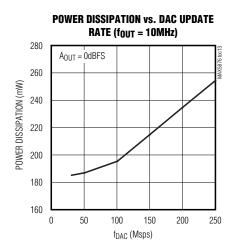

| Davis Diagination                  | Б                                         | f <sub>DAC</sub> = 250Msps, f <sub>OUT</sub> = 16MHz                                   |       | 287                           | 331   | mW                                    |

| Power Dissipation                  | P <sub>DISS</sub>                         | Power-down                                                                             |       | 16                            |       | μW                                    |

| Power-Supply Rejection Ratio       | PSRR                                      | AV <sub>DD3.3</sub> = AV <sub>CLK</sub> = DV <sub>DD3.3</sub> = +3.3V ±5% (Notes 8, 9) | -0.1  |                               | +0.1  | %FS/V                                 |

- Note 2: Specifications at  $T_A \ge +25^{\circ}C$  are guaranteed by production testing. Specifications at  $T_A < +25^{\circ}C$  are guaranteed by design.

- **Note 3:** Nominal full-scale current I<sub>OUTFS</sub> = 32 x I<sub>REF</sub>.

- Note 4: This parameter does not include update-rate-dependent effects of sin(x)/x filtering inherent in the MAX5876.

- **Note 5:** Parameter measured single-ended into a  $50\Omega$  termination resistor.

- Note 6: Not production tested. Guaranteed by design.

- Note 7: No termination resistance between XORP and XORN.

- Note 8: A differential clock input slew rate of > 100V/µs is required to achieve the specified dynamic performance.

- Note 9: Parameter defined as the change in midscale output caused by a ±5% variation in the nominal supply voltage.

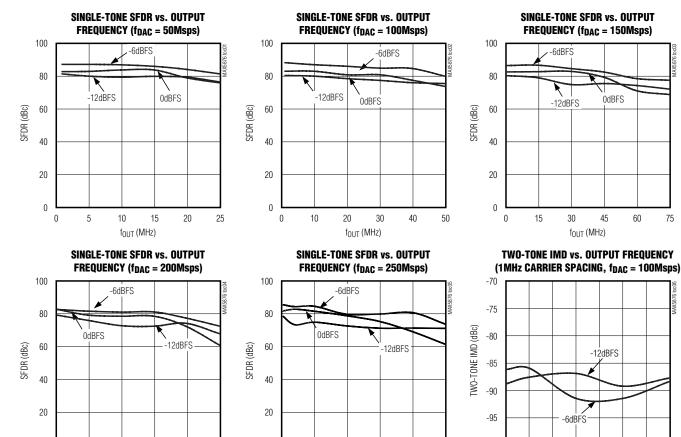

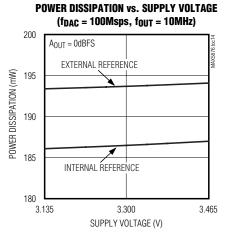

### **Typical Operating Characteristics**

-100

f<sub>OUT</sub> (MHz)

(AVDD3.3 = DVDD3.3 = AVCLK = +3.3V, AVDD1.8 = DVDD1.8 = +1.8V, external reference, VREFIO = +1.25V, RL = 50Ω double-terminated,  $I_{OUTFS} = 20$ mA,  $T_{A} = +25$ °C, unless otherwise noted.)

f<sub>OUT</sub> (MHz)

f<sub>OUT</sub> (MHz)

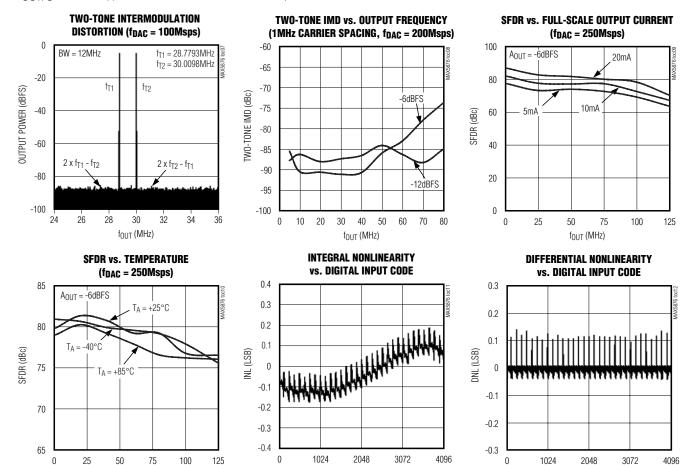

### Typical Operating Characteristics (continued)

$(AV_{DD3.3} = DV_{DD3.3} = AV_{CLK} = +3.3V, AV_{DD1.8} = DV_{DD1.8} = +1.8V,$  external reference,  $V_{REFIO} = +1.25V,$   $R_{L} = 50\Omega$  double-terminated,  $I_{OUTFS} = 20$ mA,  $I_{A} = +25$ °C, unless otherwise noted.)

DIGITAL INPUT CODE

four (MHz)

DIGITAL INPUT CODE

### Typical Operating Characteristics (continued)

$(AV_{DD3.3} = DV_{DD3.3} = AV_{CLK} = +3.3V, AV_{DD1.8} = DV_{DD1.8} = +1.8V,$  external reference,  $V_{REFIO} = +1.25V$ ,  $R_L = 50\Omega$  double-terminated,  $I_{OUTFS} = 20$ mA,  $T_A = +25$ °C, unless otherwise noted.)

## ACLR FOR WCDMA MODULATION, SINGLE-CARRIER ACLR

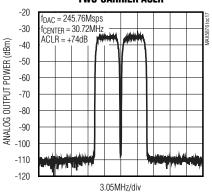

#### ACLR FOR WCDMA MODULATION, TWO-CARRIER ACLR

#### WCDMA BASEBAND ACLR (fdac = 245.76Msps)

### Pin Description

| PIN                                              | NAME                | FUNCTION                                                                                                                                                                                                                                            |

|--------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                | BON                 | Complementary Data Bit 0 (LSB)                                                                                                                                                                                                                      |

| 2–9                                              | N.C.                | No Connection. Leave floating or connect to GND.                                                                                                                                                                                                    |

| 10, 12, 13, 15,<br>20, 23, 26, 27,<br>30, 33, 36 | GND                 | Ground                                                                                                                                                                                                                                              |

| 11                                               | DV <sub>DD3.3</sub> | Digital Supply Voltage. Accepts a 3.135V to 3.465V supply voltage range. Bypass with a 0.1µF capacitor to GND.                                                                                                                                      |

| 14, 21, 22, 31,<br>32                            | AV <sub>DD3.3</sub> | Analog Supply Voltage. Accepts a 3.135V to 3.465V supply voltage range. Bypass each pin with a 0.1µF capacitor to GND.                                                                                                                              |

| 16                                               | REFIO               | Reference I/O. Output of the internal 1.2V precision bandgap reference. Bypass with a 1µF capacitor to GND. REFIO can be driven with an external reference source. See Table 1.                                                                     |

| 17                                               | FSADJ               | Full-Scale Adjust Input. This input sets the full-scale output current of the DAC. For a 20mA full-scale output current, connect a $2k\Omega$ resistor between FSADJ and DACREF. See Table 1.                                                       |

| 18                                               | DACREF              | Current-Set Resistor Return Path. Internally connected to GND. <b>Do not use as an external ground connection.</b>                                                                                                                                  |

| 19, 34                                           | AV <sub>DD1.8</sub> | Analog Supply Voltage. Accepts a 1.71V to 1.89V supply voltage range. Bypass each pin with a 0.1µF capacitor to GND.                                                                                                                                |

| 24                                               | OUTQN               | Complementary Q-DAC Output. Negative terminal for current output.                                                                                                                                                                                   |

| 25                                               | OUTQP               | Q-DAC Output. Positive terminal for current output.                                                                                                                                                                                                 |

| 28                                               | OUTIN               | Complementary I-DAC Output. Negative terminal for current output.                                                                                                                                                                                   |

| 29                                               | OUTIP               | I-DAC Output. Positive terminal for current output.                                                                                                                                                                                                 |

| 35                                               | AV <sub>CLK</sub>   | Clock Supply Voltage. Accepts a 3.135V to 3.465V supply voltage range. Bypass with a 0.1µF capacitor to GND.                                                                                                                                        |

| 37                                               | CLKN                | Complementary Converter Clock Input. Negative input terminal for LVDS/LVPECL-compatible differential converter clock. Internally biased to AV <sub>CLK</sub> / 2.                                                                                   |

| 38                                               | CLKP                | Converter Clock Input. Positive input terminal for LVDS/LVPECL-compatible differential converter clock. Internally biased to AV <sub>CLK</sub> / 2.                                                                                                 |

| 39                                               | TORB                | Two's-Complement/Binary Select Input. Set TORB to a CMOS-logic-high level to indicate a two's-complement input format. Set TORB to a CMOS-logic-low level to indicate an offset binary input format. TORB has an internal pulldown resistor.        |

| 40                                               | PD                  | Power-Down Input. Set PD to a CMOS-logic-high level to force the DAC into power-down mode. Set PD to a CMOS-logic-low level for normal operation. PD has an internal pulldown resistor.                                                             |

| 41                                               | XORN                | Complementary LVDS DAC Exclusive-OR Select Input. Set XORN high and XORP low to allow the data stream to pass unchanged to the DAC input. Set XORN low and XORP high to invert the DAC input data. If unused, connect XORN to DV <sub>DD1.8</sub> . |

| 42                                               | XORP                | LVDS DAC Exclusive-OR Select Input. Set XORN high and XORP low to allow the data stream to pass unchanged to the DAC input. Set XORN low and XORP high to invert the DAC input data. If unused, connect XORP to GND.                                |

### Pin Description (continued)

|     | 1                   |                                                                                                                                                                              |

|-----|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN | NAME                | FUNCTION                                                                                                                                                                     |

| 43  | SELIQP              | LVDS DAC Select Input. Set SELIQN low and SELIQP high to direct data to the I-DAC outputs. Set SELIQP low and SELIQN high to direct data to the Q-DAC outputs.               |

| 44  | SELIQN              | Complementary LVDS DAC Select Input. Set SELIQN low and SELIQP high to direct data to the I-DAC outputs. Set SELIQP low and SELIQN high to direct data to the Q-DAC outputs. |

| 45  | B11P                | Data Bit 11 (MSB)                                                                                                                                                            |

| 46  | B11N                | Complementary Data Bit 11 (MSB)                                                                                                                                              |

| 47  | B10P                | Data Bit 10                                                                                                                                                                  |

| 48  | B10N                | Complementary Data Bit 10                                                                                                                                                    |

| 49  | B9P                 | Data Bit 9                                                                                                                                                                   |

| 50  | B9N                 | Complementary Data Bit 9                                                                                                                                                     |

| 51  | B8P                 | Data Bit 8                                                                                                                                                                   |

| 52  | B8N                 | Complementary Data Bit 8                                                                                                                                                     |

| 53  | B7P                 | Data Bit 7                                                                                                                                                                   |

| 54  | B7N                 | Complementary Data Bit 7                                                                                                                                                     |

| 55  | B6P                 | Data Bit 6                                                                                                                                                                   |

| 56  | B6N                 | Complementary Data Bit 6                                                                                                                                                     |

| 57  | B5P                 | Data Bit 5                                                                                                                                                                   |

| 58  | B5N                 | Complementary Data Bit 5                                                                                                                                                     |

| 59  | B4P                 | Data Bit 4                                                                                                                                                                   |

| 60  | B4N                 | Complementary Data Bit 4                                                                                                                                                     |

| 61  | DV <sub>DD1.8</sub> | Digital Supply Voltage. Accepts a 1.71V to 1.89V supply voltage range. Bypass with a 0.1µF capacitor to GND.                                                                 |

| 62  | B3P                 | Data Bit 3                                                                                                                                                                   |

| 63  | B3N                 | Complementary Data Bit 3                                                                                                                                                     |

| 64  | B2P                 | Data Bit 2                                                                                                                                                                   |

| 65  | B2N                 | Complementary Data Bit 2                                                                                                                                                     |

| 66  | B1P                 | Data Bit 1                                                                                                                                                                   |

| 67  | B1N                 | Complementary Data Bit 1                                                                                                                                                     |

| 68  | B0P                 | Data Bit 0 (LSB)                                                                                                                                                             |

| _   | EP                  | Exposed Pad. Must be connected to GND through a low-impedance path.                                                                                                          |

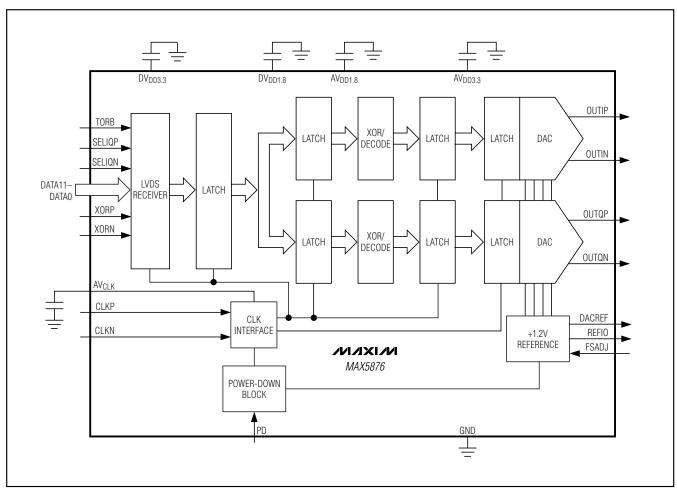

### Detailed Description

#### **Architecture**

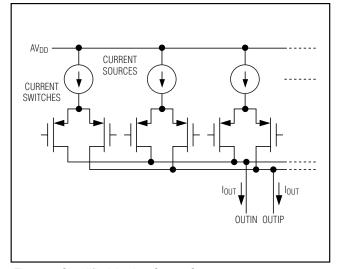

The MAX5876 high-performance, 12-bit, dual current-steering DAC (Figure 1) operates with DAC update rates up to 250Msps. The converter consists of input registers and a demultiplexer for single-port operation, followed by a current-steering array. During operation, the input data registers demultiplex the single-port data bus. The current-steering array generates differential full-scale currents in the 2mA to 20mA range. An internal current-switching network, in combination with external  $50\Omega$  termination resistors, converts the differential output currents into dual differential output voltages with a 0.1V to 1V peak-to-peak output voltage range. An integrated

+1.2V bandgap reference, control amplifier, and user-selectable external resistor determine the data converter's full-scale output range.

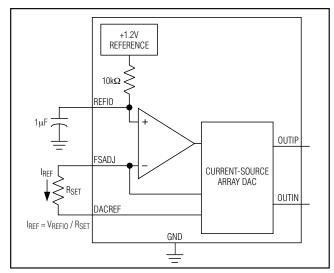

#### **Reference Architecture and Operation**

The MAX5876 supports operation with the internal +1.2V bandgap reference or an external reference voltage source. REFIO serves as the input for an external, low-impedance reference source. REFIO also serves as a reference output when the DAC operates in internal reference mode. For stable operation with the internal reference, decouple REFIO to GND with a  $1\mu F$  capacitor. Due to its limited output drive capability, buffer REFIO with an external amplifier when driving large external loads.

Figure 1. MAX5876 High-Performance, 12-Bit, Dual Current-Steering DAC

The MAX5876's reference circuit (Figure 2) employs a control amplifier to regulate the full-scale current IOUTFS for the differential current outputs of the DAC. Calculate the full-scale output current as follows:

$$I_{OUTFS} = 32 \times \frac{V_{REFIO}}{R_{SET}} \times \left(1 - \frac{1}{2^{12}}\right)$$

where I<sub>OUTFS</sub> is the full-scale output current of the DAC. RSET (located between FSADJ and DACREF) determines the amplifier's full-scale output current for the DAC. See Table 1 for a matrix of different I<sub>OUTFS</sub> and RSET selections.

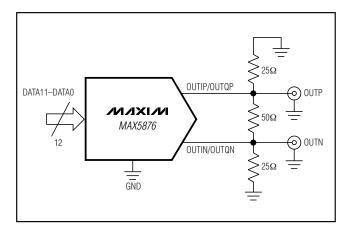

## Analog Outputs (OUTIP, OUTIN, OUTQP, OUTQN)

Each MAX5876 DAC outputs two complementary currents (OUTIP/N, OUTQP/N) that operate in a single-ended or differential configuration. A load resistor converts these two output currents into complementary single-ended output voltages. A transformer or a differential amplifier configuration converts the differential voltage existing between OUTIP (OUTQP) and OUTIN (OUTQN) to a single-ended voltage. If not using a transformer, the recommended termination from the output is a  $25\Omega$  termination resistor to ground and a  $50\Omega$  resistor between the outputs.

To generate a single-ended output, select OUTIP (or OUTQP) as the output and connect OUTIN (or OUTQN) to GND. SFDR degrades with single-ended operation or increased output swing. Figure 3 displays a simplified diagram of the internal output structure of the MAX5876.

Figure 2. Reference Architecture, Internal Reference Configuration

#### **Clock Inputs (CLKP, CLKN)**

The MAX5876 features flexible differential clock inputs (CLKP, CLKN) operating from a separate supply (AV<sub>CLK</sub>) to achieve optimum jitter performance. Drive the differential clock inputs from a single-ended or a differential clock source. For single-ended operation, drive CLKP with a logic source and bypass CLKN to GND with a 0.1µF capacitor.

CLKP and CLKN are internally biased to AV<sub>CLK</sub> / 2. This facilitates the AC-coupling of clock sources directly to the device without external resistors to define the DC level. The dynamic input resistance from CLKP and CLKN to ground is  $5k\Omega$ .

### Table 1. IOUTFS and RSET Selection Matrix Based on a Typical +1.200V Reference Voltage

| FULL-SCALE          | $R_{SET}(k\Omega)$ |            |  |  |

|---------------------|--------------------|------------|--|--|

| CURRENT IOUTFS (mA) | CALCULATED         | 1% EIA STD |  |  |

| 2                   | 19.2               | 19.1       |  |  |

| 5                   | 7.68               | 7.5        |  |  |

| 10                  | 3.84               | 3.83       |  |  |

| 15                  | 2.56               | 2.55       |  |  |

| 20                  | 1.92               | 1.91       |  |  |

Figure 3. Simplified Analog Output Structure

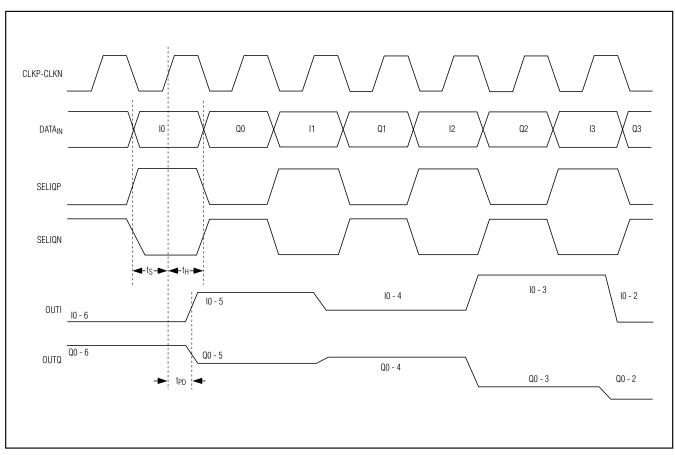

Figure 4. Timing Diagram

#### **Data Timing Relationship**

Figure 4 displays the timing relationship between digital LVDS data, clock, and output signals. The MAX5876 features a 2.0ns hold, a -1.2ns setup, and a 1.1ns propagation delay time. A nine (eight)-clock-cycle latency exists between CLKP/CLKN and OUTIP/OUTIN (OUTQP/OUTQN).

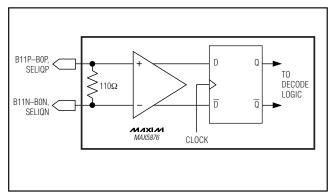

#### LVDS-Compatible Digital Inputs (B11P/B11N-B0P/B0N, XORP, XORN, SELIQP, SELIQN)

The MAX5876 latches B11P/N–B0P/N, XORP/N, and SELIQP/N data on the rising edge of the clock. A logichigh signal on SELIQP and a logic-low signal on SELIQN directs data onto the I-DAC inputs. A logic-low signal on SELIQP and a logic-high signal on SELIQN directs data onto the Q-DAC inputs.

The MAX5876 features LVDS receivers on the bus input interface with internal 110 $\Omega$  termination resistors. See

Figure 5. XORP and XORN are not internally terminated. These LVDS inputs (B11P/N-B0P/N) allow for a low differential voltage swing with low constant power consumption. A 1.25V common-mode level and 250mV differential input swing can be applied to the B11P/N-B0P/N, XORP/N, and SELIQP/N inputs.

The MAX5876 includes LVDS-compatible exclusive-OR inputs (XORP, XORN). Input data (all bits) is compared with the bits applied to XORP and XORN through exclusive-OR gates. Setting XORP high and XORN low inverts the input data. Setting XORP low and XORN high leaves the input data noninverted. By applying a previously encoded pseudo-random bit stream to the data input and applying decoding to XORP/XORN, the digital input data can be decorrelated from the DAC output, allowing for the troubleshooting of possible spurious or harmonic distortion degradation due to digital feedthrough on the printed circuit board (PCB). If XOR functionality is not required, connect XORP to GND and XORN to DVDD1.8.

Table 2. DAC Output Code Table

| DIGITAL I      | NPUT CODE        | OUT D                  | OUT N                  |

|----------------|------------------|------------------------|------------------------|

| OFFSET BINARY  | TWO'S COMPLEMENT | OUT_P                  | OUT_N                  |

| 0000 0000 0000 | 1000 0000 0000   | 0                      | loutes                 |

| 0111 1111 1111 | 0000 0000 0000   | I <sub>OUTFS</sub> / 2 | I <sub>OUTFS</sub> / 2 |

| 1111 1111 1111 | 0111 1111 1111   | loutes                 | 0                      |

## CMOS-Compatible Digital Inputs Input Data Format Select (TORB)

The TORB input selects between two's-complement or offset binary digital input data. Set TORB to a CMOS-logic-high level to indicate a two's-complement input format. Set TORB to a CMOS-logic-low level to indicate an offset binary input format.

#### Power-Down Operation (PD)

The MAX5876 also features an active-high power-down mode that reduces the DAC's digital current consumption from 33mA to less than  $5\mu A$  and the analog current consumption from 83mA to less than  $2\mu A$ . Set PD high to power down the MAX5876. Set PD low for normal operation.

When powered down, the MAX5876 reduces the overall power consumption to less than  $16\mu W$ . The MAX5876 requires 10ms to wake up from power-down and enter a fully operational state. The PD integrated pulldown resistor activates the MAX5876 if PD is left floating.

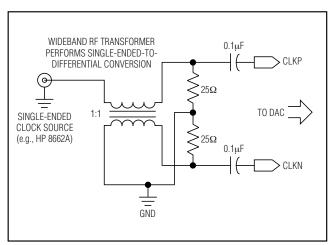

## Applications Information CLK Interface

The MAX5876 features a flexible differential clock input (CLKP, CLKN) with a separate supply (AVCLK) to achieve optimum jitter performance. Use an ultra-low jitter clock to achieve the required noise density. Clock jitter must be less than  $0.5ps_{RMS}$  for meeting the specified noise density. For that reason, the CLKP/CLKN input source must be designed carefully. The differential clock (CLKN and CLKP) input can be driven from a single-ended or a differential clock source. Differential clock drive is required to achieve the best dynamic performance from the DAC. For single-ended operation, drive CLKP with a low noise source and bypass CLKN to GND with a  $0.1\mu F$  capacitor.

Figure 6 shows a convenient and quick way to apply a differential signal created from a single-ended source (e.g., HP 8662A signal generator) and a wideband transformer. Alternatively, these inputs can be driven from a CMOS-compatible clock source; however, it is recommended to use sinewave or AC-coupled differential ECL/PECL or LVDS drive for best dynamic performance.

Figure 5. Simplified LVDS-Compatible Digital Input Structure

Figure 6. Differential Clock-Signal Generation

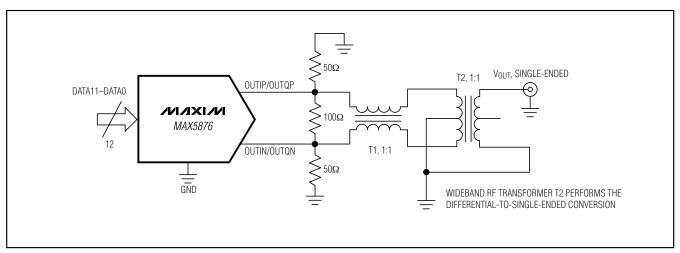

## Differential-to-Single-Ended Conversion Using a Wideband RF Transformer

Use a pair of transformers (Figure 7) or a differential amplifier configuration to convert the differential voltage existing between OUTIP/OUTQP and OUTIN/OUTQN to a single-ended voltage. Optimize the dynamic performance by using a differential transformer-coupled output and limit the output power to < 0dBm full scale. Pay close attention to the transformer core saturation characteristics when selecting a transformer for the MAX5876. Transformer core saturation can introduce strong 2nd-order harmonic distortion especially at low output frequencies and high signal amplitudes. For best results, center tap the transformer to ground. When not using a transformer, terminate each DAC output to ground with a  $25\Omega$  resistor. Additionally, place a  $50\Omega$  resistor between the outputs (Figure 8).

For a single-ended unipolar output, select OUTIP (OUTQP) as the output and ground OUTIN (OUTQN). Driving the MAX5876 single-ended is not recommended since additional noise and distortion will be added.

The distortion performance of the DAC depends on the load impedance. The MAX5876 is optimized for  $50\Omega$  differential double termination. It can be used with a transformer output as shown in Figure 7 or just one  $25\Omega$  resistor from each output to ground and one  $50\Omega$  resistor between the outputs (Figure 8). This produces a full-scale output power of up to -2dBm, depending on the output current setting. Higher termination impedance can be used at the cost of degraded distortion performance and increased output noise voltage.

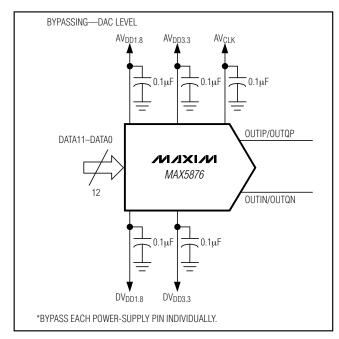

#### Grounding, Bypassing, and Power-Supply Considerations

Grounding and power-supply decoupling can strongly influence the MAX5876 performance. Unwanted digital crosstalk couples through the input, reference, power supply, and ground connections, and affects dynamic performance. High-speed, high-frequency applications require closely followed proper grounding and power-supply decoupling. These techniques reduce EMI and internal crosstalk that can significantly affect the MAX5876 dynamic performance.

Use a multilayer PCB with separate ground and powersupply planes. Run high-speed signals on lines directly above the ground plane. Keep digital signals as far away from sensitive analog inputs and outputs, reference input sense lines, and clock inputs as practical. Use a controlled-impedance, symmetric, differential design of clock input and the analog output lines to minimize 2nd-order harmonic distortion components, thus optimizing the DAC's dynamic performance. Keep digital signal paths short and run lengths matched to avoid propagation delay and data skew mismatches.

The MAX5876 requires five separate power-supply inputs for analog (AV<sub>DD1.8</sub> and AV<sub>DD3.3</sub>), digital (DV<sub>DD1.8</sub> and DV<sub>DD3.3</sub>), and clock (AV<sub>CLK</sub>) circuitry. All power-supply pins must be connected to their proper supply. Decouple each AV<sub>DD</sub>, DV<sub>DD</sub>, and AV<sub>CLK</sub> input pin with a separate 0.1µF capacitor as close to the device as possible with the shortest possible connection to the ground plane (Figure 9). Minimize the analog and digital load capacitances for optimized operation. Decouple all three power-supply voltages at the point they enter the PCB with

Figure 7. Differential-to-Single-Ended Conversion Using a Wideband RF Transformer

tantalum or electrolytic capacitors. Ferrite beads with additional decoupling capacitors forming a pi-network could also improve performance.

The analog and digital power-supply inputs AV<sub>DD3.3</sub>, AV<sub>CLK</sub>, and DV<sub>DD3.3</sub> allow a +3.135V to +3.465V supply voltage range. The analog and digital power-supply inputs AV<sub>DD1.8</sub> and DV<sub>DD1.8</sub> allow a +1.71V to +1.89V supply voltage range.

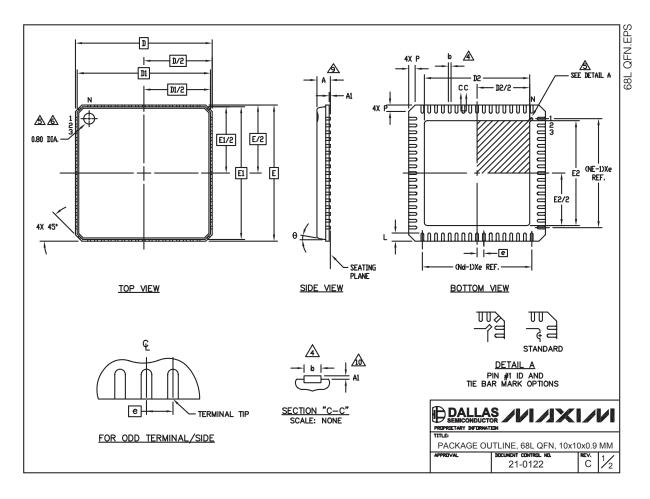

The MAX5876 is packaged in a 68-pin QFN-EP package, providing greater design flexibility, and optimized DAC AC performance. The EP enables the use of necessary grounding techniques to ensure highest performance operation. Thermal efficiency is not the key factor, since the MAX5876 features low-power operation. The exposed pad ensures a minimum inductance ground connection between the DAC and the PCB's ground layer.

The data converter die attaches to an EP lead frame with the back of this frame exposed at the package bottom surface, facing the PCB side of the package. This allows for a solid attachment of the package to the PCB with standard infrared reflow (IR) soldering techniques. A specially created land pattern on the PCB, matching the size of the EP (6mm x 6mm), ensures the proper attachment and grounding of the DAC (refer to the MAX5878 EV kit). Designing vias into the land area and implementing large ground planes in the PCB design allow for the highest performance operation of the DAC. Use an array of at least 4 x 4 vias (≤ 0.3mm diameter per via hole and 1.2mm pitch between via holes) for this 68-pin QFN-EP package. Connect the MAX5876 exposed paddle to **GND.** Vias connect the land pattern to internal or external copper planes to spread heat. Use as many vias as possible to the ground plane to minimize inductance.

Figure 8. Differential Output Configuration

## Static Performance Parameter Definitions Integral Nonlinearity (INL)

Integral nonlinearity is the deviation of the values on an actual transfer function from either a best straight-line fit (closest approximation to the actual transfer curve) or a line drawn between the end points of the transfer function, once offset and gain errors have been nullified. For a DAC, the deviations are measured at every individual step.

#### Differential Nonlinearity (DNL)

Differential nonlinearity is the difference between an actual step height and the ideal value of 1 LSB. A DNL error specification of less than 1 LSB guarantees a monotonic transfer function.

#### Offset Error

The offset error is the difference between the ideal and the actual offset current. For a DAC, the offset point is the average value at the output for the two midscale digital input codes with respect to the full scale of the DAC. This error affects all codes by the same amount.

#### Gain Error

A gain error is the difference between the ideal and the actual full-scale output voltage on the transfer curve, after nullifying the offset error. This error alters the slope of the transfer function and corresponds to the same percentage error in each step.

Figure 9. Recommended Power-Supply Decoupling and Bypassing Circuitry

## **Dynamic Performance Parameter Definitions**Signal-to-Noise Ratio (SNR)

For a waveform perfectly reconstructed from digital samples, the theoretical maximum SNR is the ratio of the full-scale analog output (RMS value) to the RMS quantization error (residual error). The ideal, theoretical minimum can be derived from the DAC's resolution (N bits):

#### $SNR_{dB} = 6.02_{dB} \times N + 1.76_{dB}$

However, noise sources such as thermal noise, reference noise, clock jitter, etc., affect the ideal reading; therefore, SNR is computed by taking the ratio of the RMS signal to the RMS noise, which includes all spectral components minus the fundamental, the first four harmonics, and the DC offset.

#### Noise Spectral Density

The DAC output noise floor is the sum of the quantization noise and the output amplifier noise (thermal and shot noise). Noise spectral density is the noise power in 1Hz bandwidth, specified in dBFS/Hz.

#### Spurious-Free Dynamic Range (SFDR)

SFDR is the ratio of RMS amplitude of the carrier frequency (maximum signal components) to the RMS value of their next-largest distortion component. SFDR is usually measured in dBc and with respect to the carrier frequency amplitude or in dBFS with respect to the DAC's full-scale range. Depending on its test condition, SFDR is observed within a predefined window or to Nyquist.

#### Two-/Four-Tone Intermodulation Distortion (IMD)

The two-tone IMD is the ratio expressed in dBc (or dBFS) of the worst 3rd-order (or higher) IMD product(s) to either output tone.

#### Adjacent Channel Leakage Power Ratio (ACLR)

Commonly used in combination with wideband codedivision multiple-access (W-CDMA), ACLR reflects the leakage power ratio in dB between the measured power within a channel relative to its adjacent channel. ACLR provides a quantifiable method of determining out-of-band spectral energy and its influence on an adjacent channel when a bandwidth-limited RF signal passes through a nonlinear device.

#### Settling Time

The settling time is the amount of time required from the start of a transition until the DAC output settles its new output value to within the converter's specified accuracy.

#### Glitch Impulse

A glitch is generated when a DAC switches between two codes. The largest glitch is usually generated around the midscale transition, when the input pattern transitions from 011...111 to 100...000. The glitch impulse is found by integrating the voltage of the glitch at the midscale transition over time. The glitch impulse is usually specified in pV•s.

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

| S<br>Y<br>M<br>B<br>O<br>L | СОММС          | N .  |                  |    |  |  |

|----------------------------|----------------|------|------------------|----|--|--|

| B <sub>O</sub> L           | MIN. NOM. MAX. |      | NO <sub>TE</sub> |    |  |  |

| Α                          | -              | 0.90 | 1.00             |    |  |  |

| A1                         | 0.00           | 0.01 | 0.05             | 11 |  |  |

| b                          | 0.18           | 0.23 | 0.30             | 4  |  |  |

| D                          | 10.00 BSC      |      |                  |    |  |  |

| D1                         | 9.75 BSC       |      |                  |    |  |  |

| е                          | 0.50 BSC       |      |                  |    |  |  |

| Ε                          | 10.00 BSC      |      |                  |    |  |  |

| E1                         | 9.75 BSC       |      |                  |    |  |  |

| L                          | 0.50           | 0.60 | 0.65             |    |  |  |

| N                          | 68             |      |                  |    |  |  |

| Nd                         | 17             |      |                  |    |  |  |

| Ne                         | 17             |      |                  |    |  |  |

| θ                          | 0              |      | 12*              |    |  |  |

| P                          | 0              | 0.42 | 0.60             |    |  |  |

- 1. DIE THICKNESS ALLOWABLE IS .012 INCHES MAXIMUM.

- 2. DIMENSIONING & TOLERANCES CONFORM TO ASME Y14.5M. 1994.

- N IS THE NUMBER OF TERMINALS.

Nd IS THE NUMBER OF TERMINALS IN X-DIRECTION &

Ne IS THE NUMBER OF TERMINALS IN Y-DIRECTION.

- DIMENSION b APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.20 AND 0.25mm FROM TERMINAL TIP.

- THE PIN #1 IDENTIFIER MUST BE LOCATED ON THE TOP SURFACE OF THE PACKAGE BY USING INDENTATION MARK OR OTHER FEATURE OF PACKAGE BODY. DETAILS OF PIN #1 IDENTIFIER IS OPTIONAL, BUT MUST BE LOCATED WITHIN ZONE INDICATED.

- 6 EXACT SHAPE AND SIZE OF THIS FEATURE IS OPTIONAL.

- 7. ALL DIMENSIONS ARE IN MILLIMETERS.

- 8. PACKAGE WARPAGE MAX 0.10mm.

- APPLIES TO EXPOSED SURFACE OF PADS AND TERMINALS

- △O APPLIES ONLY TO TERMINALS.

- 11. MEETS JEDEC MD-220.

| EXPOSED PAD VARIATIONS |      |      |      |      |      |      |  |  |  |

|------------------------|------|------|------|------|------|------|--|--|--|

|                        | D2   |      |      | E2   |      |      |  |  |  |

| PKG CODE               | MIN  | NDM  | MAX  | MIN  | NDM  | MAX  |  |  |  |

| G6800-2                | 7.55 | 7.70 | 7.85 | 7.55 | 7.70 | 7.85 |  |  |  |

| G6800-4                | 5.65 | 5.80 | 5.95 | 5.65 | 5.80 | 5.95 |  |  |  |

### Revision History

Pages changed at Rev 2: 1, 2, 3, 5, 13, 15, 16, 18

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_