**ON Semiconductor**

Is Now

# Onsemí

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

# **Linear CCD Image Sensor**

# Description

The KLI–8023 Image Sensor is a multispectral, linear solid state image sensor for color scanning applications where ultra-high resolution is required.

The imager consists of three parallel linear photodiode arrays, each with 8,000 active photosites for the output of red, green, and blue (R, G, B) signals. This device offers high sensitivity, high data rates, low noise and negligible lag. Individual electronic exposure control for each color allows the KLI–8023 sensor to be used under a variety of illumination conditions. The imager can be operated in an Extended Dynamic Range mode for the most demanding applications.

# Table 1. GENERAL SPECIFICATIONS

| Parameter                                                                   | Typical Value                                                                                 |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| Architecture                                                                | 3 Channel, RGB Trilinear CCD                                                                  |

| Pixel Count                                                                 | 8002 × 3                                                                                      |

| Pixel Size                                                                  | 9 μm (H) × 9 μm (V)                                                                           |

| Pixel Pitch                                                                 | 9 μm                                                                                          |

| Inter-Array Spacing                                                         | 108 μm (12 Lines Effective)                                                                   |

| Imager Size                                                                 | 72.0 mm (H) $\times$ 0.225 mm (V)                                                             |

| Saturation Signal                                                           | 185 ke <sup>−</sup> (Normal DR Mode)<br>400 ke <sup>−</sup> (Extended DR Mode)                |

| Dynamic Range<br>(2 MHz Data Rate)                                          | 84 dB (Normal DR Mode)<br>90 dB (Extended DR Mode)                                            |

| Responsivity<br>R, G, B (–RAA)<br>R, G, B (–DAA)<br>Mono (–AAA, –SAA, –MAA) | 32, 20, 20 V/μJ/cm <sup>2</sup><br>29, 19, 18 V/μJ/cm <sup>2</sup><br>33 V/μJ/cm <sup>2</sup> |

| Output Sensitivity                                                          | 14.4 μV/e <sup>-</sup>                                                                        |

| Dark Current                                                                | 0.002 pA/Pixel                                                                                |

| Dark Current Doubling Rate                                                  | 8°C                                                                                           |

| Charge Transfer Efficiency                                                  | 0.999998/Transfer                                                                             |

| Photoresponse Non-Uniformity                                                | 3% Peak-Peak                                                                                  |

| Lag (First Field)                                                           | 0.025%                                                                                        |

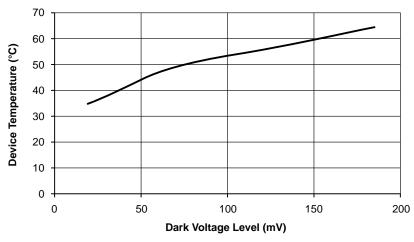

| Maximum Data Rate                                                           | 6 MHz/Channel                                                                                 |

| Package                                                                     | CERDIP (Sidebrazed, CuW)                                                                      |

| Cover Glass                                                                 | AR Coated, 2 Sides                                                                            |

NOTE: Parameters above are specified at T = 25°C (junction temperature) and 1 MHz clock rates unless otherwise noted.

# **ON Semiconductor®**

www.onsemi.com

# Figure 1. KLI–8023 Linear CCD Image Sensor

# Features

- 12 Line Spacing between Color Channels

- Single Shift Register per Channel

- High Off-Band Spectral Rejection

- Dark Reference Pixels Provided

- Anti-Reflective Glass

- Wide Dynamic Range, Low Noise

- Dual Dynamic Range Mode Operation

- No Image Lag

- Electronic Exposure Control

- High Charge Transfer Efficiency

- Two-Phase Register Clocking

- 74 ACT Logic Compatible Clocks

- 6 MHz Maximum Data Rate

# Applications

- Digitization

- Medical Imaging

- Photography

# **ORDERING INFORMATION**

See detailed ordering and shipping information on page 2 of this data sheet.

# **ORDERING INFORMATION**

# Table 2. ORDERING INFORMATION – KLI–8023 IMAGE SENSOR

| Part Number         | Description                                                                                                                                      | Marking Code                           |  |  |  |  |  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|--|--|--|--|

| KLI-8023-AAA-ED-AA  | I-8023-AAA-ED-AA Monochrome, No Microlens, CERDIP Package (Leadframe),<br>Clear Cover Glass with AR Coating (Both Sides), Standard Grade         |                                        |  |  |  |  |  |

| KLI-8023-AAA-ED-AE  | Monochrome, No Microlens, CERDIP Package (Leadframe),<br>Clear Cover Glass with AR Coating (Both Sides), Engineering Sample                      |                                        |  |  |  |  |  |

| KLI-8023-AAA-ER-AA  | Monochrome, No Microlens, CERDIP Package (Leadframe),<br>Clear Cover Glass with AR Coating (Both Sides), Standard Grade                          | KLI–8023 (Lot Code)<br>(Serial Number) |  |  |  |  |  |

| KLI-8023-AAA-ER-AE  | Monochrome, No Microlens, CERDIP Package (Leadframe),<br>Clear Cover Glass with AR Coating (Both Sides), Engineering Sample                      |                                        |  |  |  |  |  |

| KLI-8023-RAA-ED-AA  | Gen2 Color (RGB), No Microlens, CERDIP Package (Leadframe),<br>Clear Cover Glass with AR Coating (Both Sides), Standard Grade                    | KLI–8023 (Lot Code)<br>(Serial Number) |  |  |  |  |  |

| KLI-8023-RAA-ED-AE  | Gen2 Color (RGB), No Microlens, CERDIP Package (Leadframe),<br>Clear Cover Glass with AR Coating (Both Sides), Engineering Sample                |                                        |  |  |  |  |  |

| KLI-8023-SAA-ED-AA  | Monochrome with RB Surround – Gen2, No Microlens, CERDIP Package (Leadframe), Clear Cover Glass with AR Coating (Both Sides), Standard Grade     | KLI–8023 (Lot Code)<br>(Serial Number) |  |  |  |  |  |

| KLI-8023-SAA-ED-AE  | Monochrome with RB Surround – Gen2, No Microlens, CERDIP Package (Leadframe), Clear Cover Glass with AR Coating (Both Sides), Engineering Sample |                                        |  |  |  |  |  |

| KLI-8023-MAA-ED-AA* | Monochrome with RB Surround – Gen1, No Microlens, CERDIP Package (Leadframe), Clear Cover Glass with AR Coating (Both Sides), Standard Grade     | KLI–8023 (Lot Code)<br>(Serial Number) |  |  |  |  |  |

| KLI-8023-MAA-ED-AE* | Monochrome with RB Surround – Gen1, No Microlens, CERDIP Package (Leadframe), Clear Cover Glass with AR Coating (Both Sides), Engineering Sample |                                        |  |  |  |  |  |

| KLI-8023-DAA-ED-AA* | Gen1 Color (RGB), No Microlens, CERDIP Package (Leadframe),<br>Clear Cover Glass with AR Coating (Both Sides), Standard Grade                    | KLI–8023 (Lot Code)<br>(Serial Number) |  |  |  |  |  |

| KLI-8023-DAA-ED-AE* | Gen1 Color (RGB), No Microlens, CERDIP Package (Leadframe),<br>Clear Cover Glass with AR Coating (Both Sides), Engineering Sample                |                                        |  |  |  |  |  |

\*Not recommended for new designs.

# Table 3. ORDERING INFORMATION – EVALUATION SUPPORT

| Part Number         | Description                     |

|---------------------|---------------------------------|

| KLI-8023-12-5-A-EVK | Evaluation Board (Complete Kit) |

See the ON Semiconductor *Device Nomenclature* document (TND310/D) for a full description of the naming convention used for image sensors. For reference documentation, including information on evaluation kits, please visit our web site at <u>www.onsemi.com</u>.

# **DEVICE DESCRIPTION**

# Dark Reference Pixels

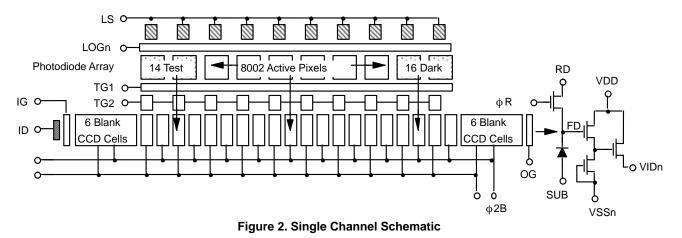

Dark reference pixels are groups of photosensitive pixels covered by a metal light shield. These pixels are used as a black level reference for the image sensor output. Since the incident light is blocked from entering these pixels, the signal contained in these pixels is due only to dark current. It is assumed that each photosensitive pixel (active and dark reference) will have approximately the same dark signal; thus, subtracting the average dark reference signal from each active pixel signal will remove the background dark signal level. Dark reference pixels are typically located at one or both ends of the arrays, as shown earlier in this document for a linear image sensor in the single channel schematic.

# Dynamic Range

Dynamic Range (DR) is the ratio of the maximum output signal, or saturation level, of an image sensor to the dark noise level of the imager. The dark noise level, or noise floor of an imager is typically expressed as the root mean square (rms) variation in dark signal voltage. The dark signal includes components from dark current within the photosite and CCD regions, reset transistor and output amplifier noise, and input clocking noise. An input referred noise signal in the charge domain can be calculated by dividing the dark noise voltage by the imager charge-to-voltage conversion factor. The dynamic range is typically expressed in units of decibels as:  $DR = 20 \cdot LOG (N_{SAT} / Noise)$ .

# High Dynamic Range Mode (DR)

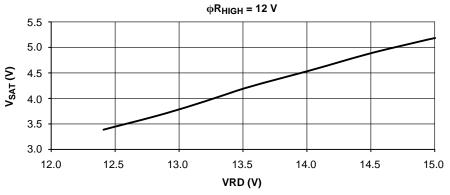

Two modes of device operation can be realized, the 'normal mode' and 'high dynamic range mode'. In 'the normal mode' of operation, clocking of the output structure reset gate (PHIR, pin 12) remains similar to all other clocks at 6.25 Vp-p. The usable saturation exposure in this mode is approximately 180,000 electrons, yielding a saturation voltage of 2.5 volts. In the 'high dynamic range' mode, the reset gate clocking is increased to 12 Vp-p and the reset drain bias (RD, pin 29) is increased to the upper amplifier supply voltage (VDD, pin 26). The usable saturation exposure in this mode increases to  $400,000 e^{-1}$  with a saturation voltage in excess of 5 volts.

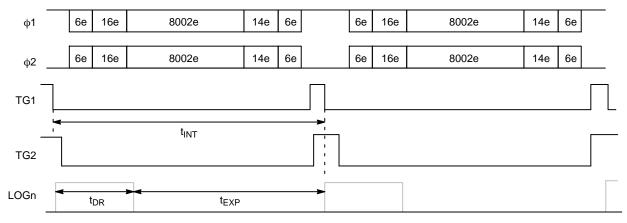

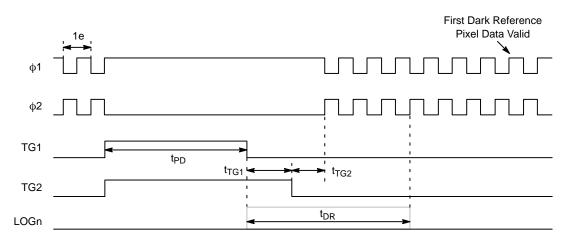

# **Image Acquisition**

During the integration period, an image is obtained by gathering electrons generated by photons incident upon the photodiodes. The charge collected in the photodiode array is a linear function of the local exposure. The charge is stored in the photodiode itself and is isolated from the CCD shift registers during the integration period by the transfer gates TG1 and TG2, which are held at barrier potentials. At the end of the integration period, the CCD register clocking is stopped with the  $\phi 1$  and  $\phi 2$  gates being held in a 'high' and 'low' state respectively. Next, the TG gates are turned 'on' causing the charge to drain from the photodiode into the TG1 storage region. As TG1 is turned back 'off' charge is transferred through TG2 and into the  $\phi$ 1 storage region. The TG2 gate is then turned 'off', isolating the shift registers from the accumulation region once again. Complementary clocking of the  $\phi 1$  and  $\phi 2$  phases now resumes for readout of the current line of data while the next line of data is integrated.

# **Charge Transport**

Readout of the signal charge is accomplished by two-phase, complementary clocking of the  $\phi 1$  and  $\phi 2$  gates. The register architecture has been designed for high speed clocking with minimal transport and output signal degradation, while still maintaining low (6.25 Vp-p min) clock swings for reduced power dissipation, lower clock noise and simpler driver design. The data in all registers is clocked simultaneously toward the output structures. The signal is then transferred to the output structures in a parallel format at the falling edge of the  $\phi 2$  clocks. Re-settable floating diffusions are used for the charge-to-voltage conversion while source followers provide buffering to external connections. The potential change on the floating diffusion is dependent on the amount of signal charge and is given by  $\Delta V_{FD} = \Delta Q / C_{FD}$ , where  $\Delta V_{FD}$  is the change in potential of the floating diffusion,  $\Delta Q$  is the amount of charge deposited on the floating diffusion, and  $C_{FD}$  is the floating diffusion capacitance. Prior to each pixel output, the floating diffusion is returned to the RD level by the reset clock,  $\phi R$ .

### Charge Transfer Efficiency

Charge Transfer Efficiency (CTE) is a measure of how efficiently electronic charge can be transported by a Charge Coupled Device (CCD). This parameter is especially important in linear imager technology due to the fact that CCDs are often required to transport charge packets over long distances at very high speeds. The result of poor CTE is to reduce the overall MTF of the line image in a nonlinear fashion: the portion of the line image at the far end of the CCD will be degraded more than the image at the output end of the CCD, since it will undergo more CCD transfers. There are many possible mechanisms that can negatively influence the CTE. Amongst these mechanisms are included excessive CCD clocking frequency, insufficient drive potential on the CCD clocking gates, and incorrect voltage bias on the output gate (OG signal). The effect of these mechanisms is that some charge is "left behind" during a CCD transfer clocking cycle. Depending on the limiting mechanism, the lost charge could be added to the immediate trailing cell or to a cell further back in time; thus, causing a horizontal smearing of the line image.

The charge lost from a CCD cell, after being transferred out of the CCD, is measured with respect to the original charge level and is termed the charge transfer inefficiency (CTI). CTI is defined as:

$$CTI = \left(\frac{\text{Total Charge Lost}}{\text{Initial Charge}}\right) \cdot \left(\frac{1}{\text{Number of Transfers}}\right)$$

The efficiency of the CCD transfer (CTE) is then defined as simply:

$$CTE = 1 - CTI$$

Note that the total transfer efficiency for the entire line (TTE) is equal to (CTE)N, where N is the total number of transfers which is equal to the number of phases per cell, times the number of cells (n).

$$\mathsf{TTE} = \mathsf{CTE} \cdot 2 \cdot 8022$$

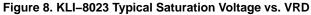

### Dark Signal Evaluation

The dark signal evaluation measures the thermally generated electronic current (i.e. background noise signal) at a specific operating temperature. Dark current is measured will all incident radiation removed (i.e. imager is in the dark). The current measured by the picoammeter is the dark current of the photodiode array plus the dark current of the CCD array. Multiplying the dark current by the total integration time yields the quantity of dark charge. And dividing the dark current per photodiode (I<sub>Dark</sub>). Dark voltage increases linearly with integration time, the worst-case

value occurs at the slowest clocking frequency. Additionally, dark current doubles for approximately every 8°C increase in temperature.

### Fixed Pattern Noise

If the output of an image sensor under no illumination is viewed at high gain, a distinct non-uniform pattern or fixed pattern noise can be seen. This fixed pattern can be removed from the video by subtracting the dark value of each pixel from the pixel values read out in all subsequent frames. Dark fixed pattern noise is usually caused by variations in dark current across an imager, but can also be caused by input clocking signals abruptly starting or stopping, or by having the CCD clocks not being close compliments of each other. Mismatched CCD clocks can result in high instantaneous substrate currents, which when combined with the fact that the silicon substrate has some non-zero resistance, can result in the substrate potential bouncing. The pattern noise can also be seen when the imager is under uniform illumination. An imager that exhibits a fixed pattern noise under uniform illumination and shows no pattern in the dark is said to have light pattern noise or photosensitivity pattern noise. In addition to the reasons mentioned above, light pattern noise can be caused by the imager entering saturation, the nonuniform clipping effect of the anti-blooming circuit, and by non-uniform photosensitive pixel areas often caused by debris covering portions of some pixels.

### **Exposure** Control

Exposure control is implemented by selectively clocking the LOG gates during portions of the scanning line time. By applying a large enough positive bias to the LOG gate, the channel potential is increased to a level beyond the 'pinning level' of the photodiode. (The 'pinning' level is the maximum channel potential that the photodiode can achieve and is fixed by the doping levels of the structure.) With TG1 in an 'off' state and LOG strongly biased, all of the photocurrent will be drawn off to the LS drain. Referring to the timing diagrams in Figure 12 and Figure 13, one notes that the exposure can be controlled by pulsing the LOG gate to a 'high' level while TG1 is turning 'off' and then returning the LOG gate to a 'low' bias level sometime during the line scan. The effective exposure  $(t_{EXP})$  is the net time between the falling edge of the LOG gate and the falling edge of the TG1 gate (end of the line). Separate LOG connections for each channel are provided, enabling on-chip light source and image spectral color balancing. As a cautionary note, the switching transients of the LOG gates during line readout may inject an artifact at the sensor output. Rising edge artifacts can be avoided by switching LOG during the photodiode-to-CCD transfer period, preferably during the TG1 falling edge. Depending on clocking speeds, the falling edge of the LOG should be synchronous with the  $\phi 1/\phi 2$  shift register readout clocks. For very fast applications, the falling edge of the LOG gate may be limited by on-chip RC delays across the array. In this case artifacts may extend across one or more pixels. Correlated double sampling (CDS) processing of the output waveform can remove the first order magnitude of such artifacts. In high dynamic range applications, it may be advisable to limit the LOG fall times to minimize the current transients in the device substrate and limit the magnitude of the artifact to an acceptable level.

# Lag

Lag, or decay lag is a measure of the amount of photogenerated charge left behind during a photodiode-to-CCD transfer cycle. Ideally, no charge is left behind during such transfers and lag is equal to zero; that is, 100% of the collected photogenerated charge is transferred to the adjacent CCD. The use of "pinned" photodiode technology enables the linear imagers to achieve near perfect lag performance. Improper Transfer Gate (TG) clocking levels can introduce a lag type response. Thus, care must be taken to ensure that the clocking levels are not limiting the lag performance.

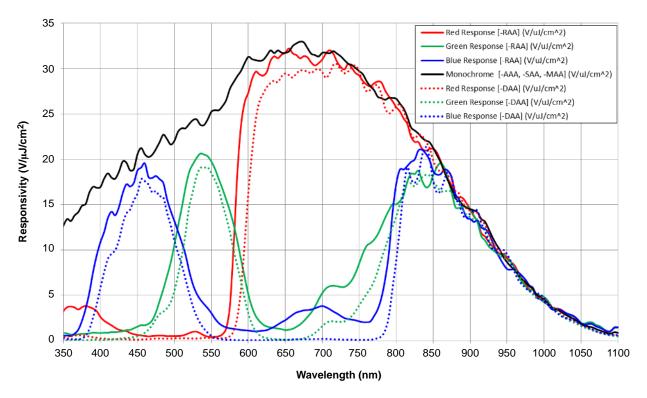

### Imager Responsivity

Responsivity is a measure of the imager output when exposed to a given optical energy density. It is measured on monochrome and color (if applicable) versions of an imager over the entire wavelength range of operation. Imagers having multiple photodiode arrays with differing color filters and/or photodiode dimensions have responsivity measured on each array. Responsivity is reported in units of:

$$\frac{V}{uJ/cm^2}$$

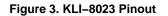

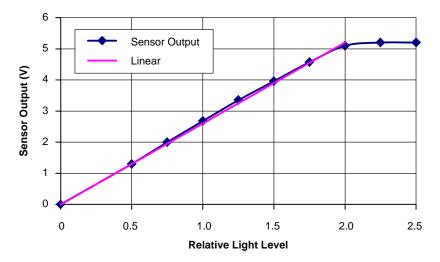

### Linearity

The non-linearity of an image sensor is typically defined as the percent deviation from the ideal linear response, which is defined by the line passing through V<sub>SAT</sub> and V<sub>DARK</sub>. The percent linearity is then 100 minus the non-linearity. The output linearity of a solid-state image sensor is determined from the linearity of the photon collection process, the electron exposure structure non-linearities (if any exists), the efficiency of charge transportation from the photosite to the output amplifier, and the output amplifier linearity. The absorption of photons within the silicon substrate can be considered an ideal linear function of incident illumination level when averaged over a given period of time. The existence of an electronic exposure control circuit adjacent to the photosensitive sites can introduce a non-linearity into the overall response by allowing small quantities of charge to remain isolated in unwanted potential wells. Whether or not any potential wells exist depends on the design and manufacturing of the particular image sensor. The existence of such potential wells in the exposure circuitry, also called exposure control defects, will degrade the linearity only at small signal levels

and may be different from one photosite to the next. An image sensor with excessive exposure control defects would be rejected during quality assurance testing. The loss of charge during the transportation of charge packets from the photosite to the CCD, which is termed lag, tends to affect the linearity only at very small signal levels. "Pinned" photodiodes, or buried photodiodes, have extremely small lag (< 0.5%), and can be considered to be lag free. The CCD charge transfer inefficiency (CTI) will reduce the amplitude of the charge packet as it is transported towards the output amplifier, with the greatest effect realized at very small signal levels. Modern CCD's have CTE in excess of 0.999999 per CCD transfer; thus, the overall effect on linearity is generally not a concern. If biased properly, the output amplifier will yield a non-linearity of typically less than 2%. Non linearity at signal levels beyond the saturation level is expected and can often vary significantly from pixel to pixel.

# Linearity Evaluation

Ideally, the output video amplitude should vary linearly with incident light intensity over the entire input range of irradiance. There are many possible phenomena that can cause non-linearity in the response curve; inadequate CTE and improper biasing or clocking to name a few.

Electronic exposure control could be used to vary the photodiode integration time; however, since electronic exposure control can introduce non-linearity, it is not recommended as a method of limiting the input signal. The output signal versus relative irradiance is graphed and a least squares, linear regression fit to the data is performed. The best fit data curve should pass through zero volts and remain linear ( $R^2 > 0.99$ ) up to the V<sub>SAT</sub> level.

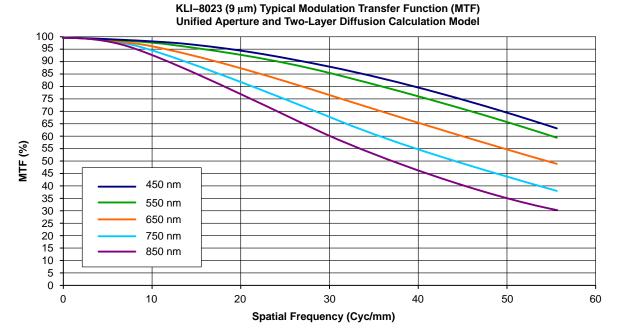

# Modulation Transfer Function (MTF)

MTF is the magnitude of the spatial frequency response of a solid-state imager. The three main components of imager MTF are termed the aperture MTF, diffusion MTF, and charge transfer efficiency MTF. The aperture MTF results from the discrete sampling nature of solid-state imagers, with smaller pixel pitches yielding a better high frequency MTF response. The diffusion of photogenerated charge degrades the imager response and is responsible for the second component. The third component is due to inefficient charge transfer in the shift register. The maximum spatial frequency an imager can detect without aliasing occurring is defined as the Nyquist frequency and is equal to the inverse of two times the pixel pitch. MTF is typically reported at the Nyquist frequency, 1/2 Nyquist, and 1/4 Nyquist. The aperture MTF limits the maximum response at Nyquist to 0.637. (Note that the maximum MTF response is 1.0). The diffusion component will further degrade this value, especially at longer optical wavelengths.

### Noise

Noise is defined as any unwanted signal added to the imager output. Temporal noise sources present in a typical imager include the dark current, photon shot noise, reset transistor noise, CCD clocking noise, and the output amplifier noise. Dark current is dependent on the imager operating temperature and can be reduced by cooling the imager. The reset transistor noise can be removed using correlated double sampling signal processing. The photon shot noise cannot be eliminated; however, by acquiring and averaging several frames it, and all temporal noise sources, can be reduced. Another source of noise is the variation in dark current from pixel to pixel leads to a dark noise pattern across an imager. The effects of this dark pattern noise can also be minimized by averaging several frames and then using the pixel-referenced, dark frame data as the zero reference level for each pixel.

### Noise Evaluation

The noise evaluation measures the noise levels associated with operating the imager at the specified clocking speeds and temperatures. The test is performed with imager temperature held stable and all incident light removed. The noise contributions of the evaluation circuitry also need to be removed from the calculation. Once this is done, the total imager noise will be approximately equal to the sum of squares of each of the CCD clocking noise, output amplifier noise, and the dark current noise.

### Photodiode Quantum Efficiency

For a given area, absolute quantum efficiency is defined as the ratio of the number of photogenerated electrons captured during an integration period to the number of impinging photons during that period. Higher values indicate a more efficient photon conversion process and hence are more desirable.

Absolute photodiode quantum efficiency is calculated from the charge-to-voltage, imager responsivity, and measured active photodiode area. It is calculated over the entire wavelength range of operation and graphed on a curve as percent Quantum Efficiency versus Wavelength.

Once the charge-to-voltage, responsivity, and active photodiode dimensions have all been measured, the absolute quantum efficiency can be calculated as:

Quantum Efficiency ( $\lambda$ ) = Responsivity ( $\lambda$ ) ÷

$\div$  Active Photodiode Area  $\times$

$\times$  Energy per Photon ( $\lambda$ )

where

Energy per Photon (

$$\lambda$$

) =  $\frac{h \cdot c}{\lambda}$

and

$h \cdot c = 1.98647E - 25 [J - m]$

Care should be taken to ensure that all quantities are represented in similar units before any calculations are performed. Using the above formulas, the absolute quantum efficiency can be expressed as:

$$QE(\lambda) = 100\% \cdot R(\lambda) \div \frac{dV}{dN_e} \div Area_{Diode} \cdot \frac{h \cdot c}{\lambda}$$

### Photoresponse Non-Uniformity (PRNU)

The PRNU measurement is taken in a flat field of collimated white light. The intensity of the light is set to a value approximately 10% to 20% below the saturated signal level. One region (or "window") of pixels is observed for uniformity at a given time, and the average response is calculated for each non-overlapping windowed section. In the case of medium or low frequency PRNU measurements, a medium filter of 3–7 pixels is applied to this region to eliminate the effects of single point defects. The maximum and minimum pixel is determined for each windowed section. Again, for each section, the following formula is applied:

$$PRNU = 100\% \cdot \left(\frac{Max_Pixel_Value - Min_Pixel_Value}{Mean_Pixel_Value}\right)$$

Each section is then compared against the specification to identify the region with the largest percent deviation from the average response for the imager.

### Resolution

The resolution of a solid-state image sensor is the spatial resolving power of that sensor. The spatial resolution of a sensor is descried in the spatial frequency domain by the modulation transfer function (MTF). The discrete sampling nature of solid-state image sensors gives rise to a sampling frequency that will determine the upper limit of the sensor's frequency response. Resolution is frequently described in terms of the number of dots or photosites per inch (DPI) in the imager or object planes. For example, a linear image sensor with a single array of 1,000 photosites of pitch 10 µm would have a resolution of 2,540 DPI (1,000 / (1,000  $\cdot$  0.01 mm  $\cdot$  1"/25.4 mm)). If the sensor were used in an optical system to image an 8" wide document, then the resolution in the document plane would be 125 DPI (1,000 pixels / 8"). This example is slightly misleading in that it does not consider the frequency response of the sensor or the optics. In reality, the sensor will have an MTF of between 0.2 and 0.7 at the Nyquist spatial frequency and the optics are likely to have an MTF of 0.6 to 0.9 at the Nyquist frequency. It is important to note that even though a sensor may have a high enough sampling frequency for a particular application, the overall frequency response of the sensor and optics may not be sufficient for that application!

# Saturation Voltage

The saturated signal level is the output voltage corresponding to the maximum charge packet the imager can handle. Adding charge above the saturated level results in the excess charge "spilling" over into neighboring photosites or CCD structures. Either the photodiode capacity or the CCD capacity, with the latter being the most typical case, can limit the charge capacity. The saturated signal level is measured by monitoring the dark-to-light transition between the first-out dark reference pixels and the first active pixels while the irradiance is slowly increased. Note that improper settings on either the output gate (OG) or the reset gate ( $\phi$ R) can have a clipping effect on the output waveform.

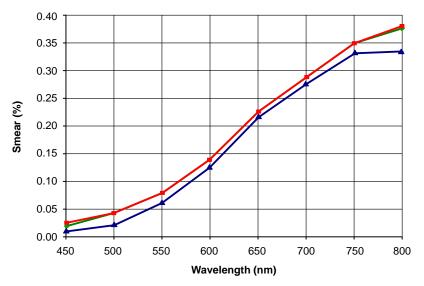

# Smear

Smear, also referred to as Photodiode-to-CCD Crosstalk, occurs when photogenerated charge diffuses to an adjacent CCD (such as a transfer register) and is collected, as opposed to being collected in the photodiode where the photon absorption occurred. The result of smear is to increase the background signal within the dark reference pixels and CCD buffer pixels. This increased background signal reduces the achievable dynamic range; hence, a high smear value is undesirable. The further the photodiode array and the CCD are apart, the less the smear. Contributors to increased smear are a short photodiode-to-CCD separation and improper transfer gate clocking levels or timing. Smear is also highly dependent on incident photon wavelength. In the application, an IR cut-off filter (~710 nm) is recommended.

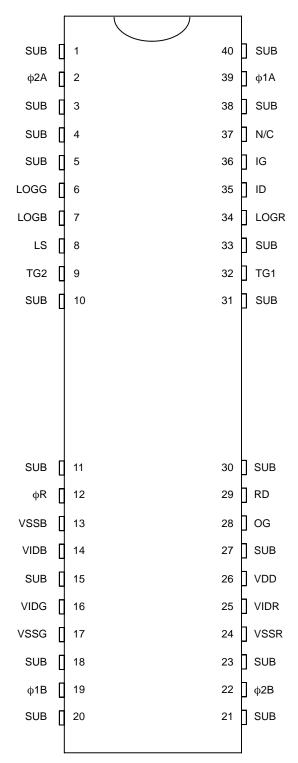

# **Physical Description**

Pin Description and Device Orientation

# Table 4. PACKAGE PIN DESCRIPTION

| Pin | Name | Description                                |

|-----|------|--------------------------------------------|

| 1   | SUB  | Substrate/Ground                           |

| 2   | φ2n  | Phase 2 CCD Clock (n = A or B)             |

| 3   | SUB  | Substrate/Ground                           |

| 4   | SUB  | Substrate/Ground                           |

| 5   | SUB  | Substrate/Ground                           |

| 6   | LOGn | Exposure Control for Channel (n = R, G, B) |

| 7   | LOGn | Exposure Control for Channel (n = R, G, B) |

| 8   | LS   | Light Shield/Exposure Drain                |

| 9   | TG2  | Transfer Gate 2 Clock                      |

| 10  | SUB  | Substrate/Ground                           |

| 11  | SUB  | Substrate/Ground                           |

| 12  | φR   | Reset Clock                                |

| 13  | VSSn | Ground Reference (n = R, G, B)             |

| 14  | VIDn | Blue Output Video (n = R, G, B)            |

| 15  | SUB  | Substrate/Ground                           |

| 16  | VIDn | Blue Output Video (n = R, G, B)            |

| 17  | VSSn | Ground Reference (n = R, G, B)             |

| 18  | SUB  | Substrate/Ground                           |

| 19  | φ1n  | Phase 1 CCD Clock (n = A or b)             |

| 20  | SUB  | Substrate/Ground                           |

| 21  | SUB  | Substrate/Ground                           |

| 22  | φ2n  | Phase 2 CCD Clock (n = A or B)             |

| 23  | SUB  | Substrate/Ground                           |

| 24  | VSSn | Ground Reference (n = R, G, B)             |

| 25  | VIDn | Blue Output Video (n = R, G, B)            |

| 26  | VDD  | Amplifier Supply                           |

| 27  | SUB  | Substrate/Ground                           |

| 28  | OG   | Output Gate                                |

| 29  | RD   | Reset Drain                                |

| 30  | SUB  | Substrate/Ground                           |

| 31  | SUB  | Substrate/Ground                           |

| 32  | TG1  | Transfer Gate 1                            |

| 33  | SUB  | Substrate/Ground                           |

| 34  | LOGn | Exposure Control for Channel (n = R, G, B) |

| 35  | ID   | Test Input – Input Diode                   |

| 36  | IG   | Test Input – Input Gate                    |

| 37  | SUB  | Substrate/Ground                           |

| 38  | SUB  | Substrate/Ground                           |

| 39  | φ1n  | Phase 1 CCD Clock (n = A or B)             |

| 40  | SUB  | Substrate/Ground                           |

# **IMAGING PERFORMANCE**

# **Typical Operational Conditions**

Specifications given under nominally specified operating conditions for the given mode of operation at 25°C,

$f_{CLK} = 1$  MHz, AR coverglass, color filters, and an active load as shown in Figure 4 unless otherwise specified. See notes on next page for further descriptions.

# Table 5. SPECIFICATIONS

| Description                                          | Symbol                    | Min.           | Nom.              | Max.        | Units                | Notes             | Verification<br>Plan |

|------------------------------------------------------|---------------------------|----------------|-------------------|-------------|----------------------|-------------------|----------------------|

| HIGH DYNAMIC RANGE MODE (V                           | RD = 15 V, φR             | (High) = 12 V) |                   |             | 1                    |                   |                      |

| Saturation Output Voltage                            | V <sub>SAT</sub>          | 5.2            | 5.5               | -           | Vp-p                 | 1, 9              | Die <sup>17</sup>    |

| Output Sensitivity                                   | $\Delta V_O / \Delta N_e$ | -              | 14                | -           | μV/e <sup>-</sup>    |                   | Design <sup>18</sup> |

| Saturation Signal Charge                             | N <sub>e,SAT</sub>        | -              | 400               | -           | ke-                  |                   | Design <sup>18</sup> |

| Dynamic Range                                        | DR                        | -              | 87                | -           | dB                   | 3                 | Design <sup>18</sup> |

| Dark Signal Non-Uniformity                           | DSNU                      | -              | 0.006             | 0.02        | V                    |                   | Design <sup>18</sup> |

| DC Gain, Amplifier                                   | A <sub>DC</sub>           | 0.725          | 0.775             | 0.825       |                      |                   | Design <sup>18</sup> |

| Dark Current                                         | IDARK                     | -              | 0.003             | 0.005       | pA/pixel             |                   | Design <sup>18</sup> |

| Charge Transfer Efficiency                           | CTE, η                    | 0.999995       | -                 | -           |                      | 5                 | die <sup>17</sup>    |

| Lag                                                  | L                         | -              | 0.003             | 0.06        | %                    |                   | Design <sup>18</sup> |

| DC Output Offset                                     | V <sub>O,DC</sub>         | 8              | 11                | 13          | V                    | 9                 | Design <sup>18</sup> |

| Darkfield Defect, Brightpoint                        | Dark Def                  | _              | -                 | 0           | Allowed              | 12                | Die <sup>17</sup>    |

| Brightfield Defect, Dark or Bright                   | Bfld Def                  | _              | _                 | 0           | Allowed              | 13                | Die <sup>17</sup>    |

| Exposure Control Defects                             | Exp Def                   | -              | -                 | 32          | Allowed              | 11, 14,<br>15, 16 | Die <sup>17</sup>    |

| <b>NORMAL MODE</b> (VRD = 11 V, $\phi$ R (           | High) = 6.5 V)            |                | 1                 |             |                      |                   | 4                    |

| Saturation Output Voltage                            | V <sub>SAT</sub>          | 2.3            | 2.6               | -           | Vp-p                 | 1, 9              | Design <sup>18</sup> |

| Saturation Signal Charge                             | N <sub>SAT</sub>          | _              | 200               | _           | ke-                  |                   | Design <sup>18</sup> |

| Dynamic Range                                        | DR                        | 78             | 82                | -           | dB                   | 3                 | Design <sup>18</sup> |

| DC Output Offset                                     | V <sub>ODC</sub>          | 5.5            | 7.75              | 10          | V                    | 9                 | Design <sup>18</sup> |

| KLI-8023-RAA CONFIGURATION                           | GEN2 COLOR                |                |                   |             | 1                    |                   |                      |

| Responsivity<br>Red<br>Green<br>Blue                 | R <sub>MAX</sub>          | -<br>-<br>-    | 29<br>19<br>18    |             | V/μJ/cm <sup>2</sup> |                   | Design <sup>18</sup> |

| Peak Responsivity Wavelength<br>Red<br>Green<br>Blue | λR                        | -<br>-<br>-    | 650<br>540<br>460 | -<br>-<br>- | nm                   |                   | Design <sup>18</sup> |

| Photoresponse Uniformity,<br>Low Frequency           | PRNU.<br>Low              | -              | 5                 | 10          | %р-р                 |                   | Die <sup>17</sup>    |

| Photoresponse Uniformity,<br>Medium Frequency        | PRNU.<br>Medium           | -              | 5                 | 10          | %р-р                 |                   | Die <sup>17</sup>    |

# Table 5. SPECIFICATIONS (continued)

| Description | Symbol | Min. | Nom. | Max. | Units | Notes | Verification<br>Plan |  |

|-------------|--------|------|------|------|-------|-------|----------------------|--|

|             |        |      |      |      |       |       |                      |  |

# KLI-8023-DAA CONFIGURATION GEN1 COLOR (Note 19)

| Responsivity<br>Red<br>Green<br>Blue            | R <sub>MAX</sub> |                  | 32<br>20<br>20    |             | V/μJ/cm <sup>2</sup> | Design <sup>18</sup> |

|-------------------------------------------------|------------------|------------------|-------------------|-------------|----------------------|----------------------|

| Responsivity Wavelength<br>Red<br>Green<br>Blue | λR               | _<br>_<br>_<br>_ | 650<br>540<br>460 | -<br>-<br>- | nm                   | Design <sup>18</sup> |

| Photoresponse Uniformity,<br>Low Frequency      | PRNU.<br>Low     | _                | 4                 | 7           | %р-р                 | Die <sup>17</sup>    |

| Photoresponse Uniformity,<br>Medium Frequency   | PRNU.<br>Medium  | -                | 4                 | 7           | %р-р                 | Die <sup>17</sup>    |

# KLI-8023-AAA, KLI-8023-SAA, AND KLI-8023-MAA CONFIGURATION MONOCHROME (Note 19)

| Responsivity<br>Monochrome                    | R <sub>MAX</sub> | _ | 33  | _ | V/µJ/cm <sup>2</sup> | Design <sup>18</sup> |

|-----------------------------------------------|------------------|---|-----|---|----------------------|----------------------|

| Responsivity Wavelength<br>Monochrome         | λR               | _ | 675 | _ | nm                   | Design <sup>18</sup> |

| Photoresponse Uniformity,<br>Low Frequency    | PRNU.<br>Low     | - | 4   | 7 | %р-р                 | Die <sup>17</sup>    |

| Photoresponse Uniformity,<br>Medium Frequency | PRNU.<br>Medium  | - | 4   | 7 | %р-р                 | Die <sup>17</sup>    |

1. Defined as the maximum output level achievable before linearity or PRNU performance is degraded beyond specification.

With color filter. Values specified at filter peaks. 50% bandwidth = ±30 nm. Color filter arrays become transparent after 710 nm. It is

recommended that a suitable IR cut filter be used to maintain spectral balance and optimal MTF. See Figure 5.

3. As measured at 2 MHz data rate. This device utilizes 2-phase clocking for cancellation of driver displacement currents. Symmetry between φ1 and φ2 phases must be maintained to minimize clock noise.

4. Dark current doubles approximately every +8°C.

5. Measured per transfer. For the total line:  $(0.999995) \cdot 16044 = 0.9229$ .

- 6. Low frequency response is measured across the entire array with a 1,000 pixel-moving window and a 5 pixel median filter evaluated under a flat field illumination.

- 7. Medium frequency response is measured across the entire array with a 50 pixel-moving window and a 5 pixel median filter evaluated under a flat field illumination.

- 8. High frequency response non-uniformity represents individual pixel defects evaluated under a flat field illumination. An individual pixel value may deviate above or below the average response for the entire array. Zero individual defects allowed per this specification.

- 9. Increasing the current load (nominally 4 mA) to improve signal bandwidth will decrease these parameters.

- 10. If resistive loads are used to set current, the amplifier gain will be reduced, thereby reducing the output sensitivity and net responsivity. (e.g. with 2.2 k $\Omega$  loads to ground, the sensitivity drops to 12.5  $\mu$ V per electron).

- 11. Defective pixels will be separated by at least one non-defective pixel within and across channels.

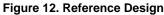

- 12. Pixels whose response is greater than the average response by the specified threshold, (16 mV). See Figure 4.

- 13. Pixels whose response is greater or less than the average response by the specified threshold, (±10%). See Figure 4.

- 14. Pixels whose response deviates from the average pixel response by the specified threshold, (4 mV), when operating in exposure control mode. See Figure 4. If dark pattern correction is used with exposure control, the dark pattern acquisition should be completed with exposure control actuated. Dark current tends to suppress the magnitude of these defects as observed in typical applications, hence line rate changes may affect perceived defect magnitude. Note: Zero defects allowed for those pixels whose response deviates from the average pixel response by a 20 mV threshold.

- 15. Defect coordinates are available upon request.

- 16. The quantity and type of defects acceptable for a specific application will be negotiated with each customer.

- 17. A parameter that is measured on every sensor during production testing.

- 18. A parameter that is quantified during the design verification activity.

- 19 Configuration KLI-8023–DAA and KLI-8023–MAA uses Gen1 color filter set and is not recommended for new designs.

# **TYPICAL PERFORMANCE CURVES**

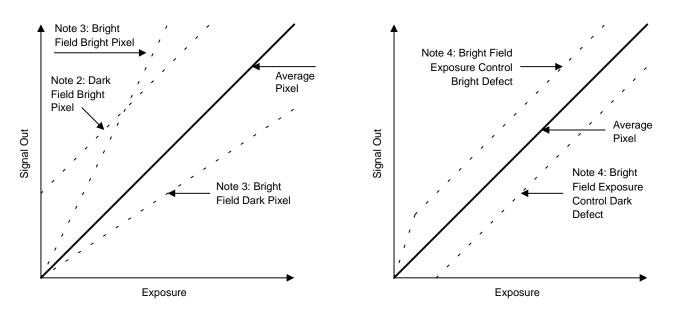

# **Defective Pixel Classification**

Figure 4. Illustration of Defect Classifications

Figure 5. KLI–8023 Typical Responsivity

Figure 6. KLI–8023 Typical Modulation Transfer Function

Figure 10. KLI–8023 Typical CCD Temperature vs. Operating Frequency

Figure 11. KLI-8023 Typical Device Response Linearity

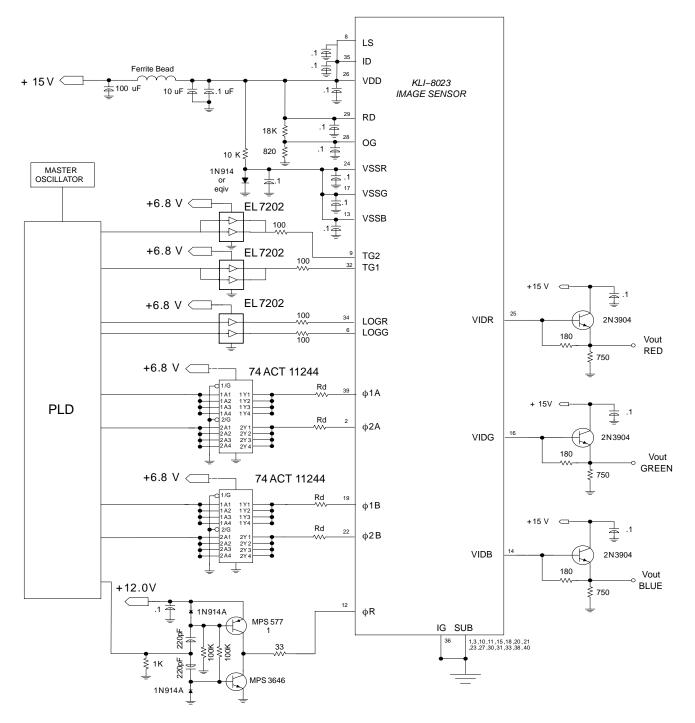

# KLI-8023 Reference Design

The KLI-8023 Reference Design provides a baseline reference for the design of a KLI-8023 image sensor into your electronic imaging application. The circuit below uses

inexpensive off-the-shelf components to provide voltage-translated clock signals and DC bias supplies required to support the KLI–8023.

# **REFERENCE DESIGN CIRCUIT OVERVIEW**

# **Programmable Logic**

See the timing waveform requirements earlier in this document before programming a logic device.

# **Clock Drivers**

There are three types of clock drivers (voltage translating buffers) used in this reference design. The most important performance consideration is the ability of the clock driver to drive the capacitive loads presented by the various gates of the CCD.

# Reset Driver

The RESET, ( $\phi$ R), gate presents a small capacitive load of 100 pF, and requires fast rise and fall times. The complimentary bipolar switching transistor circuit shown in Figure 12 provides a low cost solution. The circuit alternately drives the PNP and NPN transistors into saturation, which switches the output between VCC and ground. A 33- $\Omega$  series-damping resistor is used to suppress ringing.

# Exposure Control and Transfer Gates

The exposure control gates; LOGR and LOGG, and the transfer gates; TG1 and TG2 each present a moderate capacitive load of 500 pF. The Elantec 7202 Dual-Channel Power MOSFET driver delivers a peak output current of 2 amperes: more than enough to meet the rise and fall requirements of the LOG and TG gates. Series damping resistors are used to prevent ringing in the LOGR and LOGG gates. The transfer gates are connected together and driven by a single EL7202.

# CCD Shift Register Driver

The CCD clock phases ( $\phi$ 1A,  $\phi$ 2A,  $\phi$ 1B and  $\phi$ 2B) present a significant load of 3,100 pF per phase. Two 74ACT11244 octal buffers provide an efficient solution. Each clock phase is driven by four gates connected in parallel to increase output drive current. The 6.5-volt swing required by the shift register is obtained by setting VCC to 6.8 V. Series damping resistors R<sub>D</sub> are used to suppress ringing of the clock signals. Values for R<sub>D</sub> should be varied to eliminate ringing and achieve 50% crossover between each pair of shift register clocks.

# **Bias Supplies**

# VDD, RD and OG

VDD and VRD are supplied directly from the 15 V input power supply and OG is supplied by a voltage divider. The input power should be sufficiently filtered to prevent noise from coupling into the output stage of the KLI–8013 through the VDD node. Current spikes in the VRD and VDD nodes, due to switching of the on-chip reset FET, are suppressed by the addition of a 0.1  $\mu$ F decoupling capacitor to ground at each node. The decoupling capacitors should be located as close as possible to the pins of the CCD and should have a solid connection to ground. OG is also decoupled to suppress voltage spikes the output gate of the device. The OG node draws negligible current.

# OG, VSSR, VSSG, VSSB

A forward-biased diode provides an inexpensive and reliable voltage source for all three VSS nodes. The switching action of the reset FET of the output stage can cause voltage spikes to occur on the VSS nodes. A decoupling capacitor located as close as practical to each VSS pin, and connected to a solid system ground, will minimize voltage spiking. In high dynamic range systems, crosstalk between VSS channels might present a noise problem. A separate supply for each of the three VSS nodes will minimize channel crosstalk if it proves to be a problem.

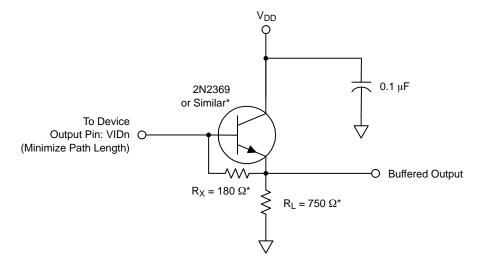

# **Output Buffers**

An emitter follower circuit buffers each output channel. The emitter follower provides a high impedance load to the on-chip source follower output stage, and provides low output impedance for driving the downstream analog signal processing circuits. A  $180-\Omega$  resistor connected between the base and emitter of the emitter follower uses the forward biased base to emitter voltage drop to provide a constant current load for the on-chip output stage.

# **DEFECT DEFINITIONS**

# **Table 6. OPERATING CONDITION SPECIFICATIONS**

(Test Conditions: T = 25°C,  $f_{CLK}$  = 1 MHz,  $t_{INT}$  = 8.054 ms)

| Field  | Defect Type      | Threshold | Units | Notes      | Number |

|--------|------------------|-----------|-------|------------|--------|

| Dark   | Bright           | 16.0      | mV    | 20, 21     | 0      |

| Bright | Bright/Dark      | 10        | %     | 20, 22     | 0      |

| Bright | Exposure Control | 4.0       | mV    | 20, 23, 24 | ≤ 32   |

20. Defective pixels will be separated by at least one non-defective pixel within and across channels.

21. Pixels whose response is greater than the average response by the specified threshold. See Figure 13 below. 22. Pixels whose response is greater or less than the average response by the specified threshold. See Figure 13 below.

23. Pixels whose response deviates from the average pixel response by the specified threshold when operating in exposure control mode. See Figure 13 below.

24. Defect coordinates are available upon request.

Figure 13. Illustration of Defect Classifications

# OPERATION

# Table 7. ABSOLUTE MAXIMUM RATINGS

| Description             | Symbol                | Minimum | Maximum | Unit | Notes  |

|-------------------------|-----------------------|---------|---------|------|--------|

| Gate Pin Voltage        | V <sub>GATE</sub>     | -0.5    | 16      | V    | 25, 26 |

| Pin-to-Pin Voltage      | V <sub>PIN-PIN</sub>  | -       | 16      | V    | 25, 27 |

| Diode Pin Voltage       | V <sub>DIODE</sub>    | -0.5    | 16      | V    | 25, 28 |

| Output Bias Current     | I <sub>DD</sub>       | -       | -10     | mA   | 29     |

| Output Load Capacitance | C <sub>VID,LOAD</sub> | _       | 15      | pF   |        |

| CCD Clocking Frequency  | f <sub>C</sub>        | _       | 20      | MHz  | 30     |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

25. Referenced to substrate voltage.

26. Includes pins:  $\phi$ 1n (n = A or B),  $\phi$ 2n (n = A or B), TG1, TG2,  $\phi$ R, OG, IG, and LOGn (n = R, G, B).

27. Voltage difference (either polarity) between any two pins.

28. Includes pins: VIDn, VSSn, RD, VDD, LS and ID (n = R, G, B).

29. Care must be taken not to short output pins to ground during operation as this may cause permanent damage to the output structures.

30. Charge transfer efficiency will degrade at frequencies higher than the maximum clocking frequency. VIDn load resistor values may need to be decreased as well.

31. Noise performance will degrade with increasing temperatures.

32. Long-term storage at the maximum temperature will accelerate color filter degradation.

33. Exceeding the upper limit on output load capacitance will greatly reduce the output frequency response. Thus, direct probing of the output pins with conventional oscilloscope probes is not recommended.

34. The absolute maximum ratings for the entire table indicate the limits of this device beyond which damage may occur. The Operating ratings indicate the conditions where the design should operate the device. Operating at or near these ratings do not guarantee specific performance limits. Guaranteed specifications and test conditions are contained in the Imaging Performance section.

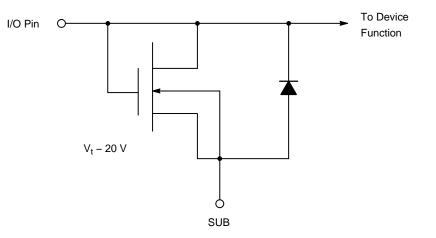

Device Input ESD Protection Circuit (Schematic)

**CAUTION:** To allow for maximum performance, this device was designed with limited input protection; thus, it is sensitive to electrostatic induced damage. These devices should be installed in accordance with strict ESD handling procedures!

# Figure 14. ESD Protection Circuit

# **DC Bias Operating Conditions**

# Table 8. DC BIAS OPERATING CONDITIONS

| Description                     | Symbol           | Minimum | Nominal          | Maximum | Units | Notes |

|---------------------------------|------------------|---------|------------------|---------|-------|-------|

| Substrate                       | V <sub>SUB</sub> | -       | 0                | -       | V     |       |

| Output Buffer Return            | V <sub>VSS</sub> | 0.5     | 0.65             | 0.75    | V     |       |

| Reset Drain Bias (Normal Mode)  | V <sub>RD</sub>  | 10.5    | 11.0             | 11.5    | V     |       |

| Reset Drain Bias (High DR Mode) | V <sub>RD</sub>  | 14.5    | V <sub>VDD</sub> | 15.5    | V     |       |

| Output Buffer Supply            | V <sub>VDD</sub> | 14.5    | 15.0             | 15.5    | V     |       |

| Output Bias Current/Channel     | I <sub>IDD</sub> | -8      | -4               | -2      | mA    | 35    |

| Output Gate Bias                | V <sub>OG</sub>  | 0.5     | 0.65             | 0.75    | V     |       |

| Light Shield/Drain Bias         | V <sub>LS</sub>  | 12.0    | 15.0             | 15.5    | V     |       |

| Test Pin – Input Gate           | V <sub>IG</sub>  | -       | 0                | -       | V     |       |

| Test Pin – Input Diode          | V <sub>ID</sub>  | 12.0    | 15.0             | 15.5    | V     |       |

35. A current sink must be supplied for each output. Load capacitance should be minimized so as not to limit bandwidth.  $R_X$  serves as the load bias for the on-chip amplifiers. Values of  $R_X$  and  $R_L$  should be chose to optimize performance for a given operating frequency, but  $R_X$  should not be less than 75  $\Omega$ . Figure 15 below shows one such solution.

Typical Output Bias/Buffer Circuit

Figure 15. Typical Output Bias/Buffer Circuit

# **AC Operating Conditions**

# **Table 9. AC ELECTRICAL CHARACTERISTICS – AC TIMING REQUIREMENTS**

| Description                | Symbol                     | Minimum | Nominal | Maximum | Units | Notes         |

|----------------------------|----------------------------|---------|---------|---------|-------|---------------|

| CCD Element Duration       | 1e (= 1/f <sub>CLK</sub> ) | 167     | 1,000   | -       | ns    | 1e Count      |

| H1A/B, H2A/B Rise Time     | t <sub>RISE</sub>          | 20      | 100     | -       | ns    |               |

| Line Integration Period    | 1L (= t <sub>INT</sub> )   | 1.343   | 8,054   | -       | ms    | 8,054e Counts |

| PD-CCD Transfer Period     | t <sub>PD</sub>            | 2666    | 16,000  | -       | ns    | 16e Counts    |

| Transfer Gate 1 Clear      | t <sub>TG1</sub>           | 167     | 1,000   | -       | ns    | 1e Count      |

| Transfer Gate 2 Clear      | t <sub>TG2</sub>           | 167     | 1,000   | -       | ns    | 1e Count      |

| Charge Drain Duration      | t <sub>DR</sub>            | 1,000   | -       | -       | ns    | 38            |

| Reset Pulse Duration       | t <sub>RST</sub>           | 20      | -       | -       | ns    | 36            |

| Clamp to H2 Delay          | t <sub>CD</sub>            | 6       | -       | -       | ns    | 37            |

| Sample to Reset Edge Delay | t <sub>SD</sub>            | 6       | -       | -       | ns    | 37            |

36. Minimum values given are for 6 MHz CCD operation.37. Recommended delays for Correlated Double Sampling (CDS) for output.

38. Minimum value required to ensure proper operation, allowing for on-chip propagation delay.

# Table 10. AC ELECTRICAL CHARACTERISTICS - CLOCK LEVEL CONDITIONS FOR OPERATION

| Description                          | Symbol                                | Minimum | Nominal | Maximum | Units | Notes  |

|--------------------------------------|---------------------------------------|---------|---------|---------|-------|--------|

| CCD Readout Clocks High (n = A or B) | V <sub>H1nH</sub> , V <sub>H2nH</sub> | 6.25    | 6.5     | 7.0     | V     |        |

| CCD Readout Clocks Low (n = A or B)  | V <sub>H1nL</sub> , V <sub>H2nL</sub> | -0.1    | 0.0     | 0.1     | V     | 39     |

| Transfer Clocks High (n = 1 or 2)    | V <sub>TGnH</sub>                     | 6.25    | 6.5     | 7.0     | V     |        |

| Transfer Clocks Low (n = 1 or 2)     | V <sub>TGnL</sub>                     | -0.1    | 0.0     | 0.1     | V     | 39     |

| Reset Clock High (Normal Mode)       | V <sub>¢RH</sub>                      | 6.25    | 6.5     | 7.0     | V     |        |

| Reset Clock High (High DR Mode)      | $V_{\phi RH}$                         | 11.5    | 12.0    | 12.5    | V     |        |

| Reset Clock Low                      | $V_{\phi RL}$                         | -0.1    | 0.0     | 0.1     | V     | 39     |

| Exposure Clocks High (n = R, G, B)   | V <sub>LOGnH</sub>                    | 6.25    | 6.5     | 7.0     | V     | 40     |

| Exposure Clocks Low (n = R, G, B)    | V <sub>LOGnL</sub>                    | -0.1    | 0.0     | 0.1     | V     | 39, 40 |

39. Care should be taken to insure that low rail overshoot does not exceed -0.5 VDC. Exceeding this value may result in non-photogenerated charge being injected into the video signal.

40. Connect pin to ground potential for applications where exposure control is not required.

$C_{\varphi R}$

# Table 11. CLOCK LINE CAPACITANCE

**Reset Gate Capacitance**

| Description                 | Symbol           | Minimum | Nominal | Maximum | Units | Notes |

|-----------------------------|------------------|---------|---------|---------|-------|-------|

| CHROMA                      |                  |         |         |         |       |       |

| Phase 1 Clock Capacitance   | C <sub>φ1</sub>  | -       | 4,180   | -       | pF    | 41    |

| Phase 2 Clock Capacitance   | C <sub>φ2</sub>  | -       | 2,000   | -       | pF    | 41    |

| Transfer Gate 1 Capacitance | C <sub>TG1</sub> | -       | 925     | -       | pF    |       |

| Transfer Gate 2 Capacitance | C <sub>TG2</sub> | -       | 475     | -       | pF    |       |

| Exposure Gate Capacitance   | C <sub>LOG</sub> | -       | 190     | -       | pF    |       |

41. This is the total load capacitance per CCD phase. Since the CCDs are driven from both ends of the sensor, the effective load capacitance per drive pin is approximately half the value listed.

11

pF

# TIMING

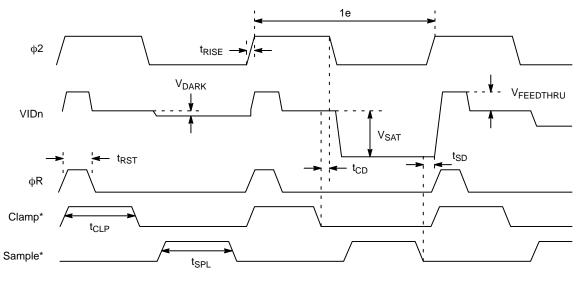

Figure 16. Line Timing

Figure 17. Photodiode-to-CCD Transfer

\* Required for Correlated Double Sampling

# Figure 18. Output Timing

# STORAGE AND HANDLING

# Table 12. STORAGE CONDITIONS

| Description           | Symbol          | Minimum | Maximum | Unit | Notes |

|-----------------------|-----------------|---------|---------|------|-------|

| Storage Temperature   | T <sub>ST</sub> | -25     | 80      | °C   | 42    |

| Operating Temperature | T <sub>OP</sub> | 0       | 70      | °C   | 43    |

42. Long-term storage toward the maximum temperature may accelerate color filter degradation.

43. Noise performance will degrade with increasing temperatures.

For information on ESD and cover glass care and cleanliness, please download the *Image Sensor Handling and Best Practices* Application Note (AN52561/D) from www.onsemi.com.

For information on soldering recommendations, please download the Soldering and Mounting Techniques Reference Manual (SOLDERRM/D) from www.onsemi.com.

For quality and reliability information, please download the *Quality & Reliability* Handbook (HBD851/D) from <u>www.onsemi.com</u>.

For information on device numbering and ordering codes, please download the *Device Nomenclature* technical note (TND310/D) from <u>www.onsemi.com</u>.

For information on Standard terms and Conditions of Sale, please download <u>Terms and Conditions</u> from <u>www.onsemi.com</u>.

# **MECHANICAL INFORMATION**

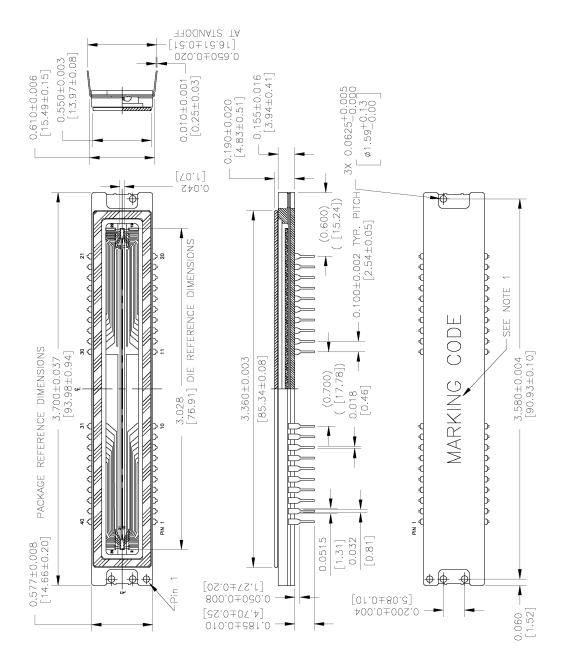

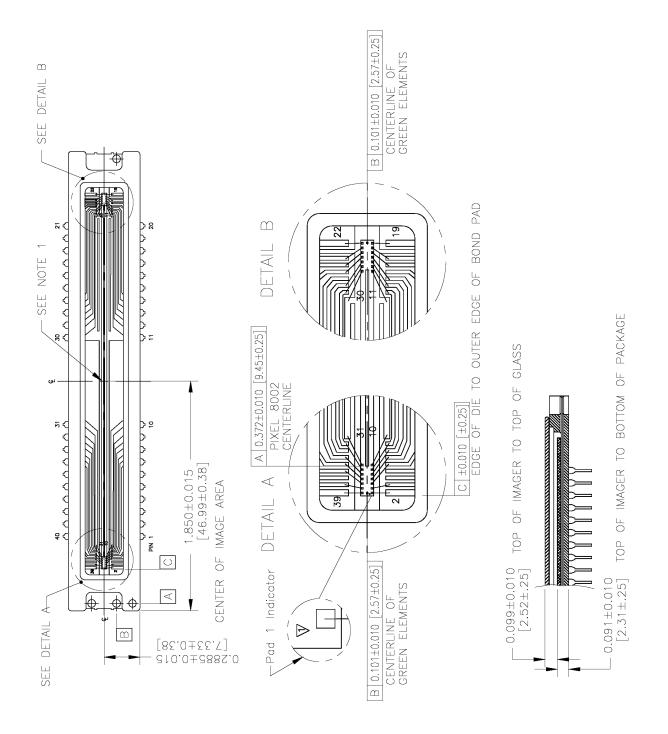

# **Completed Assembly**

Figure 19. Completed Assembly Drawing (1/2)

Figure 20. Completed Assembly Drawing (2/2)

Maximum Reflectance Allowed (Two-Sided)

### **Cover Glass**

### 2.40 2.20 2.00 1.80 1.60 Reflectance (%) 1.40 1.20 1.00 0.80 0.60 0.40 Reflectance (Two-Sided) 0.20 0.00 400 450 500 550 600 650 700 Wavelength (nm)

# Figure 21. Two-Sided Multilayer Anti-Reflective Cover Glass Specification (MAR)

ON Semiconductor and ()) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns ne rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/dt/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products for applications and applications using ON Semiconductor, "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor data sheets or use or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices or medical devices or moducts and sound to regularized application or use to fore guptications or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application. Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arisin

### PUBLICATION ORDERING INFORMATION

### LITERATURE FULFILLMENT

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5817–1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative