# Pure, Single-Stage, LLC, LED Current and System Voltage Controller

#### DESCRIPTION

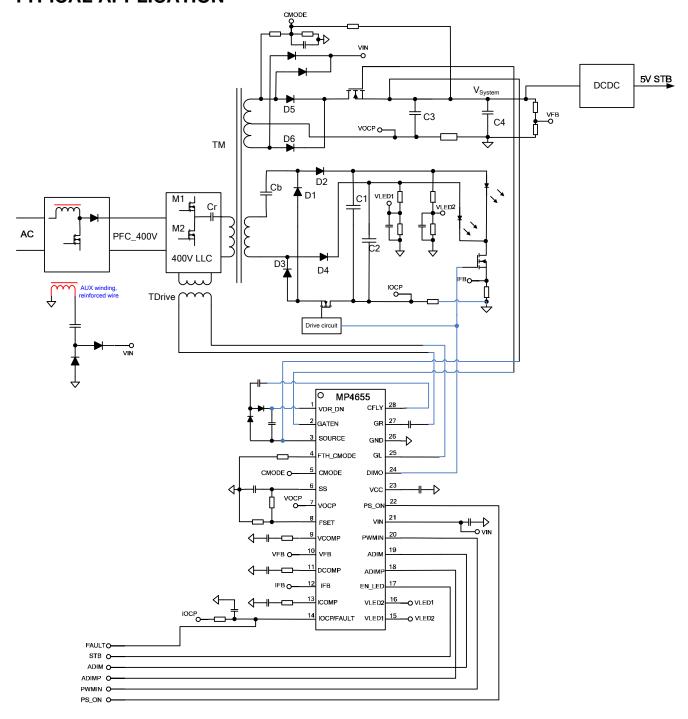

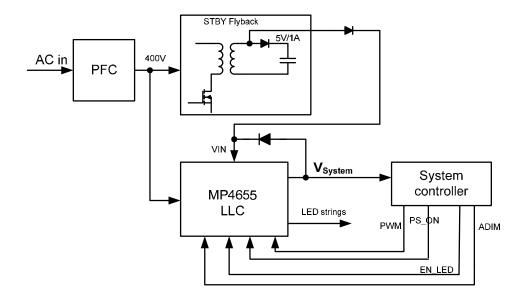

The MP4655 is a pure, single-stage, LLC, LED current and system voltage controller for LED backlighting, especially in larger TVs, and is located on the secondary side. The MP4655 uses an LLC power stage and an extra Nchannel MOSFET to regulate both the LED current and the system supply voltage. The MP4655 is powered by input supplies ranging from 9V to 35V that output two 180 degree phase shifted driving signals for the external LLC power stages. Its enhanced 12V gate driver provides sufficient driving capability and can drive the external LLC MOSFETs directly through an external gate-driving transformer. The MP4655 also provides a direct driving signal to control the extra N-channel MOSFET and regulate the system supply voltage.

The MP4655 incorporates both PWM dimming and analog dimming for the LED current. A driving signal is output to directly drive the dimming MOSFET, which helps achieve fast and high-contrast ratio PWM dimming. The analog dimming can be achieved through a DC signal on ADIM or a pulse signal on ADIMP.

The MP4655 employs smart protection methods to protect the LED driver stage and system power stage in the event that a fault occurs, increasing system reliability.

Full protection features for the LED include open LED protection, short LED protection, over-LED current protection, feedback open loop protection, and protection for any point of the LED string shorting to ground.

Full protection features for the system supply voltage stage include over-voltage protection (OVP), over-current protection (OCP), and feedback open-loop protection. The MP4655 uses an extra individual capacitive mode protection to protect the LLC power stage in any condition system in the event it enters capacitive mode. The MP4655 also employs thermal shutdown and is available in a SOIC-28 package.

#### **FEATURES**

- Pure, 1-Stage LLC for LED Current and System Supply Voltage Regulation

- CC/CV Frequency Control Loop and Duty Cycle Control Loop

- Audible Noise Elimination

- 9V to 35V Input Voltage Range

- Deep and Fast PWM Dimming

- Analog Dimming with DC or Pulse Input Signal

- Input Under-Voltage Lockout (UVLO)

- System Supply Over-Voltage Protection (OVP)

- System Supply Short Protection

- LED Open, LED Short Protection

- LED String Short to GND Protection

- Open Feedback Loop Protection for System Bus Voltage and LED Driver

- Capacitive Mode Protection for LLC

- Soft Switching for the Extra N-Channel MOSFET

- Fault Indicator

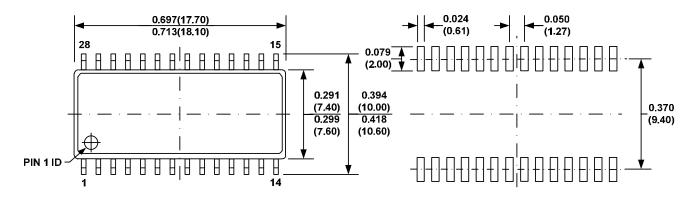

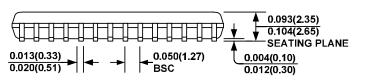

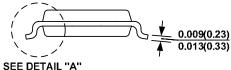

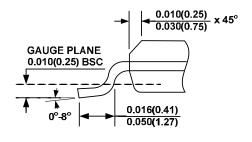

- Available in a SOIC-28 Package

#### **APPLICATIONS**

- LCD TVs and Monitors

- Desktop LCD Flat Panel Displays

- Flat Panel Video Displays

- Street Lighting

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

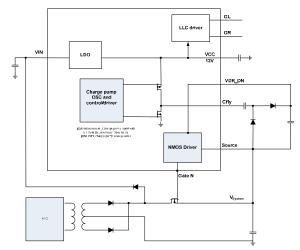

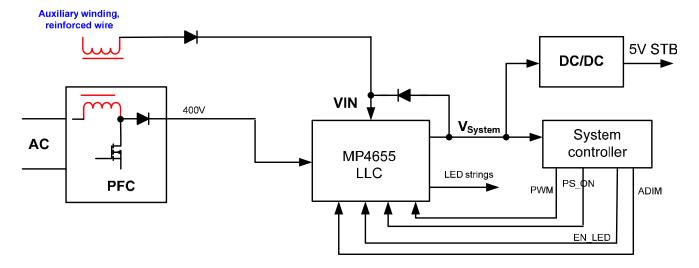

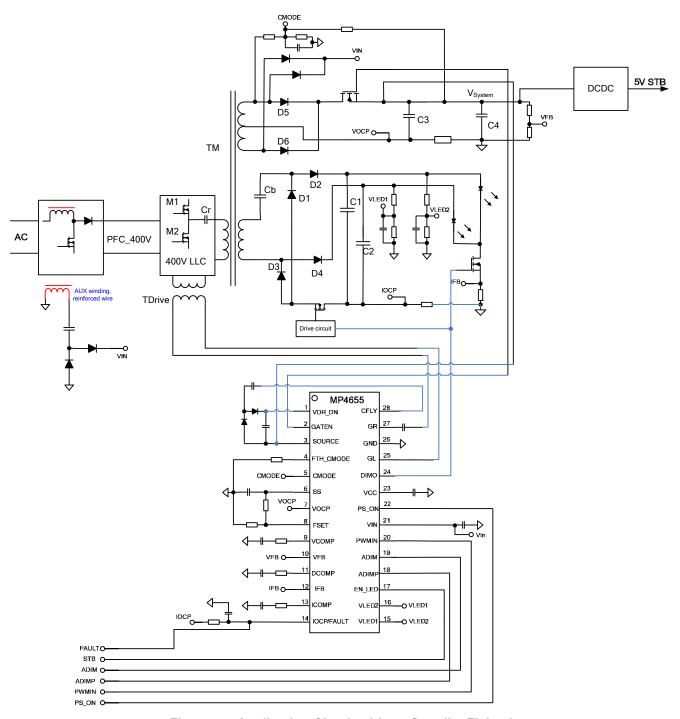

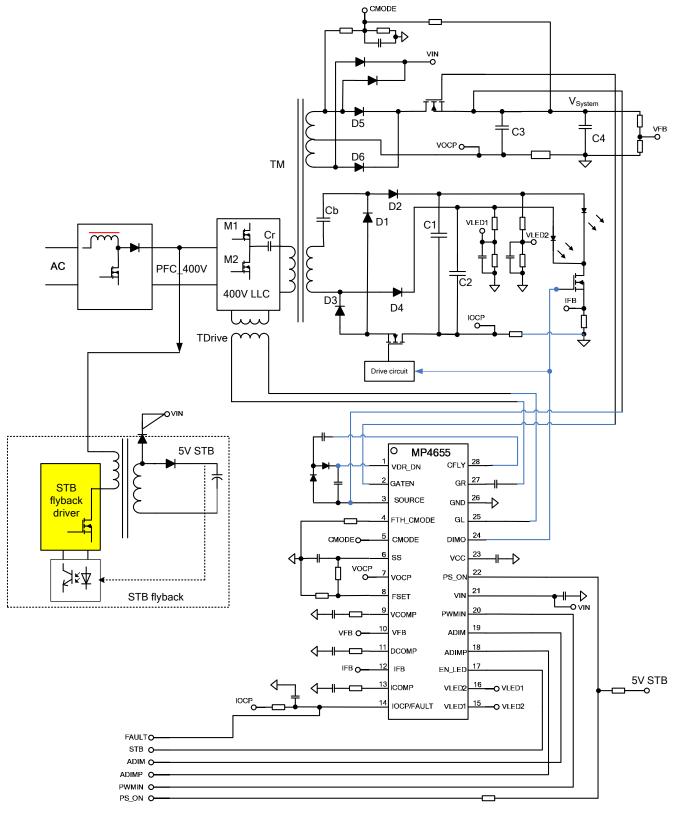

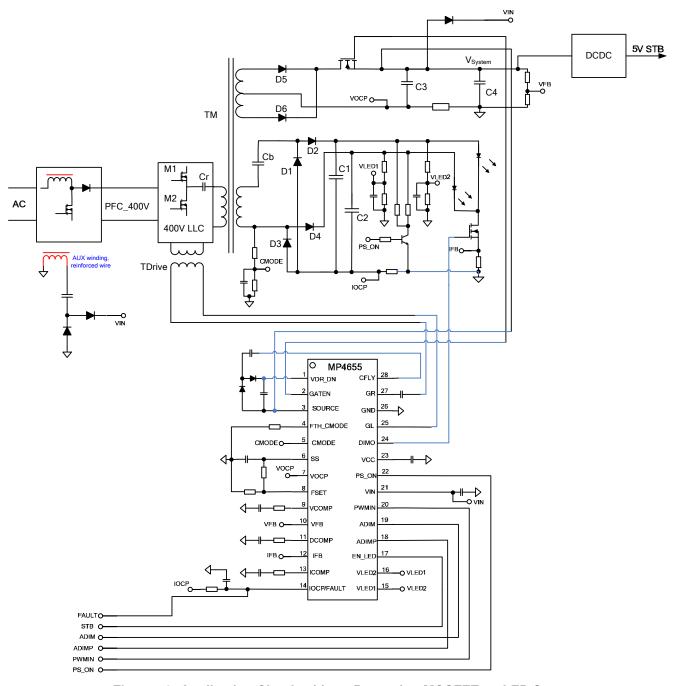

#### TYPICAL APPLICATION

#### **ORDERING INFORMATION**

| Part Number* | Package | Top Marking |

|--------------|---------|-------------|

| MP4655GY     | SOIC-28 | See Below   |

\*For Tape & Reel, add suffix –Z (eg. MP4655GY–Z)

#### **TOP MARKING**

M<u>PSYYWW</u> MP4655 LLLLLLLL

MPS: MPS prefix YY: Year code WW: Week code

MP4655: Product code of MP4655GY

LLLLLLL: Lot number

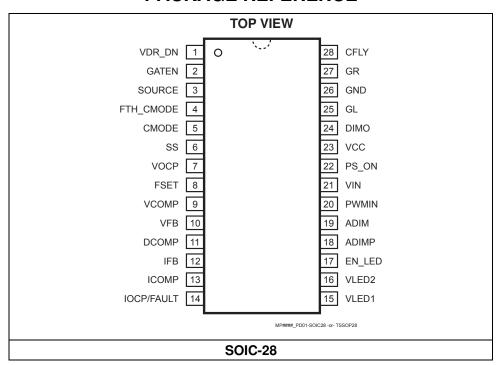

#### **PACKAGE REFERENCE**

| <b>ABSOLUTE MAXIN</b>             | MUM RATINGS (1)                               |

|-----------------------------------|-----------------------------------------------|

| VIN, PS_ON, PWMIN                 |                                               |

| GL, GR, VCC, DIMO, CF             | LY0.3V to 18V                                 |

| SOURCE                            | 0.3V to 30V                                   |

| VDR_DN, GATEN                     | 0.3V to 48V                                   |

| VDR_DN - SOURCE, GA               | TEN - SOURCE                                  |

|                                   | 0.3V to 18V                                   |

| IOCP/FAULT, VOCP, CM              | 10DE6.5V to 6V                                |

| Other pins                        | 0.3V to 6.5V                                  |

| Junction temperature              | 150°C                                         |

| Continuous power dissipa          | ation (T <sub>A</sub> = +25°C) <sup>(2)</sup> |

| SOIC-28                           | 2.1W                                          |

| Storage temperature               | 65°C to +150°C                                |

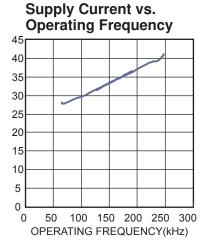

| Operating frequency               | 400kHz                                        |

| Recommended Opera                 | ting Conditions <sup>(3)</sup>                |

| Supply voltage (V <sub>IN</sub> ) | 0.3V to 35V                                   |

| Operating frequency               | 20kHz to 350kHz                               |

| Operating junction temp.          |                                               |

| Thermal Resistance (4) | $oldsymbol{	heta}_{JA}$ | $oldsymbol{	heta}_{JC}$ |      |

|------------------------|-------------------------|-------------------------|------|

| SOIC-28                | 60                      | 30                      | °C/W |

#### NOTES:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by PD (MAX) = (TJ  $(MAX)-T_A)/\theta_{JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) The device is not guaranteed to function outside of its operating conditions.

- Measured on JESD51-7, 4-layer PCB.

### **ELECTRICAL CHARACTERISTICS**

| Parameter                                                  | Symbol                      | Condition                                          | Min  | Тур              | Max  | Units |

|------------------------------------------------------------|-----------------------------|----------------------------------------------------|------|------------------|------|-------|

| VIN Supply                                                 |                             |                                                    |      |                  |      |       |

| VIN supply range                                           |                             |                                                    | 9    |                  | 35   | V     |

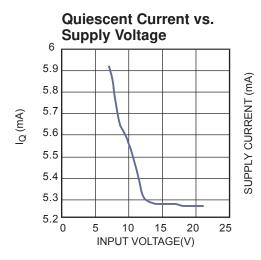

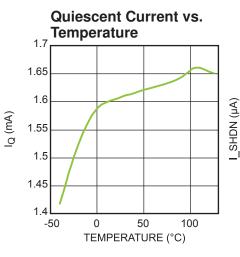

| Quiescent current                                          | lα                          | PS_ON = 5V,<br>no gate driver                      |      | 1.6              | 1.9  | mA    |

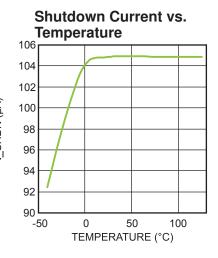

| Shutdown current                                           | I <sub>shutdown</sub>       | PS_ON = 1.5V                                       |      | 106              | 120  | μA    |

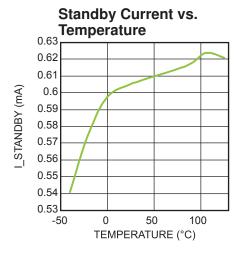

| Standby current                                            | I <sub>STB</sub>            | PS_ON = 0V                                         |      | 0.6              | 0.8  | mA    |

| Gate Driver GL, GR (LLC Powe                               | r Stage)                    |                                                    |      |                  |      |       |

| Gate pull-down resistance                                  | $R_{GD}$                    | I <sub>gate</sub> = 20mA                           |      | 2                |      | Ω     |

| Gate pull-up resistance                                    | $R_{GU}$                    | I <sub>gate</sub> = 20mA                           |      | 8                |      | Ω     |

| Output source current                                      | I <sub>SOURCE</sub>         | With 1nF load                                      |      | 0.5 (5)          |      | Α     |

| Output sink current                                        | I <sub>SINK</sub>           | With 1nF load                                      |      | 1 <sup>(5)</sup> |      | Α     |

| Dead time                                                  | t <sub>dead</sub>           |                                                    | 400  | 600              | 800  | ns    |

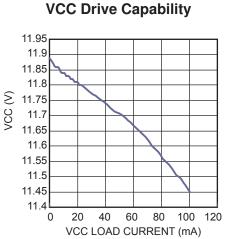

| Gate Driver Supply Voltage (VC                             | CC)                         |                                                    | -    |                  |      |       |

|                                                            |                             | I <sub>VCC</sub> = 0mA                             | 11.5 | 12.5             | 13.5 | V     |

| Voltage                                                    | $V_{VCC}$                   | I <sub>VCC</sub> = 30mA                            | 11.3 | 12.3             | 13.3 | V     |

|                                                            |                             | I <sub>VCC</sub> = 50mA                            | 11.2 | 12.2             | 13.2 | V     |

| Voltage dropout                                            |                             | I <sub>VCC</sub> = 50mA, VIN = 10V                 |      | 0.53             |      | V     |

| VCC UVLO threshold                                         | V <sub>TH_UVLO_VCC</sub>    | VCC rising                                         | 7.2  | 7.74             | 8.2  | V     |

| VCC UVLO hysteresis                                        | V <sub>TH_VCC_HYST</sub>    |                                                    | 1.8  | 2.05             | 2.3  | V     |

| Gate Driver (GATEN, for Extra                              |                             | vstem)                                             | -    |                  |      |       |

| GATEN pull-down resistance                                 | $R_{GD}$                    | I <sub>gate</sub> = 20mA                           |      | 2.5              |      | Ω     |

| GATEN pull-up resistance                                   | $R_{GU}$                    | I <sub>gate</sub> = 20mA                           |      | 9                |      | Ω     |

| Output source current                                      | I <sub>SOURCE_GATEN</sub>   | With 1nF load                                      |      | 0.5 (5)          |      | Α     |

| Output sink current                                        | I <sub>SINK_GATEN</sub>     | With 1nF load                                      |      | 1 <sup>(5)</sup> |      | Α     |

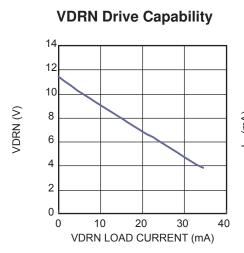

| GATEN Supply Voltage (VDR_I                                | ON)                         |                                                    |      |                  |      |       |

| Charge pump pull-up resistor                               |                             |                                                    |      | 13               |      | Ω     |

| Charge pump pull-down resistor                             |                             |                                                    |      | 4                |      | Ω     |

| Charge pump frequency                                      | f <sub>chargepump</sub>     |                                                    |      | 455              |      | kHz   |

| VDR_DN upper threshold to stop charge pump in standby mode | $V_{th\_upper\_STB}$        | Detection circuit, very small leakage              |      | VCC -<br>2.5     |      | V     |

| VDR_DN valley threshold to recover charge pump in          | $V_{	ext{th\_valley\_STB}}$ | VCC - 5.5 > 5V                                     |      | VCC -<br>5.5     |      | V     |

| standby mode                                               |                             | VCC - 5.5 < 5V                                     |      | 5                |      |       |

| Leakage current from SOURCE                                | I <sub>lkg_SOURCE</sub>     | V <sub>SOURCE</sub> = 24V,<br>charge pump disabled |      |                  | 0.2  | μΑ    |

| Parameter                                   | Symbol                     | Condition                                                              | Min  | Тур  | Max  | Units |

|---------------------------------------------|----------------------------|------------------------------------------------------------------------|------|------|------|-------|

| Analog Dimming                              |                            |                                                                        |      |      |      |       |

| Analog dimming full scale                   | $V_{ADMAX}$                | VIFB = 200mV                                                           | 2.32 | 2.39 | 2.46 | V     |

| Dimming linearity                           | VIFB_ADIM                  | VIFB_ADIM VADIM = 1.2V                                                 |      | 100  |      | mV    |

| Dimming linearity                           | VIFB_ADIM                  | VADIM = 0.8V                                                           |      | 66.8 |      | mV    |

| Dimming linearity                           | VIFB_ADIM                  | VADIM = 0.3V                                                           |      | 25   |      | mV    |

| Dimming linearity                           | VIFB_ADIM                  | VADIM = 0.1V                                                           |      | 8.5  |      | mV    |

| ADIMP logic high                            | VADIM_PHI                  |                                                                        | 1.8  |      | 3.5  | V     |

| ADIMP logic low                             | VADIM_PLO                  |                                                                        |      |      | 0.9  | V     |

| ADIMP pull-up resistor                      | RADIM_P_UP                 |                                                                        |      | 1.5  |      | МΩ    |

| ADIMP disable threshold                     |                            |                                                                        | 4.7  |      |      | V     |

| PWM Dimming                                 |                            |                                                                        |      |      |      |       |

| PWM logic high threshold                    | $V_{TH-PWM}$               | PWM dimming                                                            | 1.4  | 17   | 2    | V     |

| PWM logic input hysteresis                  | V <sub>TH-PWM-Hyst</sub>   | PWM dimming                                                            |      | 0.6  |      | V     |

| Operating Frequency                         | -                          |                                                                        |      |      |      |       |

| Minimum frequency set voltage               | $V_{FSET}$                 | IFB = 0.1V, PWMIN = high                                               | 1.65 | 1.73 | 1.83 | V     |

| Minimum operating frequency                 | F <sub>min_op</sub>        | $R_{FSET} = R_{SS\_FSET} = 300k\Omega$ , IFB = 0.1V, PWMIN = high      |      | 42.5 |      | kHz   |

| Maximum operating frequency                 | F <sub>max_op</sub>        | $R_{FSET} = R_{SS\_FSET} = 300k\Omega$ , IFB = 0.21V, PWMIN = high     |      | 130  |      | kHz   |

| Output PWM Dimming Signal                   | for LED (DIMO)             |                                                                        |      |      |      |       |

| Logic high voltage                          | $V_{\text{H-DIMO}}$        | Normal operation                                                       |      | 12.5 |      | V     |

| Logic low voltage                           | $V_{\text{L-DIMO}}$        | At fault condition, or PWMIN is low                                    |      |      | 0.1  | V     |

| DIMO up-side resistance                     |                            | 20mA drive source current for design                                   |      | 62   |      | Ω     |

| DIMO low-side resistance                    |                            | 100mA drive sink current for design                                    |      | 7    |      | Ω     |

| LED Stage Enable (EN_LED)                   |                            |                                                                        |      |      |      |       |

| EN_LED logic high threshold                 | $V_{\text{TH-EN\_LED}}$    | EN_LED rising                                                          | 1.4  | 1.7  | 2    | V     |

| EN_LED logic input hysteresis               | V <sub>TH-ENLED-Hyst</sub> |                                                                        |      | 0.6  |      | V     |

| IC Enable Signal (PS_ON)                    | ,                          | -                                                                      |      | -    |      |       |

| Threshold for IC standby                    | $V_{th\_PS\_ON\_STB}$      | Rising edge                                                            | 0.7  | 8.0  | 0.9  | V     |

| Duration time to shut down IC               |                            | V <sub>th_PS_ON_STB</sub> < V <sub>PS_ON</sub> < V <sub>th_PS_ON</sub> |      | 1    |      | ms    |

| Threshold to turn on IC to operate normally | $V_{th\_PS\_ON}$           | _ := :                                                                 | 1.9  | 2    | 2.1  | ٧     |

| Parameter                                       | Symbol                    | Condition                        | Min   | Тур   | Max  | Units                    |

|-------------------------------------------------|---------------------------|----------------------------------|-------|-------|------|--------------------------|

| Capacitive Mode Detection (CM                   | MODE)                     |                                  | •     | •     |      | •                        |

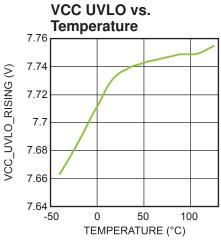

| CMODE detection high threshold                  | V <sub>th_Cmode_H</sub>   | At GL falling edge               |       | 0.97  |      | V <sub>REF_VFB</sub>     |

| CMODE detection low threshold                   | V <sub>th_Cmode_L</sub>   | At GR falling edge               |       | 0.03  |      | V <sub>REF_VFB</sub>     |

| FTH_CMODE voltage                               | $V_{Fth\_Cmode}$          |                                  | 1.15  | 1.2   | 1.25 | V                        |

| CMODE threshold frequency                       | $F_{th\_cmode}$           | 150kΩ on FTH_CMODE               |       | 91    |      | kHz                      |

| Soft Start (SS)                                 |                           |                                  |       |       |      |                          |

| Soft-start final voltage                        | V <sub>SS</sub>           | Normal operation after start-up  | 2.34  | 2.405 | 2.47 |                          |

| Soft-start current                              | I <sub>SS</sub>           | V <sub>SS</sub> = 1V             |       | 13    |      | μA                       |

| Discharge current when capacitive mode detected | I <sub>SS_Discharge</sub> | V <sub>SS</sub> = 2V             |       | 3     |      | I <sub>SS</sub>          |

| Pull low resistor at latch-up                   |                           |                                  |       | 120   |      | Ω                        |

| LED Current Feedback (IFB)                      |                           |                                  |       |       |      |                          |

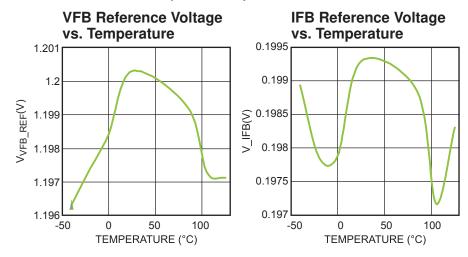

| Magnitude                                       | V <sub>IFB</sub>          |                                  | 0.188 | 0.199 | 0.21 | V                        |

| LED short threshold for immediate action        | $V_{IFBS}$                |                                  | 490   | 555   | 610  | mV                       |

| LED short detection delay time                  | $T_{blankTdelay}$         |                                  |       | 6     |      | us                       |

| LED short threshold for slow action             | V <sub>IFBSC</sub>        |                                  | 370   | 415   | 460  | mV                       |

| Delay time for slow action                      | T <sub>delay_IFB</sub>    | 400mV < V <sub>IFB</sub> < 600mV | 250   | 340   | 450  | μs                       |

| Threshold for short protection                  |                           | ICOMP saturated                  |       | 50%   |      | V <sub>IFB_REF</sub> (6) |

| Duration for short protection                   |                           |                                  |       | 1024  |      | cycle                    |

| Internal Current Loop Compen                    | sation Transco            | nductance Op-Amp (ICOMF          | P)    |       |      |                          |

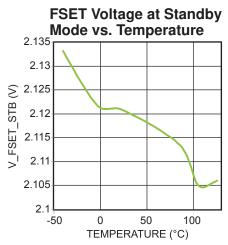

| Transconductance                                | Gm_I                      |                                  |       | 840   |      | μA/V                     |

| Saturated output current                        | I <sub>sat_I</sub>        |                                  | 30    | 50    | 70   | μA                       |

| Low-level clamp voltage                         | VICOMP_L                  | Normal operation                 | 0.97  | 1.02  | 1.07 | V                        |

| High-level clamp votlage                        | VICOMP_H                  | Normal operation                 | 2.2   | 2.28  | 2.36 | V                        |

| Output for System Voltage Fee                   | dback (VFB)               |                                  |       |       | •    |                          |

| Reference voltage                               | $V_{REF\_VFB}$            |                                  | 1.17  | 1.2   | 1.23 | V                        |

| Leakage current                                 | I <sub>lkg_VFB</sub>      | Normal operation                 |       | 0.33  |      | μA                       |

| Internal Voltage Loop Compen                    | sation Transco            | nductance Op-Amp (VCOM           | P)    |       |      |                          |

| Low-level clamp voltage                         | $V_{VCOMP\_L}$            | Normal operation                 | 0.97  | 1.02  | 1.07 | V                        |

| High-level clamp votlage                        | $V_{VCOMP\_H}$            | Normal operation                 | 2.2   | 2.28  | 2.36 | V                        |

| Transconductance                                | Gm_V                      |                                  |       | 150   |      | μA/V                     |

| Saturated output current                        | I <sub>sat_V</sub>        |                                  | 30    | 50    | 70   | μA                       |

| Parameter                                                                                   | Symbol                          | Condition                                    | Min     | Тур     | Max  | Units                               |  |  |

|---------------------------------------------------------------------------------------------|---------------------------------|----------------------------------------------|---------|---------|------|-------------------------------------|--|--|

| Internal Voltage Loop Compensation Transconductance Op-Amp for Extra MOSFET Control (DCOMP) |                                 |                                              |         |         |      |                                     |  |  |

| Low-level clamp voltage                                                                     | $V_{DCOMP_L}$                   | Normal operation,<br>VOCP = 0V               |         | 0.41    |      | V                                   |  |  |

| High-level clamp votlage                                                                    | V <sub>DCOMP_H</sub>            | Normal operation,<br>VOCP = 0V               |         | 2.1     |      | V                                   |  |  |

| Transconductance                                                                            | $G_{m\_DCOMP}$                  |                                              |         | 150     |      | μA/V                                |  |  |

| Saturated output current                                                                    | I <sub>sat_DCOMP</sub>          |                                              | 30      | 50      | 70   | μA                                  |  |  |

| <b>Bus Voltage Stage Current Det</b>                                                        | ection (VOCP)                   |                                              |         |         |      |                                     |  |  |

| VOCP detection threshold                                                                    | $V_{TH\_VOCP}$                  |                                              | -230    | -203    | -176 | mV                                  |  |  |

| VOCP delay time                                                                             | $T_{D_{VOCP}}$                  | OCP < -200mV                                 |         | 7       |      | μs                                  |  |  |

| Over LED Voltage Protection (                                                               | VLED1, VLED2)                   |                                              |         |         |      |                                     |  |  |

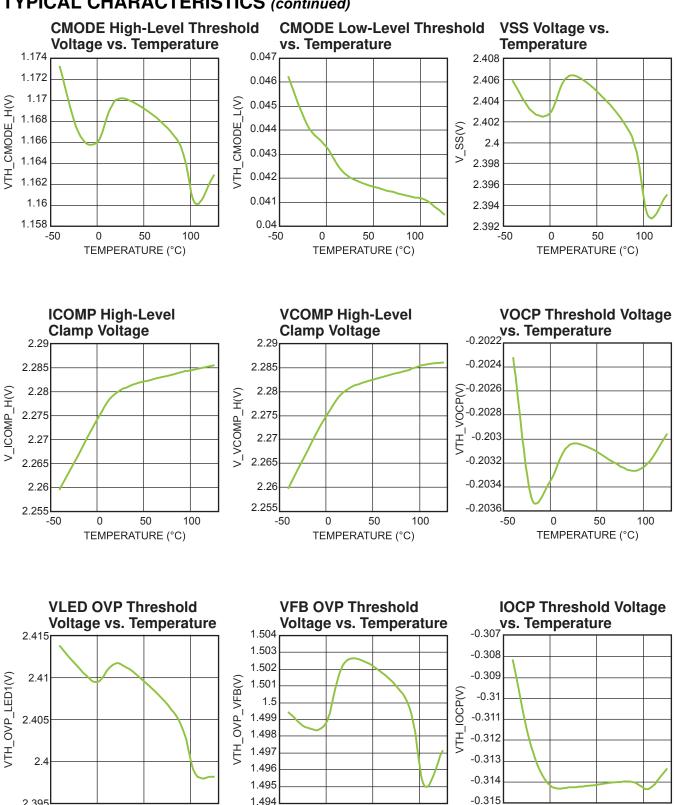

| Over LED voltage protection threshold                                                       | $V_{TH\_OVP\_LED}$              |                                              | 2.33    | 2.41    | 2.49 | V                                   |  |  |

| Over LED voltage delay time                                                                 | T <sub>delay_VLED</sub>         |                                              |         | 8       |      | μs                                  |  |  |

| Gain of differential voltage protection                                                     |                                 |                                              | 14      | 16.     | 18   |                                     |  |  |

| Internal resistance                                                                         | $R_{VLED}$                      |                                              | 16      | 20      | 24   | kΩ                                  |  |  |

| Over LED voltage to latch up LLC                                                            | V <sub>TH_OVP_LED_latch</sub>   |                                              | 2.85    | 3       | 3.15 | V                                   |  |  |

| Duration time to latch up                                                                   |                                 |                                              |         | 7.6     |      | μs                                  |  |  |

| Burst Mode (Pulse Skipping) T                                                               | hreshold at Nor                 | mal Operation (VCOMP, IC                     | OMP, VE | B, IFB) | •    |                                     |  |  |

| VCOMP threshold for burst mode                                                              | V <sub>TH_burst_VCOMP</sub>     | PS_ON = H,<br>VFB > 1.05V <sub>REF_VFB</sub> | 1.05    | 1.1     | 1.15 | V                                   |  |  |

| VCOMP hysteresis for burst mode                                                             |                                 | PS_ON = H                                    | 80      | 100     | 120  | mV                                  |  |  |

| VFB threshold for burst mode                                                                | $V_{TH\_burst\_VFB}$            | PS_ON = H                                    |         | 1.05    |      | $V_{REF\_VFB}$                      |  |  |

| VFB reset threshold for burst mode                                                          | V <sub>TH_reset_burst_VFB</sub> | PS_ON = H                                    |         | 0.95    |      | $V_{REF\_VFB}$                      |  |  |

| ICOMP threshold for burst mode                                                              | V <sub>TH_burst_ICOMP</sub>     | $PS\_ON = H,$ $V_{IFB} > 1.08V_{IFB\_REF}$   | 1.05    | 1.12    | 1.18 | V                                   |  |  |

| ICOMP hysteresis for burst mode                                                             |                                 |                                              |         | 100     |      | mV                                  |  |  |

| IFB threshold for burst mode                                                                | V <sub>TH_burst_IFB</sub>       | PS_ON = H                                    |         | 1.08    |      | V <sub>IFB_REF</sub> <sup>(6)</sup> |  |  |

| IFB reset threshold for burst mode                                                          | V <sub>TH_reset_burst_IFB</sub> | PS_ON = H                                    |         | 0.92    |      | V <sub>IFB_REF</sub> <sup>(6)</sup> |  |  |

| Parameter                                                          | Symbol                   | Condition                                               | Min  | Тур  | Max  | Units                |  |  |

|--------------------------------------------------------------------|--------------------------|---------------------------------------------------------|------|------|------|----------------------|--|--|

| Burst Mode (Pulse Skipping) Threshold in Standby Mode (VCOMP, VFB) |                          |                                                         |      |      |      |                      |  |  |

| VFB threshold to stop gate driver                                  |                          |                                                         |      | 1.05 |      | $V_{REF\_VFB}$       |  |  |

| VFB threshold to recover gate driver                               |                          |                                                         |      | 0.95 |      | V <sub>REF_VFB</sub> |  |  |

| FSET voltage at standby mode                                       | VFSET_STB                | PS_ON < 0.7V,<br>VFB = 0.8 * VREF_VFB                   |      | 2.1  |      | V                    |  |  |

| VSS low clamp value                                                |                          |                                                         |      | 0.91 |      | V                    |  |  |

| VSS soft-on recovery current                                       |                          |                                                         |      | 100  |      | μΑ                   |  |  |

| VSS soft-off recovery current                                      |                          |                                                         |      | 100  |      | μΑ                   |  |  |

| System Voltage Protection (VF                                      | В)                       |                                                         |      |      |      |                      |  |  |

| Overbus voltage protection threshold                               | $V_{TH\_OVP\_VFB}$       |                                                         |      | 1.25 |      | V <sub>REF_VFB</sub> |  |  |

| Delay time                                                         |                          | VFB > 1.5V                                              |      | 7    |      | μs                   |  |  |

| VFB open protection threshold                                      | V <sub>TH_Open_VFB</sub> |                                                         |      | 50%  |      | $V_{REF\_VFB}$       |  |  |

| Duration time for VFB open protection                              |                          | VCOMP saturated at PWM off or DCOMP saturated at PWM ON |      | 512  |      | cycles               |  |  |

| <b>LED Stage Over-Current Detec</b>                                | tion (IOCP/FAU           | LT)                                                     |      |      | •    |                      |  |  |

| IOCP threshold                                                     | V <sub>TH_IOCP</sub>     |                                                         | -360 | -320 | -280 | mV                   |  |  |

| IOCP detection delay time                                          | T <sub>D_IOCP</sub>      | IOCP < -310mV                                           |      | 7    |      | μs                   |  |  |

| IOCP duration time to latch up LLC                                 |                          | LED driver stage protection triggered and IOCP < -300mV |      | 270  |      | μs                   |  |  |

| Amplitude of output fault signal                                   | $V_{Fault}$              | Pin floated, fault condition I <sub>SOURCE</sub> = 10mA | 3.2  | 3.4  | 3.6  | V                    |  |  |

| Pull-up resistance at fault condition                              |                          |                                                         |      |      | 0.3  | kΩ                   |  |  |

| Source current of ICOP at normal operation                         |                          |                                                         |      | 5    |      | μΑ                   |  |  |

<sup>5)</sup> The parameters are tested on the bench with several parts.

<sup>6)</sup> VIFB\_REF is the reference voltage for IFB. Its value changes according to the ADIM signal.

#### TYPICAL CHARACTERISTICS

100

2.395

50

TEMPERATURE (°C)

0

0

50

TEMPERATURE (°C)

-50

0

50

TEMPERATURE (°C)

-50

#### TYPICAL PERFORMANCE CHARACTERISTICS

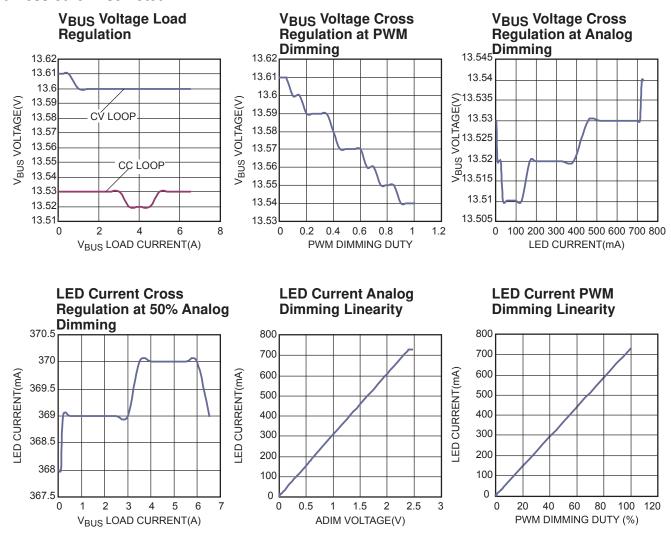

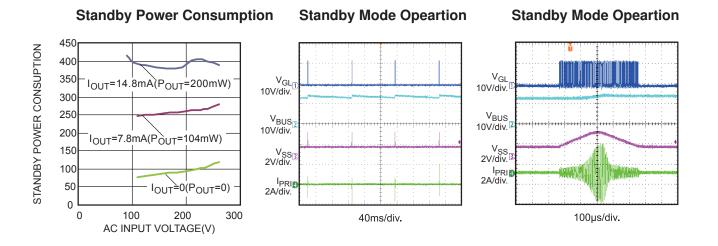

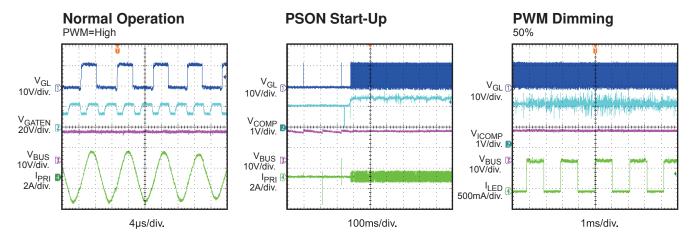

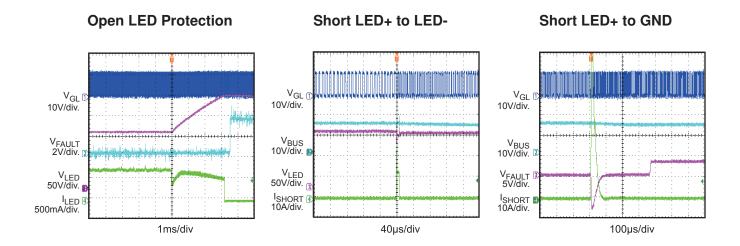

Performance waveforms are tested on the evaluation board of the Design Example section.  $400V_{bus}$  = 390V,  $V_{LED}$  = 130V, ILED = 375mA\*2 strings, System output = 13.5V/6.5A,  $T_A$  = 25°C, unless otherwise noted.

### TYPICAL PERFORMANCE CHARACTERISTICS (continued)

Performance waveforms are tested on the evaluation board of the Design Example section.  $400V_{bus}$  = 390V,  $V_{LED}$  = 130V, ILED = 375mA\*2 strings, System output = 13.5V/6.5A,  $T_A$  = 25°C, unless otherwise noted.

### **PIN FUNCTIONS**

| Pin# | Name      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | VDR_DN    | <b>Drive voltage for the extra MOSFET.</b> VDR_DN is formed by the charge pump and is referred to SOURCE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2    | GATEN     | Gate of the extra N-channel MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3    | SOURCE    | Source of the extra N-channel MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4    | FTH_CMODE | FTH_CMODE sets the threshold frequency to shut down the LLC when capacitive mode is detected. Its typical voltage is 1.2V. The sourcing current through FTH_CMODE determines the threshold frequency. When capacitive mode is detected, the IC discharges SS and increases the operating frequency. If the operating frequency is higher than this threshold frequency when capacitive mode is detected, the IC latches up LLC and the IOCP/FAULT signal output is high.                                                                                                                                                                                                                                                                                                       |

| 5    | CMODE     | <b>Detection of capacitive mode.</b> The secondary side winding voltage is fed back on CMODE for capacitive mode detection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6    | SS        | <b>Soft start.</b> SS functions as a soft start and also sets the operating frequency together with FSET. Connect a capacitor from SS to GND to set the soft-start time. An internal $10\mu A$ sourcing current charges this capacitor to 2.4V at soft start. Connect a resistor between SS and FSET to set the operating frequency together with the resistor from FSET to GND.                                                                                                                                                                                                                                                                                                                                                                                               |

| 7    | VOCP      | Over-current protection of the system bus voltage stage. VOCP senses the secondary current of the system bus voltage stage. When VOCP is lower than -203mV, the IC triggers a bus stage protection. VOCP is also used for the inner current control loop for the bus voltage compensation to control the extra MOSFET duty cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8    | FSET      | <b>Frequency set.</b> Connect a resistor from FSET to GND, and another resistor between FSET and SS. The operating frequency is determined by the sourcing current through FSET. The voltage of FSET and the operating frequency are programmed by the current control loop and the voltage control loop.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

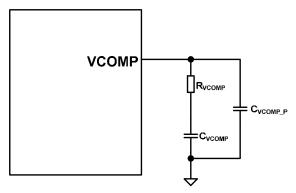

| 9    | VCOMP     | <b>Feedback compensation node of the voltage control loop.</b> Connect a compensation capacitor or an R-C network from VCOMP to GND. The VCOMP voltage is internally clamped between 1.02V and 2.28V, which limits the operating frequency range.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10   | VFB       | <b>Bus voltage feedback.</b> VFB feeds back the bus voltage for regulation. Its inner reference voltage is 1.2V. VFB is also used for over-voltage protection of the bus voltage stage. When VFB exceeds 1.5V, the over-voltage protection of the bus voltage stage is triggered. VFB also functions as the open feedback loop protection. If VFB is lower than 50% of its reference voltage and VCOMP or DCOMP is saturated for 512 cycles, the IC triggers the bus voltage stage protection.                                                                                                                                                                                                                                                                                 |

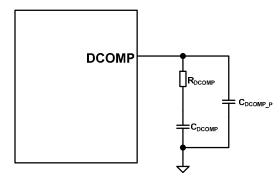

| 11   | DCOMP     | <b>Feedback compensation node of the voltage control loop</b> . DCOMP is used to program the duty cycle of the extra N-channel MOSFET. Connect a compensation capacitor or an R-C network from DCOMP to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 12   | IFB       | LED current feedback input. IFB feeds back the LED current through a sensing resistor. The internal error amplifier sinks a current from ICOMP proportional to the absolute value of the voltage at IFB. The average voltage at IFB is regulated to the reference voltage (controlled by the ADIM voltage, 199mV when ADIM is high). The voltage on IFB is also used for LED over-current detection. When the voltage on IFB rises higher than 415mV for 340µs or when the voltage rises higher than 555mV, the IC triggers the LED stage protection. IFB also functions as the LED current open feedback loop protection. If the IFB voltage is lower than 50% of its reference voltage and the ICOMP is saturated for 1024 cycles, the IC triggers the LED stage protection. |

## PIN FUNCTIONS (continued)

| Pin# | Name       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

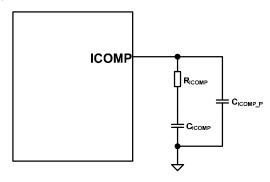

| 13   | ICOMP      | Feedback compensation node of the current control loop. Connect a compensation capacitor or an R-C network from ICOMP to GND. The ICOMP voltage is internally clamped between 1.02V and 2.28V, which limits the operating frequency range. ICOMP also functions as the short LED to GND protection. When ICOMP is saturated and the IFB voltage is lower than 50% of the reference current for 1024 cycles, IC uses it as the fault condition and triggers an LED fault protection.                                               |

| 14   | IOCP/FAULT | <b>LED stage over-current protection and fault indicator.</b> IOCP/FAULT feeds back the secondary side current of the LED driver stage. When the voltage on IOCP/FAULT is less than -320mV for 7μs, the IC disables the output of the DIMO signal. After 270μs, the IC outputs the fault indicator. If the IOCP voltage is always lower than -320mV for 270μs, the IC latches up the LLC.                                                                                                                                         |

| 15   | VLED1      | Voltage feedback of LED string 1. VLED1 and VLED2 cooperate for the protection of the LED driver stage. The maximum voltage and the voltage difference among VLED1 and VLED2 are detected and used for LED stage protection. For 1-string applications, connect VLED1 and VLED2; for two-string applications, feed back the LED strings voltages to VLED1 and VLED2; for applications with more than two strings, feed back the maximum voltage of the LED strings and the minimum voltage of the LED strings to VLED1 and VLED2. |

| 16   | VLED2      | Voltage feedback of LED string 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 17   | EN_LED     | The enable signal for the LED driver. Logic high enables the LED stage; logic low disables the LED stage.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 18   | ADIMP      | The pulse input signal for analog dimming. The duty cycle 0 to 100% of this pulse signal programs the amplitude of the LED current from 0 to 100%. Place a 100nF capacitor from ADIM to GND for this type of dimming. If this dimming is not being used, pull it high to VCC through a 100k resistor or leave it open.                                                                                                                                                                                                            |

| 19   | ADIM       | <b>Analog dimming input with DC voltage.</b> The LED current is set by $0\sim2.4V$ from 0 to 100%. ADIMP should be disabled if using this DC input analog dimming. If this dimming is not being used, pull it high to VCC through a $100k\Omega$ resistor.                                                                                                                                                                                                                                                                        |

| 20   | PWMIN      | <b>PWM dimming control input.</b> Apply a 100Hz to 2kHz PWM signal to PWMIN for PWM dimming.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 21   | VIN        | Supply input. Bypass VIN with a ceramic capacitor larger than 0.1µF.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 22   | PS_ON      | On/off signal for the system power supply. PS_ON is the enable signal for the IC. This signal determines the operation mode of the IC. If PS_ON is less than 0.8V, the IC works in standby mode. IC operates in deep burst mode, and the system bus voltage is controlled with a larger ripple voltage to decrease the power consumption. If PS_ON is greater than 0.8V but less than 2V and this saturation lasts for 1ms, the IC shuts down. If PS_ON is greater than 2V, the IC works in normal operation mode.                |

| 23   | VCC        | Power supply for the gate driver of the LLC MOSFETs and internal circuit. Bypass VCC to GND with a ceramic capacitor larger than $1\mu F$ .                                                                                                                                                                                                                                                                                                                                                                                       |

| 24   | DIMO       | Output of the driving signal for the dimming MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 25   | GL         | LLC driving signal output. 180 degree phase shift of GR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 26   | GND        | Ground reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 27   | GR         | LLC driving signal output. 180 degree phase shift of GL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 28   | CFLY       | Output of the pulse signal for the charge pump. Connect a flying cap higher than 100nF of the charge pump to CFLY. Please refer to the typical application circuit for connection details.                                                                                                                                                                                                                                                                                                                                        |

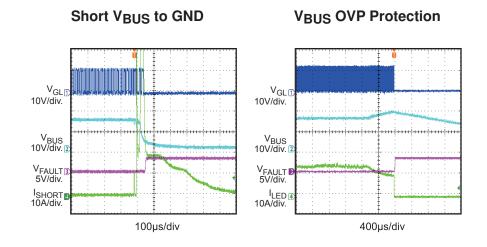

### **BLOCK DIAGRAM**

Figure 1: Functional Block Diagram

#### **OPERATION**

The MP4655 is a pure, single-stage, LLC, LED current and system voltage controller for LED backlighting located on the secondary side. The MP4655 uses the LLC power stage and an extra N-channel MOSFET to regulate both the LED current and the system supply voltage. The MP4655 is powered by 9V to 35V input supplies that output two 180 degree phase shifted driving signals for the external LLC power stages. Its enhanced 12V gate driver provides adequate driving capability and can directly drive the external LLC MOSFETs through an external gate driving transformer. The MP4655 also provides a direct driving signal to control the extra Nchannel MOSFET and regulates the system supply voltage.

The MP4655 uses frequency control on the LLC power stage to regulate the LED current at the PWM dimming on interval and the system bus voltage at the PWM dimming off interval. The duty cycle of the extra N-channel MOSFET regulates the system bus voltage at the PWM on interval. Both the LED current and the system bus voltage are regulated accurately.

#### **Internal Regulator**

The MP4655 includes an internal linear regulator (VCC). VCC is the supply voltage for the LLC gate driver, the charge pump, and the internal circuit. The MP4655 features under-voltage lockout for both the VCC regulator and the inner circuit. Until VIN exceeds its UVLO threshold, the VCC regulator does not work. The chip is disabled until VCC exceeds its UVLO threshold.

The internal VCC regulator is also controlled by the IC enable signal (PS ON).

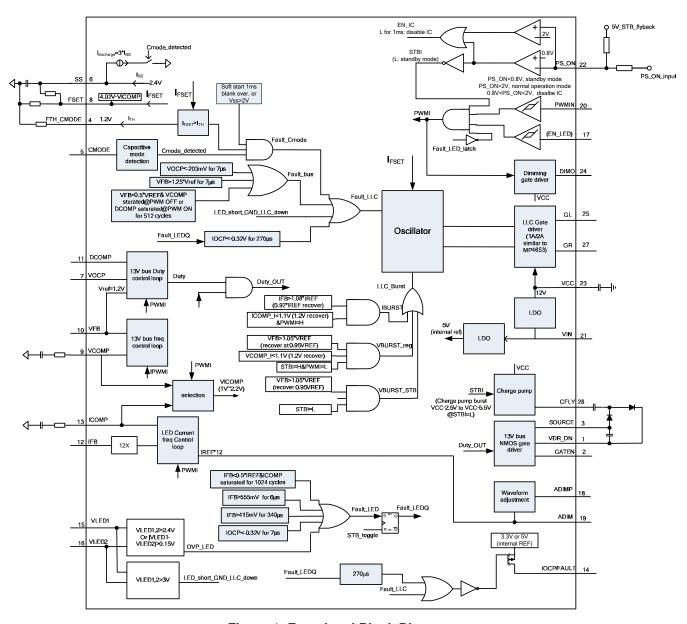

#### Charge Pump and Extra N-Channel MOSFET **Driver**

The MP4655 integrates a charge pump that drives the extra N-channel MOSFET directly (see Figure 2). The charge pump is powered by VCC and outputs a high-frequency square wave signal. Together with an external C-diode network, the charge pump forms a floating driver supply voltage on VDR DN referred to the SOURCE voltage with an amplitude close to VCC. This floating driver supply voltage can directly drive the extra N-channel MOSFET.

Figure 2: Charge Pump for Extra N-Channel **MOSFET Driver**

#### **Operation Modes and System Start-Up**

The MP4655 is controlled by its enable signal (PS ON) and uses the following operating modes:

- 1. PS\_ON > 2V: the IC is enabled in normal operation mode.

- 2.  $0.8V < PS ON \le 2V \text{ for 1ms: the IC is}$ disabled and no circuits work.

- 3. PS ON  $\leq$  0.8V: the IC is enabled in standby mode.

It is very easy to set up the system connection, whether the MP4655 is required to do so in standby or not.

When the MP4655 is enabled and the VIN supply is higher than its UVLO threshold, VCC is charged up. When VCC passes its UVLO threshold, the IC starts up. The voltage resets the control loop for LLC frequency control, voltage control loop for the extra N-channel MOSFET duty cycle control, and the soft-start capacitor.

EN LED and PWMIN control the start-up of the LED driver stage. If either EN LED or PWMIN are low, the LED driver stage is disabled and DIMO is pulled low. The system operates in constant voltage mode, and V<sub>Svstem</sub> is regulated through the LLC frequency control. The extra Nchannel MOSFET is on in this condition. If either EN LED or PWMIN are high, the LED driver stage is enabled and DIMO rises high. The LED current is regulated through the LLC frequency control, and the  $V_{\text{System}}$  is regulated through the duty cycle control of the extra N-channel MOSFET.

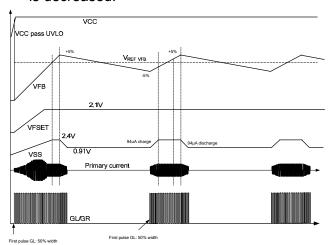

# Standby Mode with Low Consumption Power and No Audible Noise

The MP4655 features a standby mode with low consumption power on the LLC power stage. When PS\_ON  $\leq$  0.8V, the MP4655 enters standby mode, regardless of the status of the LED driver stage control signals.

In standby mode, the LED stage is disabled,  $V_{\text{System}}$  is controlled through the LLC frequency control, and the extra N-channel MOSFET is on. The MP4655 takes the following actions to decrease the system power consumption:

- V<sub>System</sub> is controlled within ± 5% and the circuit works in soft-burst mode. The VFSET voltage is clamped at 2.1V, so the switching frequency at burst mode is not too high. Power consumption is decreased in this mode. A soft burst-on time and soft burst-off time are added to the burst mode to eliminate audible noise (see Figure 3).

- The charge pump for VDR\_DN works in burst mode, and VDR\_DN is controlled with a larger ripple voltage. This decreases the IC consumption current.

- 3. The internal logic circuit consumption current is decreased.

Figure 3: LLC Soft-Burst Operation at Standby Mode

**LED Current and System Voltage Regulation**

The MP4655 accurately regulates both the LED current and the output system voltage with only one LLC power stage.

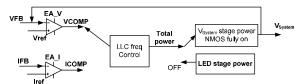

In PWM dimming off condition, the LED stage is not enabled (PWMIN is low, EN\_LED is not enabled, or LED stage fault detected). The MP4655 regulates the output system voltage through the LLC frequency control, and the extra N-channel MOSFET is on (see Figure 4A).

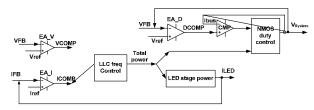

In PWM dimming on condition, the MP4655 regulates the LED current through the LLC frequency control, and regulates the output system voltage through the duty cycle control of the extra N-channel MOSFET. The integrated individual control for this extra N-channel MOSFET achieves soft switching, and there is no voltage spike (see Figure 4B).

Figure 4A: MP4655 Control Scheme at PWM Dimming Off

Figure 4B: MP4655 Control Scheme at PWM Dimming On

The regulation for the LED current and system voltage at different conditions is as follows:

LED current regulation at PWM dimming on (ICOMP loop)

For the LED current regulation loop with LLC frequency control, the LED current is fed back to IFB. The internal error amplifier regulates the average value of IFB signal to the internal 199mV reference voltage. Its output is connected to the external current-loop compensation network on ICOMP through an inner switch (S1).

During the PWM on interval, S1 is on, and the output of the error amplifier is connected to the external compensation network on ICOMP. The

© 2016 MPS. All Rights Reserved.

LED current is regulated by this control loop and the LLC operating frequency is programmed by the ICOMP voltage.

During the PWM off interval, S1 is turned off, and the compensation network on ICOMP disconnected from the error amplifier and holds its value until the next PWM on interval.

The MP4655 integrates burst mode for the LED current regulation. When the IFB voltage is higher than 1.08 times its reference voltage and the ICOMP voltage is low enough (which means it is at its highest operating frequency), the IC skips some switching cycles until the IFB voltage decreases sufficiently.

2. Output system voltage regulation at PWM dimming off (VCOMP loop)

For the system voltage regulation loop, the output system voltage is fed back to VFB. During the PWM off interval, the MP4655 regulates the system voltage through the LLC frequency control, and the extra N-channel MOSFET is on. The internal voltage-loop error amplifier regulates the average value of the VFB voltage to the reference voltage (VREF). Its output is connected external voltage-loop compensation network on VCOMP through an inner switch S2. During the PWM off interval, S2 is on, and the output of the voltage-loop error amplifier is connected to the external compensation network on VCOMP. The output system voltage is regulated by this control loop and the LLC operating frequency is programmed by VCOMP.

During the PWM on interval, S2 is turned off, and the compensation network on VCOMP is disconnected from the error amplifier and holds its value until the next PWM off interval.

The MP4655 also integrates burst mode for voltage regulation with the LLC frequency control through the VCOMP loop. When VFB is higher than 1.05 times the reference voltage and VCOMP is sufficiently low (which means a high LLC operating frequency), the IC skips some switching cycles until VFB voltage decreases sufficiently.

The LLC operating frequency is controlled by the output of the current loop error amplifier on ICOMP at PWM dimming on and is controlled by the voltage loop error amplifier on VCOMP at PWM dimming off. A higher compensation output voltage results in a lower operating frequency.

3. Output system voltage regulation at PWM dimming on (DCOMP loop)

During the PWM on interval, the LLC frequency control regulates the LED current, and the output system voltage is regulated through the duty cycle of the extra N-channel MOSFET. The output system voltage is fed back on VFB, and the internal error amplifier regulates its average value to its reference voltage (VREF). The output of this error amplifier is connected to DCOMP through an inner switch (S3). S3 is on during the PWM on interval, and the output of this error amplifier is connected to the **DCOMP** compensation network. Together with slope compensation, the DCOMP voltage is compared with the current through the output system voltage stage, which is fed back to VOCP and determines the duty cycle of the extra N-channel MOSFET. The duty cycle of this extra N-channel MOSFET can achieve a 0 to 100% range. The MP4655 integrates individual controls on the extra N-channel MOSFET and achieves soft switching with no voltage spike.

During the PWM off interval, S3 is disconnected and DCOMP holds its voltage until the next PWM on interval. The extra N-channel MOSFET is forced on during the PWM off interval.

Both the LED current and output system voltage are accurately regulated at PWM dimming on and PWM dimming off. ICOMP, VCOMP, or DCOMP holds its voltage when its loop is not effective. This achieves a fast transition between different compensation loops at PWM dimming. Together with the external dimming MOSFET, which holds the LED output voltage during the PWM off interval, both the LED current and output system voltage are regulated accurately and smoothly at PWM dimming. No voltage ripple or LED current overshoot or undershoot is caused by PWM dimming.

#### **Dimming Control**

The MP4655 provides two dimming methods: PWM dimming mode and analog dimming mode. Applying a digital PWM signal on PWMIN allows for PWM dimming. The brightness of the LED string is proportional to the duty cycle of the external PWM signal. A driving signal on DIMO is output to drive the dimming MOSFET directly, which helps achieve fast and high-contrast ratio PWM dimming.

The MP4655 achieves a 1000:1 PWM dimming ratio at 200Hz PWM dimming frequency (0.1% minimum PWM dimming duty). The PWM dimming ratio may decrease with a higher PWM dimming frequency.

For analog dimming mode, a DC voltage on ADIM or a pulse signal on ADIMP can be used. For DC input analog dimming, apply a DC analog signal from 0V to 2.4V on ADIM to dim the LED current amplitude from 0 to 100%. ADIMP can be left open or pulled high to VCC through a  $100k\Omega$ resistor in this mode.

For analog dimming with a pulse input signal, apply the pulse signal on ADIMP and a 100nF capacitor on ADIM, depending on the frequency of this pulse signal. The duty cycle of this pulse signal from 0 to 100% dims the LED current from 0 to 100%.

The PWM dimming and analog dimming could be applied to the IC simultaneously for an extra dimming ratio.

#### **Protection Features**

The MP4655 integrates sufficient protection for the LLC power stage, the output system voltage stage, and the LED driver stage.

#### Capacitive Mode Protection for the LLC **Power Stage**

The MP4655 integrates individual capacitive mode protection for the LLC power stage by detecting the secondary side signal. Feed back the secondary side winding voltage to CMODE for capacitive mode protection. When capacitive mode is detected, the MP4655 discharges the SS voltage and increases the LLC operating frequency. If the capacitive mode is still detected when the operating frequency is higher than the threshold frequency setting by FTH CMODE, the IC latches up and outputs a high fault indicator.

#### **System Voltage Stage Protection**

The protections for the system voltage stage include over-system voltage protection, short protection, and open-feedback loop protection.

1. Over-system voltage protection

VFB senses the output system voltage for regulation and over-voltage protection. If the VFB voltage is higher than 1.25V<sub>REF</sub>, the MP4655 triggers the over-system voltage protection and latches up. The fault indicator output is high.

#### 2. System voltage stage short protection

VOCP senses the current through the output system voltage stage for short protection of the system voltage stage. If the voltage on VOCP is lower than -203mV for 7µs, the MP4655 latches up and outputs a high fault indicator.

voltage 3. System stage open-feedback protection

During the PWM dimming off interval, if the VFB voltage is lower than 50% of its reference and VCOMP is saturated for 512 switching cycles, the IC latches up and outputs a high fault indicator.

During the PWM dimming on interval, if the VFB voltage is lower than 50% of its reference voltage and DCOMP is high for 512 cycles, the IC latches up and outputs a high fault indicator.

#### **LED Driver Stage Protection**

The fault protection for the LED driver stage includes the open LED protection, short LED protection, over-LED current protection, open feedback loop protection, and protection for any point of the LED string shorting to ground.

The voltage of the LED strings is sensed on VLED1 and VLED2. Both the maximum value and the difference in voltages of VLED1 and VLED2 are used for protection. When the maximum value of VLED1 and VLED2 rises higher than 2.41V or the difference in the voltages rises higher than 150mV for 8µs, the IC triggers over-LED voltage protection (the voltage difference can be adjusted by the external input resistance on VLED1 or VLED2).

DIMO is pulled low, and the output system voltage is regulated by the LLC frequency control, the same as in PWM off condition, and the fault indicator output is high. If the maximum value of VLED1 and VLED2 rises higher than 3V for 7.6µs. the MP4655 latches up and disables the LLC power stage to avoid any damage to the LED driver stage. The fault indicator output is high.

The secondary side current of the LED driver stage is sensed on IOCP/FAULT. When the

IOCP voltage is lower than -320mV for 7μs, the MP4655 triggers the LED driver stage protection. At the LED driver stage protection, the DIMO is pulled low, and the output system voltage is regulated by the LLC frequency control, the same as in PWM off condition. The fault indicator output is high after 270μs. After the LED driver stage protection is triggered, IOCP/FAULT continues detecting the LED driver stage current. If the voltage on IOCP/FAULT remains lower than -320mV for 270μs, the MP4655 latches up and disables the LLC power stage.

The LED current feedback (IFB) is used for over-LED current protection. When IFB voltage rises higher than 415mV for 340µs or the IFB voltage rises higher than 555mV for 6µs, the IC triggers the LED driver stage protection.

If the voltage on IFB is lower than 50% of its reference voltage, and the ICOMP is saturated

for 1024 cycles, the IC considers this to be a short LED to GND protection or open feedback protection and triggers the LED driver stage protection. The reference voltage varies according to the analog dimming signal.

In a fault condition of the LED driver stage, the gate driving signals for the LLC power MOSFETs are still active and the output system voltage is regulated, only if the LED driver stage can be disconnected from the power stage. Therefore, the system power supply is not influenced by the fault protection of the LED driver stage. A MOSFET can be used to disconnect the LED driver stage at the LED fault condition (see Figure 11).

Thermal protection is also integrated in the MP4655.

#### APPLICATION INFORMATION

#### Frequency Set and Soft Start (SS, FSET)

The resistor on FSET and the resistor between FSET and SS determine the operating frequency, which can be calculated with Equation (1):

$$f = (\frac{V_{FSET}}{R_{FSET}} - \frac{Vss - V_{FSET}}{R_{SS\_FSET}}) * 11.4 * 10^{9} (Hz) (1)$$

Where  $V_{\text{FSET}}$  = 4.01V -  $V_{\text{C}}$ .  $V_{\text{C}}$  is the VCOMP voltage at PWM dimming off and ICOMP voltage at PWM dimming on. The  $V_{\text{C}}$  range is clamped from 1.02V to 2.28V.  $V_{\text{SS}}$  is the voltage on SS, typically 2.4V.

The minimum operating frequency can be calculated with Equation (2):

$$f_{min} = (\frac{1.73V}{R_{FSET}} - \frac{0.675V}{R_{SS-FSET}}) * 11.4 * 10^9 (Hz) (2)$$

The maximum operating frequency at steady state can be calculated with Equation (3):

$$f_{\text{max}} = \left(\frac{2.99V}{R_{\text{FSET}}} + \frac{0.585V}{R_{\text{SS FSET}}}\right) * 11.4 * 10^{9} (\text{Hz}) (3)$$

When  $V_{SS}$  is 0V, the soft start-up frequency is calculated with Equation (4):

$$f_{start} = (\frac{2.99V}{R_{ss}} + \frac{2.99V}{R_{ss}}) * 11.4 * 10^{9} (Hz) (4)$$

The operating frequency at standby mode is calculated with  $V_{ESET} = 2.1V$ . See Equation (5):

$$f_{STB} = (\frac{2.1V}{R_{ESET}} - \frac{0.305V}{R_{SS-ESET}}) * 11.4 * 10^{9} (Hz) (5)$$

It is recommended to set the operating frequency in standby mode close to the LLC resonant frequency ( $f_0$ ) for optimum efficiency.

The soft start-up time is determined by the capacitor on SS and can be calculated with Equation (6):

$$T_{SS} = \frac{2.405V * C_{SS}}{13uA}$$

(6)

A 10nF capacitor on SS results in a 1.85ms softstart time.

#### **LED Current Set (IFB)**

The LED current is set by the current sense resistor on the cathode of LED and can be calculated with Equation (7):

$$I_{LED} = \frac{V_{IREF}}{Rsense} = \frac{199mV}{Rsense}$$

(7)

A  $2k\Omega$  resistor is recommended between the LED current sense resistor and IFB, considering the possible spike voltage on the current sense resistor when shorting the LED string.

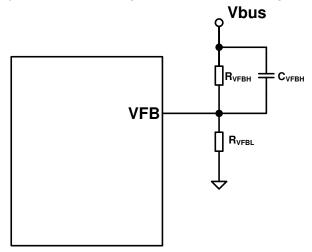

#### System Output Voltage Set (VFB)

VFB feeds back the system output voltage. Adjust the voltage divider to set the output system voltage. See Equation (8):

$$V_{\text{system}} = \frac{V_{\text{REF\_VFB}} * (R_{\text{VFBH}} + R_{\text{VFBL}})}{R_{\text{VFBL}}} = \frac{1.2V * (R_{\text{VFBH}} + R_{\text{VFBL}})}{R_{\text{VFBL}}}$$

(8)

A capacitor ( $C_{VFBH}$ ) between the system output and VFB provides a better phase margin for the system output voltage control loop (see Figure 5).

Figure 5: Voltage Feedback Network

The zero composed by  $R_{VFBH}$  and  $C_{VFBH}$  is recommended to be in range of one-fifth to one-third of the operating frequency. See Equation (9):

$$\frac{1}{2\pi * R_{VFBH} * C_{VFBH}} = (\frac{1}{5} \text{ to } \frac{1}{3}) f_{op}$$

(9)

The VFB also functions as the protection for the over system output voltage. When VFB is 25% higher than its reference voltage, the IC triggers system output voltage stage protection.

#### **LED Current Compensation Loop (ICOMP)**

ICOMP is the compensation node for the LED current control loop. Connect a capacitor in series with a resistor on ICOMP or an R-C-C network (see Figure 6). The zero composed of  $R_{\text{ICOMP}}$  and  $C_{\text{ICOMP}}$  is recommended to cancel the pole formed by the LED output. See Equation (10):

$$\frac{1}{R_{\text{ICOMP}} * C_{\text{ICOMP}}} = \frac{1}{R_{\text{eq\_LED}} * C_{\text{OUT\_LED}}} = \frac{1}{\frac{(10\% \text{ to } 20\%) * V_{\text{LED}}}{I_{\text{LED}}}} * C_{\text{OUT\_LED}}}$$

(10)

$C_{\text{ICOMP}}$  is in range of 10nF to 470nF, typically. Select  $C_{\text{ICOMP\_P}}$  to be less than one-twentieth of  $C_{\text{ICOMP}}$ .

Figure 6: Compensation Network on ICOMP

# System Output Voltage Compensation Loop through LLC Control (VCOMP)

VCOMP is the compensation node for the system output voltage control loop through the LLC frequency. Connect a capacitor in series with a resistor on VCOMP or an R-C-C network (see Figure 7). The zero composed of the  $R_{\text{ICOMP}}$  and  $C_{\text{ICOMP}}$  is recommended to cancel the pole formed by the system output. See Equation (11):

$$\frac{1}{R_{\text{VCOMP}} * C_{\text{VCOMP}}} = \frac{1}{R_{\text{Vbus}} * C_{\text{OUT\_Vbus}}} = \frac{1}{\frac{V_{\text{bus}}}{I_{\text{out\_full}}}} * C_{\text{OUT\_Vbus}}} \tag{11}$$

Where  $C_{\text{VCOMP}}$  is in the range of 10nF to 470nF, typically.

The pole formed by  $R_{VCOMP}$  and  $C_{VCOMP\_P}$  can be designed to be around half of the operating frequency. See Equation (12):

$$\frac{1}{2\pi * R_{VCOMP} * C_{VCOMP P}} = \frac{f_{op}}{2}$$

(12)

Figure 7: Compensation Network on VCOMP

# System Output Voltage Compensation Loop through Duty-Controlled NMOS (DCOMP)

DCOMP is the compensation node for the system output voltage control loop through the duty-controlled NMOS. Connect a capacitor in series with a resistor on DCOMP or an R-C-C network (see Figure 8).

Figure 8: Compensation Network on DCOMP

The zero composed of  $R_{DCOMP}$  and  $C_{DCOMP}$  is recommended to cancel the pole formed by the system output. See Equation (13):

$$\frac{1}{R_{\text{DCOMP}} * C_{\text{DCOMP}}} = \frac{1}{R_{\text{Vbus}} * C_{\text{OUT\_Vbus}}} = \frac{1}{\frac{I}{I_{\text{out\_full}}} * C_{\text{OUT\_Vbus}}} (13)$$

Where  $C_{VCOMP}$  is in the range of 4.7nF to 100nF, typically.

The pole formed by  $R_{DCOMP}$  and  $C_{DCOMP\_P}$  can be designed to be around half of the operating frequency. See Equation (14):

$$\frac{1}{2\pi * R_{DCOMP} * C_{DCOMP, P}} = \frac{f_{op}}{2}$$

(14)

#### Over-Current Protection for the System **Output Stage (VOCP)**

VOCP implements an over-current protection for the system output voltage stage. The current of the system output voltage stage is sensed on VOCP with a negative polarity. When the voltage on VOCP is lower than -203mV, the IC triggers the system output voltage stage protection. Calculate the over-bus current protection threshold with Equation (15):

$$I_{OCP\_Bus} = \frac{203mV}{R_{VOCP}}$$

(15)

Typically, the protection point is around 1.5 to 3 times the normal current of the system output voltage stage.

#### Over-Current Protection for the LED Driver Stage (IOCP/FAULT)