## 4-Channel, 16-Bit, Simultaneous-Sampling ADCs with PGA, Filter, and 8-/12-Bit Dual-Stage DAC

## **General Description**

The MAX11043 features 4 single-ended or differential channels of simultaneous-sampling ADCs with 16-bit resolution. The MAX11043 contains a versatile filter block and programmable-gain amplifier (PGA) per channel. The filter consists of seven cascaded 2nd-order filter sections for each channel, allowing the construction of a 14th-order filter. The filter coefficients are user-programmable. Configure each 2nd-order filter as lowpass (LP), highpass (HP), or bandpass (BP) with optional rectification. Gain and phase mismatch of the analog signal path is better than -50dB.

The ADC can digitize signals up to 200kHz. A 40MHz serial interface provides communication to and from the device. The SPI interface provides throughput of 1600ksps; 4 channels at 400ksps per channel or 2 channels at 800ksps per channel. A software-selectable scan mode allows reading the ADC results while simultaneously updating the DAC. Other features of the MAX11043 include an internal (+2.5V) or external (+2.0V to +2.8V) reference, power-saving modes, and a PGA with gains of 1 to 64. The PGA includes an equalizer (EQ) function that automatically boosts low-amplitude, high-frequency signals for applications such as CW-chirp radar.

The MAX11043 includes two 8-bit coarse DACs that set the high and low references for a second-stage 12-bit fine DAC, typically used for VCO control. Use software controls to write to the DAC or step the DAC up and down under hardware control in programmable steps. The device operates from a +3.0V to +3.6V supply. The MAX11043 is available in a 40-pin, 6mm x 6mm TQFN package and operates over the extended -40°C to +125°C temperature range.

## **Applications**

- Automotive Radar Systems Data Acquisition Systems Industrial Controls

- Power-Grid Monitoring

#### **Features**

- 4 Single-Ended or Differential Channels of Simultaneous-Sampling, 16-Bit ADCs

- ♦ ±10 LSB INL, ±1 LSB DNL, No Missing Codes

- ♦ 93dB SFDR at 100kHz Input

- PGA with Gain of 1, 2, 4, 8, 16, 32, or 64 for Each Channel

- EQ Function Automatically Boosts High-Frequency, Low-Amplitude Signals

- Seven-Stage Internal Programmable Biquad Filters per Channel

- High Throughput, 400ksps per Channel for 4 Channels

- Dual-Stage DAC Two 8-Bit Coarse Reference DACs 12-Bit Fine DAC

- +2.5V Internal Reference or +2.0V to +2.8V External Reference

- Single +3.3V Operation

- Shutdown and Power-Saving Modes

- ♦ 40-Pin, 6mm x 6mm TQFN Package

- ♦ -40°C to +125°C Operating Temperature

#### **Ordering Information**

| PART           | TEMP RANGE      | PIN-PACKAGE |

|----------------|-----------------|-------------|

| MAX11043ATL+   | -40°C to +125°C | 40 TQFN-EP* |

| MAX11043ATL/V+ | -40°C to +125°C | 40 TQFN-EP* |

+Denotes a lead(Pb)-free/RoHS-compliant package. *N* denotes an automotive qualified part.

\*EP = Exposed pad.

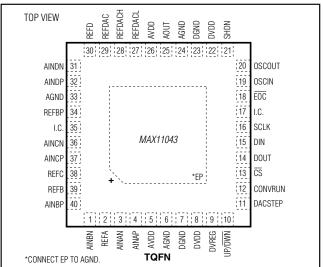

## **Pin Configuration**

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maximintegrated.com.

## **4-Channel, 16-Bit, Simultaneous-Sampling ADCs** with PGA, Filter, and 8-/12-Bit Dual-Stage DAC

#### **ABSOLUTE MAXIMUM RATINGS**

| VDD to AGND0.3V to +4.0V                                      |

|---------------------------------------------------------------|

| OVDD to DGND0.3V to +4.0V                                     |

| OVREG to DGND0.3V to +3.0V                                    |

| AGND to DGND0.3V to +0.3V                                     |

| analog I/O, REFDACH, REFDACL, REFA, REFB, REFC, REFD,         |

| AOUT, REFDAC, REFBP to AGND0.3V to (V <sub>AVDD</sub> + 0.3V) |

| JP/DWN, CONVRUN, SHDN, DACSTEP, EOC, Digital I/O,             |

| OSCIN, OSCOUT to DGND0.3V to (V <sub>DVDD</sub> + 0.3V)       |

| Iaximum Current into Any Pin except AVDD, DVDD, DVREG,        |

| AGND, DGND±50mA                                               |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

|-------------------------------------------------------|----------------|

| TQFN Multilayer Board                                 |                |

| (derate 37mW/°C above +70°C)                          | 2963mW         |

| TQFN Single-Layer Board                               |                |

| (derate 26.3mW/°C above +70°C)                        | 2105.3mW       |

| Operating Temperature Range                           | 40°C to +125°C |

| Junction Temperature                                  | +150°C         |

| Storage Temperature Range                             | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C         |

| Soldering Temperature (reflow)                        | +260°C         |

|                                                       |                |

-----

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{AVDD} = +3.0V \text{ to } +3.6V, V_{DVDD} = +3.0V, C_{DVREG} = 10\mu\text{F}, V_{AGND} = V_{DGND} = 0V, \text{ common-mode input voltage} = V_{AVDD}/2, V_{REFBP} = V_{REFA} = V_{REFD} = V_{REFD} = V_{REFD} = +2.5V \text{ (external reference)}, V_{REFDAC} = V_{REFDACH} = +1.25V \text{ (external reference)}, V_{REFDACL} = 0V, C_{REFBP} = C_{REFA} = C_{REFD} = C_{REFD} = C_{REFD} = C_{REFDAC} = 1\mu\text{F}, \text{f}_{SCLK} = 38.4\text{MHz}, \text{f}_{EXCLK} = 38.4\text{MHz} \text{ (external clock applied to OSCIN)}, clock divider set to 4, SHDN = DACSTEP = UP/DWN = DGND, CONVRUN = DVDD, all analog inputs driven directly through a series 150\Omega/330pF anti-alias filter, PGA gain = 1. Default filters and gain settings. DIFF = 1. T_A = T_{MIN} \text{ to } T_{MAX}, unless otherwise noted (Note 1). Typical values are at T_A = +25^{\circ}\text{C}.)$

| PARAMETER                                | SYMBOL      | CONDITIONS                                                  | MIN    | ТҮР   | МАХ   | UNITS   |

|------------------------------------------|-------------|-------------------------------------------------------------|--------|-------|-------|---------|

| SIGMA-DELTA ADC                          |             | ·                                                           | •      |       |       |         |

| Resolution                               | Ν           |                                                             | 16     |       |       | Bits    |

| Integral Nonlinearity                    | INL         |                                                             | -16    | ±2    |       | LSB     |

| Differential Nonlinearity                | DNL         | Guaranteed monotonic                                        | -1     |       | +1    | LSB     |

| Offset Error                             | OE          |                                                             | -35    |       | +35   | mV      |

| Offset-Error Drift                       |             |                                                             |        | ±30   |       | µV/°C   |

| Gain Error                               | GE          | Trimmed with 150 $\Omega$ /330pF anti-alias filter          | -1     |       | +1    | %       |

| Gain Temperature Coefficient             |             |                                                             |        | ±50   |       | ppm/°C  |

| Channel Gain-Error Matching              |             | Complete analog signal path                                 | -0.25  |       | +0.25 | %       |

| Channel Offset Matching                  |             | Complete analog signal path                                 | -60    |       | +60   | mV      |

| DYNAMIC PERFORMANCE (PGA                 | Disabled, P | GA Gain = 1 x (25kHz -1dB Full-Scale Signa                  | I))    |       |       |         |

| Maximum Full-Scale Input                 |             | ADC modulator gain = 1                                      |        | 1.2   |       | VP-P    |

| Input-Referred Noise Spectral<br>Density |             | 100kHz                                                      |        | 85    |       | nV/√Hz  |

| Second Harmonic to<br>Fundamental        |             |                                                             | -80    | -93   |       | dB      |

| Third Harmonic to Fundamental            |             |                                                             | -80    | -110  |       | dB      |

| Spurious-Free Dynamic Range              | SFDR        |                                                             | 77     | 93    |       | dB      |

| Channel-to-Channel Isolation             |             | Unused channels are shorted and unconnected                 | 85 108 |       |       | dB      |

| Channel Phase Matching                   |             | Between all channels, including complete analog signal path |        | -0.05 | +0.05 | Degrees |

## 4-Channel, 16-Bit, Simultaneous-Sampling ADCs with PGA, Filter, and 8-/12-Bit Dual-Stage DAC

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = +3.0V \text{ to } +3.6V, V_{DVDD} = +3.0V, C_{DVREG} = 10\mu\text{F}, V_{AGND} = V_{DGND} = 0V, \text{ common-mode input voltage} = V_{AVDD}/2, V_{REFBP} = V_{REFA} = V_{REFD} = V_{REFD} = V_{REFD} = +2.5V \text{ (external reference)}, V_{REFDAC} = V_{REFDACH} = +1.25V \text{ (external reference)}, V_{REFDACL} = 0V, C_{REFBP} = C_{REFA} = C_{REFD} = C_{REFD} = C_{REFD} = C_{REFDAC} = 1\mu\text{F}, \text{f}_{SCLK} = 38.4\text{MHz}, \text{f}_{EXCLK} = 38.4\text{MHz} \text{ (external clock applied to OSCIN)}, clock divider set to 4, SHDN = DACSTEP = UP/DWN = DGND, CONVRUN = DVDD, all analog inputs driven directly through a series 150\Omega/330pF anti-alias filter, PGA gain = 1. Default filters and gain settings. DIFF = 1. T_A = T_{MIN} \text{ to } T_{MAX}, unless otherwise noted (Note 1). Typical values are at T_A = +25^{\circ}\text{C}.)$

| PARAMETER                                | SYMBOL        | CONDITIONS                                                  | MIN        | ТҮР | MAX    | UNITS              |

|------------------------------------------|---------------|-------------------------------------------------------------|------------|-----|--------|--------------------|

| DYNAMIC PERFORMANCE (PG)                 | A Enabled, PO | GA Gain = 8 x (25kHz -1dB Full-Scale Signal                 | ))         |     |        |                    |

| Maximum Full-Scale Input                 |               | ADC modulator gain = 1                                      |            | 150 |        | mV <sub>P-P</sub>  |

| Input-Referred Noise Spectral<br>Density |               | 100kHz                                                      |            | 20  |        | nV/√ <del>Hz</del> |

| Second Harmonic to<br>Fundamental        |               |                                                             |            | -92 |        | dB                 |

| Third Harmonic to Fundamental            |               |                                                             |            | -94 |        | dB                 |

| Spurious-Free Dynamic Range              | SFDR          |                                                             |            | 92  |        | dB                 |

| Channel-to-Channel Isolation             |               | Unused channels are shorted and unconnected                 |            | 110 |        | dB                 |

| Channel Phase Matching                   |               | Between all channels, including complete analog signal path | -0.05      |     | +0.05  | Degrees            |

| DYNAMIC PERFORMANCE (PG)                 | A Enabled, PC | GA Gain = 16 x (25kHz -1dB Full-Scale Signa                 | i))        |     |        |                    |

| Maximum Full-Scale Input                 |               | ADC modulator gain = 1                                      |            | 75  |        | mV <sub>P-P</sub>  |

| Input-Referred Noise Spectral<br>Density |               | 100kHz                                                      |            | 15  |        | nV/√Hz             |

| Second Harmonic to<br>Fundamental        |               |                                                             |            | -99 |        | dB                 |

| Third Harmonic to Fundamental            |               |                                                             |            | -93 |        | dB                 |

| Spurious-Free Dynamic Range              | SFDR          |                                                             |            | 93  |        | dB                 |

| Channel-to-Channel Isolation             |               | Unused channels are shorted and unconnected                 |            | 106 |        | dB                 |

| Channel Phase Matching                   |               | Between all channels, including complete analog signal path | -0.075     |     | +0.075 | Degrees            |

| DYNAMIC PERFORMANCE (EQ                  | Mode (5kHz -  | 1dB Full-Scale Signal, CONFIG_ Register B                   | it 3 = 1)) |     |        |                    |

| Maximum Full-Scale Input                 |               | ADC modulator gain = 1 (Note 2)                             |            | 800 |        | mV <sub>P-P</sub>  |

| Input-Referred Noise Spectral<br>Density |               | 100kHz                                                      |            | 6   |        | nV/√Hz             |

| Second Harmonic to<br>Fundamental        |               |                                                             | -80        | -90 |        | dB                 |

| Third Harmonic to Fundamental            |               |                                                             | -77        | -98 |        | dB                 |

| Spurious-Free Dynamic Range              | SFDR          | Input referred (Note 3)                                     | 77         | 89  |        | dB                 |

# **4-Channel, 16-Bit, Simultaneous-Sampling ADCs** with PGA, Filter, and 8-/12-Bit Dual-Stage DAC

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = +3.0V \text{ to } +3.6V, V_{DVDD} = +3.0V, C_{DVREG} = 10\mu\text{F}, V_{AGND} = V_{DGND} = 0V, \text{ common-mode input voltage} = V_{AVDD}/2, V_{REFBP} = V_{REFA} = V_{REFD} = V_{REFD} = V_{REFD} = +2.5V \text{ (external reference)}, V_{REFDAC} = V_{REFDACH} = +1.25V \text{ (external reference)}, V_{REFDACL} = 0V, C_{REFBP} = C_{REFA} = C_{REFD} = C_{REFD} = C_{REFD} = C_{REFDAC} = 1\mu\text{F}, \text{fs}_{CLK} = 38.4\text{MHz}, \text{fe}_{XCLK} = 38.4\text{MHz} \text{ (external clock applied to OSCIN)}, clock divider set to 4, SHDN = DACSTEP = UP/DWN = DGND, CONVRUN = DVDD, all analog inputs driven directly through a series 150\Omega/330pF anti-alias filter, PGA gain = 1. Default filters and gain settings. DIFF = 1. T_A = T_{MIN} \text{ to } T_{MAX}, unless otherwise noted (Note 1). Typical values are at T_A = +25^{\circ}\text{C}.)$

| PARAMETER                     | SYMBOL             | CONDI                                       | TIONS               | MIN   | ТҮР  | MAX   | UNITS   |

|-------------------------------|--------------------|---------------------------------------------|---------------------|-------|------|-------|---------|

| Channel-to-Channel Isolation  |                    | Unused channels are s<br>unconnected        | shorted and         | 80    | 104  |       | dB      |

| Channel Phase Matching        |                    | Between all channels,<br>analog signal path | including complete  | -0.12 |      | +0.12 | Degrees |

| DYNAMIC PERFORMANCE (All      | Modes)             | ·                                           |                     |       |      |       |         |

| Conversion Rate               |                    | All 4 channels                              |                     |       |      | 400   | kapa    |

| Conversion Rale               |                    | 2 channels only                             |                     |       |      | 800   | ksps    |

| Minimum Throughput            |                    |                                             |                     |       | 5    |       | ksps    |

| Power-Supply Rejection Ratio  | DCPSRR             |                                             |                     |       | 50   |       | dB      |

| ANALOG INPUTS (AINAP/AINA     | N, AINBP/AIN       | BN, AINCP/AINCN, AIN                        | DP/AINDN)           |       |      |       |         |

| Absolute Voltage Any Input    |                    | (Note 4)                                    |                     | 0     |      | VAVDD | V       |

| Input Impedance (Note 5)      |                    | Direct input to ADC,                        | DIFF = 1            | 25    |      |       |         |

|                               |                    | gain = 1                                    | DIFF = 0            | 100   |      |       |         |

|                               |                    | Direct input to ADC, gain = $2$             |                     | 7     |      |       | kΩ      |

|                               |                    | Direct input to ADC, gain = 4 or 8          |                     | 7     |      |       |         |

|                               |                    | PGA gain = 16                               |                     | 5.5   |      |       |         |

| Input Capacitance             |                    | EQ mode only                                |                     |       | 50   |       | pF      |

| EQ FILTER (Analog and Digital | )                  |                                             |                     |       |      |       |         |

| Unity-Gain Frequency          |                    | Default                                     |                     |       | 5    |       | kHz     |

| Lower Transition Frequency    |                    | Default, from 40dB/dec                      | cade to 0dB/decade  |       | 190  |       | kHz     |

| Upper Transition Frequency    |                    | Default, from 0dB/deca                      | ade to -80dB/decade |       | 205  |       | kHz     |

| LP FILTER                     |                    |                                             |                     |       |      |       |         |

| -3dB Corner Frequency         |                    | Default                                     |                     |       | 205  |       | kHz     |

| REFERENCE INPUT               |                    |                                             |                     |       |      |       |         |

| REF_ Input Voltage Range      | V <sub>REF</sub> _ |                                             |                     | 2     | 2.5  | 2.8   | V       |

| Input Current                 |                    |                                             |                     |       |      | 150   | μA      |

| REFBP Input Voltage Range     | VREFBP             |                                             |                     | 2     | 2.5  | 2.8   | V       |

| Input Current                 |                    |                                             |                     |       |      | 700   | μA      |

| REFDAC Input Voltage Range    | VREFDAC            |                                             |                     | 1     | 1.25 | 1.4   | V       |

| Input Resistance              |                    |                                             |                     | 17    |      |       | kΩ      |

## 4-Channel, 16-Bit, Simultaneous-Sampling ADCs with PGA, Filter, and 8-/12-Bit Dual-Stage DAC

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = +3.0V \text{ to } +3.6V, V_{DVDD} = +3.0V, C_{DVREG} = 10\mu\text{F}, V_{AGND} = V_{DGND} = 0V, \text{ common-mode input voltage} = V_{AVDD}/2, V_{REFBP} = V_{REFA} = V_{REFD} = V_{REFD} = V_{REFD} = +2.5V \text{ (external reference)}, V_{REFDAC} = V_{REFDACH} = +1.25V \text{ (external reference)}, V_{REFDACL} = 0V, C_{REFBP} = C_{REFA} = C_{REFD} = C_{REFD} = C_{REFD} = C_{REFDAC} = 1\mu\text{F}, \text{f}_{SCLK} = 38.4\text{MHz}, \text{f}_{EXCLK} = 38.4\text{MHz} \text{ (external clock applied to OSCIN)}, clock divider set to 4, SHDN = DACSTEP = UP/DWN = DGND, CONVRUN = DVDD, all analog inputs driven directly through a series 150\Omega/330pF anti-alias filter, PGA gain = 1. Default filters and gain settings. DIFF = 1. T_A = T_{MIN} \text{ to } T_{MAX}, unless otherwise noted (Note 1). Typical values are at T_A = +25^{\circ}\text{C}.)$

| PARAMETER                               | SYMBOL          | CONDITIONS                             | MIN                        | ТҮР | MAX                        | UNITS  |

|-----------------------------------------|-----------------|----------------------------------------|----------------------------|-----|----------------------------|--------|

| REFDAC_ Input Voltage Range             | VREFDAC_        |                                        | 0                          |     | 1.4                        | V      |

| Input Resistance                        |                 |                                        | 150                        |     |                            | kΩ     |

| INTERNAL REFERENCE                      |                 |                                        |                            |     |                            |        |

| Reference Voltage                       | VREFBP          |                                        | 2.45                       | 2.5 | 2.55                       | V      |

| Reference Temperature<br>Coefficient    |                 |                                        |                            | 100 |                            | ppm/°C |

| <b>CRYSTAL OSCILLATOR (Max ES</b>       | SR 100Ω, 22p    | F Load Capacitors to DGND)             |                            |     |                            |        |

| Maximum Crystal Operating<br>Frequency  |                 | Epson Electronics MA-505 (16MHz)       | 16                         |     |                            | MHz    |

| External Clock Input Frequency<br>Range |                 | External clock applied to OSCIN        | 4                          |     | 40                         | MHz    |

| Stability                               |                 | Excluding crystal                      |                            | 25  |                            | ppm    |

| Startup Time                            |                 | Epson Electronics MA-505 (16MHz)       |                            | 10  |                            | ms     |

| OSCIN Input Low Voltage                 |                 | When driven with external clock source |                            |     | 0.3 x<br>V <sub>DVDD</sub> | V      |

| OSCIN Input High Voltage                |                 | When driven with external clock source | 0.7 x<br>V <sub>DVDD</sub> |     |                            | V      |

| OSCIN Leakage Current                   |                 |                                        | -5                         |     | +5                         | μA     |

| DIGITAL INPUTS                          |                 | ·                                      |                            |     |                            |        |

| Input High Voltage                      | VIH             |                                        | 0.7 x<br>V <sub>DVDD</sub> |     |                            | V      |

| Input Low Voltage                       | VIL             |                                        |                            |     | 0.3 x<br>V <sub>DVDD</sub> | V      |

| Input Hysterisis                        |                 |                                        |                            | 15  |                            | mV     |

| Input Leakage Current                   | l <sub>IN</sub> | $V_{IN} = 0V \text{ or } V_{DVDD}$     | -1                         |     | +1                         | μA     |

| Input Capacitance                       | CIN             |                                        |                            | 15  |                            | рF     |

| DIGITAL OUTPUTS                         |                 |                                        |                            |     |                            |        |

| Output-Voltage High                     | V <sub>OH</sub> | I <sub>SOURCE</sub> = 0.8mA            | V <sub>DVDD</sub><br>- 0.6 |     |                            | V      |

| Output-Voltage Low                      | Vol             | I <sub>SINK</sub> = 1.6mA              |                            |     | 0.4                        | V      |

| Three-State Leakage Current             |                 | DOUT only                              | -1                         |     | +1                         | μA     |

| Three-State Output Capacitance          |                 | DOUT only                              |                            | 15  |                            | pF     |

| VOLTAGE REGULATOR                       |                 |                                        |                            |     |                            |        |

| Regulated Digital Supply Voltage        | DVREG           | Internal use only                      |                            | 2.5 |                            | V      |

| POWER REQUIREMENTS                      |                 |                                        |                            |     |                            |        |

| Analog Supply Voltage                   |                 |                                        | 3.0                        |     | 3.6                        | V      |

| Digital Supply Voltage                  |                 |                                        | 3.0                        |     | 3.6                        | V      |

# **4-Channel, 16-Bit, Simultaneous-Sampling ADCs** with PGA, Filter, and 8-/12-Bit Dual-Stage DAC

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = +3.0V \text{ to } +3.6V, V_{DVDD} = +3.0V, C_{DVREG} = 10\mu\text{F}, V_{AGND} = V_{DGND} = 0V, \text{ common-mode input voltage} = V_{AVDD}/2, V_{REFBP} = V_{REFA} = V_{REFD} = V_{REFD} = V_{REFD} = +2.5V \text{ (external reference)}, V_{REFDAC} = V_{REFDACH} = +1.25V \text{ (external reference)}, V_{REFDACL} = 0V, C_{REFBP} = C_{REFA} = C_{REFD} = C_{REFD} = C_{REFD} = C_{REFDAC} = 1\mu\text{F}, \text{fs}_{CLK} = 38.4\text{MHz}, \text{fe}_{XCLK} = 38.4\text{MHz} \text{ (external clock applied to OSCIN)}, clock divider set to 4, SHDN = DACSTEP = UP/DWN = DGND, CONVRUN = DVDD, all analog inputs driven directly through a series 150\Omega/330pF anti-alias filter, PGA gain = 1. Default filters and gain settings. DIFF = 1. T_A = T_{MIN} \text{ to } T_{MAX}, unless otherwise noted (Note 1). Typical values are at T_A = +25^{\circ}\text{C}.)$

| PARAMETER                               | SYMBOL                    | CONDIT                        | MIN          | ТҮР    | MAX | UNITS |                   |

|-----------------------------------------|---------------------------|-------------------------------|--------------|--------|-----|-------|-------------------|

|                                         |                           |                               | PGA disabled |        | 60  | 80    |                   |

| Analog Supply Current                   | IAVDD                     | All channels selected         | PGA enabled  |        | 120 | 140   | mA                |

| Digital Supply Current                  | IDVDD                     |                               |              |        | 26  | 40    | mA                |

| Shutdown Current                        | IAVDD                     |                               |              |        |     | 5     | ~^^               |

| Shuldown Current                        | IDVDD                     |                               |              |        |     | 5     | mA                |

| STATIC ACCURACY—FINE DA                 | C (C <sub>L</sub> = 200pF | , R <sub>L</sub> = 10kΩ)      |              |        |     |       |                   |

| Resolution                              |                           |                               |              | 12     |     |       | Bits              |

| Integral Nonlinearity                   | INL                       |                               |              | -5     |     | +5    | LSB               |

| Differential Nonlinearity               | DNL                       | Guaranteed monotonic          |              | -1     |     | +1    | LSB               |

| Offset Error                            |                           |                               |              | -70    |     | +70   | mV                |

| Offset-Error Temperature<br>Coefficient |                           |                               |              |        | ±50 |       | µV/°C             |

| Gain Error                              |                           |                               |              | -2     |     | 0     | %                 |

| Gain-Error Temperature<br>Coefficient   |                           |                               |              |        | ±20 |       | ppm of<br>FS/°C   |

| DYNAMIC PERFORMANCE—F                   | INE DAC (CL =             | 200pF, R <sub>L</sub> = 10kΩ) |              |        |     |       |                   |

| Output Noise                            |                           | f = 0.1Hz to $1MHz$           |              |        | 200 |       | μV <sub>RMS</sub> |

| DAC Glitch Impulse                      |                           | Major carry transition        |              |        | 12  |       | nV∙s              |

|                                         |                           | 25% to 75% FS                 |              |        | 3   |       |                   |

| Voltage-Output Settling Time            |                           | 1% FS                         |              |        | 1.5 |       | μs                |

| Voltage-Output Slew Rate                |                           |                               |              |        | 0.6 |       | V/µs              |

| STATIC ACCURACY-REFDAC                  | H AND REFD                | ACL                           |              |        |     |       |                   |

| Resolution                              |                           |                               |              | 8      |     |       | Bits              |

| Integral Nonlinearity                   | INL                       |                               |              | -0.5   |     | +0.5  | LSB               |

| Differential Nonlinearity               | DNL                       |                               |              | -0.2   |     | +0.2  | LSB               |

| Offset Error                            |                           |                               |              | -30    |     | +30   | mV                |

| Offset-Error Temperature<br>Coefficient |                           |                               |              |        | ±50 |       | µV/°C             |

| Gain Error                              |                           |                               |              | -5     |     | +5    | LSB               |

| Gain-Error Temperature<br>Coefficient   |                           |                               |              |        |     | ±20   | ppm of<br>FS/°C   |

| FLASH MEMORY                            |                           | •                             |              |        |     |       | •                 |

| Programming Endurance                   |                           |                               |              | 10,000 |     |       | Cycles            |

| Data Retention                          |                           | $T_A = +85^{\circ}C$          |              | 15     |     |       | Years             |

## 4-Channel, 16-Bit, Simultaneous-Sampling ADCs with PGA, Filter, and 8-/12-Bit Dual-Stage DAC

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = +3.0V \text{ to } +3.6V, V_{DVDD} = +3.0V, C_{DVREG} = 10\mu\text{F}, V_{AGND} = V_{DGND} = 0V, \text{ common-mode input voltage} = V_{AVDD}/2, V_{REFBP} = V_{REFA} = V_{REFD} = V_{REFD} = V_{REFD} = +2.5V \text{ (external reference)}, V_{REFDAC} = V_{REFDACH} = +1.25V \text{ (external reference)}, V_{REFDACL} = 0V, C_{REFBP} = C_{REFA} = C_{REFD} = C_{REFD} = C_{REFD} = C_{REFDAC} = 1\mu\text{F}, \text{fs}_{CLK} = 38.4\text{MHz}, \text{fe}_{XCLK} = 38.4\text{MHz} \text{ (external clock applied to OSCIN)}, clock divider set to 4, SHDN = DACSTEP = UP/DWN = DGND, CONVRUN = DVDD, all analog inputs driven directly through a series 150\Omega/330pF anti-alias filter, PGA gain = 1. Default filters and gain settings. DIFF = 1. T_A = T_{MIN} \text{ to } T_{MAX}, unless otherwise noted (Note 1). Typical values are at T_A = +25^{\circ}\text{C}.)$

| PARAMETER                                    | SYMBOL           | CONDITIONS               | MIN | ТҮР | МАХ | UNITS |

|----------------------------------------------|------------------|--------------------------|-----|-----|-----|-------|

| SPI INTERFACE                                |                  |                          |     |     |     |       |

| SCLK Clock Period                            | tCP              |                          | 25  |     |     | ns    |

| SCLK Pulse-Width High                        | tсн              |                          | 10  |     |     | ns    |

| SCLK Pulse-Width Low                         | tCL              |                          | 10  |     |     | ns    |

| SCLK Rise to DOUT Transition                 | <b>t</b> DOT     | $C_{LOAD} = 20 pF$       | 1   |     | 15  | ns    |

| CS Fall to SCLK Rise Setup Time              | tcss             |                          | 10  |     |     | ns    |

| SCLK Rise to $\overline{CS}$ Rise Setup Time | tCSH             |                          | 5   |     |     | ns    |

| DIN to SCLK Rise Setup Time                  | tDS              |                          | 10  |     |     | ns    |

| DIN to SCLK Rise Hold Time                   | tDH              |                          | 0   |     |     | ns    |

| CS Pulse-Width High                          | <b>t</b> CSPWH   |                          | 10  |     |     | ns    |

| CS Rise to DOUT Disable                      | tdod             | C <sub>LOAD</sub> = 20pF |     |     | 20  | ns    |

| CS Fall to DOUT Enable                       | <b>t</b> DOE     | $C_{LOAD} = 20 pF$       | 1   |     |     | ns    |

| EOC Fall to CS Fall                          | t <sub>RDS</sub> |                          | 10  |     |     | ns    |

Note 1: Devices 100% production tested at  $T_A = +125^{\circ}C$ . Guaranteed by design and characterization to  $T_A = -40^{\circ}C$ .

Note 2: Full scale in analog EQ mode decreases with increasing frequency at a rate of 20dB/decade from 8kHz. If digital EQ is also used, full scale decreases with increasing frequency at 40dB/decade from 5kHz.

**Note 3:** SFDR in the EQ mode is normalized to the input by subtracting the analog EQ gain at each frequency (20dB/decade) from the FFT results.

Note 4: The absolute input voltage range is 0 to AVDD. For optimal performance, use a common-mode voltage of AVDD/2.

Note 5: Switched capacitor input impedance is proportional to 1/fC. Where f is the sampling frequency and C is the input capacitance.

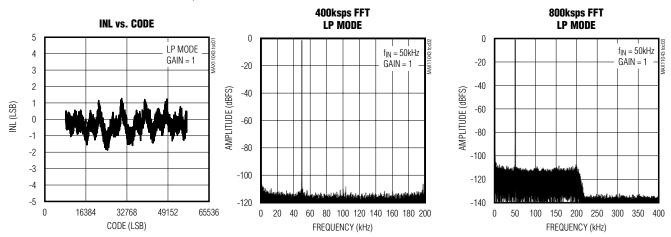

## **Typical Operating Characteristics**

$(V_{AVDD} = +3.3V, V_{DVDD} = +3.0V, f_{SCLK} = f_{EXCLK} = 19.2MHz, V_{REFBP}, V_{REF} = +2.5V, common-mode input voltage = V_{AVDD}/2, T_A = +25°C, unless otherwise noted.)$

# **4-Channel, 16-Bit, Simultaneous-Sampling ADCs with PGA, Filter, and 8-/12-Bit Dual-Stage DAC**

# 4-Channel, 16-Bit, Simultaneous-Sampling ADCs with PGA, Filter, and 8-/12-Bit Dual-Stage DAC

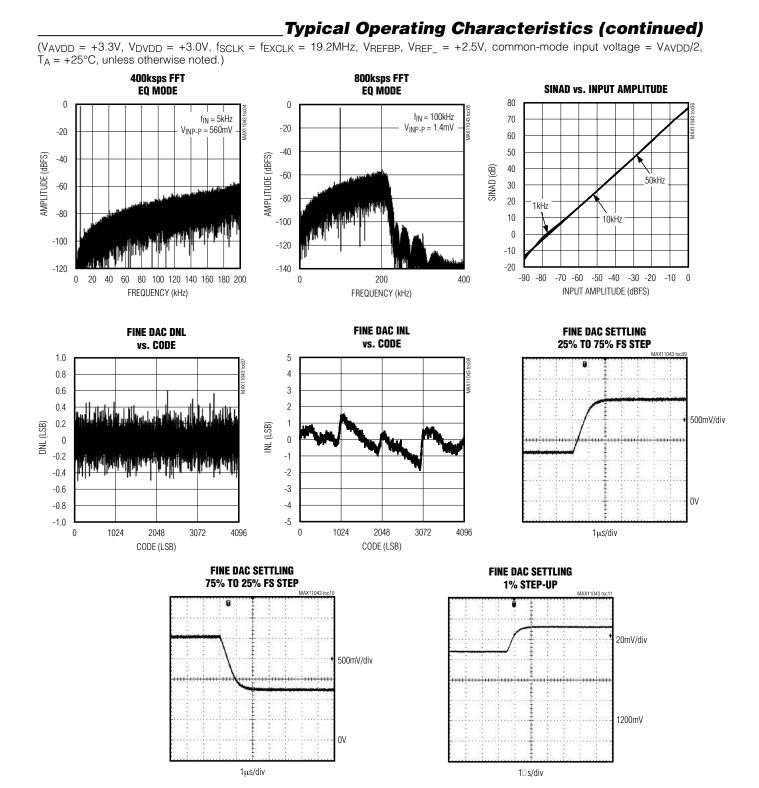

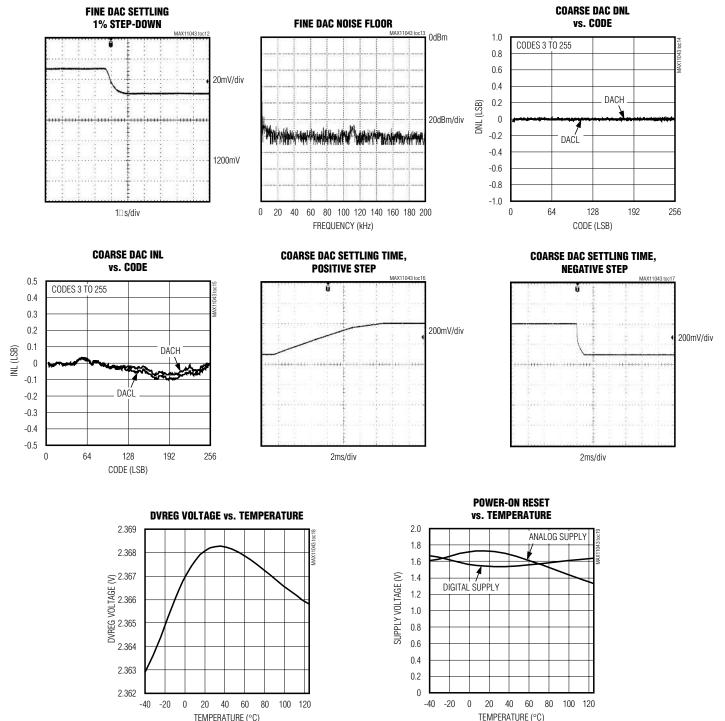

### Typical Operating Characteristics (continued)

$(V_{AVDD} = +3.3V, V_{DVDD} = +3.0V, f_{SCLK} = f_{EXCLK} = 19.2MHz, V_{REFBP}, V_{REF} = +2.5V, common-mode input voltage = V_{AVDD}/2, T_A = +25°C, unless otherwise noted.)$

# **4-Channel, 16-Bit, Simultaneous-Sampling ADCs with PGA, Filter, and 8-/12-Bit Dual-Stage DAC**

## **Pin Description**

| PIN       | NAME    | FUNCTION                                                                                                                                                           |

|-----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1         | AINBN   | Channel B Analog Negative Input                                                                                                                                    |

| 2         | REFA    | Channel A Reference Bypass. Bypass REFA with a nominal 1µF capacitor to AGND.                                                                                      |

| 3         | AINAN   | Channel A Analog Negative Input                                                                                                                                    |

| 4         | AINAP   | Channel A Analog Positive Input                                                                                                                                    |

| 5, 26     | AVDD    | Analog Supply. Bypass each AVDD with a nominal 1µF capacitor to AGND.                                                                                              |

| 6, 24, 33 | AGND    | Analog Ground. Connect AGND inputs together.                                                                                                                       |

| 7, 23     | DGND    | Digital Ground. Connect DGND inputs together.                                                                                                                      |

| 8, 22     | DVDD    | Digital Supply. Bypass each DVDD with a nominal $1\mu$ F capacitor to DGND.                                                                                        |

| 9         | DVREG   | Regulated Digital Core Supply. Bypass DVREG to DGND with a 10µF capacitor.                                                                                         |

| 10        | UP/DWN  | DAC Step Direction Select. Drive high to step up, drive low to step down when DACSTEP is toggled.                                                                  |

| 11        | DACSTEP | DAC Step Input. Drive high to move the DAC output in the direction of UP/DWN on the next rising edge of the system clock.                                          |

| 12        | CONVRUN | Convert Run. Drive high to start continuous conversions on all 4 channels. The device is idle when CONVRUN is low.                                                 |

| 13        | CS      | Active-Low Serial-Interface Chip Select                                                                                                                            |

| 14        | DOUT    | Serial-Interface Data Out. Data transitions on the rising edge of SCLK.                                                                                            |

| 15        | DIN     | Serial-Interface Data In. Data is sampled on the rising edge of SCLK.                                                                                              |

| 16        | SCLK    | Serial-Interface Clock                                                                                                                                             |

| 17, 35    | I.C.    | Internally Connected. Connect to either AGND or DGND.                                                                                                              |

| 18        | EOC     | Active-Low End-of-Conversion Indicator. EOC asserts low to indicate that new data is ready.                                                                        |

| 19        | OSCIN   | Crystal Oscillator/External Clock Input                                                                                                                            |

| 20        | OSCOUT  | Crystal-Oscillator Output. Leave unconnected when using external clock.                                                                                            |

| 21        | SHDN    | Active-High Shutdown Input. Drive high to shut down the MAX11043.                                                                                                  |

| 25        | AOUT    | Buffered 12-Bit Fine DAC Output                                                                                                                                    |

| 27        | REFDACL | Fine DAC Low Reference Bypass. Bypass REFDACL with a nominal 1µF capacitor to AGND.                                                                                |

| 28        | REFDACH | Fine DAC High Reference Bypass. Bypass REFDACH with a nominal 1µF capacitor to AGND.                                                                               |

| 29        | REFDAC  | Coarse DAC Reference Bypass. Bypass REFDAC with a nominal 1µF capacitor to AGND.                                                                                   |

| 30        | REFD    | Channel D Reference Bypass. Bypass REFD with a nominal $1\mu$ F capacitor to AGND.                                                                                 |

| 31        | AINDN   | Channel D Analog Negative Input                                                                                                                                    |

| 32        | AINDP   | Channel D Analog Positive Input                                                                                                                                    |

| 34        | REFBP   | Main Reference Bypass. Bypass REFBP with a nominal 1µF capacitor to AGND.                                                                                          |

| 36        | AINCN   | Channel C Analog Negative Input                                                                                                                                    |

| 37        | AINCP   | Channel C Analog Positive Input                                                                                                                                    |

| 38        | REFC    | Channel C Reference Bypass. Bypass REFC with a nominal 1µF capacitor to AGND.                                                                                      |

| 39        | REFB    | Channel B Reference Bypass. Bypass REFB with a nominal 1µF capacitor to AGND.                                                                                      |

| 40        | AINBP   | Channel B Analog Positive Input                                                                                                                                    |

|           | EP      | Exposed Pad. Connect EP to a ground plane on the PCB to enhance thermal dissipation. Internally connected to AGND. Not intended as an electrical connection point. |

# 4-Channel, 16-Bit, Simultaneous-Sampling ADCs with PGA, Filter, and 8-/12-Bit Dual-Stage DAC

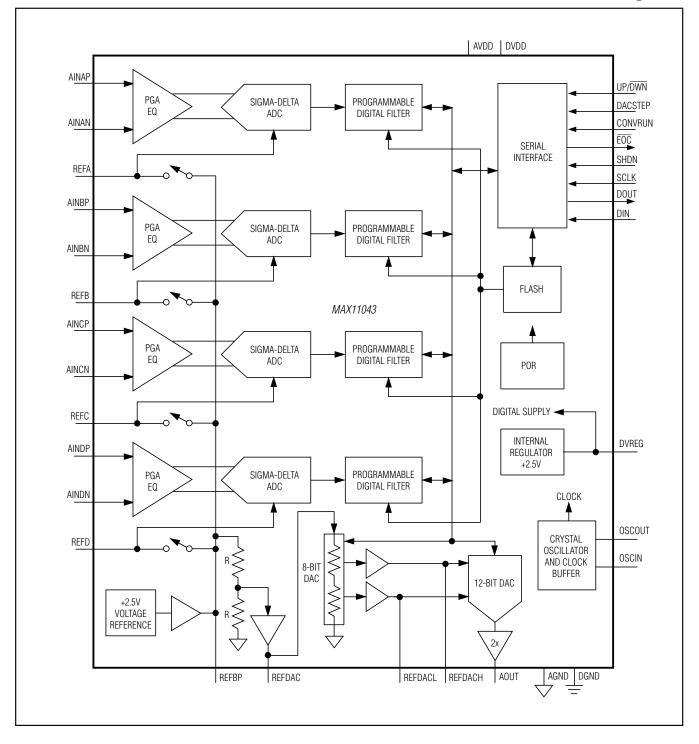

**Functional Diagram**

# 4-Channel, 16-Bit, Simultaneous-Sampling ADCs with PGA, Filter, and 8-/12-Bit Dual-Stage DAC

## **Detailed Description**

The MAX11043 features 4 single-ended or differential channels of simultaneous-sampling ADCs with 16-bit resolution. The MAX11043 contains a versatile filter block and PGA per channel. The filter consists of seven cascaded 2nd-order filter sections for each channel allowing the construction of a 14th-order filter. The filter coefficients are user-programmable. Configure each 2nd-order filter as a LP filter, HP filter, or BP filter with optional rectification. Gain and phase mismatch of the analog signal path is better than -50dB.

The ADCs can digitize signals up to 200kHz. A 40MHz serial interface provides communication to and from the device. The SPI interface provides throughput of 1600ksps; 4 channels at 400ksps per channel or 2 channels at 800ksps per channel. A software-selectable scan mode allows reading the ADC results while simultaneously updating the DAC. Other features of the MAX11043 include an internal (+2.5V) or external (+2.0V to +2.8V) reference, power-saving modes, and a PGA with gains of 1 to 64. The PGA includes an EQ function that automatically boosts low-amplitude, high-frequency signals for applications such as CW-chirp radar.

The MAX11043 includes two 8-bit coarse DACs that set the high and low references for a second-stage 12-bit fine DAC, typically used for VCO control. Use software controls to set the DAC, or step the DAC up and down using hardware control in programmable steps.

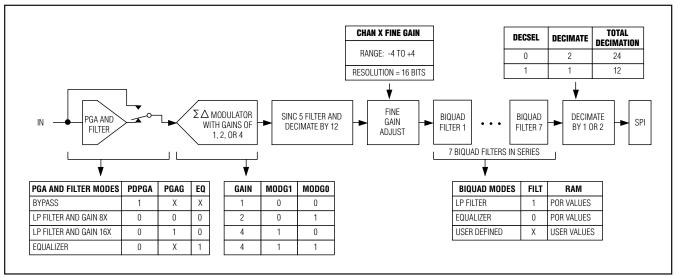

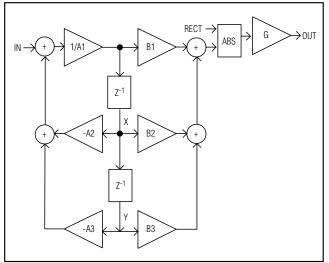

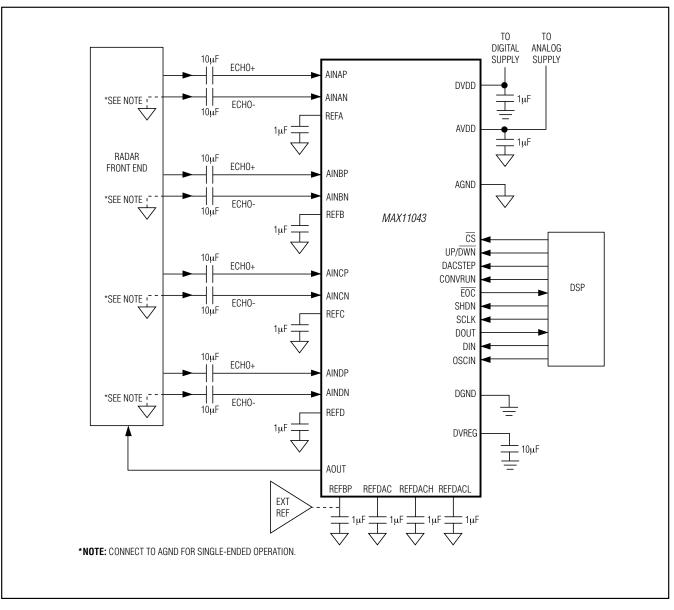

#### MAX11043 Signal Path

Each of the 4 ADC channels features a PGA and filter block that feeds the signal to the sigma-delta modulator. The PGA can either be bypassed, which provides a gain of 1, set to a gain of 8, a gain of 16, or set to analog EQ mode. For more amplification, set the ADC modulator gain to one, two, or four. After the modulator, the result passes through the sinc 5 filter and decimator. Seven biquad programmable digital filters isolate the band of interest. Read the result using the 40MHz SPI interface. See Figure 1.

#### **Analog-to-Digital Converter**

The MAX11043 features a quad sigma-delta ADC architecture with 4 differential input channels. For singleended operation, connect the N input to the common-mode voltage or bypass to AGND with a 10µF capacitor. All inputs feature a programmable bias generator; see the *CONFIG\_ Register (0Ch–0Fh)* section. All four ADCs convert simultaneously with a maximum modulator sampling rate of 9.6Msps; decimated by 12 or 24 for output rates of 800ksps and 400ksps, respectively. The SPI bus limits the maximum output data rate to 40Mbps.

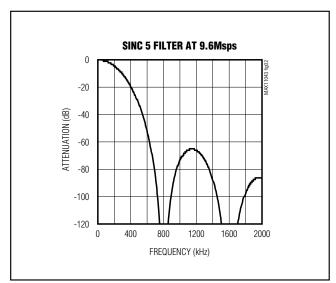

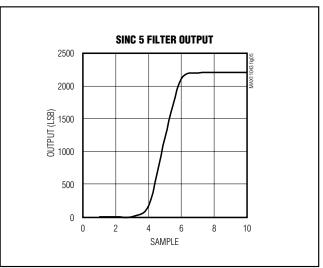

#### **Sinc 5 Filter**

The sinc 5 filter removes high-frequency noise from the output of the sigma-delta modulator and sets the upper frequency response of the ADC. It also decimates the modulator data by a factor of 12, providing a maximum of 800ksps to the programmable filters when the modulator is operating at 9.6Msps. Figure 2 shows the frequency characteristics of the sinc 5 filter with the

Figure 1. Signal Path

## 4-Channel, 16-Bit, Simultaneous-Sampling ADCs with PGA, Filter, and 8-/12-Bit Dual-Stage DAC

modulator running at 9.6Msps. Operating the modulator at a lower sample rate causes a proportional reduction in the frequency response of the sinc 5 filter. The total attenuation of the MAX11043 is the sum of the analog filtering, the sinc 5 filter, and the seven stages of programmable filters.

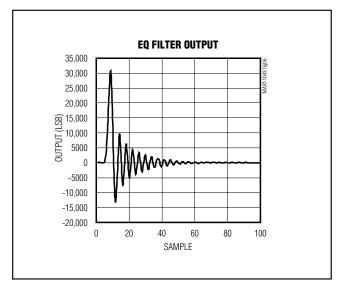

#### Equalizer (EQ)

The EQ matches the frequency/gain characteristics of CW-chirp radar systems where the distance to the target is proportional to the measured frequency. Distant targets not only have a higher frequency, they have a weaker signal. Hence, higher frequencies need more amplification than lower frequencies. The EQ provides gain proportional to frequencies up to 190kHz, at which point the gain rolls off at 80dB/decade.

The EQ consists of an analog section in the PGA and a digital EQ created from the biquad filters. The analog EQ (PGA) provides 20dB/decade of gain and the default digital EQ provides an additional 20dB/decade of gain. Together they provide 40dB/decade of gain up to 190kHz with a gain of 0dB at 5kHz.

Variations in the manufacturing process affect the gain and phase of the analog filter. Compensation for these variations include adjustments to the digital filter during the manufacture of the MAX11043. Use the analog and digital EQs together for optimal performance.

#### **Conversion and ADC Reading**

Drive CONVRUN high to initiate a continuous conversion on all 4 channels. Keep CONVRUN high for the entire conversion process. Do not pulse CONVRUN. EOC asserts low when new data is available. Initiate a data read prior to the next rising edge of EOC or the result is overwritten. EOC asserts high upon read completion of all active channels. Use ConfigA, ConfigB, ConfigC, and ConfigD registers to read single channel data. Concatenated data is available in the ADCAB, ADCCD, and ADCABCD registers. Use concatenated registers to ensure simultaneous results are read. See the *Register Functions* section for more details.

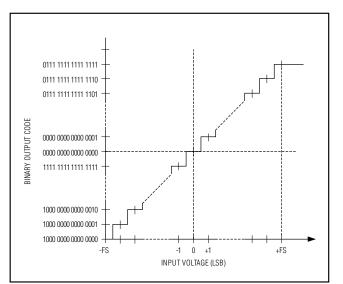

A software-selectable scan mode automatically sends the result from selected channels following the  $\overline{CS}$ falling edge and allows other registers to be simultaneously updated. To enable scan mode, set SCHAN\_ bits high. See the *Configuration Register (08h)* section for a detailed description. The ADC output is presented in two's complement format (Figure 3).

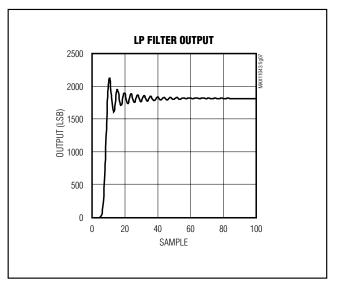

#### Digital Filter

Seven cascaded, individually configurable, 2nd-order filter elements make up the digital filter. Figure 4 shows the structure of a single filter section. Configure these elements as LP, BP, HP, or all pass (AP) filters with optional rectification. Filter configuration is transferred from the flash to coefficient RAM (C-RAM) on power-up. Store custom filters permanently in the flash or write directly to C-RAM each time on power-up. Two separate sets of programmable coefficients exist for each filter. Dual coefficient sets allow rapid filter reconfiguration. These filter coefficients are programmed to LP and EQ modes at the factory. Multiple flash memory pages exist so that custom filters can be created while preserving factory-programmed filter coefficients.

Figure 2. Sinc 5 Filter Frequency Response

Figure 3. Two's Complement Transfer Function

# **4-Channel, 16-Bit, Simultaneous-Sampling ADCs with PGA, Filter, and 8-/12-Bit Dual-Stage DAC**

Filter coefficients A1 and B1 are always 1. B3 is limited to -1, 0, and 1.

Filter coefficients A2, A3, and B2 are stored as 16-bit two's complement values in the range of -4 to +4. Filter coefficients A2 and A3 are stored as -A2 and -A3.

Gain is limited to the following values 2<sup>4</sup>, 2<sup>2</sup>, 2<sup>0</sup>, 2<sup>-2</sup>, 2<sup>-4</sup>, 2<sup>-6</sup>, 2<sup>-8</sup>, and 2<sup>-10</sup>. For better gain resolution, adjust the

Figure 4. Single Programmable 2nd-Order Filter Section

#### **Table 1. Default Filter Coefficients**

Fine Gain A/B/C/D Registers at the input of each filter set. Fine gain adjustment has a resolution of 16 bits and a gain range of -4 to +4. Set the RECT bit to rectify the filter output.

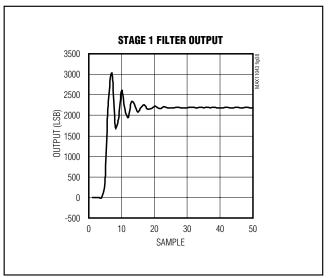

Figures 5–8 show the response to a step input of the default filters used for ADC trimming.

Figure 5. Sinc 5 Filter Response to a Step Input

|       | DEFAULT LOWPASS FILTER COEFFICIENTS |             |               |              |              |              |      |  |  |  |  |

|-------|-------------------------------------|-------------|---------------|--------------|--------------|--------------|------|--|--|--|--|

| STAGE | B1                                  | B2          | B3            | A1           | A2           | A3           | GAIN |  |  |  |  |

| 1     | 1                                   | + 2.0 (typ) | +1.0000       | 1            | +0.468 (typ) | +0.607 (typ) | +0   |  |  |  |  |

| 2     | 1                                   | +1.9509     | +1.0000       | 1            | +0.6874      | +0.1317      | -2   |  |  |  |  |

| 3     | 1                                   | +1.6139     | +1.0000       | 1            | +0.5936      | +0.2015      | -2   |  |  |  |  |

| 4     | 1                                   | +1.1488     | +1.0000       | 1            | +0.4395      | +0.3258      | +0   |  |  |  |  |

| 5     | 1                                   | +0.7415     | +1.0000       | 1            | +0.2715      | +0.4851      | +0   |  |  |  |  |

| 6     | 1                                   | +0.4651     | +1.0000       | 1            | +0.1310      | +0.6685      | +0   |  |  |  |  |

| 7     | 1                                   | +0.3296     | +1.0000       | 1            | +0.0493      | +0.8788      | +0   |  |  |  |  |

|       |                                     | DEI         | FAULT EQUALIZ | ZER COEFFICI | ENTS         |              |      |  |  |  |  |

| STAGE | B1                                  | B2          | B3            | A1           | A2           | A3           | GAIN |  |  |  |  |

| 1     | 1                                   | + 2.0 (typ) | +1.0000       | 1            | +0.468 (typ) | +0.607 (typ) | +0   |  |  |  |  |

| 2     | 1                                   | +1.9401     | +1.0000       | 1            | +0.6886      | +0.1359      | +0   |  |  |  |  |

| 3     | 1                                   | +1.5458     | +1.0000       | 1            | +0.5803      | +0.2275      | -2   |  |  |  |  |

| 4     | 1                                   | +1.0518     | +1.0000       | 1            | +0.4139      | +0.3887      | +0   |  |  |  |  |

| 5     | 1                                   | +0.6785     | +1.0000       | 1            | +0.2563      | +0.5966      | +0   |  |  |  |  |

| 6     | 1                                   | -1.0000     | +0.0000       | 1            | +0.0039      | -0.0000      | +4   |  |  |  |  |

| 7     | 1                                   | +0.4902     | +1.0000       | 1            | +0.1649      | +0.8489      | +2   |  |  |  |  |

## 4-Channel, 16-Bit, Simultaneous-Sampling ADCs with PGA, Filter, and 8-/12-Bit Dual-Stage DAC

#### Programmable Gain Amplifier

Each ADC channel features an input buffer with input impedance of at least  $5k\Omega$  and programmable gain of eight or 16. When set to a gain of one, the signal bypasses the PGA to reduce noise.

The PGA features an optional 20dB/decade analog EQ mode, with a gain of 0dB near 8kHz and attenuation above 190kHz to reduce out-of-band noise. Using the digital EQ filter adds another 20dB/decade of gain and sets the 0dB frequency to 5kHz. Control the EQ and PGA gain from their respective CONFIG\_ registers. For additional filtering and equalization, use the integrated digital filters.

#### **Digital-to-Analog Converter**

The MAX11043 features a 12-bit fine DAC with high and low reference inputs set by the 8-bit, dual tap coarse DAC or driven externally. The output buffer of the fine DAC has a gain of two and can drive  $10k\Omega$  and 200pF in parallel. Bypass the REFDACH and REFDACL with a 1µF capacitor when using the coarse DAC to set the reference values, or power down the buffers and drive REFDACH and REFDACL with external references. Alternatively drive one of the fine DAC references using the coarse DAC and the other using an external reference.

The fine DAC register contains the current value of the output. The output value changes by writing to this register or by the rising edge of the DACSTEP input. The DAC register updates on the next rising edge of the system clock following the rising edge of the DACSTEP input. The programmable DACSTEP register contains

Figure 6. EQ Filter Response to a Step Input

the step size. The UP/DWN input sets the direction of the step. Drive UP/DWN high to step up, drive low to step down.

The coarse 8-bit, dual tap DAC generates the high and low reference values for the fine DAC. Obtain the coarse DAC reference from the main reference or by driving the REFDAC input externally. The main reference, REFBP, is divided by two before the coarse DAC. When driving REFDAC, REFDACH, or REFDACL directly, ensure the voltage to the fine DAC does not exceed AVDD/2 to prevent the output amplifier from saturating.

Figure 7. LP Filter Response to a Step Input

Figure 8. Stage 1 Default Filter Response to a Step Input

## **4-Channel, 16-Bit, Simultaneous-Sampling ADCs** with PGA, Filter, and 8-/12-Bit Dual-Stage DAC

#### **Reference (REFBP)**

The MAX11043 features an internal 2.5V bandgap reference. Bypass REFBP with a 1 $\mu$ F capacitor or power down the buffer amplifier and drive REFBP with an external reference. In internal reference mode, REFBP provides the main reference voltage for the MAX11043.

Refer to <u>www.maximintegrated.com/references</u> for a list of available precision references.

In addition to the integrated main reference, there are seven separate references derived from REFBP, one for each ADC channel, one for the coarse DAC, and two (one high and one low) for the fine DAC. When using the main reference, bypass each of the references with a 1 $\mu$ F capacitor or set the appropriate bits (7–0), in the reference (10h) register, to power down the references and drive externally. Use external references capable of driving a 700 $\mu$ A or total load.

**Clock Sources** The MAX11043 features an internal 16MHz oscillator that supports either an external crystal or ceramic resonator. For highest performance, set bit 15 in the configuration register to 1 and use an external clock (EX clock) source, up to 40MHz, to drive OSCIN. A programmable clock divider divides the EX clock by 2, 3, 4, or 6 to generate the ADC sample clock. The system clock, used for all digital timing, is twice the ADC sample clock. Ensure that the minimum EX clock high or low time is greater than 25ns when using the divide-by-2 or divide-by-3 mode. The system clock, used for all internal timing, is derived from the clock divider setting and the input clock.

For optimal performance, derive the SPI clock and system clock from the same source.

#### **Power Saving**

The MAX11043 features an active-high power-down input, as well as an SPI-controlled power-down bit that places the MAX11043 in low-power mode. In addition, the MAX11043 features an independent, SPI-controlled, power-down for each ADC channel, the DAC, and the oscillator. See the *Configuration Register (08h)* section for more details.

#### **Serial Communication**

The SPI-compatible interface allows synchronous serial data transfers up to 40Mbps. The bandwidth is divided between the DACs and the ADC. Maximum conversion throughput depends on which read commands are used. The highest conversion rates are obtained by using the scan mode. The second highest rate is obtained by reading concatenated registers. The slowest method is to read the results individually.

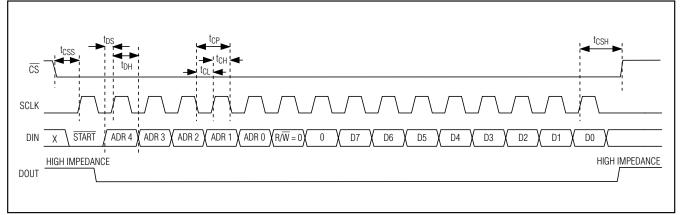

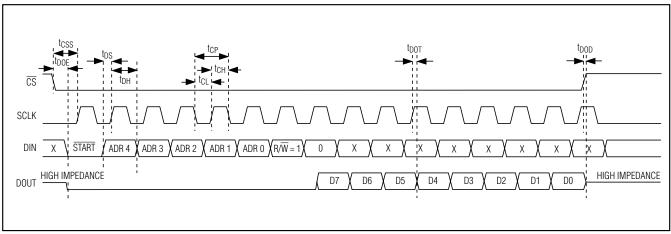

Configure the SPI master for SCLK to idle low (SCLK is low when  $\overline{CS}$  is asserted). The data at DIN is latched on the rising edge of SCLK. Data at DOUT transitions immediately after the rising edge of SCLK.

All SPI transactions start with a command byte. The command byte selects the address of the register and the mode of operation (read/write).

#### **SPI Command Byte**

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| START | ADR4  | ADR3  | ADR2  | ADR1  | ADR0  | R/W   | 0     |

**START**<**7>:** Start bit. This bit must be 0 for normal operation.

**ADR\_<6:2>:** Device register address bits. See the register map in Table 2.

**R/W**<1>: Read/write bit. 1 = read from device. 0 = write to device.

# 4-Channel, 16-Bit, Simultaneous-Sampling ADCs with PGA, Filter, and 8-/12-Bit Dual-Stage DAC

Figure 9. SPI 8-Bit Write Operation

Figure 10. SPI 8-Bit Read Operation

# **4-Channel, 16-Bit, Simultaneous-Sampling ADCs with PGA, Filter, and 8-/12-Bit Dual-Stage DAC**

#### **Register Map**

| ADDRESS | REGISTER NAME               | FUNCTION                                                                                                                  | BITS  |

|---------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------|-------|

| 00h     | ADCA                        | ADC channel A result register                                                                                             | 16/24 |

| 01h     | ADCB                        | ADC channel B result register                                                                                             | 16/24 |

| 02h     | ADCC                        | ADC channel C result register                                                                                             | 16/24 |

| 03h     | ADCD                        | ADC channel D result register                                                                                             | 16/24 |

| 04h     | ADCAB                       | ADC channels A and B results register                                                                                     | 32/48 |

| 05h     | ADCCD                       | ADC channels C and D results register                                                                                     | 32/48 |

| 06h     | ADCABCD                     | ADC channels A, B, C, and D results register                                                                              | 64/96 |

| 07h     | Status                      | Status register                                                                                                           | 8     |

| 08h     | Configuration               | Configures the device                                                                                                     | 16    |

| 09h     | DAC                         | Fine DAC value                                                                                                            | 16    |

| 0Ah     | DACSTEP                     | Step size for DAC increment/decrement function                                                                            | 16    |

| 0Bh     | DACH/DACL                   | High and low coarse DAC values                                                                                            | 8 + 8 |

| 0Ch     | ConfigA                     | ADC channel A configuration                                                                                               | 16    |

| 0Dh     | ConfigB                     | ADC channel B configuration                                                                                               | 16    |

| 0Eh     | ConfigC                     | ADC channel C configuration                                                                                               | 16    |

| 0Fh     | ConfigD                     | ADC channel D configuration                                                                                               | 16    |

| 10h     | Reference/Delay             | Sets the operation state of the reference and buffers                                                                     | 16    |

| 11h     | AGain                       | Channel A fine gain                                                                                                       | 16    |

| 12h     | BGain                       | Channel B fine gain                                                                                                       | 16    |

| 13h     | CGain                       | Channel C fine gain                                                                                                       | 16    |

| 14h     | DGain                       | Channel D fine gain                                                                                                       | 16    |

| 15h     | Filter coefficient address  | Selects the filter coefficient to read or write. This autoincrements each time the coefficient data register is accessed. | 8     |

| 16h     | Filter coefficient data out | Coefficient RAMs output data                                                                                              | 32    |

| 17h     | Filter coefficient data in  | Filter coefficient data                                                                                                   | 32    |

| 18h     | Flash mode                  | Flash mode selection register                                                                                             | 8     |

| 19h     | Flash addr                  | Flash address register                                                                                                    | 16    |

| 1Ah     | Flash data in               | Flash data in register                                                                                                    | 16    |

| 1Bh     | Flash data out              | Flash data out register                                                                                                   | 16    |

| 1Ch     | Reserved                    | _                                                                                                                         |       |

| 1Dh     | Reserved                    | _                                                                                                                         |       |

| 1Eh     | Reserved                    | _                                                                                                                         |       |

| 1Fh     | Reserved                    | _                                                                                                                         |       |

## Table 2. SPI Register Map

## 4-Channel, 16-Bit, Simultaneous-Sampling ADCs with PGA, Filter, and 8-/12-Bit Dual-Stage DAC

#### **Register Functions** ADCA, ADCB, ADCC, and ADCD Result Registers (00h–03h)

The ADC channel A, B, C, and D result registers provide the result data from the 4 ADC channels. EOC asserts low when new data is available. Initiate a data read prior to the next rising edge of EOC or the result is overwritten. Set bit 5 of the configuration register 08h high to read the data out in 24-bit resolution or set bit 5 low to read the data out in 16-bit resolution.

#### ADCAB, ADCCD, and ADCABCD Result Registers (04h–06h)

Registers ADCAB, ADCCD, and ADCABCD contain concatenated ADC results ensuring simultaneous results are read. This reduces the risk of reading samples delayed by one cycle from channel to channel.

Set bit 5 of the configuration register 08h high to read the data out in 24-bit resolution or set bit 5 low to read the data out in 16-bit resolution.

### Status Register (07h)

| BIT 7 | BIT 6 | BIT 5      | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|------------|-------|-------|-------|-------|-------|

| X     | X     | Flash Busy | BOOT  | OFLGA | OFLGB | OFLGC | OFLGD |

The status register contains the channel overflow flags and POR bits.

**BOOT<4>:** Power-on reset flag.

**OFLG\_<3:0>:** Channel overflow flag, one per channel.

X<7:6>: Don't-care bits.

**Flash Busy<5>:** Do not start a new flash operation until this is 0.

#### **Configuration Register (08h)**

| BIT 15 | BIT 14  | BIT 13  | BIT 12 | BIT 11 | BIT 10 | BIT 9 | BIT 8 |

|--------|---------|---------|--------|--------|--------|-------|-------|

| EXTCLK | CLKDIV1 | CLKDIV0 | PD     | PDA    | PDB    | PDC   | PDD   |

| BIT 7 | BIT 6 | BIT 5 | BIT 4  | BIT 3  | BIT 2  | BIT 1  | BIT 0  |

|-------|-------|-------|--------|--------|--------|--------|--------|

| PDDAC | PDOSC | 24BIT | SCHANA | SCHANB | SCHANC | SCHAND | DECSEL |

EXTCLK<15>: External clock select.

1 = logic-level clock supplied on OSCIN.

0 = crystal or resonator connected between OSCIN and OSCOUT (default).

**CLKDIV1:CLKDIV0<14:13>:** Clock divider ratio (EX clock : ADC sample clock).

00 = 1:2 clock divider.

01 = 1:3 clock divider.

10 = 1:4 clock divider.

11 = 1:6 clock divider (default).

**PD<12>:** Power-down analog circuitry (reference and SPI interface remains active).

1 = low-power mode.

0 = normal operation (default).

**PD\_<11:8>:** ADC power-down for each channel (A, B, C, and D).

1 = powers down analog signal path.

0 = normal operation (default).

PDDAC< 7>: DAC power-down.

1 = fine DAC buffer powered down.

0 = normal operation (default).

PDOSC<6>: Oscillator power-down.

1 = oscillator powered down (disconnects EX clock in EX clock mode).

0 = normal operation (default).

24BIT<5>: ADC output data format.

1 = ADC data output as 24 bits.

0 = ADC data output as 16 bits (default).

Use the 24-bit ADC output in conjunction with external digital filtering to improve signal-to-noise ratio.

# **4-Channel, 16-Bit, Simultaneous-Sampling ADCs** with PGA, Filter, and 8-/12-Bit Dual-Stage DAC

**SCHAN\_<4:1>:** Automatic ADC result output for each channel (A, B, C, and D).

1 = ADC channel data is output on DOUT each time a new result is valid in the sequence, A, B, C, and D.

0 = ADC data is not presented automatically for this channel (default).

When SCHAN\_ = 1, the selected ADC channel data is automatically presented on DOUT each time  $\overline{EOC}$ asserts low in the sequence A, B, C, and D with the unselected channels omitted. The data transitions on the rising edge of SCLK. Force  $\overline{CS}$  low to initiate transmission.  $\overline{CS}$  can go high between results. The MSB of the first selected ADC channel outputs immediately after the falling edge of EOC. EOC goes high after the last bit of the selected channels clocks out or one clock cycle before the next result is ready. Insufficient SCLK pulses result in truncated data. Extra clock pulses give an undefined output. In scan mode, keep DIN high or write data to the MAX11043 as usual. In scan mode, the MAX11043 ignores requests for data reads.

DECSEL<0>: Decimate select.

1 = decimate by 12.

0 = decimate by 24 (default).

Set DECSEL high to decimate the ADC result by 12, doubling the number of samples. The SPI interface is limited to 40Mbps.

### Fine DAC Register (09h)

| BIT 15 | BIT 14 | BIT 13 | BIT 12 | BIT 11 | BIT 10 | BIT 9 | BIT 8 |

|--------|--------|--------|--------|--------|--------|-------|-------|

| Х      | Х      | Х      | Х      | DAC11  | DAC10  | DAC9  | DAC8  |

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| DAC7  | DAC6  | DAC5  | DAC4  | DAC3  | DAC2  | DAC1  | DAC0  |

X<15:12>: Don't-care bits.

**DAC\_<11:0>:** Contains current fine DAC output value. When using the DACSTEP input to change the DAC

value, this register updates to the new value on the next rising edge of the system clock following the rising edge of DACSTEP. The power-on default is 0.

#### DACSTEP Register (0Ah)

| BIT 15 | BIT 14 | BIT 13 | BIT 12 | BIT 11    | BIT 10    | BIT 9    | BIT 8    |

|--------|--------|--------|--------|-----------|-----------|----------|----------|

| Х      | Х      | Х      | Х      | DACSTEP11 | DACSTEP10 | DACSTEP9 | DACSTEP8 |

| BIT 7    | BIT 6    | BIT 5    | BIT 4    | BIT 3    | BIT 2    | BIT 1    | BIT 0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| DACSTEP7 | DACSTEP6 | DACSTEP5 | DACSTEP4 | DACSTEP3 | DACSTEP2 | DACSTEP1 | DACSTEP0 |

#### X<15:12>: Don't-care bits.

**DACSTEP11:DACSTEP0<11:0>:** Provides the size of the DAC step. The value is positive only and the UP/DWN input is used to set the direction. The value in

the fine DAC register updates on the next rising edge of the system clock following the rising edge of the DACSTEP input. The power-on default is 0.

#### Coarse DACH/DACL Register (0Bh)

| BIT 15 | BIT 14 | BIT 13 | BIT 12 | BIT 11 | BIT 10 | BIT 9 | BIT 8 |

|--------|--------|--------|--------|--------|--------|-------|-------|

| DACH7  | DACH6  | DACH5  | DACH4  | DACH3  | DACH2  | DACH1 | DACH0 |

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| DACL7 | DACL6 | DACL5 | DACL4 | DACL3 | DACL2 | DACL1 | DACLO |

DACH7:DACH0<15:8>: High coarse DAC value. DACL7:DACL0<7:0>: Low coarse DAC value. Coarse DAC sets high and low references for the fine DAC. The power-on default is 0.

# 4-Channel, 16-Bit, Simultaneous-Sampling ADCs with PGA, Filter, and 8-/12-Bit Dual-Stage DAC

| BIT 15                                                                                                                                                                                                                                                                                             | BIT 14                                                                                                                                                        | BIT 13 | BIT 12 | BIT 11                                                                                                                                                                                                                      | BIT 10                                                                                                                                                                                | BIT 9                                                                                         | BIT 8        |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------|--|--|--|

| Х                                                                                                                                                                                                                                                                                                  | Х                                                                                                                                                             | Х      | BDAC3  | BDAC2                                                                                                                                                                                                                       | BDAC1                                                                                                                                                                                 | BDAC0                                                                                         | DIFF         |  |  |  |

|                                                                                                                                                                                                                                                                                                    |                                                                                                                                                               |        |        |                                                                                                                                                                                                                             |                                                                                                                                                                                       |                                                                                               |              |  |  |  |