OBSOLETE PRODUCT

POSSIBLE SUBSTITUTE PRODUCT

INTERSIL PART NUMBER HI1175

March 2003

FN4711.1

## 8-Bit, 20MSPS, Flash A/D Converter

The HI5675 is an 8-bit, analog-to-digital converter built in an advanced CMOS process. The low power, low differential gain and phase, high sampling rate, and single 5V supply make the HI5675 ideal for video and imaging applications.

The adoption of a 2-step flash architecture achieves low power consumption (60mW) at a maximum conversion speed of 20MSPS with only a 2.5 clock cycle data latency. The HI5675 also features digital output enable/disable and a built in voltage reference. The HI5675 can be configured to use the internal reference or an external reference if higher precision is required.

#### Part Number Information

| PART NUMBER | TEMP.<br>RANGE (°C) | PACKAGE    | PKG. NO. |  |

|-------------|---------------------|------------|----------|--|

| HI5675JCB   | -40 to 85           | 24 Ld SOIC | M24.2-S  |  |

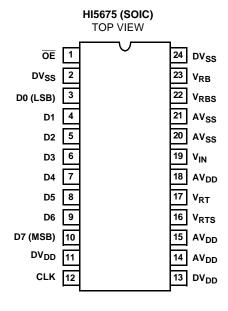

#### **Pinout**

#### **Features**

| • Resolution                                         | 8-Bit ±0.3 LSB (DNL) |

|------------------------------------------------------|----------------------|

| Maximum Sampling Frequency .                         | 20MSPS               |

| • Low Power Consumption (Reference Current Excluded) | 60mW                 |

- · Built-In Sample and Hold Circuit

- · Built-In Reference Voltage Self Bias Circuit

- Three-State TTL Compatible Output

- Single +5V Power Supply

- Low Cost

- Direct Replacement for TLC5510 and ADC1175

## **Applications**

- Video Digitizing

- PC Video Capture

- · Image Scanners

- TV Set Top Boxes

- Multimedia

- Personal Communication Systems (PCS)

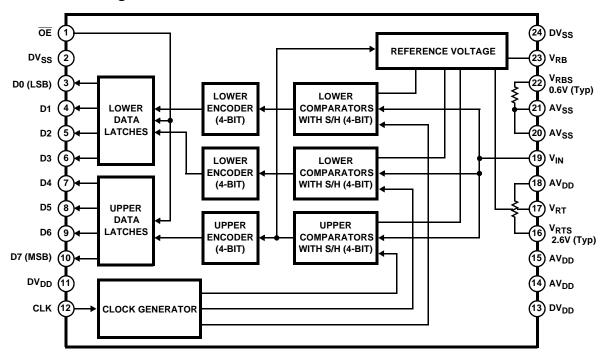

# Functional Block Diagram

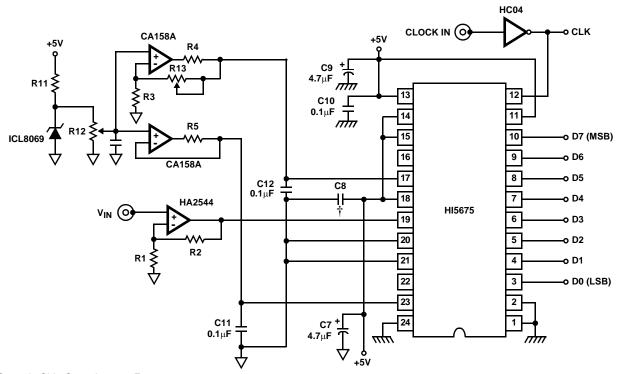

# **Typical Application Schematic**

$\ensuremath{^{\dagger}}$  : Ceramic Chip Capacitor  $0.1 \mu F$

: Analog GND

NOTE: It is necessary that  $AV_{DD}$  and  $DV_{DD}$  pins be driven from the same supply. The gain of analog input signal can be changed by adjusting the ratio of R2 to R1.

# HI5675

# Pin Descriptions

| PIN<br>NUMBER | SYMBOL           | DESCRIPTION                                                                                           |

|---------------|------------------|-------------------------------------------------------------------------------------------------------|

| 1             | ŌĒ               | When $\overline{OE}$ = Low, Data is valid. When $\overline{OE}$ = High, D0 to D7 pins high impedance. |

| 2, 24         | DV <sub>SS</sub> | Digital GND.                                                                                          |

| 3-10          | D0 to D7         | D0 (LSB) to D7 (MSB) Output.                                                                          |

| 11, 13        | DV <sub>DD</sub> | Digital +5V. (Connect to AV <sub>DD</sub> to avoid Latchup).                                          |

| 12            | CLK              | Clock Input.                                                                                          |

| 16            | V <sub>RTS</sub> | Shorted with V <sub>RT</sub> generates, +2.6V.                                                        |

| 17            | V <sub>RT</sub>  | Reference Voltage (Top).                                                                              |

| 23            | V <sub>RB</sub>  | Reference Voltage (Bottom).                                                                           |

| 14, 15, 18    | AV <sub>DD</sub> | Analog +5V. Digital +5V. (Connect to DV <sub>DD</sub> to avoid Latchup).                              |

| 19            | V <sub>IN</sub>  | Analog Input.                                                                                         |

| 20, 21        | AV <sub>SS</sub> | Analog GND.                                                                                           |

| 22            | V <sub>RBS</sub> | Shorted with V <sub>RB</sub> generates +0.6V.                                                         |

### **Absolute Maximum Ratings**

| Supply Voltage, V <sub>DD</sub>                           | 7V                                                         |

|-----------------------------------------------------------|------------------------------------------------------------|

| Reference Voltage, V <sub>RT</sub> , V <sub>RB</sub>      | $V_{\mbox{\scriptsize DD}}$ to $V_{\mbox{\scriptsize SS}}$ |

| Analog Input Voltage, V <sub>IN</sub>                     | $V_{DD}$ to $V_{SS}$                                       |

| Digital Input Voltage, CLK                                | $V_{DD}$ to $V_{SS}$                                       |

| Digital Output Voltage, V <sub>OH</sub> , V <sub>OL</sub> | $V_{DD}$ to $V_{SS}$                                       |

#### **Operating Conditions** (Note 1)

| operating contained (note )                                                                                        |

|--------------------------------------------------------------------------------------------------------------------|

| Temperature Range, T <sub>A</sub> 40°C to 85°C                                                                     |

| Supply Voltage                                                                                                     |

| $AV_{DD}$ , $AV_{SS}$ , $DV_{DD}$ , $DV_{SS}$ +4.75V to +5.25V                                                     |

| DGND-AGND 0mV to 100m\                                                                                             |

| Reference Input Voltage                                                                                            |

| V <sub>RB</sub> 0V and Above                                                                                       |

| V <sub>RT</sub> 2.8V and Below                                                                                     |

| Analog Input Range, V <sub>IN</sub> V <sub>RB</sub> to V <sub>RT</sub> (1.8V <sub>P-P</sub> to 2.8V <sub>P-P</sub> |

| Clock Pulse Width                                                                                                  |

| t <sub>PW1</sub>                                                                                                   |

| t <sub>PW0</sub>                                                                                                   |

|                                                                                                                    |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)                   | $\theta_{JA}$ (°C/W)                 |

|--------------------------------------------------------|--------------------------------------|

| SOIC Package                                           | 98                                   |

| Maximum Junction Temperature                           | 150°C                                |

| Maximum Storage Temperature Range, T <sub>STG</sub> 65 | <sup>o</sup> C to 150 <sup>o</sup> C |

| Maximum Lead Temperature (Soldering 10s)               |                                      |

| (SOIC - Lead Tips Only)                                |                                      |

#### **Die Characteristics**

| Die | Size: | <br> | <br> | <br>. 2.23 x 2.24mr |

|-----|-------|------|------|---------------------|

|     |       |      |      |                     |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1.  $\theta_{\mbox{\scriptsize JA}}$  is measured with the component mounted on an evaluation PC board in free air.

$\textbf{Electrical Specifications} \quad \text{ f}_{C} = \text{20MSPS, AV}_{DD} = \text{DV}_{DD} = \text{5V, V}_{RB} = \text{0.5V, V}_{RT} = \text{2.5V, T}_{A} = \text{25}^{o}\text{C (Note 1)}$

| PARAMETER                                                          | TEST CONDITIONS                                 | MIN | TYP  | MAX  | UNIT   |

|--------------------------------------------------------------------|-------------------------------------------------|-----|------|------|--------|

| SYSTEM PERFORMANCE                                                 |                                                 | •   | •    | '    |        |

| Offset Voltage                                                     |                                                 |     |      |      |        |

| E <sub>OT</sub>                                                    |                                                 | -60 | -35  | -10  | mV     |

| E <sub>OB</sub>                                                    |                                                 | 0   | +15  | +45  | mV     |

| Integral Non-Linearity, INL                                        | $f_C = 20MSPS$ , $V_{IN} = 0.6V$ to 2.6V        | -   | ±0.5 | ±1.3 | LSB    |

| Differential Non-Linearity, DNL                                    | $f_C = 20MSPS$ , $V_{IN} = 0.6V$ to 2.6V        | -   | ±0.3 | ±0.5 | LSB    |

| DYNAMIC CHARACTERISTICS                                            |                                                 | '   |      |      |        |

| Effective Number of Bits, ENOB                                     | f <sub>IN</sub> = 1MHz                          | -   | 7.6  | -    | Bits   |

| Spurious Free Dynamic Range                                        | f <sub>IN</sub> = 1MHz                          | -   | 51   | -    | dB     |

| Signal to Noise Ratio, SINAD                                       | $f_C = 20MHz$ , $f_{IN} = 1MHz$                 | -   | 46   | -    | dB     |

| $= \frac{\text{RMS Signal}}{\text{RMS Noise} + \text{Distortion}}$ | $f_C = 20MHz$ , $f_{IN} = 3.58MHz$              | -   | 46   | -    | dB     |

| Maximum Conversion Speed, f <sub>C</sub>                           | $V_{IN} = 0.6V$ to 2.6V, $f_{IN} = 1kHz$ Ramp   | 20  | -    | -    | MSPS   |

| Minimum Conversion Speed                                           |                                                 | -   | -    | 0.5  | MSPS   |

| Differential Gain Error, DG                                        | NTSC 40 IRE Mod Ramp, f <sub>C</sub> = 14.3MSPS | -   | 1.0  | -    | %      |

| Differential Phase Error, DP                                       |                                                 | -   | 0.5  | -    | Degree |

| Aperture Jitter, t <sub>AJ</sub>                                   |                                                 | -   | 30   | -    | ps     |

| Sampling Delay, t <sub>DS</sub>                                    |                                                 | -   | 4    | -    | ns     |

| Data Latency, t <sub>LAT</sub>                                     |                                                 | -   | -    | 2.5  | Cycles |

| ANALOG INPUTS                                                      | ,                                               | 1   | ч    | ı    |        |

| Analog Input Bandwidth (-1dB), BW                                  |                                                 | -   | 18   | -    | MHz    |

| Analog Input Capacitance, C <sub>IN</sub>                          | $V_{IN} = 1.5V + 0.07V_{RMS}$                   | -   | 11   | -    | pF     |

$\textbf{Electrical Specifications} \quad \text{$f_{C}$ = $20MSPS, $AV_{DD}$ = $DV_{DD}$ = $5V$, $V_{RB}$ = $0.5V$, $V_{RT}$ = $2.5V$, $T_{A}$ = $25^{\circ}C$ (Note 1) $ (\textbf{Continued})$ }$

| PARAMETER                                                                    | TEST CONI                                            | MIN                      | TYP  | MAX  | UNIT |    |

|------------------------------------------------------------------------------|------------------------------------------------------|--------------------------|------|------|------|----|

| REFERENCE INPUT                                                              |                                                      |                          |      |      |      | ,  |

| Reference Pin Current, I <sub>REF</sub>                                      |                                                      |                          | 4.5  | 6.6  | 8.7  | mA |

| Reference Resistance (V <sub>RT</sub> to V <sub>RB</sub> ), R <sub>REF</sub> |                                                      |                          | 230  | 300  | 450  | Ω  |

| INTERNAL VOLTAGE REFERENCE                                                   |                                                      |                          |      |      |      |    |

| Self Bias Mode 1                                                             |                                                      |                          |      |      |      |    |

| $V_{RB}$                                                                     | Short V <sub>RB</sub> and V <sub>RBS</sub> , Short V | $_{RT}$ and $V_{RTS}$    | 0.60 | 0.64 | 0.68 | V  |

| V <sub>RT</sub> - V <sub>RB</sub>                                            |                                                      |                          | 1.96 | 2.09 | 2.21 | V  |

| Self Bias Mode 2, V <sub>RT</sub>                                            | V <sub>RB</sub> = AGND, Short V <sub>RT</sub> and    | V <sub>RTS</sub>         | 2.25 | 2.39 | 2.53 | V  |

| DIGITAL INPUTS                                                               |                                                      |                          |      |      |      |    |

| Digital Input Voltage                                                        |                                                      |                          |      |      |      |    |

| V <sub>IH</sub>                                                              |                                                      |                          | 4.0  | -    | -    | V  |

| V <sub>IL</sub>                                                              |                                                      |                          | -    | -    | 1.0  | V  |

| Digital Input Current                                                        |                                                      |                          |      |      |      |    |

| _IIH                                                                         | V <sub>DD</sub> = Max                                | $V_{IH} = V_{DD}$        | -    | -    | 5    | μΑ |

| I <sub>IL</sub>                                                              |                                                      | $V_{IL} = 0V$            | -    | -    | 5    | μА |

| DIGITAL OUTPUTS                                                              |                                                      |                          |      |      |      |    |

| Digital Output Current                                                       |                                                      |                          |      |      |      |    |

| Гон                                                                          | $\overline{OE} = V_{SS}, V_{DD} = Min$               | $V_{OH} = V_{DD} - 0.5V$ | -1.1 | -    | -    | mA |

| I <sub>OL</sub>                                                              |                                                      | $V_{OL} = 0.4V$          | 3.7  | -    | -    | mA |

| Digital Output Current                                                       |                                                      |                          |      |      |      |    |

| I <sub>OZH</sub>                                                             | $\overline{OE} = V_{DD}, V_{DD} = Max$               | $V_{OH} = V_{DD}$        | -    | 0.01 | 16   | μΑ |

| I <sub>OZL</sub>                                                             |                                                      | -                        | 0.01 | 16   | μΑ   |    |

| TIMING CHARACTERISTICS                                                       |                                                      |                          |      |      |      |    |

| Output Data Delay, t <sub>DL</sub>                                           |                                                      |                          | -    | 18   | 30   | ns |

| POWER SUPPLY CHARACTERISTIC                                                  |                                                      |                          |      | -    |      | ,  |

| Supply Current, I <sub>DD</sub>                                              | f <sub>C</sub> = 20MSPS, NTSC Ramp W                 | ave Input                | -    | 12   | 17   | mA |

| NOTE:                                                                        |                                                      |                          | 1    | 1    | 1    |    |

#### NOTE:

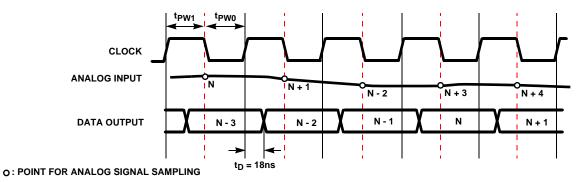

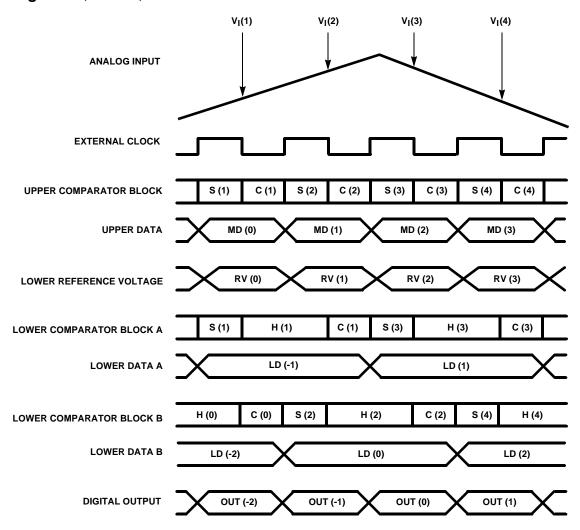

# **Timing Diagrams**

FIGURE 1.

<sup>2.</sup> Electrical specifications guaranteed only under the stated operating conditions.

## Timing Diagrams (Continued)

FIGURE 2.

TABLE 1. A/D OUTPUT CODE TABLE

| INPUT SIGNAL    |      | DIGITAL OUTPUT CODE |    |    |    |    |    |    |     |

|-----------------|------|---------------------|----|----|----|----|----|----|-----|

| VOLTAGE         | STEP | MSB                 | D6 | D5 | D4 | D3 | D2 | D1 | LSB |

| V <sub>RT</sub> | 255  | 1                   | 1  | 1  | 1  | 1  | 1  | 1  | 1   |

|                 | •    |                     |    |    |    | •  |    |    |     |

| •               | •    |                     |    |    |    | •  |    |    |     |

| •               | •    |                     |    |    |    | •  |    |    |     |

| •               | 128  | 1                   | 0  | 0  | 0  | 0  | 0  | 0  | 0   |

| •               | 127  | 0                   | 1  | 1  | 1  | 1  | 1  | 1  | 1   |

| •               | •    |                     |    |    |    | •  |    |    |     |

| •               | •    |                     |    |    |    | •  |    |    |     |

|                 | •    |                     |    |    |    | •  |    |    |     |

| $V_{RB}$        | 0    | 0                   | 0  | 0  | 0  | 0  | 0  | 0  | 0   |

## **Detailed Description**

The HI5675 is a 2-step A/D converter featuring a 4-bit upper comparator group and two lower comparator groups of 4 bits each. The reference voltage can be obtained from the onboard bias generator or be supplied externally. This IC uses an offset canceling type comparator that operates synchronously with an external clock. The operating modes of the part are input sampling (S), hold (H), and compare (C).

The operation of the part is illustrated in Figure 2. A reference voltage that is between V<sub>RT</sub> -V<sub>RB</sub> is constantly applied to the upper 4-bit comparator group. VI(1) is sampled with the falling edge of the first clock by the upper comparator block. The lower block A also samples VI(1) on the same edge. The upper comparator block finalizes comparison data MD(1) with the rising edge of the first clock. Simultaneously the reference supply generates a reference voltage RV(1) that corresponds to the upper results and applies it to the lower comparator block A. The lower comparator block finalizes comparison data LD(1) with the rising edge of the second clock. MD(1) and LD(1) are combined and output as OUT(1) with the rising edge of the third clock. There is a 2.5 cycle clock delay from the analog input sampling point to the corresponding digital output data. Notice how the lower comparator blocks A and B alternate generating the lower data in order to increase the overall A/D sampling rate.

#### Power, Grounding, and Decoupling

To reduce noise effects, separate the analog and digital grounds.

In order to avoid latchup at power up, it is necessary that  $AV_{DD}$  and  $DV_{DD}$  be driven from the same supply.

Bypass both the digital and analog  $V_{DD}$  pins to their respective grounds with a ceramic  $0.1\mu F$  capacitor close to the pin.

#### Analog Input

The input capacitance is small when compared with other flash type A/D converters. However, it is necessary to drive the input with an amplifier with sufficient bandwidth and drive capability. In order to prevent parasitic oscillation, it may be necessary to insert a low value (i.e.,  $0.24\Omega$ ) resistor between the output of the amplifier and the A/D input.

#### Reference Input

The range of the A/D is set by the voltage between  $V_{RT}$  and  $V_{RB}$ . The internal bias generator will set  $V_{RTS}$  to 2.6V and  $V_{RBS}$  to 0.6V. These can be used as the part reference by shorting  $V_{RT}$  and  $V_{RTS}$  and  $V_{RB}$  to  $V_{RBS}$ . The analog input range of the A/D will now be from 0.6V to 2.6V and is referred to as Self Bias Mode 1. Self Bias Mode 2 is where VRB is connected to AGND and  $V_{RT}$  is shorted to  $V_{RTS}$ . The analog input range will now be from 0V to 2.4V.

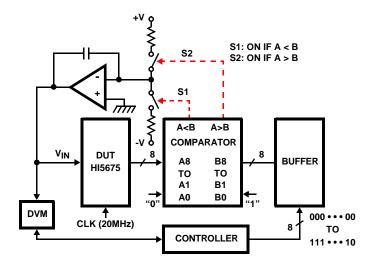

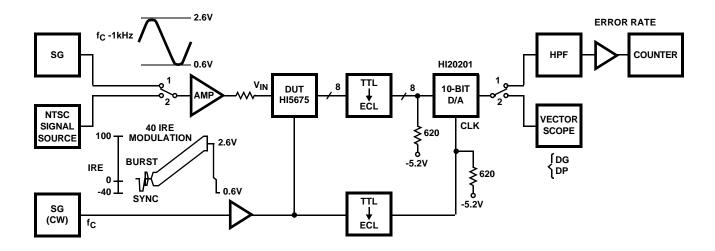

### **Test Circuits**

FIGURE 3. INTEGRAL AND DIFFERENTIAL NON-LINEARITY ERROR AND OFFSET VOLTAGE TEST CIRCUIT

FIGURE 4. MAXIMUM OPERATIONAL SPEED AND DIFFERENTIAL GAIN AND PHASE ERROR TEST CIRCUIT

FIGURE 5. DIGITAL OUTPUT CURRENT TEST CIRCUIT

#### Static Performance Definitions

Offset, full scale, and gain all use a measured value of the internal voltage reference to determine the ideal plus and minus full scale values. The results are all displayed in LSBs.

#### Offset Error (E<sub>OB</sub>)

The first code transition should occur at a level  $^{1}/_{2}LSB$  above the bottom reference voltage. Offset is defined as the deviation of the actual code transition from this point. Note that this is adjustable to zero.

### Full Scale Error (EOT)

The last code transition should occur for a analog input that is  $1^{1}/_{2}$  LSBs below full scale. Full scale error is defined as the deviation of the actual code transition from this point.

#### Differential Linearity Error (DNL)

DNL is the worst case deviation of a code width from the ideal value of 1 LSB. The converter is guaranteed to have no missing codes.

#### Integral Linearity Error (INL)

INL is the worst case deviation of a code center from a best fit straight line calculated from the measured data.

#### **Dynamic Performance Definitions**

Fast Fourier Transform (FFT) techniques are used to evaluate the dynamic performance of the HI5675. A low distortion sine wave is applied to the input, it is sampled, and the output is stored in RAM. The data is then transformed into the frequency domain with a 1024 point FFT and analyzed to evaluate the dynamic performance of the A/D. The sine wave input to the part is -0.5dB down from fullscale for all these tests. The distortion numbers are quoted in dBc (decibels with respect to carrier) and **DO NOT** include any correction factors for normalizing to fullscale.

### Signal-to-Noise Ratio (SNR)

SNR is the measured RMS signal to RMS noise at a specified input and sampling frequency. The noise is the RMS sum of all of the spectral components except the fundamental and the first five harmonics.

#### Signal-to-Noise + Distortion Ratio (SINAD)

SINAD is the measured RMS signal to RMS sum of all other spectral components below the Nyquist frequency excluding DC.

#### Effective Number Of Bits (ENOB)

The effective number of bits (ENOB) is derived from the SINAD data. ENOB is calculated from:

ENOB =  $(SINAD - 1.76 + V_{CORR}) / 6.02$ ,

where:  $V_{CORR} = 0.5$ dB.

#### **Total Harmonic Distortion**

This is the ratio of the RMS sum of the first 5 harmonic components to the RMS value of the measured input signal.

#### 2nd and 3rd Harmonic Distortion

This is the ratio of the RMS value of the 2nd and 3rd harmonic component respectively to the RMS value of the measured input signal.

#### Spurious Free Dynamic Range (SFDR)

SFDR is the ratio of the fundamental RMS amplitude to the RMS amplitude of the next largest spur or spectral component. If the harmonics are buried in the noise floor it is the largest peak.

#### Full Power Input Bandwidth

Full power bandwidth is the frequency at which the amplitude of the digitally reconstructed output has decreased 3dB below the amplitude of the input sine wave. The input sine wave has a peak-to-peak amplitude equal to the reference voltage. The bandwidth given is measured at the specified sampling frequency.

## **Timing Definitions**

## Sampling Delay (tSD)

Sampling delay is the time delay between the external sample command (the falling edge of the clock) and the time at which the signal is actually sampled. This delay is due to internal clock path propagation delays.

#### Aperture Jitter (t<sub>AJ</sub>)

This is the RMS variation in the sampling delay due to variation of internal clock path delays.

#### Data Latency (t<sub>LAT</sub>)

After the analog sample is taken, the data on the bus is available after 2.5 cycles of the clock. This is due to the architecture of the converter where the data has to ripple through the stages. This delay is specified as the data latency. After the data latency time, the data representing each succeeding sample is output at the following clock pulse. The digital data lags the analog input by 2.5 cycles.

### Output Data Delay (tD)

Output Data Delay is the delay time from when the data is valid (rising clock edge) to when it shows up at the output bus. This is due to internal delays at the digital output.

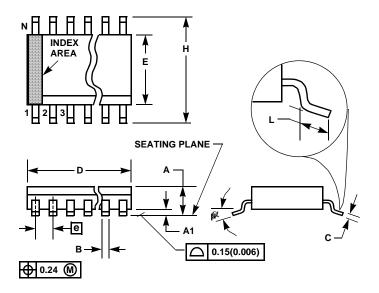

## Small Outline Plastic Packages (SOIC)

#### NOTES:

- 1. Dimension "D" does not include mold flash, protrusions or gate burrs.

- 2. Dimension "E" does not include interlead flash or protrusions.

- 3. "L" is the length of terminal for soldering to a substrate.

- 4. "N" is the number of terminal positions.

- 5. Terminal numbers are shown for reference only.

- Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

M24.2-S 24 LEAD SMALL OUTLINE PLASTIC PACKAGE (200 MIL)

|        | INCHES |                 | MILLIM   | MILLIMETERS     |       |  |

|--------|--------|-----------------|----------|-----------------|-------|--|

| SYMBOL | MIN    | MAX             | MIN      | MAX             | NOTES |  |

| Α      | 0.067  | 0.088           | 1.70     | 2.25            | -     |  |

| A1     | 0.002  | 0.011           | 0.05     | 0.30            | -     |  |

| В      | 0.014  | 0.021           | 0.35     | 0.55            | -     |  |

| С      | 0.006  | 0.011           | 0.15     | 0.30            | -     |  |

| D      | 0.587  | 0.606           | 14.9     | 15.4            | 1     |  |

| Е      | 0.205  | 0.220           | 5.2      | 5.6             | 2     |  |

| е      | 0.050  | BSC             | 1.27 BSC |                 | -     |  |

| Н      | 0.296  | 0.326           | 7.5      | 8.3             | -     |  |

| L      | 0.012  | 0.027           | 0.30     | 0.70            | 3     |  |

| N      | 24     |                 | 24       |                 | 4     |  |

| α      | 0°     | 10 <sup>0</sup> | 0°       | 10 <sup>0</sup> | -     |  |

Rev. 1 4/95

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.