## EH320-TFC-CC-DK1 EH320-TFC-CC-DK2 1PPS Time to Frequency Converter Modules

2111 Comprehensive Drive Aurora, Illinois 60505 Phone: 630-851-4722 Fax: 630-851-5040

> A T A

HE

| Bulletin | SG200        |

|----------|--------------|

| Revision | 06           |

| Date     | 13 Sept 2022 |

#### Overview

The EH320-TFC Series is a highly integrated time and frequency synchronizing module. This design implementation is dedicated for use in applications which specifically require locking to an incoming 1PPS reference signal. This high precision phase and frequency synchronization solution also integrates "any frequency" clock signal generation and frequency translation. This product can be used to support a high-stability frequency reference for use in wireless systems,

IEEE 1588v2, and applications employing a 1PPS frequency source for high precision, long term time and frequency generation. The -CC module option includes an on board OCXO that is further compensated for thermal stability to less than ±0.5ppb, which provides the system's master clock for disciplining the internal DPLL and supports the holdover performance when the 1PPS incoming reference signal is lost. The EH320-TFC-CC module outputs a 1PPS signal and a digitally synthesized 3.3V LVCMOS clock output at frequencies from 152Hz to 80 MHz. In addition, the module can generate up to 5 additional clean clock outputs at a variety of frequencies from 750MHz to <1KHz. The generated frequency outputs are both phase and frequency locked to the incoming 1PPS reference signal.

#### **Features**

- Accepts 1 PPS Reference input

- Locked, Holdover indication

- 1 PPS & NCO Frequency Output

- "Any Frequency" Generation from 152 Hz to 80MHz

- 1PPS Auto-detect

- Automatic entry into holdover

- 3.3VDC Supply Voltage

- Five Clean low phase noise clock outputs

- One Differential LVDS or LVPECL output to 750MHz

- CC Option for Sub ±0.5 ppb holdover performance

- OCXO Master Clock

- Phase and Frequency locked outputs

- 0°C to 70°C operating temperature range

- OEM SM footprint 25 x 22 mm

- RoHS Compliant

RoHS

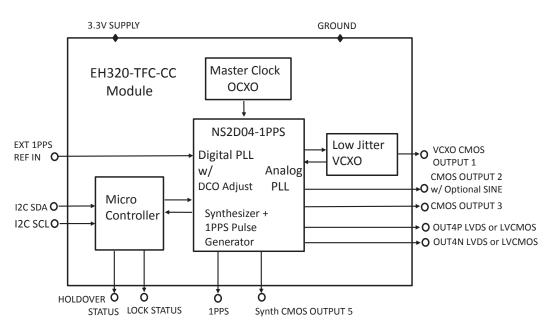

Figure 1: EH320-TFC-CC Functional Block Diagram

#### 1 INTRODUCTION

The EH320-TFC-CC is a small OEM surface mount timing module specifically designed for use in synchronization and timing applications. This module incorporates Connor-Winfield's advanced NS2D04 synchronizing ASIC which integrates a digital phase lock loop system with an analog phase lock loop system and multiple output transmitters to allow the user to discipline an external 1PPS signal and generate multiple output clocks phase locked and aligned to the incoming 1PPS reference.

The digital PLL system design supports multiple bandwidth settings used for disciplining the incoming 1PPS signal. The DPLL system in the EH320-TFC-CC is supported by a master clock which is derived from a high precision/low ADEV OCXO that is further internally compensated for thermal instability to achieve sub 1ppb thermal frequency stability while the module is in free run and holdover. Due to the ultra low ADEV performance of the module's master clock, the DPLL bandwidth in the EH320-TFC-CC is set to <1mHz.

The EH320-TFC-CC module auto-detects a valid incoming 3.3V 1PPS reference signal. When a valid 1PPS signal is present, the module has a three stage locking process starting with a frequency locking stage, followed by a fast phase locking stage before achieving full phase locking. The module is allowed to soak in a fast locking stage for a period of time while the OCXO has time to settle. After the frequency locking phase is complete, the 1PPS alignment process moves to within the closest period of the lowest common output frequency. A phase build-out process then adjusts and pulls the remaining phase offset alignment until fully aligned. For phase alignment to take place, frequencies must be divisible by 8kHz.

The DPLL block implements a digital synthesizer that generates an outgoing 1PPS, a variable frequency synthesized clock made available to the user in Output 5, and a synthesized clock that is sent to the Analog PLL system within the ASIC. Using a low jitter internal VCXO, the module generates multiple clock outputs at frequencies integer related to the VCXO frequency. Output 1 is the frequency of the VCXO used in the module. Output 2 and 3 are both 3.3V CMOS outputs and output 4 P/N can be configured as a differential signal (LVDS or LVPECL) or two CMOS outputs at the same frequency. Outputs 1 through 4 are derived from the frequency of the VCXO, directly divided at the output transmitter port. If frequencies higher than 125MHz are required, a secondary APLL block can be employed to integer divide outputs from a high frequency VCO in the range of 1.2 GHz to 1.46 GHz. If this secondary APLL is used, all outputs must be generated from this system, except for output 1 which always is derived from and is the same as the VCXO frequency. Except for output 1 and output 5, the output ports each have 20-bit dividers that can be used from either the VCXO frequency using the first PLL option or the VCO frequency if the second PLL block is used. Output 5 is a 3.3V CMOS output than can be programmed to any 8kHz divisible frequency from 10M to 80MHz and then further divided with an integer post divider with a 16 bit capability.

The EH320-TFC-CC incorporates a micro controller that moderates the internal ASIC, setting the registers and monitors operations. The module is programmed at the factory but some system commands may be available for changing some registers. The module is intended to be defined and provided to the user as a complete system capable of operating with no user input required.

The EH320-TFC-CC is RoHS and REACH compliant. It's highly integrated architecture is packaged in a small 22x25mm surface mount footprint allowing for easy integration into host systems.

For more detailed information on the operation of the internal system ASIC NS2D04, see the following data sheet. http://www.conwin.com/datasheets/tm/tm138.pdf

#### 2 PHYSICAL CHARACTERISTICS

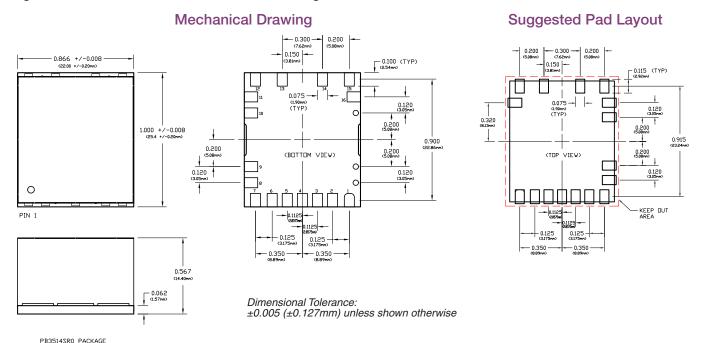

The EH320-TFC-CC is a multi-chip module (MCM) built on an FR4 fiberglass 22x25mm PCB. The general arrangement of the EH320-TFC-CC is shown in the diagram below.

Figure 2 EH320-TFC-CC Mechanical Drawing and Suggested Pad Layout

Figure 3 Marking Configuration

| Pin | Function           | Notes                                |

|-----|--------------------|--------------------------------------|

| 1   | FREQ_OUT2          |                                      |

| 2   | 1PPS_IN            |                                      |

| 3   | GND_Analog         | For output pins 1, 4, 10, 11, and 12 |

| 4   | FREQ_OUT3          |                                      |

| 5   | GND_Analog         | For output pins 1, 4, 10, 11, and 12 |

| 6   | 1PPS_OUT           |                                      |

| 7   | VCC_3V3_Digital    |                                      |

| 8   | LOCKED             |                                      |

| 9   | HOLDOVER           |                                      |

| 10  | FREQ_OUT4P         |                                      |

| 11  | FREQ_OUT4N         |                                      |

| 12  | FREQ_OUT1 VCXO     |                                      |

| 13  | I2C SCL            |                                      |

| 14  | I2C SDA            |                                      |

| 15  | GND_Digital        |                                      |

| 16  | FREQ_OUT5 Variable |                                      |

#### **3 SIGNAL DESCRIPTION**

The signals on the EH320-TFC-CC are described in the table below.

### 3.1 Power Signals

| VCC_3V3         | Type: Power                                                                                               | Direction: Input                                                | Pin: 7                                      |  |

|-----------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------|--|

|                 | The Supply Input. The                                                                                     | nis 3.3V ± 10% input supplies po                                | ower to the module                          |  |

|                 |                                                                                                           |                                                                 |                                             |  |

| GND             | Type: Power                                                                                               | Direction: Input/Output                                         | Pin: 15                                     |  |

|                 | The Input Ground. Th                                                                                      | is is the return path for the vcc 3V                            | /3 supply and the ground for the module.    |  |

| OND ANALOO      | T D                                                                                                       | Diversities of the second (October of                           | Din. 0. 5                                   |  |

| GND ANALOG      | Type: Power                                                                                               | Direction: Input/Output  nds only for output pins 1, 4, 10, 11, | Pin: 3, 5                                   |  |

|                 | rriese are arialog grou                                                                                   | nds only for output pins 1, 4, 10, 11,                          | , and 12                                    |  |

| 3.2 I/O Signals |                                                                                                           |                                                                 |                                             |  |

| 0.2 0.019.10.0  |                                                                                                           |                                                                 |                                             |  |

| TX[0]           | Type: I/O                                                                                                 | Direction: Output                                               | Pin: 13                                     |  |

|                 | I2c SCL PIN                                                                                               |                                                                 |                                             |  |

|                 |                                                                                                           |                                                                 |                                             |  |

| RX[0]           | Type: I/O                                                                                                 | Direction: Input                                                | Pin: 14                                     |  |

|                 | I2c SDA PIN                                                                                               |                                                                 |                                             |  |

| HOLDOVER        | Type: I/O                                                                                                 | Direction: Output                                               | Pin: 9                                      |  |

| HOLDOVEIT       |                                                                                                           | · · · · · · · · · · · · · · · · · · ·                           | Holdover status. High indicates holdover    |  |

|                 |                                                                                                           | as a 3.3V CMOS drive.                                           |                                             |  |

|                 |                                                                                                           |                                                                 |                                             |  |

| LOCKED          | Type: I/O                                                                                                 | Direction: Output                                               | Pin: 8                                      |  |

|                 | Standard software builds use this signal to indicate LOCK status. High indicates locked to 1p             |                                                                 | LOCK status. High indicates locked to 1pps. |  |

|                 | This signal has a 3.3                                                                                     | V CMOS drive.                                                   |                                             |  |

| FREQ_OUT1 VCXO  | Type: I/O                                                                                                 | Direction: Output                                               | Pin: 12                                     |  |

| 11124_001110110 | Primary output of the module which is a pass through of the frequency of the VCXO internal to the module. |                                                                 |                                             |  |

|                 |                                                                                                           |                                                                 |                                             |  |

|                 |                                                                                                           |                                                                 |                                             |  |

| FREQ_OUT2       | Type: I/O                                                                                                 | Direction: Output                                               | Pin: 1                                      |  |

|                 | Second output from                                                                                        | the module that can be provided                                 | d as either 3.3V LVCMOS or 3.3V Sinewave.   |  |

| EDEO OUT2       | Tunou I/O                                                                                                 | Directions Output                                               | Din. 4                                      |  |

| FREQ_OUT3       | Type: I/O  Third output from the                                                                          | Direction: Output<br>e module 3.3V LVCMOS.                      | Pin: 4                                      |  |

|                 | Third Odipat Holli tik                                                                                    | c module 0.0 v Evolvido.                                        |                                             |  |

| FREQ_OUT4P/N    | Type: I/O                                                                                                 | Direction: Output                                               | Pin: 10, 11                                 |  |

|                 | Fourth output from the module that can be provided as either 3.3V LVDS, 3.3V LVPECL                       |                                                                 |                                             |  |

|                 | or 2 x 3.3V LVCMOS                                                                                        | ).                                                              |                                             |  |

|                 |                                                                                                           |                                                                 |                                             |  |

| 1 PPS_IN        | Type: I/O                                                                                                 | Direction: Input                                                | Pin: 2                                      |  |

|                 |                                                                                                           | cond Reference Input Signal. T<br>d by an external GPS/GNSS so  | his is normally as a 1 pulse aligned with   |  |

|                 | or o time, generate                                                                                       | a by an external ar orango so                                   | ouroc.                                      |  |

#### 3 SIGNAL DESCRIPTION continued

3.2 I/O Signals cont'd

1 PPS OUT Type: I/O Direction: Output Pin: 6

The 1 Pulse-Per-Second Signal.

This is normally as a 1 pulse aligned with incoming 1PPS\_IN signal.

FREQ OUT5 Variable Type: I/O Direction: Output Pin: 16

Frequency Output that defaults to 10 MHz and is factory configurable. The output is enabled on power-up and is steered by the incoming 1PPS signal. This clock output is a 3.3V LVCMOS single ended signal generated by the internal NCO with output frequency values achievable from 152Hz to 80MHz.

Internally, the frequency output is a value determined by two separate register settings. An initial value of M is used to multiply 8kHz to a frequency in the range between 10MHz and 80MHz. Once the M value is determined, a 16-bit post divider can be employed to generate a set of lower rate frequencies by choosing an N value which divides the base frequency by that number. V alid M values are integer numbers >= 1250 and <=10,000.V alid N values are integer numbers =>1 and <= 65536. A "0" value for M will disable the output while a "0" value for N will disable the post divider.

NOTE: Phase alignment between the 1PPS incoming reference and the synthesized frequency output is possible only if the synthesized output frequency is integer related to 8kHz. All frequencies generated by values of only M will be phased aligned with the incoming 1PPS signal. However, using the 16 bit post divider, only N values chosen that result in an output frequency that has an integer relationship with 8kHz will be phase aligned to the incoming 1PPS signal.

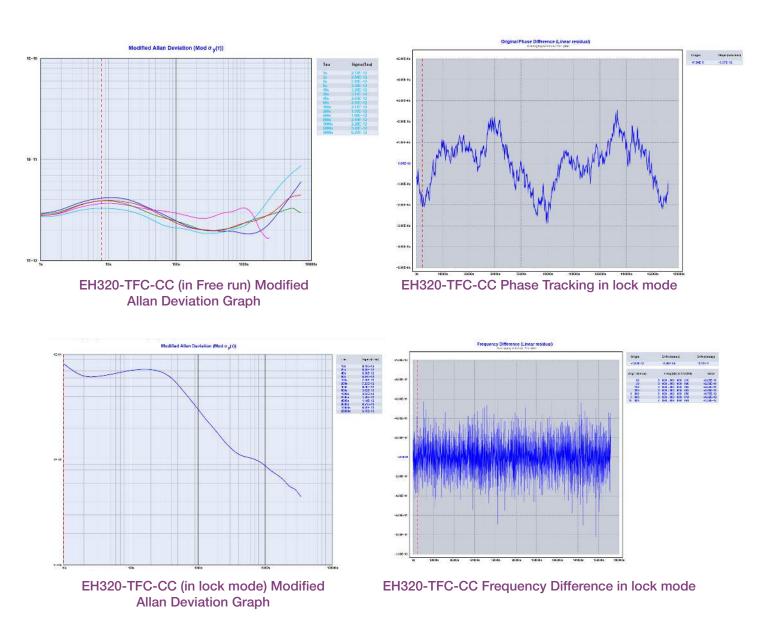

#### **4 PERFORMANCE COMPARISON**

The EH320-TFC model series allows for a choice of master clock options which dictate the bandwidth setting chosen to optimize performance. The -CC option allows for loop bandwidth settings of 1 mHz or less due to its master clock ultra-low ADEV performance.

Figure 4: EH320-TFC-CC Performance Comparisons

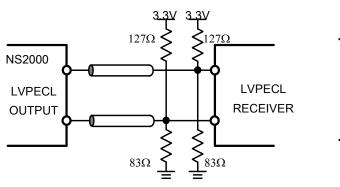

## **LVPECL Suggested Termination**

**DC-Coupled LVPECL Termination**

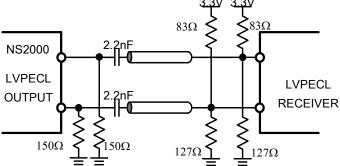

AC-Coupled LVPECL Termination

# LVPECL Current Consumption fvco=1.244GHz, fvcxo=38.88MHz,ftcxo=20MHz

| OUTPUT FREQUENCY<br>(MHz) | DUTY CYCLE (%) | <b>RISE TIME</b> (20%~80%)(ps) | CURRENT<br>CONSUMPTION (mA) | <b>DIFFERENTIAL</b><br>SWING (Vp-p) |

|---------------------------|----------------|--------------------------------|-----------------------------|-------------------------------------|

| 38.88                     | 50.09          | 590                            | 41.69                       | 1.183                               |

| 103.681                   | 49.97          | 570                            | 41.59                       | 1.139                               |

| 113.108                   | 45.44          | 560                            | 41.59                       | 1.148                               |

| 124.417                   | 49.98          | 570                            | 41.57                       | 1.161                               |

| 138.239                   | 44.49          | 520                            | 41.53                       | 1.171                               |

| 155.519                   | 49.98          | 530                            | 41.56                       | 1.152                               |

| 177.74                    | 43.06          | 570                            | 41.56                       | 1.163                               |

| 207.362                   | 50.1           | 510                            | 41.41                       | 1.182                               |

| 248.836                   | 42             | 430                            | 41.34                       | 1.095                               |

| 311.054                   | 50.14          | 500                            | 41.32                       | 1.049                               |

| 414.736                   | 35.64          | 370                            | 41.53                       | 0.86                                |

| 622.115                   | 51.05          | 270                            | 41.56                       | 0.778                               |

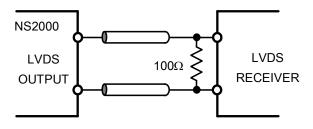

## **LVDS Suggested Termination**

**DC-Coupled LVDS Termination**

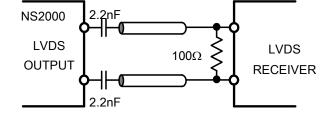

AC-Coupled LVDS Termination

# LVDS Current Consumption fvco=1.244GHz, fvcxo=38.88MHz.ftcxo=20MHz

|                           | 1700-1.2-1-0112, | 1 4 0 7 0 - 00 . 00 1 1 1 1 2,1 | LONG-ZOIVII IZ              |                                     |

|---------------------------|------------------|---------------------------------|-----------------------------|-------------------------------------|

| OUTPUT FREQUENCY<br>(MHz) | DUTY CYCLE (%)   | <b>RISE TIME</b> (20%~80%)(ps)  | CURRENT<br>CONSUMPTION (mA) | <b>DIFFERENTIAL</b><br>SWING (Vp-p) |

| 38.8815                   | 49.97            | 700                             | 18.18                       | 0.593                               |

| 103.68                    | 50.18            | 620                             | 18.26                       | 0.586                               |

| 113.107                   | 50.46            | 600                             | 18.26                       | 0.593                               |

| 124.414                   | 50.21            | 610                             | 18.26                       | 0.606                               |

| 138.241                   | 50.52            | 580                             | 18.26                       | 0.61                                |

| 155.52                    | 50.26            | 600                             | 18.26                       | 0.6                                 |

| 177.737                   | 50.81            | 610                             | 18.26                       | 0.598                               |

| 207.363                   | 50.52            | 600                             | 18.25                       | 0.623                               |

| 248.832                   | 50.8             | 450                             | 18.25                       | 0.575                               |

| 311.05                    | 50.62            | 580                             | 18.26                       | 0.547                               |

| 414.733                   | 49.57            | 250                             | 18.27                       | 0.431                               |

| 622.108                   | 50.9             | 220                             | 18.24                       | 0.378                               |

Delivering a New Generation of Time and Frequency Solutions for a Connected World.

EH320-TFC-CC-DK1/DK2 Data Sheet #. **SG200** Page **7** of **9** Rev: **06** Date: **09/13/22**

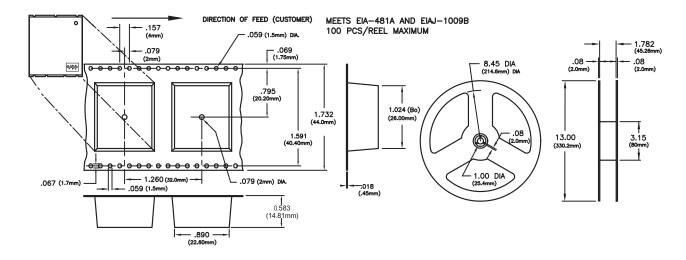

Figure 5 Tape and Reel

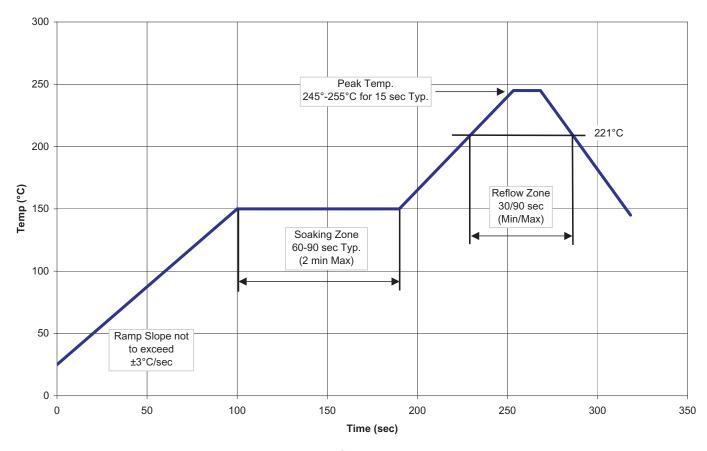

#### **6 SOLDER PROFILE**

Figure 6 Solder Profile

## EH320-TFC-CC-DK1 EH320-TFC-CC-DK2 Time to Frequency Converter Module

**Ordering Information:**

EH320-TFC-CC-DK1

BASE MCLK CONFIGURATION SUFFIX

| MCLK Suffix      | Thermal Stability    | Comments                     |  |

|------------------|----------------------|------------------------------|--|

| -CC              | ±0.5ppb; 0 to 70°C   | Compensated OCXO             |  |

| Custom Configura | ation: -DK1          | -DK2                         |  |

| VCXO Frequency:  | 10.0 MHz             | 100.0 MHz                    |  |

| OUT1 (Pin 12):   | 10.0 MHz LVCMOS      | 100.0 MHz LVCMOS             |  |

| OUT2 (Pin 1):    | 10.0 MHz Sinewave    | e 10.0 MHz Sinewave          |  |

| OUT3 (Pin 4):    | 10.0 MHz LVCMOS      | 10.0 MHz LVCMOS              |  |

| OUT4P (Pin 10):  | 5.0 MHz LVCMOS       | 25.0 MHz LVDS                |  |

| OUT4N (Pin 11):  | 5.0 MHz LVCMOS       | 25.0 MHz LVDS                |  |

| OUT5 (Pin 16):   | Variable (up to 80 N | MHz) Variable (up to 80 MHz) |  |

<sup>\*</sup> Any unused outputs can be turned off

| List of Figures                                           | Page |

|-----------------------------------------------------------|------|

| Figure 1 EH320-TFC-CC Block Diagram                       | 1    |

| Figure 2 EH320-TFC-CC Dimensions and Suggested Pad Layout | 3    |

| Figure 3 EH320-TFC-CC Marking Configurations              | 3    |

| Figure 4 EH320-TFC-CC Performance Comparisons             | 6    |

| Figure 5 Tape and Reel                                    | 8    |

| Figure 6 Solder Reflow Profile                            | 8    |

## **Revision History**

| Revision | Date     | Note                                                                     |

|----------|----------|--------------------------------------------------------------------------|

| 00       | 05/27/20 | New Release                                                              |

| 01       | 08/27/20 | Updated frequency configuration and added LVPECL & LVDS Consumption Page |

| 02       | 09/29/20 | Removed incorrect reference on page 7                                    |

| 03       | 02/18/21 | Updated footprint with 2 extra analog ground pins                        |

| 04       | 08/25/21 | Updated temperature range to from -40/85°C to 0/70°C                     |

| 05       | 01/06/22 | Add Pin 2 1PPS_IN back into pin table, add pin numbers to                |

|          |          | Frequency outputs on p. 9                                                |

| 06       | 09/13/22 | Change Pin 16 description from user to factory configurable.             |

2111 Comprehensive Drive Aurora, Illinois 60505 Phone: 630-851-4722 Fax: 630-851-5040 www.conwin.com