# **CMX881** Baseband Processor for PMR and Trunked Radios

D/881/17 April 2009

# Full-Feature Audio-Processing, Signalling and Data for Half Duplex Dual-Mode Analogue PMR and Trunked Radios

### Features

- Automatic signal type scanning and IRQ on detection of valid Rx signals, level or RSSI

- Tone generator for caller recognition tunes

- Programmable powerdown control

- Programmable signal detection thresholds

- Low Power operation with 'Zero Power' mode

- Uncommitted Aux ADC with switchable input to monitor signals

- Voice processing facilities, including Tx and Rx gain setting and voice/subaudio filtering

- C-BUS serial host interface

- RF interface allowing 1 or 2 point modulation

- Programmable soft limiter

- Programmable Selcall Codec

- Zero 'Talkdown' CTCSS decoder performance prevents dropouts

- DTMF transmitter

- Meets ETS 300 086, MPT1327, PAA1382 and ETS 300 230 specifications

- Standard (39-tone) CTCSS and 23/24 bit DCS Codecs

- Robust half-duplex FFSK/MSK modem, 1200/2400bps with CRC and parity generator/checker, gets data through when signal is too degraded for voice – for text messaging/paging, location transfer, etc. applications.

### 1.1 Brief Description

CMX881, a full-function half-duplex audio and signalling processor IC for both PMR and Trunked radio systems suitable for complex and simple end-designs. Under the control of the host  $\mu$ C, all voiceband requirements are catered for: voiceband and sub-audio filtering, pre/de-emphasis and audio routing and global level setting with single or two-point modulation in the transmit path.

The combination of CTCSS and DCS functions and Selcall operation of this product offer, under software control, increased functionality, versatility and privacy.

To cater for call setup and system signalling the CMX881 provides an embedded 1200/2400 bps MSK/FFSK free-format modem for text messaging/paging, passing GPS location data with checksum generation and reception and sync detection in the Rx path.

<sup>© 2009</sup> CML Microsystems Plc

With ultra low power requirements and graduated powersave, this product requires a smaller, lowerpower  $\mu$ C than existing PMR or trunked radio solutions. It is available in compact SSOP and TSSOP packages.

## **CMX881 Functions and Facilities**

#### Half Duplex Operation

Working in a half duplex mode, when the product is in Tx the Rx sections can be powered down to extend battery life, conversely in Rx major sections of the Tx can be treated in the same manner.

#### Serial Control and Data Interface

C-BUS: Serial control, data and command program interface compatible with SCI, SPI and Microwire type interfaces.

#### **Power Requirements and Economy**

With an ultra low power requirement, the CMX881 operates from a single 2.7 to 5.5 Volt supply with graduated 'Sleep Mode' powersaving facilities for both Rx and Tx modes.

#### Signalling:

#### CTCSS

Zero 'Talkdown' performance eliminates unwanted breaks in communication. The CMX881 is preprogrammed with 39 standard CTCSS (+ Notone and DCS 'turn off' tone) frequencies, any one of which can be selected for reception or transmission. Decoding is aided by the use of adjustable decode bandwidths and threshold levels. Decoding is carried out rapidly thus avoiding the loss of the beginning of speech or data signals.

#### DCS

The DCS code is in NRZ format and is transmitted at 134.4b/s in either 23 or 24 bit patterns. The code, for transmission or reception is programmed via the host  $\mu$ C with the 'turn off' tone being supplied from the CTCSS facility. Decoding is carried out rapidly thus avoiding the loss of the beginning of speech or data signals.

#### Selcall

This product implements a fully programmable Selcall encoder and decoder employing normal and special tones. Tone frequencies, decoder bandwidths and thresholds are programmed by the host  $\mu$ C. In receive the CMX881 scans its internal tone table for a match, reporting its results to the  $\mu$ C.

#### FFSK/MSK Data

An MPT packet and free-format half duplex FFSK/MSK modem is implemented. In receive this device can decode data at either automatic or manually selected 1200b/s or 2400b/s rates. Additionally, in receive, a 16-bit programmed frame sync (MPT packet-type) pattern can be detected. Formatting control and data transfers to and from the modem is under the control of the host  $\mu$ C.

#### **DTMF** Tx

The CMX881, under  $\mu$ C control, can generate and transmit all standard DTMF tone-pairs.

#### **Signal Monitor**

An auxiliary circuit intended for the monitoring of any signal or level; both internal and external. This function can be used in conjunction with the host  $\mu$ C to allow such activities as: VOX operation and/or the 'wake-up' of powered-down circuitry.

#### Audio Processing:

#### Adjustable Gain Input Amplifiers

Selectable, component adjustable inputs are available for microphone or line voiceband or discriminator inputs. In either mode (Tx or Rx) the selected input can be further level adjusted under the control of the host  $\mu$ C prior to signal- or audio- processing.

#### Voiceband and Sub-Audio Filtering with Limiting

Both Rx and Tx paths present voiceband filtering; the Tx path filter can be configured to either 12.5 or 25 kHz channel spacing whilst the Rx path also includes a sub-audio passband filter.

#### **Voiceband Pre-emphasis and De-emphasis**

Voiceband pre-emphasis is selectable to either 12.5 or 25 kHz channel configurations in the Tx path; deemphasis at -6dB/ octave is selectable in the Rx path.

#### Software Adjustable Gains, Volume, Mixing and Routing

Providing total flexibility of operation, this product, under  $\mu$ C control has the ability to select and route functions and audio and signal paths, set bandwidths and threshold levels, mix audio and sub bands and vary both input and out gain/attenuation levels. Output levels from all analogue ports can be 'ramped' up and down at independently programmed rates.

#### Attenuation-Adjustable Single/Two-Point Modulation Outputs

To facilitate a wide range of transmitter types, the CMX881 has the ability to provide, independently programmable, modulation outputs; for single or two-point modulation schemes.

#### CONTENTS

#### Section

#### <u>Page</u>

| 1.0 |                   | es                                                |    |  |  |  |

|-----|-------------------|---------------------------------------------------|----|--|--|--|

| 1.1 | Brief Description |                                                   |    |  |  |  |

| 1.2 | Block [           | Diagram                                           | 7  |  |  |  |

| 1.3 |                   | List                                              |    |  |  |  |

| 1.4 | Extern            | al Components                                     | 10 |  |  |  |

|     | 1.4.1             | PCB Layout Guidelines and Power Supply Decoupling | 11 |  |  |  |

|     | 1.4.2             | Modulator Outputs                                 | 12 |  |  |  |

| 1.5 | Genera            | al Description                                    |    |  |  |  |

|     | 1.5.1             | Sleep Mode and Auto Start Up                      | 14 |  |  |  |

|     | 1.5.2             | Auxiliary ADC                                     | 14 |  |  |  |

|     | 1.5.3             | Receive Mode                                      | 15 |  |  |  |

|     | 1.5.4             | Transmit Mode                                     | 22 |  |  |  |

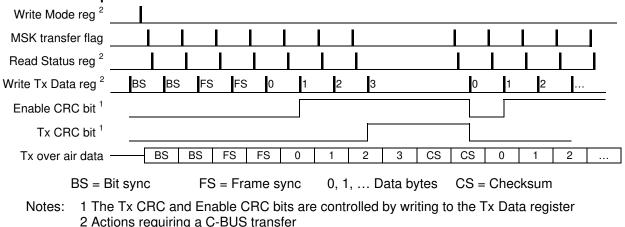

|     | 1.5.5             | FFSK/MSK Data packeting                           | 26 |  |  |  |

|     | 1.5.6             | C-BUS Operation                                   |    |  |  |  |

| 1.6 | C-BUS             | Register Description                              | 29 |  |  |  |

| 1.7 |                   | ation Notes                                       |    |  |  |  |

|     | 1.7.1             | CRC and Parity information                        | 52 |  |  |  |

| 1.8 | Perforr           | nance Specification                               |    |  |  |  |

|     | 1.8.1             | Electrical Performance                            |    |  |  |  |

|     | 1.8.2             | Packaging                                         |    |  |  |  |

|     |                   |                                                   |    |  |  |  |

### Table

#### Page

| Table 1 | Concurrent Rx Signalling Modes Supported by the CMX881 | 15 |

|---------|--------------------------------------------------------|----|

| Table 2 | CTCSS Tones                                            | 18 |

| Table 3 | DCS Modulation Modes                                   | 18 |

| Table 4 | DCS 23 Bit Codes                                       | 19 |

| Table 5 | Selcall Tones                                          | 20 |

| Table 6 | Concurrent Tx Modes Supported by the CMX881            | 22 |

| Table 7 | Data Frequencies for each Baud Rate                    | 25 |

| Table 8 | DTMF Tone Pairs and Corresponding Tx Programming Codes | 26 |

| Table 9 | Maximum Data Transfer Latency                          | 27 |

#### <u>Figure</u>

#### <u>Page</u>

| Figure 1 Block Diagram                                                 | 7  |

|------------------------------------------------------------------------|----|

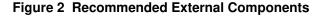

| Figure 2 Recommended External Components                               |    |

| Figure 3 Power Supply Connections and De-coupling                      | 11 |

| Figure 4 Modulator output components to achieve -100dB/decade roll-off |    |

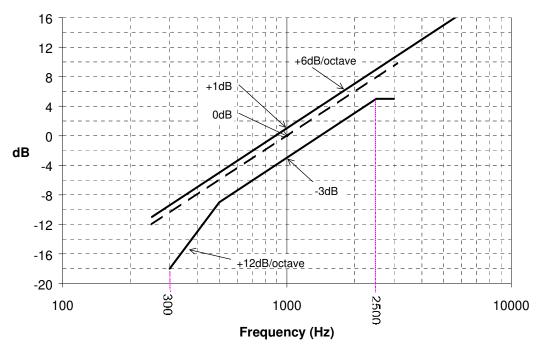

| Figure 5 Rx Audio Filter Frequency Response                            | 16 |

| Figure 6 De-emphasis Curve for TIA/EIA-603 Compliance                  |    |

| Figure 7 Low Pass Sub-Audio Band Filter for CTCSS and DCS              | 17 |

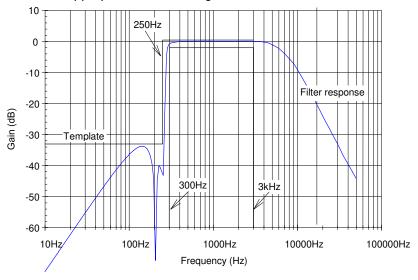

| Figure 8 25kHz Channel Audio Filter Response Template                  | 23 |

| Figure 9 12.5kHz Channel Audio Filter Response Template                | 23 |

| Figure 10 Audio Frequency Pre-emphasis Template                        | 24 |

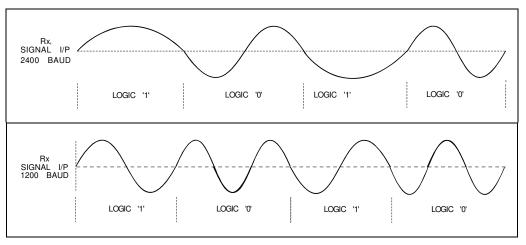

| Figure 11 Modulating Waveforms for 1200 and 2400 Baud FFSK/MSK Signals | 25 |

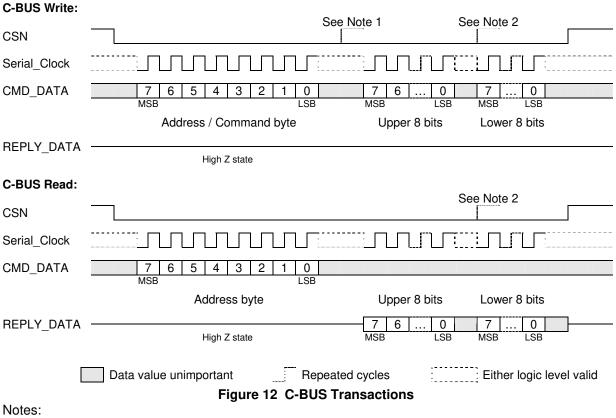

| Figure 12 C-BUS Transactions                                           |    |

| Figure 13 Possible PMR Configuration                                          | 52 |

|-------------------------------------------------------------------------------|----|

| Figure 14 C-BUS Timing                                                        | 61 |

| Figure 15 Typical FFSK/MSK Bit Error Rate Graph                               |    |

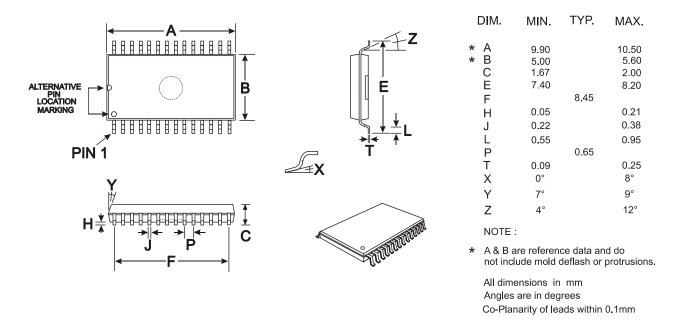

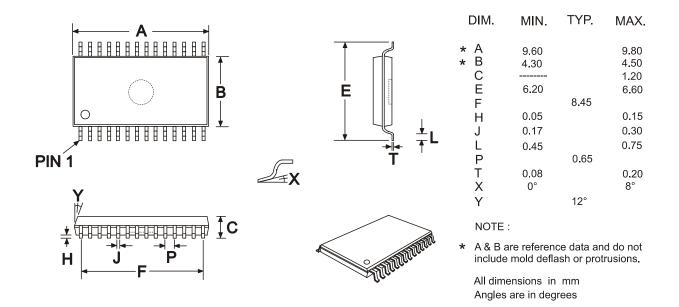

| Figure 16 Mechanical Outline of 28-pin SSOP (D6): Order as part no. CMX881D6  | 63 |

| Figure 17 Mechanical Outline of 28-pin TSSOP (E1): Order as part no. CMX881E1 | 63 |

It is always recommended that you check for the latest product datasheet version from the Datasheets page of the CML website: [www.cmlmicro.com].

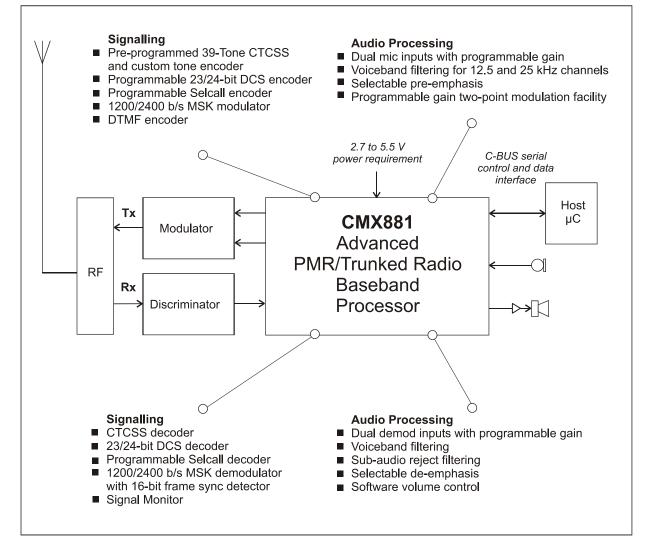

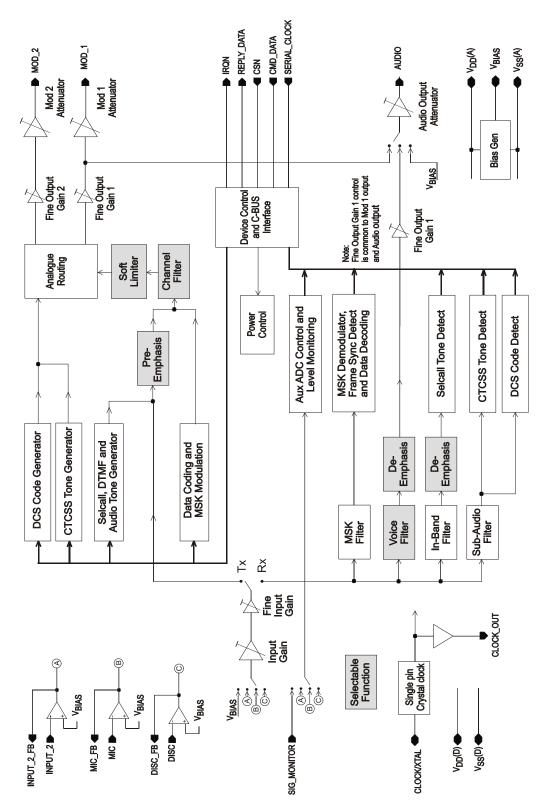

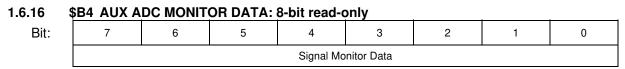

### 1.2 Block Diagram

Figure 1 Block Diagram

| Package<br>D6, E1 | Signal              |       |                                                                                                                                                                                                                        |  | Description |

|-------------------|---------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|

| Pin No.           | Name                | Туре  |                                                                                                                                                                                                                        |  |             |

| 23                | V <sub>DD</sub> (D) | Power | The digital positive supply rail. This pin should be decoupled to $V_{SS(D)}$ by a capacitor mounted close to the device pins.                                                                                         |  |             |

| 5                 | V <sub>SS(D)</sub>  | Power | The negative supply rail (digital ground).                                                                                                                                                                             |  |             |

| 18                | V <sub>DD</sub> (A) | Power | The analogue positive supply rail. Levels and thresholds within the device are proportional to this voltage. This pin should be decoupled to $V_{SS(A)}$ by a capacitor mounted close to the device pins.              |  |             |

| 9, 21             | V <sub>SS</sub> (A) | Power | The negative supply rail. Both pins must be connected to analogue ground.                                                                                                                                              |  |             |

| 1, 2              |                     | NC    | No connection should be made to these pins.                                                                                                                                                                            |  |             |

| 3                 | IRQN                | O/P   | A 'wire-Orable' output for connection to the Interrupt Request input of the host. This output is pulled down to $V_{SS(D)}$ when active and is high impedance when inactive. An external pull-up resistor is required. |  |             |

| 4                 | REPLY_DATA          | T/S   | The C-BUS serial data output to the host. This output is held at high impedance when not sending data to the host.                                                                                                     |  |             |

| 6                 | SERIAL_CLOCK        | I/P   | The C-BUS serial clock input from the host.                                                                                                                                                                            |  |             |

| 7                 | CMD_DATA            | I/P   | The C-BUS serial data input from the host.                                                                                                                                                                             |  |             |

| 8                 | CSN                 | I/P   | The C-BUS data loading control function. Data transfer sequences are initiated, and completed by the CSN signal.                                                                                                       |  |             |

#### Signal List (continued) 1.3

| Package<br>D6, E1 | Signal            |      | Description                                                                                                                                                                                                                                     |  |  |

|-------------------|-------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin No.           | Name              | Туре |                                                                                                                                                                                                                                                 |  |  |

| 10                | V <sub>BIAS</sub> | O/P  | Internally generated bias voltage of approximately $V_{DD}(A)/2$ , except when bias is power-saved when $V_{BIAS}$ will discharge to $V_{SS}(A)$ . This pin should be decoupled to $V_{SS}(A)$ by a capacitor mounted close to the device pins. |  |  |

| 11                | DISC              | I/P  | Input terminal of discriminator input amplifier.                                                                                                                                                                                                |  |  |

| 12                | DISC_FB           | O/P  | Output / feedback terminal of discriminator input amplifier.                                                                                                                                                                                    |  |  |

| 13                | INPUT_2           | I/P  | Input terminal of amplifier 2, for either a second microphone or discriminator input.                                                                                                                                                           |  |  |

| 14                | INPUT_2_FB        | O/P  | Output / feedback terminal of input amplifier 2.                                                                                                                                                                                                |  |  |

| 15                | MIC               | I/P  | Input terminal of microphone input amplifier.                                                                                                                                                                                                   |  |  |

| 16                | MIC_FB            | O/P  | Output / feedback terminal of microphone input amplifier.                                                                                                                                                                                       |  |  |

| 17                | SIG_MONITOR       | I/P  | Signal Monitor input to the internal level detecting circuit.                                                                                                                                                                                   |  |  |

| 19                | MOD_1             | O/P  | Modulator 1 output.                                                                                                                                                                                                                             |  |  |

| 20                | MOD_2             | O/P  | Modulator 2 output.                                                                                                                                                                                                                             |  |  |

| 22                | AUDIO             | O/P  | Output of the audio section.                                                                                                                                                                                                                    |  |  |

| 24                | CLOCK/XTAL        | I/P  | The input to the on-chip oscillator for an external crystal or a clock circuit.                                                                                                                                                                 |  |  |

| 25                | CLOCK_OUT         | O/P  | Buffered (un-inverted) clock output available for use by other devices in the system.                                                                                                                                                           |  |  |

| 26                |                   | I/P  | Test input, connect to V <sub>SS(D)</sub> .                                                                                                                                                                                                     |  |  |

| 27, 28            |                   | NC   | No connection should be made to these pins.                                                                                                                                                                                                     |  |  |

|                   |                   |      |                                                                                                                                                                                                                                                 |  |  |

Notes: I/P = Input

T/S =

3-state Output No Connection NC =

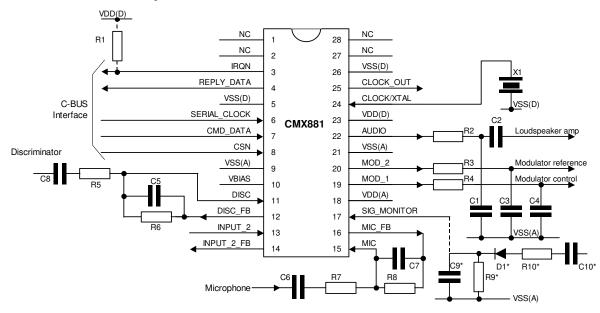

#### 1.4 External Components

| See note 1 |

|------------|

|            |

|            |

|            |

Resistors  $\pm$ 5%, capacitors and inductors  $\pm$ 20% unless otherwise stated.

Notes:

- 1. X1 can be a crystal or an external clock generator; this will depend on the application. The clock drift requirement is defined in section 1.8.1. The tracks between the crystal and pin 24 and pin 5 should be as short as possible to achieve maximum stability and best start up performance.

- 2. R5 should be selected to provide the desired dc gain (assuming C8 is not present) of the discriminator input, as follows:

$$|\text{GAIN}_{\text{Disc}}| = 100 \text{k}\Omega / \text{R5}$$

The gain should be such that the resultant output at the DISC\_FB pin is within the discriminator input signal range specified in section 1.8.1.

3. R7 should be selected to provide the desired dc gain (assuming C6 is not present) of the microphone input, as follows:

$$|\text{GAIN}_{\text{Mic}}| = 100 \text{k}\Omega / \text{R7}$$

The gain should be such that the resultant output at the MIC\_FB pin is within the microphone input signal range specified in section 1.8.1. For optimum performance with low signal microphones, an additional external gain stage may be required.

4. C6 and C8 should be selected to maintain the lower frequency roll-off of the microphone and discriminator inputs as follows:

$$\begin{array}{l} C6 \geq 30 nF \times \mid GAIN_{Mic} \mid \\ C8 \geq 1 \mu F \times \mid GAIN_{Disc} \mid \end{array}$$

- 5. INPUT\_2 and INPUT\_2\_FB connections allow the user to have a second discriminator or microphone input. Component connections and values are as for the networks around pins 11 and 12 or pins 15 and 16 respectively. If this input is not required pin 13 must be connected to pin 14.

- 6. The circuit formed by D1, C9, C10, R9 and R10 is a peak detector, this is only required when the signal monitor is connected to an ac signal (e.g. microphone or received signal). For a dc type signal (e.g. RSSI) these components are not required. The values of C9 and R10 set the attack time, C9 and R9 set the decay time. D1 can be any suitable small signal diode. R10 should be a high enough value so as not to distort the signal source.

#### 1.4.1 PCB Layout Guidelines and Power Supply Decoupling

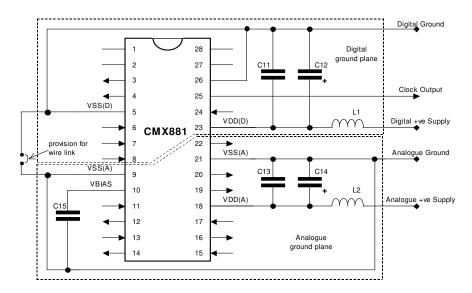

#### Figure 3 Power Supply Connections and De-coupling

| C11 | 10nF | C14 | 10µF  | L1 | 100nH | See note 7 |

|-----|------|-----|-------|----|-------|------------|

| C12 | 10μF | C15 | 100nF | L2 | 100nH | See note 7 |

| C13 | 10nF |     |       |    |       |            |

# Resistors $\pm 5\%$ , capacitors and inductors $\pm 20\%$ unless otherwise stated. Notes:

7. The inductors L1 and L2 can be omitted but this may degrade system performance.

It is important to protect the analogue pins from extraneous inband noise and to minimise the impedance between the CMX881 and the supply and bias de-coupling capacitors. The de-coupling capacitors C11, C12, C13 and C14 should be as close as possible to the CMX881, particularly C11 and C13. It is therefore recommended that the printed circuit board is laid out with separate ground planes for the  $V_{SS}(A)$  and  $V_{SS}(D)$  in the area of the CMX881, with provision to make a link between them close to the CMX881.

$V_{BIAS}$  is used as an internal reference for detecting and generating the various analogue signals. It must be carefully decoupled, to ensure its integrity, so apart from the decoupling capacitor shown, no other loads should be connected. If  $V_{BIAS}$  needs to be used to set the discriminator mid-point reference, it must be buffered with a high input impedance buffer.

The single ended microphone input(s) and audio output must be ac coupled as shown, so their return paths can be connected to  $V_{SS}(A)$  without introducing dc offsets. Further buffering of the audio output is advised.

The crystal X1 can be replaced with an external clock source if required/desired. The internal clock generating circuit can be placed in power-save mode if the clock is provided externally.

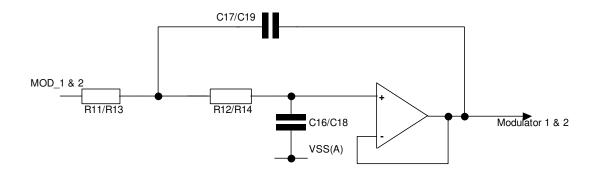

#### 1.4.2 Modulator Outputs

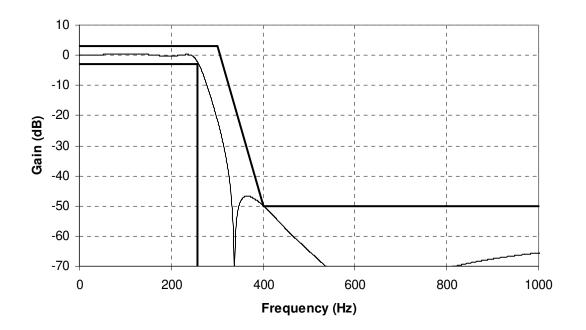

The combination of CMX881 and the modulator output components, R3/C3 and R4/C4, achieve roll-off rates better than -60dB/decade. If required this can be increased to better than -100dB/decade by replacing R3/C3 and R4/C4 with the active filter circuit shown in Figure 4.

#### Figure 4 Modulator output components to achieve -100dB/decade roll-off

| R11 | 120kΩ | C16 | 220pF |           |

|-----|-------|-----|-------|-----------|

| R12 | 120kΩ | C17 | 440pF | (2 x C16) |

| R13 | 120kΩ | C18 | 220pF | . ,       |

| R14 | 120kΩ | C19 | 440pF | (2 x C18) |

Resistors  $\pm 5\%$ , capacitors and inductors  $\pm 20\%$  unless otherwise stated.

Notes:

8. The external op-amp must be chosen to ensure that the required signal output level can be driven within acceptable distortion limits.

#### 1.5 General Description

The CMX881 is intended for use in half duplex analogue two way land mobile radio (LMR) equipment and is particularly suited to multi standard PMR systems. The CMX881 provides radio signal encoder and decoder functions for: Voice, Selcall, Tx DTMF, CTCSS, DCS and FFSK/MSK data permitting simple to sophisticated levels of tone control and data transfer. Power control facilities allow the device to be placed in varying levels of sleep allowing the user to fine tune the power depending on system requirements. The CMX881 includes a crystal clock generator, with buffered output, to provide a common system clock if required. A block diagram of the CMX881 is shown in Figure 1.

#### Tx functions

#### Audio

- o Single/dual microphone inputs with input amplifier and programmable gain adjustment

- Filtering selectable for 12.5kHz and 25kHz channels

- Selectable pre-emphasis

- o 2-point modulation outputs with programmable level adjustment

#### Signalling

- Pre-programmed 39 tone CTCSS encoder

- Programmable 23/24bit DCS encoder

- Programmable audio tone generator (for custom audio tones)

- Programmable Selcall encoder

- DTMF encoder

- o 1200/2400bps MSK modulator

#### Rx functions

#### Audio

- o Single/dual demodulator inputs with input amplifier and programmable gain adjustment

- Voice-band and sub-audio rejection filtering

- Selectable de-emphasis

- o Software volume control

#### Signalling

- 1 from 39 CTCSS decoder + Tone Clone mode

- o 23/24bit DCS decoder

- Programmable Selcall decoder

- o 1200/2400bps MSK demodulator and 16-bit frame sync detector

- Signal Monitor (RSSI / Microphone / Rx channel level monitor)

#### **Host Interface**

A serial data interface (C-BUS) is used for command, status and data transfers between the CMX881 and the host  $\mu$ C; this interface is compatible with microwire, SPI etc. Interrupt signals notify the host  $\mu$ C when a change in status has occurred and the  $\mu$ C should read the status register across the C-BUS and respond accordingly. Interrupts only occur if the appropriate mask bit has been set. See section 1.6.15.

#### Auxiliary (Signal Monitor) analogue signal

The CMX881 includes a Signal level monitor. This is an 8-bit successive approximation ADC and a two level signal sensor. The two level sensor facility can be used in conjunction with the power saving mode to wake up powered down blocks, and issue an interrupt on the IRQN line when the Signal exceeds the preset threshold level. The auxiliary ADC voltage reference is taken directly from the  $V_{DD}(A)$  supply, so the Signal level being monitored should be derived from this supply voltage.

A power-on reset signal remains asserted for approximately 256 x xtal clock cycles after power is applied and the clock or xtal oscillator is established. It performs the same function as the C-BUS General Reset command (\$01), further details of which are given in section 1.6.2. A temporary loss of power may cause the power-on reset signal to be re-asserted. If this happens, both the C-BUS registers and the Programming register block should be reprogrammed, once power has been restored and a C-BUS General Reset command has been issued. This is to prevent any possibility of data corruption within the device.

Power-on reset or C-BUS general reset places the CMX881 into sleep mode, which results in all internal blocks, except the xtal clock circuit, being placed in power-saved mode. The xtal clock circuit can be power-saved but this must be done by an explicit C-BUS command. Power saving is achieved by turning off bias current sources or disabling local clocks, as appropriate.

During system standby periods, parts of the device can be put into sleep mode by the host to conserve power. The Auxiliary ADC can be programmed so that when the level exceeds a threshold, an interrupt is issued over the C-BUS and the selected mode (Tx or Rx) "woken up" within 400 $\mu$ s. If this time is too long to ensure no part of the signal is lost, the DISC or MIC input and ADC path can be kept powered up whilst in standby mode. The receive modes and transmit modes can also be activated by commands from the C-BUS. On wake up, activation of the various signal path stages are phased appropriately to avoid causing unwanted transients. More details are provided in section 1.6.4 on Signal Routing.

The CMX881 can be programmed to wake up its receive path automatically (automatic start-up) when the DISC input level exceeds the 'high' level threshold. While the CMX881 is in automatic receive start-up mode the DISC input must also be selected for the signal path. When not in automatic start-up mode it is recommended that the required input is selected during Auxiliary ADC operation to avoid subsequent switching of the input signal source.

#### 1.5.2 Auxiliary ADC

This section of the CMX881 operates in both Tx and Rx modes and can be used to monitor one of 4 signal sources: Sig\_Monitor pin, MIC1, Input\_2 or DISC inputs. Activity on the selected input will optionally issue an interrupt if host intervention is required. During idle periods the majority of the CMX881 can be placed into low power mode. If monitoring ac signals connected to the Sig\_Monitor pin they must be rectified and filtered using passive external circuitry.

The Auxiliary ADC facility comprises an 8-bit ADC, a comparator, an 8-bit result data word and two 8-bit threshold registers, one defining the 'Signal high' level and the other the 'Signal low' level. The two threshold registers are combined into one 16-bit C-BUS register word. The ADC measures the Signal level at intervals that are set by C-BUS command.

It is advised that the interval be set to <125 $\mu$ s while waiting for a new incoming signal so that the CMX881 and host  $\mu$ C can be powered up and put into the correct mode in time to avoid missing any part of the signal. The default interval period following a reset is 20.8 $\mu$ s. Power dissipation of the Auxiliary ADC can be reduced by increasing the conversion interval time.

The result of the most recent Auxiliary ADC measurement can be read over the C-BUS whenever the Signal Processing and Aux ADC circuits are powered up.

The Auxiliary ADC compares each conversion result with the values in the 'Signal high' or the 'Signal low' threshold registers. The CMX881 can, for example, issue an interrupt to the host  $\mu$ C to wake up the receive path when the Auxiliary ADC input exceeds the 'high' level threshold. The CMX881 can also issue an interrupt to the host  $\mu$ C to indicate a weak or absent signal when it falls below the 'low' level threshold. This provides a user programmable hysteresis facility. The host must ensure that the value in the 'low' register is always less than that of the 'high' register. The options for issuing interrupts and for automatic start-up are selected by C-BUS command.

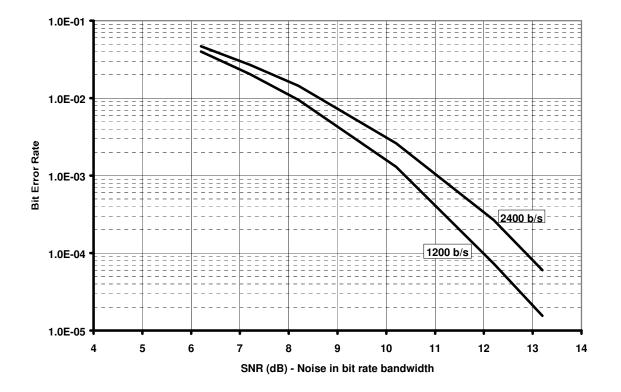

The Auxiliary ADC options are controlled by the \$B2, \$B3 and \$C0 C-BUS registers. The auxiliary ADC data can be read from the \$B4 C-BUS register.

The Auxiliary ADC requires the Auxiliary ADC, BIAS and Xtal clock to all be enabled in the Power Down Control register.

#### 1.5.3 Receive Mode

The CMX881 can receive voice and various signal formats: CTCSS tone, DCS code, Selcall and FFSK/ MSK data at 1200 and 2400bps. Reception of each of these signal types can be independently enabled/disabled by C-BUS command. If enabled, an interrupt will be issued to notify the host  $\mu$ C of the presence and type of the incoming signal.

In receive mode the CMX881 performs signal type identification in 2 frequency bands, sub-audio (60 - 260Hz) and voice band (300 - 3kHz), to determine what type of signal is being received. When an enabled signal is detected this will be indicated to the host over the C-BUS and the CMX881 will continue to process the received signal in its band. Identification / process mode will continue in the other band. The CMX881 can process voice and simultaneously identify and process at least 2 other signal types. See Table 1 for valid combinations.

The receive gain and audio output amplifier gain can be adjusted by the host  $\mu$ C, via C-BUS command, to provide receive signal level adjustment and output volume control or muting.

|                                                                         | Sub-Audio                         | Voice band signalling                                                                                                                                                                                           |

|-------------------------------------------------------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b></b>                                                                 | All combinations of:              | Any one of A - C:                                                                                                                                                                                               |

| With Rx Voice<br>Processing <sup>1</sup> or<br>Audio Tone<br>generation | DCS<br>Inverted DCS<br>CTCSS      | A: None<br>B: Selcall<br>C: 1200bps FFSK/MSK                                                                                                                                                                    |

|                                                                         |                                   |                                                                                                                                                                                                                 |

|                                                                         | Sub-Audio<br>All combinations of: | Voice band signalling <i>Any one of A - G:</i>                                                                                                                                                                  |

| No Voice<br>Processing or<br>Audio Tone<br>generation                   | DCS<br>Inverted DCS<br>CTCSS      | A: None<br>B: Selcall<br>C: 1200bps FFSK/MSK<br>D: 2400bps FFSK/MSK<br>E: 1200 & 2400 bps FFSK/MSK<br>F: Selcall & 1200bps FFSK/MSK<br>G: Selcall & 2400bps FFSK/MSK                                            |

|                                                                         |                                   |                                                                                                                                                                                                                 |

|                                                                         | Sub-Audio<br>All combinations of: | Voice band signalling<br>Any one of A - H:                                                                                                                                                                      |

| No Voice<br>Processing or<br>Audio Tone<br>generation                   | No Subaudio<br>processing         | A: None<br>B: Selcall<br>C: 1200bps FFSK/MSK<br>D: 2400bps FFSK/MSK<br>E: 1200 & 2400 bps FFSK/MSK<br>F: Selcall & 1200bps FFSK/MSK<br>G: Selcall & 2400bps FFSK/MSK<br>H: Selcall & 1200bps & 2400bps FFSK/MSK |

#### Table 1 Concurrent Rx Signalling Modes Supported by the CMX881

1 Including optional de-emphasis

By disabling all the decoding modes, the device can be configured to receive voice only signals with no decoding of the voice band, CTCSS or DCS signalling. This will result in reception of all signals as if they are voice. In this case it is up to the user/host  $\mu$ C to respond appropriately to incoming signals.

The CMX881 operates in half duplex, so whilst in receive mode the transmit path (microphone input and modulator output amplifiers) can be disabled and powered down if required. The AUDIO output signal level is equalised (to  $V_{BIAS}$ ) before switching between the audio port and the modulator ports, to minimise unwanted audible transients. The Off/Power-save level of the modulator outputs is the same as the  $V_{BIAS}$  pin, so the audio output level must also be at this level before switching.

#### 1.5.3.1 Receiving Voice Band Signals

When a voice based signal is being received, it is up to the  $\mu$ C, in response to signal status information provided by the CMX881, to control muting/enabling of the voice band signal to the AUDIO output.

The discriminator path through the device has a programmable gain stage. Whilst in receive mode this should normally be set to 0dB (the default) gain.

#### **Receive Filtering**

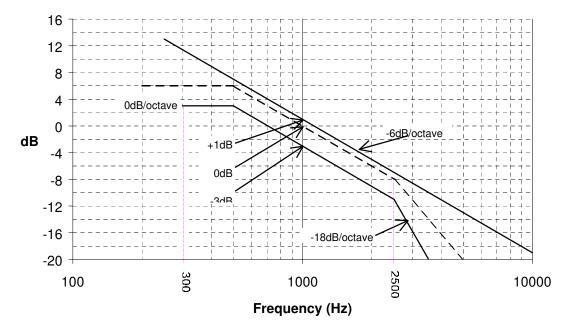

The incoming signal is filtered, as shown in Figure 5, to remove sub-audio components and to minimise high frequency noise. When appropriate the voice signal can then be routed to the AUDIO output.

Figure 5 Rx Audio Filter Frequency Response

#### **De-emphasis**

Optional de-emphasis at -6dB per octave from 300Hz to 3000Hz (shown in Figure 6) can be selected to facilitate compliance with TIA/EIA-603.

Figure 6 De-emphasis Curve for TIA/EIA-603 Compliance

#### **Receiving and Decoding CTCSS Tones** 1.5.3.2

The CMX881 is able to accurately detect valid CTCSS tones quickly to avoid losing the beginning of voice or possibly data transmissions, and is able to continuously monitor the detected tone with minimal probability of falsely dropping out. The received signal is filtered in accordance with the template shown in Figure 7, to prevent signals outside the sub-audio range from interfering with the sub-audio tone detection.

#### Figure 7 Low Pass Sub-Audio Band Filter for CTCSS and DCS

Once a valid CTCSS tone has been detected, the voice band signal can be passed to the audio output. The voice band signal is extracted from the received signal by band pass filtering as shown in Figure 5.

To help decode received CTCSS tones adjustable decoder bandwidths and threshold levels permit decode certainty and signal to noise performance to be traded when congestion or range limits the system performance. This entails setting the tone decoder bandwidth and threshold level in P2.1 of the Programming register (\$C8) and programming the Audio & CTCSS Control register with the desired tone.

Tone Cloning<sup>™</sup>: Tone Cloning<sup>™</sup> facilitates the detection of CTCSS tones 1 to 39 in receive mode. This allows the device to non-predictively detect any tone in this range. The received tone number will be reported in the Tones Status register. This tone code can then be programmed into the 'Audio and Device Address Control' register, by the host  $\mu$ C. The cloned tone will only be active when CTCSS is enabled in the Mode register.

It is recommended that the CTCSS bandwidth selected in Programming Register word P2.1 is set to be sufficiently low to ensure no overlapping of adjacent tones.

$<sup>^{\</sup>mathsf{TM}}$  Tone Cloning is a trademark of CML Microsystems Plc.

#### **CTCSS** Tones

Table 2 lists the CTCSS tones available. The tone numbers are decimal equivalents of the numbers written to the Audio & CTCSS Control register (\$C2) and reported in the Tone Status register (\$CC).

| Tone<br>Number  | Freq.<br>(Hz) | Tone<br>Number | Freq.<br>(Hz) | Tone<br>Number  | Freq.<br>(Hz) |

|-----------------|---------------|----------------|---------------|-----------------|---------------|

| 00 <sup>1</sup> | No Tone       | 20             | 131.8         | 40-54           | Reserved      |

| 01              | 67.0          | 21             | 136.5         | 55 <sup>2</sup> | Invalid       |

| 02              | 71.9          | 22             | 141.3         |                 | tone          |

| 03              | 74.4          | 23             | 146.2         | >=56            | Reserved      |

| 04              | 77.0          | 24             | 151.4         |                 |               |

| 05              | 79.7          | 25             | 156.7         |                 |               |

| 06              | 82.5          | 26             | 162.2         |                 |               |

| 07              | 85.4          | 27             | 167.9         |                 |               |

| 08              | 88.5          | 28             | 173.8         |                 |               |

| 09              | 91.5          | 29             | 179.9         |                 |               |

| 10              | 94.8          | 30             | 186.2         |                 |               |

| 11              | 97.4          | 31             | 192.8         |                 |               |

| 12              | 100.0         | 32             | 203.5         |                 |               |

| 13              | 103.5         | 33             | 210.7         |                 |               |

| 14              | 107.2         | 34             | 218.1         |                 |               |

| 15              | 110.9         | 35             | 225.7         |                 |               |

| 16              | 114.8         | 36             | 233.6         |                 |               |

| 17              | 118.8         | 37             | 241.8         |                 |               |

| 18              | 123.0         | 38             | 250.3         |                 |               |

| 19              | 127.3         | 39             | 69.3          |                 |               |

| Tabl | e 2 | CTCS | S Toi                         | าคร |

|------|-----|------|-------------------------------|-----|

| ιαν  |     |      | $\mathbf{v}$ i $\mathbf{v}$ i | 103 |

#### Notes:

- 1 Tone number 00 in the Tone Status register (\$CC) indicates that none of the above subaudio tones is being detected see also section 1.6.19. If tone number 00 is programmed into the Audio & CTCSS Control register (\$C2) no tone will be scanned for. If CTCSS transmit is selected this tone setting will cause the CTCSS generator to output no signal.

- 2 Tone number 55 is reported in the Tone Status register (\$CC), when CTCSS receive is enabled and a subaudio tone is detected that does not correspond to the selected tone. This could be a tone in the subaudio band which is not in the table or a tone in the table which is not the selected tone.

#### 1.5.3.3 Receiving and Decoding DCS Codes

DCS Code is in NRZ format and transmitted at 134.4  $\pm$ 0.4bps. The CMX881 is able to decode any 23 or 24 bit pattern in either of the two DCS modulation modes defined by TIA/EIA-603 and described in Table 3. The CMX881 can detect a valid DCS Code quickly enough to avoid losing the beginning of voice transmissions.

| Modulation Type: | Data Bit: | FM Frequency Change:  |

|------------------|-----------|-----------------------|

| A                | 0         | Minus frequency shift |

|                  | 1         | Plus frequency shift  |

| В                | 0         | Plus frequency shift  |

|                  | 1         | Minus frequency shift |

| Table 3 DCS Modulation M |

|--------------------------|

|--------------------------|

The CMX881 detects the DCS code that matches the programmed code defined in the 'DCS Code' words (P2.2-3) in the Programming register (\$C8).

To detect the pre-programmed DCS code the signal is low pass filtered to suppress all but the sub-audio band using the filter shown in Figure 7. Further equalisation filtering, signal slicing and level detection are done to extract the code being received. The extracted code is then matched with the programmed 23 or 24-bit DCS code to be recognised, in the order least significant first through to most significant DCS code bit last. Table 4 shows a selection of valid 23-bit DCS codes, this does not preclude other codes being programmed. Recognition of a valid DCS Code will be flagged if the decode is successful (3 or less errors). A failure to decode is indicated by a '0' flag. This flag is updated after the decoding of every 4th bit of the incoming signal.

Once a valid DCS Code has been detected, the voice band signal can be passed to the AUDIO output under the control of the host µC. The voice signal is extracted from the received input signal by band pass filtering; see Figure 5. More details for programming DCS Codes are provided in section 1.6.20.3.

The end of DCS transmissions is indicated by a 134.4 ±0.5Hz tone for 150-200ms. To detect the DCS turn off tone while receiving DCS, the DCS turn off tone option must be selected in the Audio and CTCSS Control (\$C2) register. When a DCS turn off tone is detected it will cause a DCS interrupt; the receiver audio output can then be muted by the host.

| DCS<br>Code | DCS<br>bits<br>22-12 | DCS<br>bits<br>11-0 | DCS<br>Code |     | DCS<br>bits<br>11-0 | DCS<br>Code | DCS<br>bits<br>22-12 | DCS<br>bits<br>11-0 |

|-------------|----------------------|---------------------|-------------|-----|---------------------|-------------|----------------------|---------------------|

| 023         | 763                  | 813                 | 174         | 18B | 87C                 | 445         | 7B8                  | 925                 |

| 025         | 6B7                  | 815                 | 205         | 6E9 | 885                 | 464         | 27E                  | 934                 |

| 026         | 65D                  | 816                 | 223         | 68E | 893                 | 465         | 60B                  | 935                 |

| 031         | 51F                  | 819                 | 226         | 7B0 | 896                 | 466         | 6E1                  | 936                 |

| 032         | 5F5                  | 81A                 | 243         | 45B | 8A3                 | 503         | 3C6                  | 943                 |

| 043         | 5B6                  | 823                 | 244         | 1FA | 8A4                 | 506         | 2F8                  | 946                 |

| 047         | 0FD                  | 827                 | 245         | 58F | 8A5                 | 516         | 41B                  | 94E                 |

| 051         | 7CA                  | 829                 | 251         | 627 | 8A9                 | 532         | 0E3                  | 95A                 |

| 054         | 6F4                  | 82C                 | 261         | 177 | 8B1                 | 546         | 19E                  | 966                 |

| 065         | 5D1                  | 835                 | 263         | 5E8 | 8B3                 | 565         | 0C7                  | 975                 |

| 071         | 679                  | 839                 | 265         | 43C | 8B5                 | 606         | 5D9                  | 986                 |

| 072         | 693                  | 83A                 | 271         | 794 | 8B9                 | 612         | 671                  | 98A                 |

| 073         | 2E6                  | 83B                 | 306         | 0CF | 8C6                 | 624         | 0F5                  | 994                 |

| 074         | 747                  | 83C                 | 311         | 38D | 8C9                 | 627         | 01F                  | 997                 |

| 114         | 35E                  | 84C                 | 315         | 6C6 | 8CD                 | 631         | 728                  | 999                 |

| 115         | 72B                  | 84D                 | 331         | 23E | 8D9                 | 632         | 7C2                  | 99A                 |

| 116         | 7C1                  | 84E                 | 343         | 297 | 8E3                 | 654         | 4C3                  | 9AC                 |

| 125         | 07B                  | 855                 | 346         | 3A9 | 8E6                 | 662         | 247                  | 9B2                 |

| 131         | 3D3                  | 859                 | 351         | 0EB | 8E9                 | 664         | 393                  | 9B4                 |

| 132         | 339                  | 85A                 | 364         | 685 | 8F4                 | 703         | 22B                  | 9C3                 |

| 134         | 2ED                  | 85C                 | 365         | 2F0 | 8F5                 | 712         | 0BD                  | 9CA                 |

| 143         | 37A                  | 863                 | 371         | 158 | 8F9                 | 723         | 398                  | 9D3                 |

| 152         | 1EC                  | 86A                 | 411         | 776 | 909                 | 731         | 1E4                  | 9D9                 |

| 155         | 44D                  | 86D                 | 412         | 79C | 90A                 | 732         | 10E                  | 9DA                 |

| 156         | 4A7                  | 86E                 | 413         | 3E9 | 90B                 | 734         | 0DA                  | 9DC                 |

| 162         | 6BC                  | 872                 | 423         | 4B9 | 913                 | 743         | 14D                  | 9E3                 |

| 165         | 31D                  | 875                 | 431         | 6C5 | 919                 | 754         | 20F                  | 9EC                 |

| 172         | 05F                  | 87A                 | 432         | 62F | 91A                 |             |                      |                     |

#### Table 4 DCS 23 Bit Codes

#### **Receiving and Decoding Selcall Tones** 1.5.3.4

Selcall tones can be used to flag the start and end of a call. They may also occur during a call in which case the tone may be audible at the receiver. If enabled, an interrupt will be issued when a signal matching a valid Selcall tone is detected and when a present Selcall tone turns off or changes (i.e. at the start and at the end of each Selcall tone). The audio path can then be turned on and off at the appropriate times under control of the host  $\mu$ C.

The CMX881 implements a fully programmable Selcall encoder / decoder. The frequency of each tone is defined in the Program registers P1.2-18. See section 1.6.20 for programming details.

In receive the CMX881 scans through the tone table sequentially, the code reported will be the first one that matches the incoming frequency.

Adjustable decoder bandwidths, threshold levels are programmable via the Programming register and permits certainty of detection and signal to noise performance to be traded when congestion or range limits the system performance. The Selcall signal is derived from the received input signal after the band pass filtering shown in Figure 5.

Table 5 lists the Selcall codes available, these are 5 bit numbers set or reported in: Tx Tone register (\$C3) and Tone Status register (\$CC).

| S     |      | Information Tones<br>(5 <sup>th</sup> bit = 0) |       | Normal Tones<br>(5 <sup>th</sup> bit = 1) |                    |  |  |

|-------|------|------------------------------------------------|-------|-------------------------------------------|--------------------|--|--|

| 4 bit | Code | Frequency set in                               | 4 bit | Code                                      | Frequency set in   |  |  |

| Dec   | Hex  | Program register:                              | Dec   | Hex                                       | Program register:  |  |  |

| 0     | 0    | No Tone                                        | 0     | 0                                         | P1.3 <sup>1</sup>  |  |  |

| 1     | 1    |                                                | 1     | 1                                         | P1.4 <sup>1</sup>  |  |  |

| 2     | 2    |                                                | 2     | 2                                         | P1.5 <sup>1</sup>  |  |  |

| 3     | 3    |                                                | 3     | 3                                         | P1.6 <sup>1</sup>  |  |  |

| 4     | 4    |                                                | 4     | 4                                         | P1.7 <sup>1</sup>  |  |  |

| 5     | 5    |                                                | 5     | 5                                         | P1.8 <sup>1</sup>  |  |  |

| 6     | 6    | 1 10                                           | 6     | 6                                         | P1.9 <sup>1</sup>  |  |  |

| 7     | 7    | 1-13<br>Reserved                               | 7     | 7                                         | P1.10 <sup>1</sup> |  |  |

| 8     | 8    | Reserved                                       | 8     | 8                                         | P1.11 <sup>1</sup> |  |  |

| 9     | 9    |                                                | 9     | 9                                         | P1.12 <sup>1</sup> |  |  |

| 10    | Α    |                                                | 10    | Α                                         | P1.13 <sup>1</sup> |  |  |

| 11    | В    |                                                | 11    | В                                         | P1.14 <sup>1</sup> |  |  |

| 12    | С    |                                                | 12    | С                                         | P1.15 <sup>1</sup> |  |  |

| 13    | D    |                                                | 13    | D                                         | P1.16 <sup>1</sup> |  |  |

| 14    | E    | P1.2 <sup>1,2</sup>                            | 14    | E                                         | P1.17 <sup>1</sup> |  |  |

| 15    | F    | Unrecognised tone                              | 15    | F                                         | Unrecognised tone  |  |  |

#### Table 5 Selcall Tones

Notes:

- 1 Special tone 14, and Normal tones 0 15 provide user programmable tone options for both transmit and receive modes as set in the indicated Program register, for programming information see section 1.6.20.2. To ensure correct operation tones should not be programmed with overlapping detect bandwidths.

- 2 Special tone 14 is the repeat tone, this code must be used in transmit when the new code to be sent is the same as the previous one. e.g. to send '333' the sequence '3R3' should be sent, where 'R' is the repeat tone. When receiving Selcall tones the CMX881 will indicate the repeat tone when it is received, it is up to the host to interpret this and decode tones accordingly.

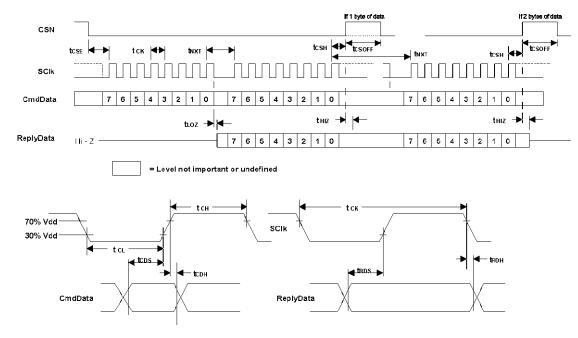

The CMX881 can decode incoming FFSK/MSK signals at either 1200 or 2400 baud data rates. It can achieve this by deriving the baud rate from the received signal. Alternatively a control word may set the baud rate, in which case the device only responds to signals operating at that rate. The form of FFSK/MSK signals for these baud rates, excluding noise, is shown in Figure 11.

The received signal is filtered and data is extracted. A PLL is used to extract the clock from the recovered serial data stream. The recovered data is stored in a 1 byte buffer and an interrupt issued to indicate received data is ready. Data is transferred over the C-BUS, controlled by host instructions. If this data is not read before the next data is decoded it will be overwritten. The MSK bit clock is not output externally. It is up to the user to ensure that the data is transferred at an adequate rate following data ready being flagged, see Table 9.

The extracted data is compared with up to three 16-bit programmed frame sync patterns (SYND, SYNC and it's inverse SYNT). SYNC and SYND are both preset to \$C4D7 following a RESET command. An interrupt will be flagged when the programmed frame sync pattern is detected. The host may stop the frame sync search by disabling the MSK demodulator.

FFSK may be transmitted in conjunction with a CTCSS or DCS sub-audio component. The device will handle the sub-audio signals as already described. If a sub-audio signal turns off during reception of FFSK, it is up to the host  $\mu$ C to turn off the FFSK decoding as the device will continue receiving and processing the incoming signal until commanded otherwise by the host  $\mu$ C.

The host must keep track of the message length or otherwise determine the end of reception (e.g. by using sub-audio information or the Auxiliary ADC to check for signal level) and disable the FFSK demodulator at the appropriate time.

The device operates in half duplex, so when the device is in transmit mode the receive path (discriminator and audio output amplifiers) should be disabled, and can be powered down, by the host  $\mu$ C.

Two modulator outputs with independently programmable gains are provided to facilitate single or twopoint modulation, separate sub-audio and voice band outputs. If one of the modulator outputs is not used it can be disabled to conserve power.

To avoid erroneous transmission of out of band frequencies when changing from Rx to Tx the MOD\_1 and MOD\_2 outputs are ramped to the quiescent modulator output level,  $V_{BIAS}$  before switching. Similarly, when starting a transmission, the transmitted signal strength is ramped up from the quiescent  $V_{BIAS}$  level and when ending a transmission the transmitted signal strength is ramped down to the quiescent  $V_{BIAS}$  level. The ramp rates are set in the Programming register P4.6. When the modulator outputs are disabled, their outputs will be set to  $V_{BIAS}$ . When the modulator output drivers are powered down, their outputs will be floating (high impedance), so the RF modulator will need to be turned off.

Table 6 Concurrent Tx Modes Supported by the CMX881

| Sub-Audio |   | Voice band |

|-----------|---|------------|

| CTCSS     |   |            |

| CTCSS     | + | Voice      |

| CTCSS     | + | Selcall    |

| CTCSS     | + | FFSK/MSK   |

| CTCSS     | + | DTMF       |

| DCS       |   |            |

| DCS       | + | Voice      |

| DCS       | + | Selcall    |

| DCS       | + | DTMF       |

| DCS       | + | FFSK/MSK   |

|           |   | Voice      |

|           |   | Selcall    |

|           |   | DTMF       |

|           |   | FFSK/MSK   |

For all transmissions the host must only enable signals after the appropriate data and settings for those signals are loaded into the C-BUS registers. As soon as any signalling is enabled the CMX881 will use the settings to control the way information is transmitted.

A programmable gain stage in the microphone input path facilitates a host controlled VOGAD capability.

#### 1.5.4.1 Processing Voice Signals for Transmission over Analogue Channels

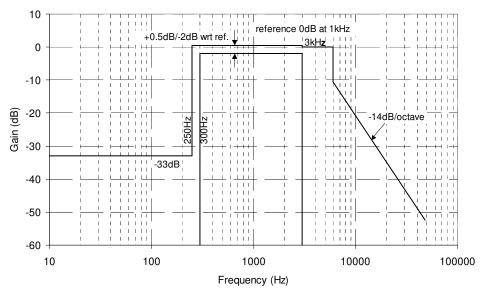

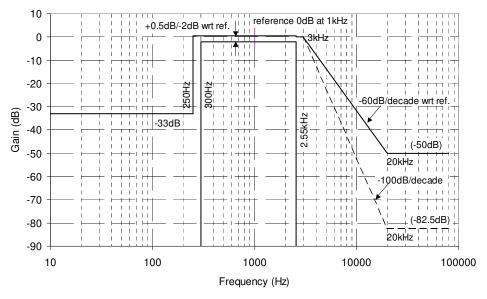

The microphone input(s), with programmable gain, can be selected as the voice input source. Preemphasis is selectable with either version of the 2 analogue Tx audio filters (for 12.5kHz and 25kHz channel spacing). These are designed for use in ETS-300-086 and/or TIA/EIA-603 compliant applications. Both filters attenuate sub-audio frequencies below 250Hz by more than 33dB wrt the signal level at 1kHz. These filters together with a built in limiter help ensure compliance with ETS-300-086 (25kHz and 12.5kHz channel spacing) when levels and gain settings are set up correctly in the target system.

Figure 8 25kHz Channel Audio Filter Response Template

The filter characteristics of the 12.5kHz channel filter fits the filter template shown in Figure 9 (solid outline). This filter also facilitates implementation of systems compliant with TIA/EIA-603 'A' and 'B' bands. To achieve attenuation above 3kHz of better than -100dB/decade for TIA/EIA-603 'C' bands (dashed outline), additional external circuitry is required, such as suggested in section 1.4.2.

Figure 9 12.5kHz Channel Audio Filter Response Template

The CMX881 provides selectable pre-emphasis filtering of +6dB per octave from 300Hz to 3000Hz, matching the template shown in Figure 10.

Figure 10 Audio Frequency Pre-emphasis Template

#### Modulator Output Routing

The sub-audio component can be combined with the voice band signal and this composite signal routed to both MOD\_1 and MOD\_2 outputs, or the sub-audio and voice band signal can be output separately (sub-audio to MOD\_2 and voice band to MOD\_1), in accordance with the settings of the Signal Routing register (\$B1).

#### 1.5.4.2 CTCSS Tone

The sub-audio CTCSS tone generated is defined in the Audio & CTCSS Control register (\$C2). Table 2 lists the CTCSS tones and the corresponding value for programming the TX TONE bits.

#### 1.5.4.3 DCS Code

A 23 or 24-bit sub-audio DCS Code can be generated, as defined by the 'DCS Code' words (P2.2-3) of the Programming register (\$C8); the same DCS Code pattern is used for detection and transmission. The DCS Code is NRZ encoded at 134.4±0.4 bits/s, low pass filtered and added to the voice band signal, prior to passing the signal to the modulator output stages. Valid 23-bit DCS codes and the corresponding settings for the DCS Code Register are shown in Table 4, this does not preclude other codes being programmed. The least significant bit of the DCS code is transmitted first and the most significant bit is transmitted last. The CMX881 is able to encode and transmit either of the two DCS modulation modes defined by TIA/EIA-603 and described in Table 3.

To signal the end of the DCS transmission, the host should set the special sub-audio bits in the Audio & CTCSS Control register (\$C2) to enable the DCS turn off tone for 150ms to 200ms. After this time period has elapsed the host should then disable DCS in the Mode register (\$C1). Do not enable CTCSS in the Mode Control (\$C1) register when transmitting the DCS turn off tone. To summarize, detection of DCS turn off tone requires the CTCSS decoder to be enabled, whereas generation of the DCS turn off tone requires the CTCSS encoder to be disabled.

The Selcall tone to be generated is defined in the Tx In-Band Tones register (\$C3). The tone level is set in the Programming register (P1.0). The Selcall tone must be transmitted without other signals in the voice band, so when either In-band signalling bit is selected, the voice path is automatically disabled. The voice path bit should not be set to '0' at this time, as this produces anomalous results. However, the voice path can be disabled by setting bits 4 and 5 to '00' in the Signal Routing register (\$B1). Table 5 shows valid Selcall tones, together with the values for programming the Selcall bits of the Tx In-Band Tones register.

Custom Selcall tone frequencies are set in the program register (\$C8) P1.2-17. See section 1.6.20.2 for programming details.

#### 1.5.4.5 Transmitting FFSK/MSK Signals

The FFSK/MSK encoding operates in accordance with the bit settings in the Mode Control register (\$C1). When enabled the MSK modulator begins transmitting data using the settings and values in the Tx Data register. Therefore, these registers should be programmed to the required value before transmission is enabled.

The CMX881 generates it's own internal data clock and converts the binary data into the appropriately phased frequencies, as shown in Figure 11 and Table 7. The binary data is taken from register \$CA, most significant bit first. The following data words must be provided over the C-BUS within certain time limits to ensure the selected baud rate is maintained. The time limits will be dependent on the data coding being used, see Table 9.

Figure 11 Modulating Waveforms for 1200 and 2400 Baud FFSK/MSK Signals

The table below shows the combinations of frequencies and number of cycles to represent each bit of data, for both baud rates.

Table 7 Data Frequencies for each Baud Rate

| Baud Rate | Data | Frequency | Number of Cycles |

|-----------|------|-----------|------------------|

| 1200 baud | 1    | 1200Hz    | one              |

|           | 0    | 1800Hz    | one and a half   |

| 2400 baud | 1    | 1200Hz    | half             |

|           | 0    | 2400Hz    | one              |

Note: FFSK may be transmitted in conjunction with a CTCSS or DCS sub-audio component.

#### 1.5.4.6 Transmitting DTMF Tones

The DTMF signals to be generated are defined in the TX TONE register (\$C3). Single tones and twist (lower frequency tone reduced by 2dB) can be enabled by setting the appropriate bit in the \$C3 register to '1'. The DTMF level is set in programming register P1.0. The DTMF tones must be transmitted on their own within the voice band, the host  $\mu$ C must disable other voice band signals prior to initiating transmission of the DTMF tones, and (if required) restore the voice band signals after the DTMF transmission is complete. Table 8 shows the DTMF tone pairs, together with the values for programming the 'Tone Pair' field of the TX TONE register.

| Tone Pair  | Key Pad  | Low Tone   | High Tone   |

|------------|----------|------------|-------------|

| Code (Hex) | Position | (Hz)       | (Hz)        |

| 1          | 1        | <u>697</u> | 1209        |

| 2          | 2        | <u>697</u> | 1336        |

| 3          | 3        | <u>697</u> | 1477        |

| 4          | 4        | <u>770</u> | 1209        |

| 5          | 5        | <u>770</u> | 1336        |

| 6          | 6        | <u>770</u> | 1477        |

| 7          | 7        | <u>852</u> | 1209        |

| 8          | 8        | 852        | <u>1336</u> |

| 9          | 9        | 852        | <u>1477</u> |

| A          | 0        | 941        | <u>1336</u> |

| В          | *        | 941        | <u>1209</u> |

| С          | #        | 941        | <u>1477</u> |

| D          | А        | 697        | <u>1633</u> |

| E          | В        | 770        | <u>1633</u> |

| F          | С        | 852        | <u>1633</u> |

| 0          | D        | <u>941</u> | 1633        |

Table 8 DTMF Tone Pairs and Corresponding Tx Programming Codes

Note: Only the underlined tone is generated when the 'Single Tone' bit is enabled.

#### 1.5.5 FFSK/MSK Data packeting

The CMX881 has a built in 15 bit CRC and 1 bit parity generator / checker to ease host processing during transmission and reception of data packets. The CRC / parity function can be used with any length message in both Tx and Rx modes. In Tx the host may reset, add to or send the 2 byte checksum at any byte boundary in the data sequence. In Rx the host may reset the checking circuit at any byte boundary and the CMX881 will indicate for each subsequent byte if the preceding bytes satisfied the CRC and parity requirements.

#### Tx frame example:

#### Rx frame example:

| in nume examplei              |    |    |         |       |     |      |     |        |      |      |      |      |   |   |

|-------------------------------|----|----|---------|-------|-----|------|-----|--------|------|------|------|------|---|---|

| Rx over air data —            | BS | BS | FS      | FS    | 0   | 1    | 2   | 3      | CS   | CS   | 0    | 1    | 2 |   |

| Write Mode reg <sup>2</sup>   |    |    |         |       |     |      |     |        |      |      |      |      |   |   |

| Frame Sync flag               |    |    |         |       |     |      |     |        |      |      |      |      |   |   |

| MSK transfer flag             |    |    |         |       |     |      |     |        |      |      |      |      |   |   |

| Read Status reg <sup>2</sup>  |    |    |         |       |     |      |     |        |      |      |      |      |   |   |

| Checksum bit <sup>3</sup>     |    |    |         |       |     |      |     |        |      |      |      |      |   |   |

| Read Rx Data reg <sup>2</sup> |    |    |         |       |     | 0    | 1   | 2      | 3    | CS   | CS   | 0    | 1 | 2 |

| Enable CRC bit <sup>2,1</sup> |    |    |         |       |     |      |     |        |      |      |      |      |   |   |

| BS = Bit syne                 | С  | FS | 6 = Fra | ame s | ync | 0, 1 | , D | ata by | /tes | CS = | Chec | ksum |   |   |

|                               |    |    |         |       |     |      |     |        |      |      |      |      |   |   |

Notes: 1 The Enable CRC bit is controlled by writing to the Tx Data register 2 Actions requiring a C-BUS transfer 3 The Checksum bit is read from the Rx Data register

#### 5 The Checksum bit is read nom the RX Da

#### 1.5.5.1 Tx Hang bit

When transmitting FFSK/MSK data, the user should ensure that the data is terminated with a hang bit. This is recommended regardless of whether the on-chip data formatting is used. To do this, the host must set the 'Last Data' bit in the Tx Data register (\$CA) when the message is required to end. This will append a hang bit onto the end of the current byte and generate (if enabled) an interrupt when the last Tx data has left the modulator.

| Write Mode reg <sup>2</sup>  |                                                             |

|------------------------------|-------------------------------------------------------------|

| MSK transfer flag            |                                                             |

| Tx MSK end flag              |                                                             |

| Read Status reg <sup>2</sup> |                                                             |

| Write Tx Data reg 2          | BS BS FS FS 0 1 2 3                                         |

| Enable CRC bit <sup>1</sup>  |                                                             |

| Tx CRC bit <sup>1</sup>      |                                                             |

| Last Data bit 1              |                                                             |

| Tx over air data -           | BS BS FS FS 0 1 2 3 CS CS H                                 |

| BS = Bit sync                | FS = Frame sync 0, 1, Data bytes CS = Checksum H = Hang Bit |

|                              |                                                             |

Notes: 1 The Tx CRC, Enable CRC and Last Data bits are changed by writing to the Tx Data register 2 Actions requiring a C-BUS transfer

#### 1.5.5.2 Data Buffer Timing

Data must be transferred at the rate appropriate to the signal type and data format. The CMX881 buffers signal data in the lower 8-bits of a 16-bit register. The CMX881 will issue interrupts to indicate when data is available or required. The host must respond to these interrupts within the maximum allowable latency for the signal type. Table 9 shows the maximum latencies for transferring signal data to maintain appropriate data throughput.

| Data type   | Max time to read from<br>or write to data buffer | Data buffer<br>size |

|-------------|--------------------------------------------------|---------------------|

| 1200b/s MSK | 6.6ms                                            | 8 bits              |

| 2400b/s MSK | 3.3ms                                            | 8 bits              |

| Table 9 | Maximum | Data | Transfer | Latency |

|---------|---------|------|----------|---------|

|---------|---------|------|----------|---------|

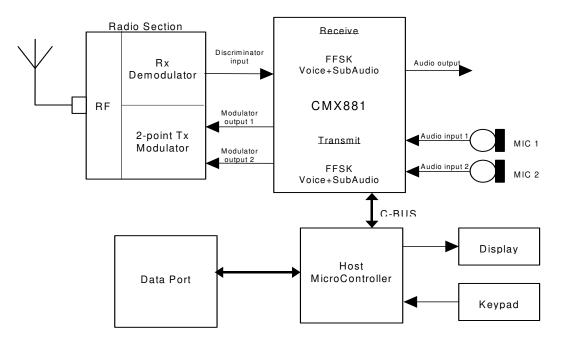

#### 1.5.6 C-BUS Operation

This block provides for the transfer of data and control or status information between the CMX881's internal registers and the  $\mu$ C over the C-BUS serial interface. Each transaction consists of a single Register Address byte sent from the  $\mu$ C which may be followed by one or more data byte(s) sent from the  $\mu$ C to be written into one of the CMX881's Write Only Registers, or one or more data byte(s) read out from one of the CMX881's Read Only Registers, as illustrated in Figure 12.

Data sent from the  $\mu$ C on the Command Data line is clocked into the CMX881 on the rising edge of the Serial\_Clock input. Reply Data sent from the CMX881 to the  $\mu$ C is valid when the Serial\_Clock is high. The CSN line must be held low during a data transfer and kept high between transfers. The C-BUS interface is compatible with most common  $\mu$ C serial interfaces and may also be easily implemented with general purpose  $\mu$ C I/O pins controlled by a simple software routine.

The number of data bytes following an A/C byte is dependent on the value of the A/C byte. The most significant bit of the address or data are sent first. For detailed timings see section 1.8.1.

- 1. For Command byte transfers only the first 8 bits are transferred (\$01 = Reset).

- 2. For single byte data transfers only the first 8 bits of the data are transferred.

- 3. The CMD\_DATA and REPLY\_DATA lines are never active at the same time. The Address byte determines the data direction for each C-BUS transfer.

- 4. The Serial\_Clock input can be high or low at the start and end of each C-BUS transaction.

- 5. The gaps shown between each byte on the CMD\_DATA and REPLY\_DATA lines in the above diagram are optional, the host may insert gaps or concatenate the data as required.

#### 1.6 C-BUS Register Description

#### 1.6.1 C-BUS Register Summary

#### C-BUS Write Only Registers

| ADDR.<br>(hex) | REGISTER                  | Word Size<br>(bits) |

|----------------|---------------------------|---------------------|

| \$01           | C-BUS RESET               | 0                   |

| \$B0           | ANALOGUE GAIN             | 16                  |

| \$B1           | SIGNAL ROUTING            | 16                  |

| \$B2           | AUXILIARY ADC THRESHOLDS  | 16                  |

| \$B3           | AUXILIARY ADC CONTROL     | 8                   |

| \$C0           | POWER DOWN CONTROL        | 16                  |

| \$C1           | MODE CONTROL              | 16                  |

| \$C2           | AUDIO & CTCSS CONTROL     | 16                  |

| \$C3           | TX IN-BAND TONES          | 16                  |

| \$C7           | RESERVED REGISTER ADDRESS | 16                  |

| \$C8           | PROGRAMMING REGISTER      | 16                  |

| \$CA           | TX DATA                   | 16                  |

| \$CB           | RESERVED REGISTER ADDRESS | 16                  |

| \$CD           | AUDIO TONE                | 16                  |

| \$CE           | INTERRUPT MASK            | 16                  |

| \$CF           | RESERVED REGISTER ADDRESS | 16                  |

The C-BUS addresses \$C7, \$CB and \$CF are allocated for production testing and must not be accessed in normal operation.

#### **C-BUS Read Only Registers**

| ADDR<br>(hex) | REGISTER                  | Word Size<br>(bits) |

|---------------|---------------------------|---------------------|

| \$B4          | AUX ADC MONITOR DATA      | 8                   |

| \$C5          | RX DATA                   | 16                  |

| \$C6          | STATUS                    | 16                  |

| \$C9          | RESERVED REGISTER ADDRESS | 16                  |

| \$CC          | TONE STATUS               | 16                  |

#### Interrupt Operation

The CMX881 will issue an interrupt on the IRQN line when the IRQ bit (bit 15) of the Status register and the IRQ Mask bit (bit 15) are both set to '1'. The IRQ bit is set when the state of the interrupt flag bits in the Status register change from a '0' to a '1' and the corresponding mask bit(s) in the Interrupt Mask register is(are) set.

All interrupt flag bits in the Status register except the Programming Flag (bit 0) are cleared and the interrupt request is cleared following the command/address phase of a C-BUS read of the Status register. The Programming Flag bit is set to '1' only when it is permissible to write a new word to the Programming register.

#### 1.6.2 \$01 C-BUS RESET: address only.