# Lattice **CORE**

## SGMII and Gb Ethernet PCS IP Core User's Guide

# **Table of Contents**

| Chapter 1. Introduction                                          | 4   |

|------------------------------------------------------------------|-----|

| Quick Facts                                                      |     |

| Features                                                         | 5   |

| Chapter 2. Functional Description                                | 6   |

| Transmit Rate Adaptation                                         |     |

| Transmit State Machine                                           |     |

| Soft Receive Clock Tolerance Compensation (CTC) Circuit          |     |

| Synchronization State Machine                                    |     |

| Receive State Machine                                            |     |

| Receive Rate Adaptation                                          |     |

| Auto-Negotiation State Machine                                   | 9   |

| Collision Detect                                                 | 11  |

| Carrier Sense                                                    | 12  |

| Data Path Latency Specifications                                 | 12  |

| Signal Descriptions                                              | 13  |

| Chapter 3. Parameter Settings                                    | 17  |

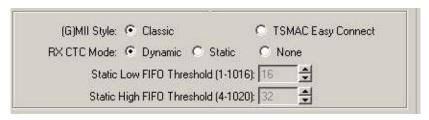

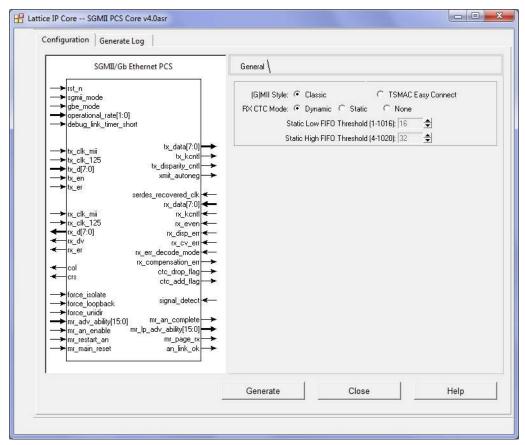

| General Tab                                                      | 17  |

| (G)MII Style                                                     | 17  |

| RX CTC Mode                                                      | 17  |

| Static CTC FIFO Low Threshold                                    | 17  |

| Static CTC FIFO High Threshold                                   | 18  |

| Guidelines for Calculating Static CTC FIFO Thresholds            | 18  |

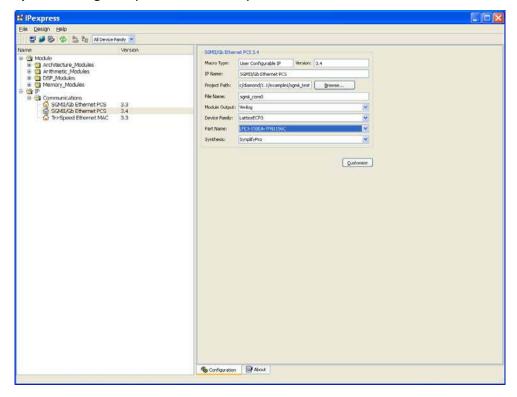

| Chapter 4. IP Core Generation                                    | 19  |

| IP Core Generation in IPexpress                                  | 19  |

| Licensing the IP Core                                            |     |

| Getting Started                                                  |     |

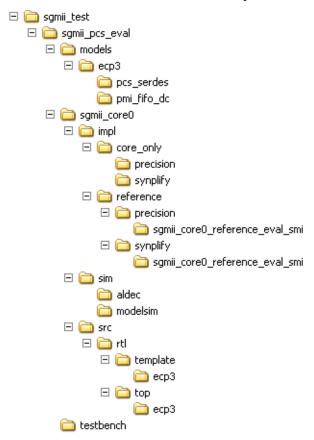

| IPexpress-Created Files and Top Level Directory Structure        |     |

| Instantiating the Core                                           |     |

| Running Functional Simulation                                    |     |

| Synthesizing and Implementing the Core in a Top-Level Design     |     |

| Hardware Evaluation                                              |     |

| Updating/Regenerating the IP Core                                |     |

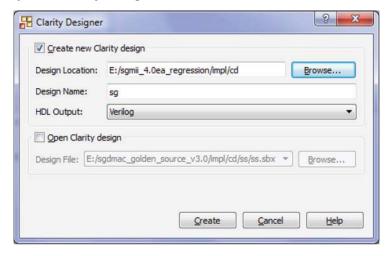

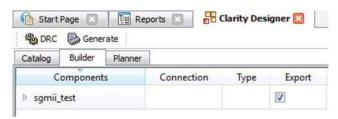

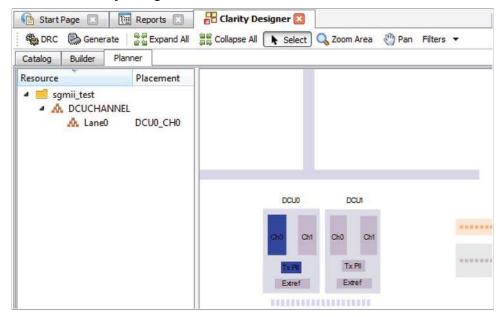

| IP Core Generation in Clarity Designer                           |     |

| Getting Started                                                  |     |

| Clarity Designer Created Files and Top Level Directory Structure |     |

| Simulation Evaluation                                            |     |

| IP Core Implementation                                           |     |

| Regenerating an IP Core in Clarity Designer Tool                 |     |

| Recreating an IP Core in Clarity Designer Tool                   |     |

| Chapter 5. Application Support                                   |     |

| SGMII-to-(G)MII Reference Design                                 |     |

| Features                                                         |     |

| Detailed Description                                             |     |

| The SGMII and Gb Ethernet PCS IP Core                            |     |

| PCS/SERDES                                                       |     |

| Rate Resolution                                                  |     |

| Control Registers(G)MII I/O Logic                                |     |

| Signal Descriptions                                              |     |

| OIGHAI DESCRIPTIONS                                              | 4 I |

© 2014 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Chapter 6. Core Validation       | 43 |

|----------------------------------|----|

| Chapter 7. Support Resources     |    |

| Lattice Technical Support        |    |

| E-mail Support                   |    |

| Local Support                    |    |

| Internet                         | 44 |

| References                       | 44 |

| LatticeECP3                      |    |

| ECP5                             | 44 |

| Revision History                 | 45 |

| Appendix A. Resource Utilization | 46 |

| LatticeECP3 FPGAs                |    |

| Supplied Netlist Configurations  | 46 |

| ECP5 FPGAs                       |    |

| Supplied Netlist Configurations  |    |

## Introduction

The Lattice SGMII and Gb Ethernet PCS IP core implements the PCS functions of both the Cisco SGMII and the IEEE 802.3z (1000BaseX) specifications. The PCS mode is pin selectable. This IP core may be used in bridging applications and/or PHY implementations.

The Serial Gigabit Media Independent Interface (SGMII) is a connection bus for Ethernet Media Access Controllers (MACs) and Physical Layer Devices (PHYs) defined by Cisco Systems. It replaces the classic 22-wire GMII connection with a low pin count, 4-pair, differential SGMII connection. The classic GMII interface defined in the IEEE802.3 specification is strictly for Gigabit rate operation. However, the Cisco SGMII specification defines a method for operating 10 Mbps and 100 Mbps MACs over the interface. Moreover, the Cisco SGMII specification is comprised of more than just a bus interface definition; it defines a bridging function between SGMII and GMII buses.

These applications can be completely implemented in ECP5™ and LatticeECP3™ Field Programmable Gate Array (FPGA) devices. As an example, Lattice has developed a reference design for a complete SGMII-to-(G)MII bridge. This reference design is included with the SGMII and Gb Ethernet PCS IP Core package and is described in detail in "SGMII-to-(G)MII Reference Design" on page 33.

This document describes the IP core's operation, and provides instructions for generating the core through Lattice's IPexpress™ tool, and for instantiating, synthesizing, and simulating the core.

#### **Quick Facts**

Table 1-1 gives quick facts about the Lattice SGMII and Gb Ethernet PCS core.

Table 1-1. Lattice SGMII and Gb Ethernet PCS IP Core Quick Facts

|                         | Γ                            | SGMII and Gb Etherr                               | net IP Configuration                |  |  |  |  |

|-------------------------|------------------------------|---------------------------------------------------|-------------------------------------|--|--|--|--|

|                         |                              | Across All IP Configurations                      |                                     |  |  |  |  |

| Core                    | FPGA Families<br>Supported   | ECP5, Lat                                         | ticeECP3                            |  |  |  |  |

| Requirements            | Minimal Device Needed        | LFE5UM-25F-6MG285C                                | LFE3-17E-7FN256C                    |  |  |  |  |

|                         | Targeted Devices             | LFE5UM-85F-7BG756C                                | LFE3-70EA-7FN484C                   |  |  |  |  |

| _                       | Data Path Width              | 8                                                 |                                     |  |  |  |  |

| Resource<br>Utilization | LUTs                         | 800 to 1000                                       |                                     |  |  |  |  |

| otinzation              | sysMEM EBRs                  | 0 to 1                                            |                                     |  |  |  |  |

|                         | Registers                    | 800 to 1000                                       |                                     |  |  |  |  |

|                         | Lattice Implementation       | Lattice Diar                                      | mond® 3.2                           |  |  |  |  |

|                         | Synthesis                    | Synopsys® Synplify Pro® for Lattice I-2013.09L-Si |                                     |  |  |  |  |

| Design Tool<br>Support  | Mentor Graphics <sup>®</sup> | Precision® RTL                                    |                                     |  |  |  |  |

| ouppo. t                | Simulation                   | Aldec <sup>®</sup> Active⁻HDL <sup>™</sup>        | 9.3 Lattice Edition                 |  |  |  |  |

|                         |                              | Mentor Graphics® Mode                             | ISim <sup>®</sup> SE (Verilog only) |  |  |  |  |

#### **Features**

- Implements PCS functions of the Cisco SGMII Specification, Revision 1.8

- Implements PCS functions for IEEE 802.3z (1000BaseX)

- Dynamically selects SGMII/1000BaseX PCS operation

- Supports MAC or PHY mode for SGMII auto-negotiation

- Supports (G)MII data rates of 1G bps, 100 Mbps, 10 Mbps

- · Provides Management Interface Port for control and maintenance

- Includes Easy Connect option for seamless integration with Lattice's Tri-Speed MAC (TSMAC) IP core

# **Functional Description**

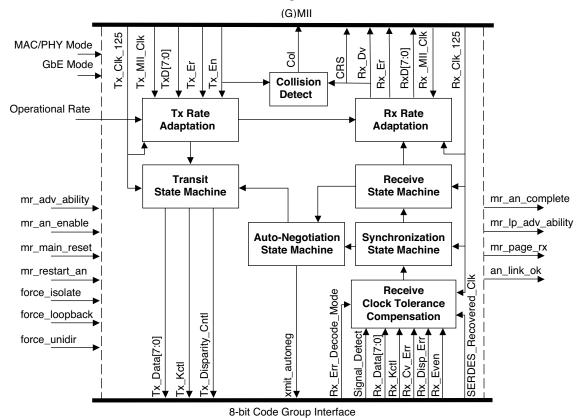

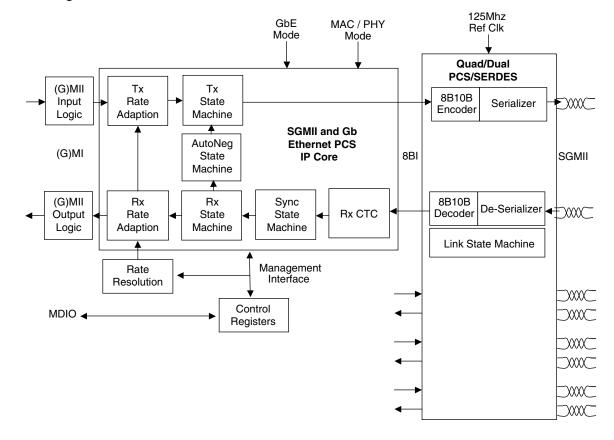

The SGMII and Gb Ethernet PCS IP core converts GMII frames into 8-bit code groups in both transmit and receive directions and performs auto-negotiation with a link partner as described in the Cisco SGMII and IEEE 802.3z specifications. The IP core's block diagram is shown in Figure 2-1.

Figure 2-1. SGMII and Gb Ethernet PCS IP Core Block Diagram

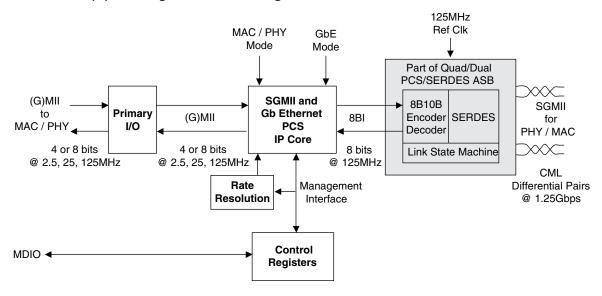

An example of how this core may be used in implementing a complete SGMII-to-(G)MII bridge is shown in Figure 2-2.

Figure 2-2. SGMII to (G)MII Bridge Reference Design

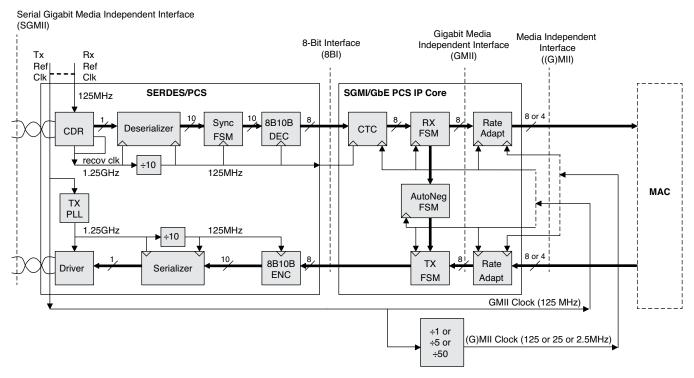

Figure 2-3 shows typical clock network connections between the IP core, the SERDES, and a MAC.

#### Figure 2-3. Typical SGMII Clocking Network

#### **Transmit Rate Adaptation**

This block adjusts the byte-per-byte data rate such that the output rate is always 1Gbps. For the case where the incoming (G)MII operates at 1Gbps, there is no data rate alteration. The incoming data is 8 bits wide clocked at 125 MHz and the outgoing data is also 8 bits wide clocked at 125 MHz. For the case where the incoming (G)MII operates at 100 Mbps, each incoming data byte is replicated ten times on the outgoing port. The incoming data is 4 bits wide clocked at 25 MHz clock and the outgoing data is 8 bits wide clocked at 125 MHz. The case for 10 Mbps (G)MII operation is similar except that data bytes are replicated 100 times and the incoming clock rate is 2.5 MHz.

#### **Transmit State Machine**

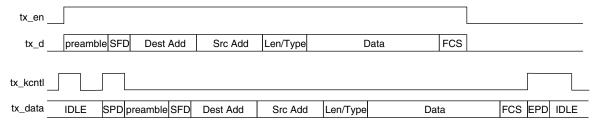

The transmit state machine implements the transmit functions described in clause 36 of the IEEE802.3 specification. The state machine's main purpose is to convert GMII data frames into code groups. A typical timing diagram for this circuit block is shown in Figure 2-4. Note that the state machine in this IP core does not fully implement the conversion to 10-bit code groups as specified in the IEEE802.3 specification. Instead, partial conversion to 8-bit code groups is performed. A separate encoder in the Lattice SERDES completes the full conversion to 10-bit code groups.

Figure 2-4. Typical Transmit Timing Diagram

### Soft Receive Clock Tolerance Compensation (CTC) Circuit

This block allows the receive path to compensate for slight frequency offsets between two clocks with a nominal frequency of 125 MHz. One timing source is the recovered clock from the SERDES Rx physical link. The other timing source is the locally generated Rx clock. As long as the two clock frequencies are within acceptable limits, the compensation circuit can maintain data path integrity. The circuit employs a 1024-byte deep FIFO with programmable high and low watermarks. When the FIFO occupancy is below the low watermark and the datastream is within an inter-packet region, FIFO reading is halted and two idle-2 ordered sets are inserted into the datastream. This action compensates for situations where the local clock is faster than the recovered clock. When the FIFO occupancy is above the high watermark and the datastream is within an inter-packet region, FIFO writing is inhibited for a period of one idle ordered set. This action compensates for situations where the local clock is slower than the recovered clock.

Note that the amount of timing drift between the two CTC clocks is dependent upon the size of the frequency offset and the size of the ethernet frame. Larger frame sizes produce larger timing drifts; larger frequency offsets produce larger timing drifts. For example, a +/- 100 ppm offset for a 1500 byte frame produces a 2.4 ns time drift. Increasing the frame size to 15,000 bytes produces a 24 ns time drift. The characteristics of the system design affect the compensation requirements for the CTC.

To address some of these issues, the IP core has three CTC implementations.

- A dynamic mode.

- · A static mode.

- · A "none" mode.

The user chooses the desired CTC mode when the IP core is generated using the IPexpress tool.

The dynamic CTC mode is intended for use where the IP core is expected to utilize all three of the possible (G)MII data rates (1 Gbps, 100 Mbps, 10 Mbps). The dynamic mode CTC automatically changes its FIFO thresholds to match the (G)MII data rate. These thresholds are hard-coded, and cannot be changed by the user. The thresholds are 16/32 for 1 Gbps, 34/68 for 100 Mbps, 340/640 for 10 Mbps. These settings provide the following compensation performance for a 9600 byte frame: +/- 729 ppm for 1Gbps; +/- 166 ppm for 100 Mbps; and +/- 176 ppm for 10 Mbps.

The static CTC mode is intended for use where the IP core is expected to operate at only one (G)MII data rate (1 Gbps, or 100 Mbps, or 10 Mbps). The user is able to choose the FIFO thresholds when the IP core is generated using the IPexpress tool. The default FIFO thresholds are 16/32, providing +/- 729 ppm compensation for a 9600 byte frame at (G)MII data rate of 1 Gbps. However, the user can alter these thresholds to provide other compensation capabilities.

The "none" CTC mode is intended for cases where a CTC function within the IP core is unwanted. The "none" mode utilizes a 16-byte deep FIFO to provide clean data transfers between the RX recovered clock, and the local RX clock. These two clocks may have arbitrary phase relationships with respect to each other; however the clocks must be at exactly the same frequency (0 ppm offset).

### **Synchronization State Machine**

The synchronization state machine implements the alignment functions described in clause 36 of the IEEE802.3 specification. The state machine's main purpose is to determine whether incoming code groups are properly aligned. Once alignment is attained, proper code groups are passed to the receive state machine. If alignment is lost for an extended period, an auto-negotiation restart is triggered.

#### **Receive State Machine**

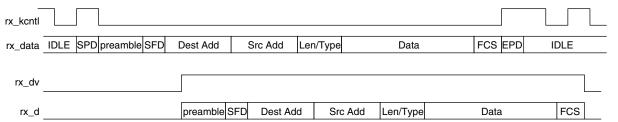

The receive state machine implements the receive functions described in clause 36 of the IEEE802.3 specification. The state machine's main purpose is to convert code groups into GMII data frames. A typical timing diagram for this circuit block is shown in Figure 2-5. Note that the state machine in this IP core does not fully implement the conversion from 10-bit code groups as specified in the IEEE802.3 specification. Instead, partial conversion from 8-bit code groups is performed. A separate decoder in the Lattice SERDES performs 10-bit to 8-bit code group conversions.

Figure 2-5. Typical Receive Timing Diagram

### **Receive Rate Adaptation**

This block's function is similar to the transmit rate adaptation block, except that it operates in reverse. The incoming data rate is always 1Gbps. The outgoing data rate is reduced by factors of 1x, 10x, or 100x for (G)MII rates of 1Gbps, 100 Mbps, and 10 Mbps respectively.

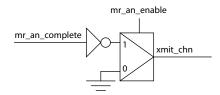

#### **Auto-Negotiation State Machine**

The auto-negotiation state machine implements the link configuration functions described in clause 37 of IEEE802.3 specification. However, the Cisco SGMII specification defines several changes (summarized below). This IP core will operate in adherence to either specification, based on the setting of an external "mode" pin. Please consult the two specifications for a detailed description of auto-negotiation operation. From a high-level view, the primary auto-negotiation functions are: testing the physical link for proper operation, and passing link configuration information between entities sitting on both sides of the link.

The major Cisco SGMII auto-negotiation modifications include:

- Decreases link timer interval from 10 msec to 1.6 msec.

- Redefines "link ability" bit assignments (see Table 2-1).

- Eliminates the need to pass link ability information from MAC to PHY.

- Adds a new condition that forces a restart on the PHY side whenever the PHY link abilities change.

A rough flow of auto-negotiation operation is as follows:

- An event triggers the process (e.g. reset, loss of sync).

- Both link entities recognize that the process has started and begin transmitting their abilities.

- The link timer expires.

- Both link entities attempt to verify reception of link partner abilities. Once reception is achieved, the entity transmits an acknowledge signal.

- The link timer expires.

- Both link entities verify receipt of link partner acknowledgement and then begin transmitting IDLE code groups.

- The link timer expires.

- Both link entities verify reception of IDLE code groups from link partner. Then the process enters the LINK-OK state and normal PCS operation can begin. The machine will remain in the LINK-OK state until a re-start event is detected.

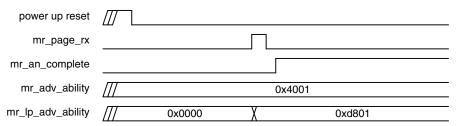

Figure 2-6. Typical Auto-Negotiation Timing Diagram for MAC-Side Entity

IP core signal ports associated with the auto-negotiation function are listed in Table 2-1.

Table 2-1. IP Core Signal Ports Associated with Auto-Negotiation

|                         | Bit Number                                                                                                                                                                                                                                                                                                                                                                                        | SGMII PHY Mode                                          | SGMII MAC Mode         | GbE Mode                                                |  |  |  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------------------------|---------------------------------------------------------|--|--|--|

|                         | 15                                                                                                                                                                                                                                                                                                                                                                                                | Link Status                                             | 0                      | Next Page                                               |  |  |  |

|                         | 14                                                                                                                                                                                                                                                                                                                                                                                                | Acknowledge<br>(controlled by autoneg<br>state machine) | 1                      | Acknowledge<br>(controlled by autoneg<br>state machine) |  |  |  |

|                         | 13                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                       | 0                      | Remote Fault[1]                                         |  |  |  |

|                         | 12                                                                                                                                                                                                                                                                                                                                                                                                | Duplex Mode<br>1=full; 0=half                           | 0                      | Remote Fault[0]                                         |  |  |  |

|                         | 11                                                                                                                                                                                                                                                                                                                                                                                                | (G)MII Speed[1]<br>11=rsvd; 10=1Gbps                    | 0                      | 0                                                       |  |  |  |

| mr_adv_ability[15:0]    | 10                                                                                                                                                                                                                                                                                                                                                                                                | (G)MII Speed[0]<br>01=100Mbps;<br>00=10Mbps             | 0                      | 0                                                       |  |  |  |

|                         | 9                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                       | 0                      | 0                                                       |  |  |  |

|                         | 8                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                       | 0                      | Pause[1]                                                |  |  |  |

|                         | 7                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                       | 0                      | Pause[0]                                                |  |  |  |

|                         | 6                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                       | 0                      | Half Duplex                                             |  |  |  |

|                         | 5                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                       | 0                      | Full Duplex                                             |  |  |  |

|                         | 4                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                       | 0                      | 0                                                       |  |  |  |

|                         | 3                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                       | 0                      | 0                                                       |  |  |  |

|                         | 2                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                       | 0                      | 0                                                       |  |  |  |

|                         | 1                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                       | 0                      | 0                                                       |  |  |  |

|                         | 0                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                       | 1                      | 0                                                       |  |  |  |

| mr_lp_adv_ability[15:0] | Displays ability data rece                                                                                                                                                                                                                                                                                                                                                                        | ived by entity (from link pa                            | artner)                |                                                         |  |  |  |

| mr_an_enable            | Active high signal; enable                                                                                                                                                                                                                                                                                                                                                                        | es auto-negotiation operat                              | tion                   |                                                         |  |  |  |

| mr_restart_an           | Active high signal; forces                                                                                                                                                                                                                                                                                                                                                                        | restart of auto-negotiatio                              | n                      |                                                         |  |  |  |

| mr_page_rx              | Active high signal, assert                                                                                                                                                                                                                                                                                                                                                                        | ts while state machine is i                             | n "Complete Acknowledg | je" state                                               |  |  |  |

| mr_an_complete          | Active high signal, asserts while state machine is in "Link OK" state                                                                                                                                                                                                                                                                                                                             |                                                         |                        |                                                         |  |  |  |

| sgmii_mode              | Controls auto-negotiation behavior. 0 = MAC-side operation; 1 = PHY-side operation                                                                                                                                                                                                                                                                                                                |                                                         |                        |                                                         |  |  |  |

| debug_link_timer_short  | Controls duration of link interval timer.  0 = Timer interval is normal (1.6 msec/SGMII 10msec/1000BaseX)  1 = Timer interval is 2 µsec (debug).  This signal should be tied to logic-0 when synthesizing the IP core so that the timer operates normally. However, for simulation, the signal can be tied to logic high to speed up completion of the autonegotiation portion of the simulation. |                                                         |                        |                                                         |  |  |  |

### **Collision Detect**

The collision detect signal is the logical-and of the tx\_en and rx\_dv GMII signals.

#### **Carrier Sense**

The carrier sense signal is identical to the rx\_dv GMII signal.

### **Data Path Latency Specifications**

Latency is the time delay taken to propagate signals between two points in the data path. This section provides latency specifications for the transmit and receive data paths of the SGMII IP core. The latency values are found by measuring the delay time between the leading edge of the SFD symbol of an ethernet frame, as it passes through the data path. For example, to specify the latency of the RX-CTC circuit, a continuous burst of constant-width ethernet frames, with constant 12-clock-cycle inter frame gaps are applied to the head-end of the RX data path. Then the latency is found by measuring the difference between the leading edge of the SFD symbol into and out-of the CTC circuit. The latency specifications are given in units of clock-cycles (125 MHz clock). All latency specifications are provided for the 1Gbps (G)MII data rate.

Referring back to Figure 2-3, it is shown that the two major elements in the IP core's transmit data path include the transmit-rate-adaptation-block and the transmit-state-machine-block. Both blocks provide constant delays, regardless of ethernet frame size, clock accuracy, and inter frame gap. There is no latency variation due to these factors. Table 2-2 shows the transmit data path latencies for the IP core's two (G)MII configurations – classic style and TSMAC easy connect style. Other IP core modes such as MAC/PHY, GbE/SGMII, etc. have no influence on transmit data path latency.

Table 2-2. Transmit Data Path Latency Specifications

| IP Core GMII<br>Configuration | TX FSM<br>Latency | TX Rate Adapt<br>Latency | TX Total<br>Latency |

|-------------------------------|-------------------|--------------------------|---------------------|

| Classic GMII                  | 3                 | 9                        | 12                  |

| Easy Connect GMII             | 3                 | 2                        | 5                   |

Referring back to Figure 2-3, it is shown that the three major elements in the IP core's receive data path include the RX-CTC-block, the RX-state-machine-block, and the RX-rate-adaptation-block. The last two blocks provide constant delays; there is no frame-to-frame latency variation. However, the RX-CTC block is affected by frame-size, clock accuracy, and FIFO-thresholds. The RX-CTC-block does exhibit frame-to-frame latency variation. Table 2-3 shows the RX data path latencies for various frequency accuracies, frame sizes, and (G)MII physical configurations. Note however that all specifications are given with Dynamic/Static CTC FIFO thresholds of 16-low; 32-high (these are the default threshold settings).

Table 2-3. Receive Data Path Latency Specifications

| Frequency Offset<br>Between Sender | IP Core GMII      | RX CTC Expected<br>Number of Clock | of Clock<br>Added/I | Number<br>k Cycles<br>Dropped<br>rame |      | CTC<br>ency |      | FSM<br>ency |      | e Adapt<br>ency | RX Total | Latency |

|------------------------------------|-------------------|------------------------------------|---------------------|---------------------------------------|------|-------------|------|-------------|------|-----------------|----------|---------|

| and Receiver                       | Configuration     | Slips per Frame                    | Min.                | Max.                                  | Min. | Max.        | Min. | Max.        | Min. | Max.            | Min.     | Max.    |

| 64-Byte Frames                     | •                 | •                                  | •                   |                                       |      | •           |      |             |      |                 | •        |         |

| +200 ppm                           | Classic GMII      | -0.03                              | 0                   | 2 <sub>add</sub>                      | 24   | 26          | 6    | 6           | 8    | 8               | 38       | 40      |

| 0 ppm                              | Classic GMII      | 0                                  | 0                   | 0                                     | 27   | 27          | 6    | 6           | 8    | 8               | 41       | 41      |

| -200 ppm                           | Classic GMII      | +0.03                              | 0                   | 2 <sub>drop</sub>                     | 32   | 34          | 6    | 6           | 8    | 8               | 46       | 48      |

| +200 ppm                           | Easy Connect GMII | -0.03                              | 0                   | 2 <sub>add</sub>                      | 24   | 26          | 6    | 6           | 2    | 2               | 32       | 34      |

| 0 ppm                              | Easy Connect GMII | 0                                  | 0                   | 0                                     | 27   | 27          | 6    | 6           | 2    | 2               | 35       | 35      |

| -200 ppm                           | Easy Connect GMII | +0.03                              | 0                   | 2 <sub>drop</sub>                     | 32   | 34          | 6    | 6           | 2    | 2               | 40       | 42      |

| 1500-Byte Frames                   |                   | •                                  | •                   |                                       |      | •           |      |             |      |                 | •        |         |

| +200 ppm                           | Classic GMII      | -0.3                               | 0                   | 2 <sub>add</sub>                      | 24   | 26          | 6    | 6           | 8    | 8               | 38       | 40      |

| 0 ppm                              | Classic GMII      | 0                                  | 0                   | 0                                     | 27   | 27          | 6    | 6           | 8    | 8               | 41       | 41      |

| -200 ppm                           | Classic GMII      | +0.3                               | 0                   | 2 <sub>drop</sub>                     | 32   | 34          | 6    | 6           | 8    | 8               | 46       | 48      |

| +200 ppm                           | Easy Connect GMII | -0.3                               | 0                   | 2 <sub>add</sub>                      | 24   | 26          | 6    | 6           | 2    | 2               | 32       | 34      |

| 0 ppm                              | Easy Connect GMII | 0                                  | 0                   | 0                                     | 27   | 27          | 6    | 6           | 2    | 2               | 35       | 35      |

| -200 ppm                           | Easy Connect GMII | +0.3                               | 0                   | 2 <sub>drop</sub>                     | 32   | 34          | 6    | 6           | 2    | 2               | 40       | 42      |

Table 2-3. Receive Data Path Latency Specifications (Continued)

| Frequency Offset<br>Between Sender                                              | IP Core GMII      | RX CTC Expe    |      | of Clock<br>Added/I | Number<br>k Cycles<br>Dropped<br>rame |      | CTC<br>ency | RX FSM<br>Latency |      | RX Rate Adapt<br>Latency |      | RX Total Latency |      |

|---------------------------------------------------------------------------------|-------------------|----------------|------|---------------------|---------------------------------------|------|-------------|-------------------|------|--------------------------|------|------------------|------|

| and Receiver                                                                    | Configuration     | Slips per Fra  |      | Min.                | Max.                                  | Min. | Max.        | Min.              | Max. | Min.                     | Max. | Min.             | Max. |

| 15,000-Byte Frame                                                               | es                |                |      |                     |                                       |      |             |                   |      |                          |      |                  |      |

| +200 ppm                                                                        | Classic GMII      | -3.0           |      | 2 <sub>add</sub>    | 4 <sub>add</sub>                      | 25   | 27          | 6                 | 6    | 8                        | 8    | 39               | 41   |

| 0 ppm                                                                           | Classic GMII      | 0              |      | 0                   | 0                                     | 27   | 27          | 6                 | 6    | 8                        | 8    | 41               | 41   |

| -200 ppm                                                                        | Classic GMII      | +3.0           |      | 2 <sub>drop</sub>   | 4 <sub>drop</sub>                     | 31   | 33          | 6                 | 6    | 8                        | 8    | 45               | 47   |

| +200 ppm                                                                        | Easy Connect GMII | -3.0           |      | 2 <sub>add</sub>    | 4 <sub>add</sub>                      | 25   | 27          | 6                 | 6    | 2                        | 2    | 33               | 35   |

| 0 ppm                                                                           | Easy Connect GMII | 0              |      | 0                   | 0                                     | 27   | 27          | 6                 | 6    | 2                        | 2    | 35               | 35   |

| -200 ppm                                                                        | Easy Connect GMII | +3.0           |      | 2 <sub>drop</sub>   | 4 <sub>drop</sub>                     | 31   | 33          | 6                 | 6    | 2                        | 2    | 39               | 41   |

| Random Frame Sizes From 64 to 15,000 Bytes, Random PPM Offset From -200 to +200 |                   |                |      |                     |                                       |      |             |                   |      |                          |      |                  |      |

| Random ppm                                                                      | Classic GMII      | -3.0 min. +3.0 | max. | 4 <sub>drop</sub>   | 4 <sub>add</sub>                      | 24   | 34          | 6                 | 6    | 8                        | 8    | 38               | 48   |

| Random ppm                                                                      | Easy Connect GMII | -3.0 min. +3.0 | max. | 4 <sub>drop</sub>   | 4 <sub>add</sub>                      | 24   | 34          | 6                 | 6    | 2                        | 2    | 32               | 42   |

## **Signal Descriptions**

Table 2-4 shows a detailed listing of all the SGMII IP core I/O signals.

Table 2-4. SGMII and Gb Ethernet PCS IP Core Input and Output Signals

| Signal Name            | I/O | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock Signals          |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| tx_clk_125             | In  | <b>Transmit 125MHz Clock</b> - 125 MHz clock for transmit state machine. Incoming data from the transmit rate adaptation block data is sampled on rising edge of this clock. Outgoing 8-bit code group transmit data is launched on the rising edge of this clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| tx_mii_clk             | In  | <b>Transmit MII Clock</b> - 125 MHz, 25 MHz, or 2.5 MHz clock for incoming (G)MII transmit data. Data is sampled on the rising edge of this clock. Note, this port is only present when the IP core is generated using the "classic" (G)MII option.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| tx_clock_enable_source | Out | Transmit Clock Enable Source - This signal is only present when the IP core is generated using the "TSMAC Easy Connect" (G)MII option. This signal is used in combination with the transmit 125 MHz clock to regulate the flow of transmit (G)MII data. The signal is generated by the transmit rate adaptation block. This clock enable should be tied to the transmit section of the Lattice MAC that sends transmit Ethernet frames to the SGMII and Gb Ethernet PCS IP core. This clock enable should also be tied to the clock enable "sink" of the SGMII and Gb Ethernet PCS IP core. This clock enable's behavior is controlled by the setting of the operational_rate pins of the IP core. For 1Gbps operation, the clock enable is constantly high. For 100 Mbps operation, the clock enable is high for one-out-of-ten 125 MHz clock cycles. For 10 Mbps operation, the clock enable is high for one-out-of-one-hundred 125 MHz clock cycles. |

| tx_clock_enable_sink   | ln  | <b>Transmit Clock Enable Sink</b> - This signal is only present when the IP core is generated using the "TSMAC Easy Connect" (G)MII option. This signal is used in combination with the transmit 125 MHz clock to regulate the flow of transmit (G)MII data. When the clock enable is high and the transmit clock edge rises, (G)MII data is sampled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| rx_clk_125             | In  | Receive 125MHz Clock - 125 MHz clock for synchronization and receive state machines. Incoming code groups from the receive CTC block data are sampled on rising edge of this clock. Outgoing GMII data is launched on the rising edge of this clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| rx_mii_clk             | In  | <b>Receive MII Clock</b> - 125 MHz, 25 MHz, or 2.5 MHz clock for outgoing (G)MII receive data. Data is launched on the rising edge of this clock. Note, this port is only present when the IP core is generated using the "classic" (G)MII option.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| rx_clock_enable_source | Out | Receive Clock Enable Source - This signal is similar to the tx_clock_enable_source described above, except that it is used for the receive data path. Note that this signal is only present when the IP core is generated using the "TSMAC Easy Connect" (G)MII option.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| rx_clock_enable_sink   | ln  | Receive Clock Enable Sink - This signal is only present when the IP core is generated using the "TSMAC Easy Connect" (G)MII option. This signal is used in combination with the receive 125 MHz clock to regulate the flow of receive (G)MII data. When the clock enable is high and the receive clock edge rises, (G)MII data is launched.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Table 2-4. SGMII and Gb Ethernet PCS IP Core Input and Output Signals (Continued)

| Signal Name            | I/O | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SERDES_recovered_clk   | ln  | SERDES Recovered Clock -125 MHz clock recovered from receive side of SERDES. This signal is synchronous with the 8-bit code groups received by the SERDES and should be used to clock receive data between the SERDES and the IP core. The IP core samples incoming 8-bit code groups on the rising edge of this clock.                                                                                                                                                                                                                                                                                                                                                                                                       |

| GMII Signals           |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| tx_d[7:0]              | ln  | Transmit Data - Incoming (G)MII data. Note, this port's behavior varies depending on the (G)MII option used when generating the IP core. For "classic" mode, when the (G)MII data rate is 1Gbps, all 8 bits of tx_d are valid. However, for 100 Mbps and 10 Mbps, only bits 3:0 of tx_d are valid. For the "TSMAC Easy Connect" mode all 8 bits of tx_d are valid for all (G)MII data rates (1Gbps, 100 Mbps, 10 Mbps).                                                                                                                                                                                                                                                                                                       |

| tx_en                  | ln  | Transmit Enable - Active high signal, asserts when incoming data is valid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| tx_er                  | ln  | <b>Transmit Error</b> - Active high signal used to denote transmission errors and carrier extension on incoming (G)MII data port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| rx_d[7:0]              | Out | Receive Data - Outgoing (G)MII data. Note, this port's behavior varies depending on the (G)MII option used when generating the IP core. For "classic" mode, when the (G)MII data rate is 1Gbps, all 8 bits of rx_d are valid. However, for 100 Mbps and 10 Mbps, only bits 3:0 of rx_d are valid. For the "TSMAC Easy Connect" mode all 8 bits of rx_d are valid for all (G)MII data rates (1Gbps, 100 Mbps, 10 Mbps).                                                                                                                                                                                                                                                                                                        |

| rx_dv                  | Out | Receive Data Valid - Active high signal, asserts when outgoing data is valid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| rx_er                  | Out | <b>Receive Error</b> - Active high signal used to denote transmission errors and carrier extension on outgoing (G)MII data port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| col                    | Out | <b>Collision Detect</b> - Active high signal, asserts when tx_en and rx_dv are active at the same time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| crs                    | Out | Carrier Sense Detect - Active high signal, asserts when rx_dv is high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 8-Bit Code Group Signa | ls  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| tx_data[7:0]           | Out | Represented to the port truly behaves as an 8-bit code group interface where data is tx_data[7:0], and tx_kcntl and tx_disparity_cntl are control signals for the 8-bit to 10-bit encoder within the LatticeSC, the port behaves as a 10-bit code group interface, with signals tx_land tx_disparity_cntl are control of the 10-bit encoder within the LatticeSC, the port behaves as a 10-bit code group interface, with signals tx_land tx_disparity_cntl and tx_disparity_cntl are control of the 10-bit encoder within the LatticeSC, the port behaves as a 10-bit code group interface, with signals tx_land tx_disparity_cntl forming bits 8 and 0 of the 10-bit interface. In addition, the 8-bit to 10-bit interface. |

| ix_data[r.o]           | Out | tx_kcntl and tx_disparity_cntl forming bits 8 and 9 of the 10-bit interface. In addition, the 8-bit to 10-bit encoder resides within the IP core; and consequently the encoder within the LatticeSC SERDES is bypassed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                        |     | Note that even though there are functional differences between the LatticeECP2M and LatticeSC implementations, the IPcore/SERDES connectivity is the same for both implementations - tx_data[7:0] of IP core connects to tx_data[7:0] of SERDES - tx_kcntl of IP core connects to tx_kcntl of SERDES - tx_disparity_cntl connects to tx_disparity_cntl of SERDES.                                                                                                                                                                                                                                                                                                                                                             |

| tx_kcntl               | Out | 8b Transmit K Control - Denotes whether current code group is data or control. 1 = control, 0 = data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| tx_disparity_cntl      | Out | <b>8b Transmit Disparity Control</b> - Used to influence the disparity state of an idle code group at the beginning of an inter-packet gap. 1 = Insert /I1/ if inter-packet gap begins with positive disparity, otherwise insert /I2/; 0 = normal, insert /I2/.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| rx_data[7:0]           | In  | 8b Receive Data - 8-bit code group data presented to the receive state machine.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| rx_kcntl               | ln  | <b>8b Receive K Control</b> - Denotes whether current code group is data or control. 1 = control, 0 = data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Table 2-4. SGMII and Gb Ethernet PCS IP Core Input and Output Signals (Continued)

| Signal Name             | 1/0 | Signal Description                                                                                                                                                                                                                                                                                                                |

|-------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         |     | Receive Error Control Mode - The embedded SERDES block of the LatticeECP2M FPGAs has two modes of interpreting errors - decoded and normal. In decoded mode, the three signals (rx_even, rx_cv_err, rx_disp_err) are used to decode one of eight error conditions. In decoded mode, the IP core responds to the following errors: |

| rx_err_decode_mode      | In  | 100 - Coding Violation Error<br>111 - Disparity Error                                                                                                                                                                                                                                                                             |

|                         |     | All other error codes are ignored by the IP core.                                                                                                                                                                                                                                                                                 |

|                         |     | In normal mode, the three error signals (rx_even, rx_cv_err, rx_disp_err) behave normally. The rx_err_decode_mode signal should be set high for decode-mode, and low for normal mode. When using LatticeSC devices, the pin should always be tied low.                                                                            |

| rx_even                 | In  | <b>Rx Even</b> - This signal is only used when error decoding mode is active. Otherwise, the signal should be tied low.                                                                                                                                                                                                           |

| rx_cv_err               | In  | <b>Rx Coding Violation Error</b> - In normal mode, an active high signal denoting a coding violation error in the receive data path. In decode mode, used to decode 1 of 8 error conditions.                                                                                                                                      |

| rx_disp_err             | In  | <b>Rx Disparity Error</b> - In normal mode, an active high signal denoting a disparity error in the receive data path. In decode mode, used to decode 1 of 8 error conditions.                                                                                                                                                    |

| signal_detect           | In  | <b>Signal Detect</b> - Denotes status of SERDES Rx physical link. 1 = signal is good; 0 = loss of receive signal.                                                                                                                                                                                                                 |

| rx_compensation_err     | Out | <b>Receive CTC Compensation Error</b> - This active high signal asserts when the receive CTC FIFO either underflows or overflows.                                                                                                                                                                                                 |

| ctc_drop_flag           | Out | CTC Drop Indication – Active high signal that asserts when the CTC logic drops an idle-code-group from the RX data stream.                                                                                                                                                                                                        |

| ctc_add_flag            | Out | CTC Add Indication – Active high signal that asserts when the CTC logic adds an idlecode group to the RX data stream.                                                                                                                                                                                                             |

|                         |     | <b>Auto-negotiation XMIT Status</b> – This signal should be tied to the "xmit_chn" pin of the SERDES. When the signal is high, it forces the RX data path of the SERDES to periodically insert idle-code groups into the SERDES RX data stream. This ensures that the SERDES CTC has opportunities to rate-adapt for ppm offsets. |

| xmit_autoneg            | Out | The PCS IP core drives this signal high when the auto-negotiation process is running. At all other times, the PCS IP core drives this signal low.                                                                                                                                                                                 |

|                         |     | Use of this signal is required if the designer chooses to use the CTC function embedded within the SERDES (instead of using the soft CTC function within the SGMII/GbE PCS IP core). Otherwise, the use of this signal is optional.                                                                                               |

| Management Signals      |     |                                                                                                                                                                                                                                                                                                                                   |

| mr_adv_ability[15:0]    | ln  | <b>Advertised Ability</b> - Configuration status transmitted by PCS during auto-negotiation process.                                                                                                                                                                                                                              |

| mr_an_enable            | In  | <b>Auto-Negotiation Enable</b> - Active high signal that enables auto-negotiation state machine to function.                                                                                                                                                                                                                      |

| mr_main_reset           | In  | Main Reset - Active high signal that forces all PCS state machines to reset.                                                                                                                                                                                                                                                      |

| mr_restart_an           | In  | <b>Auto-Negotiation Restart</b> - Active high signal that forces auto-negotiation process to restart.                                                                                                                                                                                                                             |

| mr_an_complete          | Out | <b>Auto-Negotiation Complete</b> - Active high signal that indicates that the auto-negotiation process is completed.                                                                                                                                                                                                              |

| mr_lp_adv_ability[15:0] | Out | <b>Link Partner Advertised Ability</b> - Configuration status received from partner PCS entity during the auto-negotiation process. The bit definitions are the same as described above for the mr_adv_ability port.                                                                                                              |

| mr_page_rx              | Out | <b>Auto-Negotiation Page Received</b> - Active high signal that asserts while the auto-negotiation state machine is in the "Complete_Acknowledge" state.                                                                                                                                                                          |

Table 2-4. SGMII and Gb Ethernet PCS IP Core Input and Output Signals (Continued)

| Signal Name            | I/O | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |