SLVSA42-FEBRUARY 2010

# TRIPLE BUCK POWER MANAGEMENT IC

Check for Samples: TPS65232

# **FEATURES**

- Wide Input Supply Voltage Range (10.8 V 22 V)

- One Adjustable PWM Buck Controller

- 10.8-V 22-V Input Voltage Range

- 3.3-V 6.1-V Output Voltage Range

- 500-kHz Switching Frequency

- Type III Compensation

- Programmable Current Limit

- Two Adjustable Step-Down Converter With Integrated Switching FETs:

- 4.75-V 5.5-V Input

- 0.9-V-3.3-V Output Voltage Range

- 3-A Output Current

- 1-MHz Switching Frequency

- Type III Compensation

- Pull-Up Current Sources on Buck Enable Pins for Accurate Start-Up Timing Control with Preset Default

- Over Current Protection on All Rails

- Thermal Shutdown to Protect Device During Excessive Power Dissipation

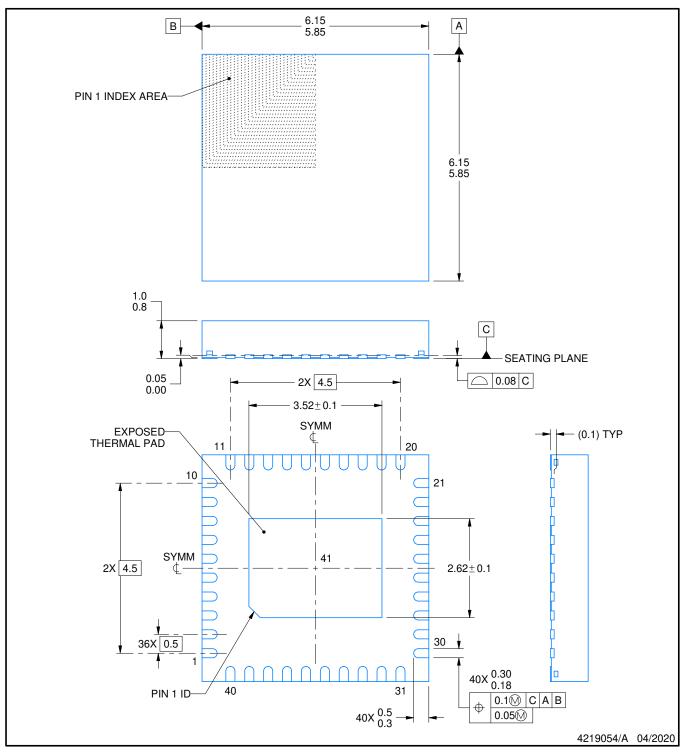

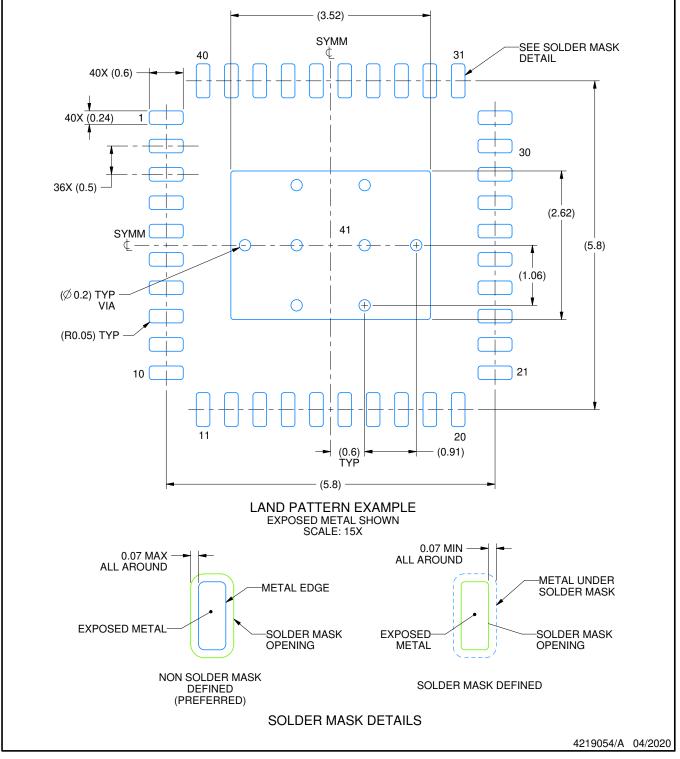

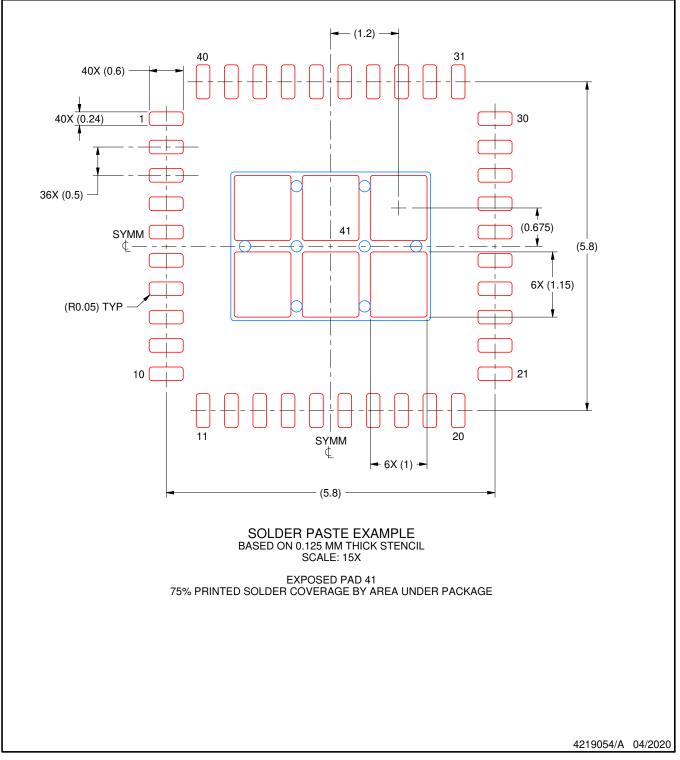

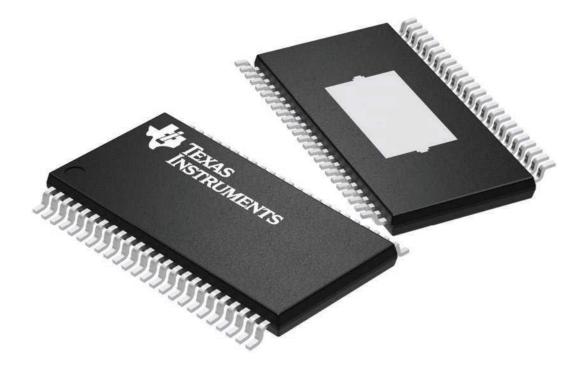

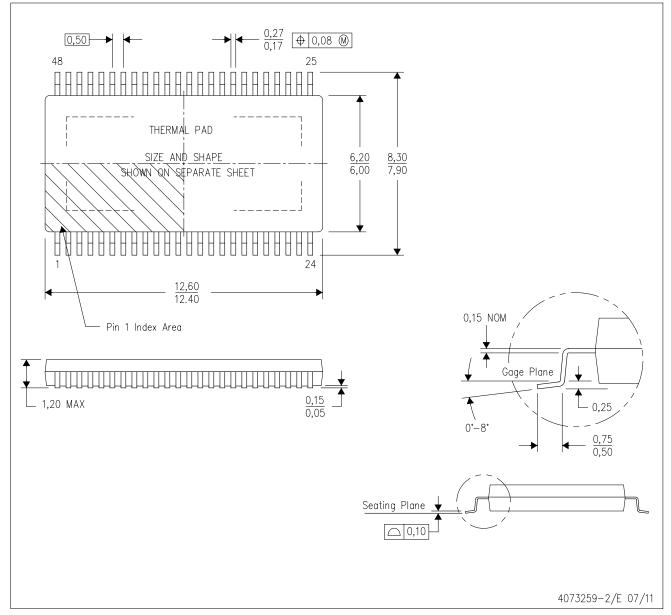

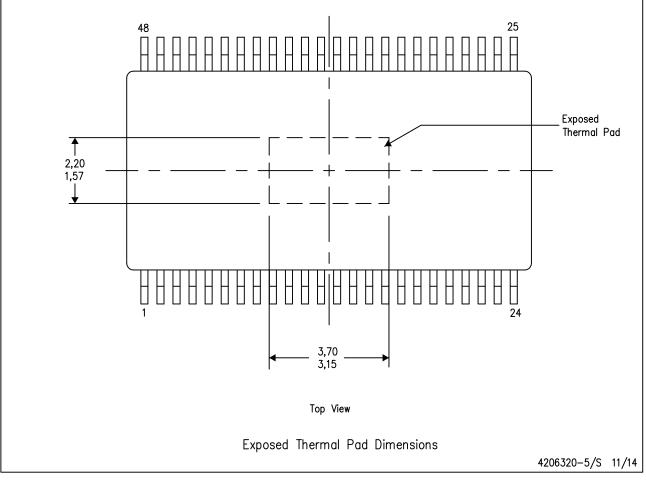

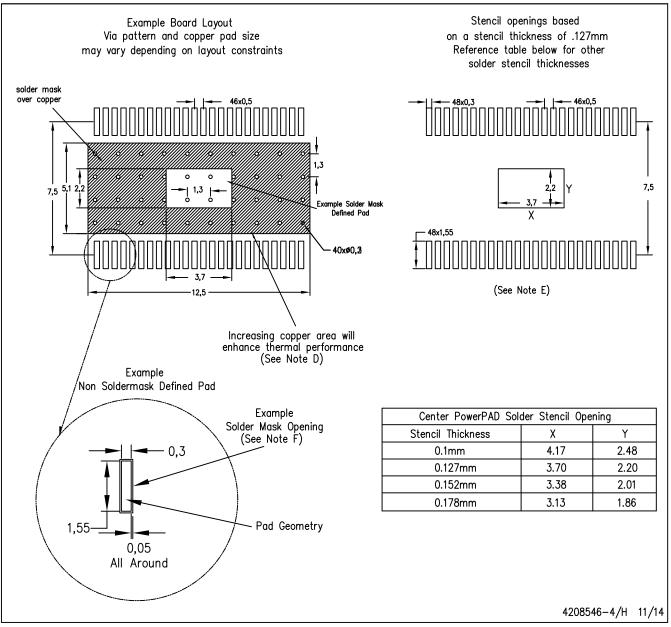

- Thermally Enhanced Package for Efficient Heat Management (48-pin HTSSOP or 6-mm x 6-mm 40-Pin QFN)

### **APPLICATIONS**

- xDSL and Cable Modems

- Wireless Access Points

- STB, DTV, DVD and Home Gateway

# **DESCRIPTION/ORDERING INFORMATION**

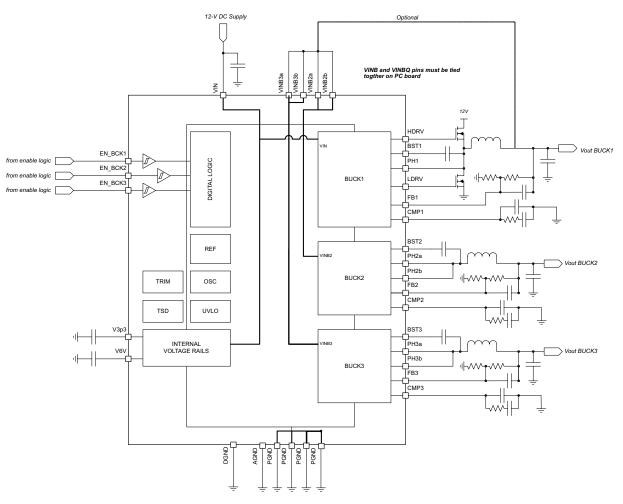

The TPS65232 provides one PWM buck controller, two adjustable, synchronous buck regulators. The SMPS have integrated switching FETs for optimized power efficiency and reduced external component count. All power blocks have thermal and over current/short circuit protection. The TPS65232 startup timing can be controlled through buck enable pins. The buck controller and buck converters have internal pole/zero pairs to help stabilizing the system with minimum external components.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### SLVSA42-FEBRUARY 2010

FUNCTIONAL BLOCK DIAGRAM

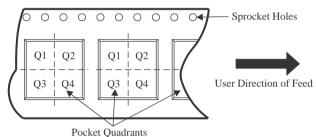

#### ORDERING INFORMATION<sup>(1)</sup>

| T <sub>A</sub> | PACKAGE <sup>(2)</sup> |              | PACKAGE <sup>(2)</sup> ORDERABLE PART NU |          | ORDERABLE PART NUMBER | TOP-SIDE MARKING |

|----------------|------------------------|--------------|------------------------------------------|----------|-----------------------|------------------|

| 0°C to 85°C    | 48-pin (HTSSOP) - DCA  | Reel of 2000 | TPS65232A2DCAR                           | TPS65232 |                       |                  |

|                | 40-pin (QFN) - RHA     | Reel of 2500 | TPS65232A0RHAR                           | TPS65232 |                       |                  |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

(2) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

TPS65232

SLVSA42-FEBRUARY 2010

| H3   | 36, 37 | 0 | Switching pin (BUCK3)                       |

|------|--------|---|---------------------------------------------|

| INB3 | 38, 39 | I | Input supply for BUCK3 (must be tied to VIN |

| ST3  | 40     | I | Bootstrap input (BUCK3)                     |

|      |        |   |                                             |

|      |        |   |                                             |

|      |        |   |                                             |

|      |        |   |                                             |

|      |        |   |                                             |

|      |        |   |                                             |

|      |        |   |                                             |

|      |        |   |                                             |

|      |        |   |                                             |

|      |        |   |                                             |

|      |        |   |                                             |

|      |        |   |                                             |

|      |        |   |                                             |

# SLVSA42-FEBRUARY 2010

NAME

NO.

1

www.ti.com

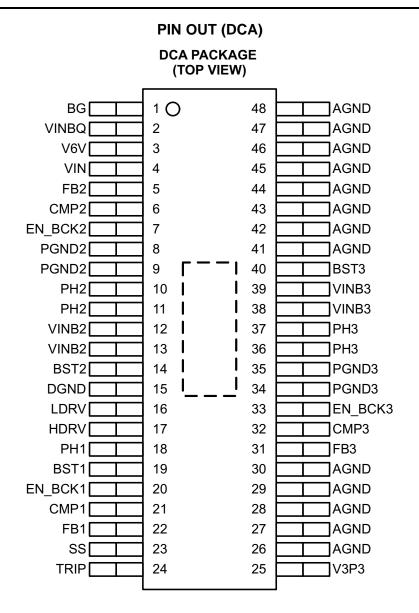

# **TERMINAL FUNCTIONS (DCA)**

Reference filter pin

I/O

Т

| VINBQ   | 2                                                        | I | Reference supply for BUCK2 and BUCK3                  |

|---------|----------------------------------------------------------|---|-------------------------------------------------------|

| V6V     | 3                                                        | Ι | Filter pin for internal voltage regulator (6 V)       |

| VIN     | 4                                                        | Ι | Input supply for BUCK1 and support circuitry          |

| FB2     | 5                                                        | Ι | Feedback pin (BUCK2)                                  |

| CMP2    | 6                                                        | I | Regulator Compensation (BUCK2)                        |

| EN_BCK2 | 7                                                        | I | Enable pin for BUCK2, active high                     |

| PGND2   | 8, 9                                                     |   | Power ground BUCK2                                    |

| PH2     | 10, 11                                                   | 0 | Switching pin (BUCK2)                                 |

| VINB2   | 12, 13                                                   |   | Input supply for BUCK2 (must be tied to VINB3, VINBQ) |

| BST2    | 14                                                       | I | Bootstrap input (BUCK2)                               |

| DGND    | 15                                                       |   | Digital ground                                        |

| LDRV    | 16                                                       | 0 | Low-side gate drive output (PWM controller)           |

| HDRV    | 17                                                       | 0 | High-side gate drive output (PWM controller)          |

| PH1     | 18                                                       | 0 | Switching pin (BUCK1)                                 |

| BST1    | 19                                                       | I | Bootstrap input (BUCK1)                               |

| EN_BCK1 | 20                                                       | I | Enable pin for BUCK1, active high                     |

| CMP1    | 21                                                       | I | Regulator compensation (PWM controller)               |

| FB1     | 22                                                       | I | Feedback pin (PWM controller)                         |

| SS      | 23                                                       | I | External capacitor for soft start                     |

| TRIP    | 24                                                       | I | BUCK1 over current trip point set-up                  |

| V3P3    | 25                                                       | I | Filter pin for internal voltage regulator (3.3 V)     |

| AGND    | 26, 27, 28, 29,<br>30, 41, 42, 43,<br>44, 45, 46, 47, 48 |   | Analog ground                                         |

| FB3     | 31                                                       | Ι | Feedback pin (BUCK3)                                  |

| CMP3    | 32                                                       | I | Regulator compensation (BUCK3)                        |

| EN_BCK3 | 33                                                       | I | Enable pin for BUCK3, active high                     |

| PGND3   | 34, 35                                                   |   | Power ground BUCK3                                    |

| PH3     | 36, 37                                                   | 0 | Switching pin (BUCK3)                                 |

| VINB3   | 38, 39                                                   | Ι | Input supply for BUCK3 (must be tied to VINB2, VINBQ) |

| BST3    | 40                                                       | I | Bootstrap input (BUCK3)                               |

ВG

DESCRIPTION

# TPS65232

www.ti.com

Submit Documentation Feedback 5

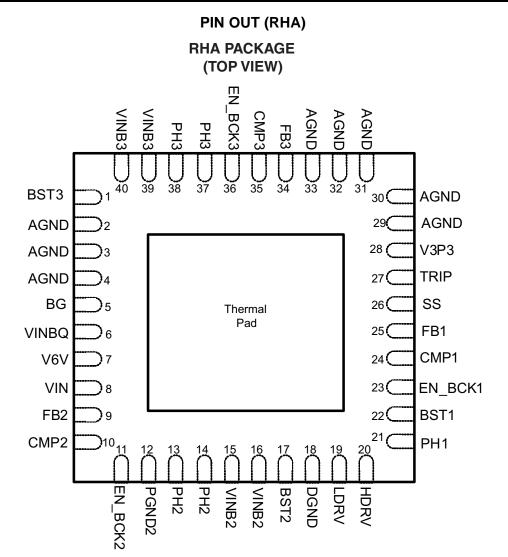

| PH3   | 37, 38 | 0 | Switching pin (BUCK3)                                 |

|-------|--------|---|-------------------------------------------------------|

| VINB3 | 39, 40 | I | Input supply for BUCK3 (must be tied to VINB2, VINBQ) |

| BST3  | 1      | I | Bootstrap input (BUCK3)                               |

|       |        |   |                                                       |

|       |        |   |                                                       |

|       |        |   |                                                       |

|       |        |   |                                                       |

|       |        |   |                                                       |

|       |        |   |                                                       |

|       |        |   |                                                       |

|       |        |   |                                                       |

|       |        |   |                                                       |

|       |        |   |                                                       |

|       |        |   |                                                       |

|       |        |   |                                                       |

|       |        |   |                                                       |

TPS65232

#### SLVSA42-FEBRUARY 2010

NAME

ΒG

V6V

VIN

FB2

CMP2

EN\_BCK2

PGND2

PH2

VINB2

BST2

DGND

LDRV

HDRV

PH1

BST1

CMP1

FB1

SS

TRIP

V3P3

AGND

FB3

CMP3

EN\_BCK3

EN\_BCK1

VINBQ

NO.

5

6

7

8

9

10

11

12

13, 14

15, 16

17

18

19

20

21

22

23

24

25

26

27

28

2, 3, 4, 29, 30,

31, 32, 33

34

35

36

www.ti.com

**NSTRUMENTS**

EXAS

DESCRIPTION

### TERMINAL FUNCTIONS (RHA)

Reference filter pin

Feedback pin (BUCK2)

Power ground BUCK2

Switching pin (BUCK2)

Bootstrap input (BUCK2)

Switching pin (BUCK1)

Bootstrap input (BUCK1)

Enable pin for BUCK1, active high

Feedback pin (PWM controller)

External capacitor for soft start

BUCK1 over current trip point set-up

Regulator Compensation (BUCK3)

Enable pin for BUCK3, active high

Digital ground

Analog ground

Feedback pin (BUCK3)

Regulator compensation (BUCK2)

Enable pin for BUCK2, active high

Reference supply for BUCK2 and BUCK3

Filter pin for internal voltage regulator (6 V)

Input supply for BUCK1 and support circuitry

Low-side gate drive output (PWM controller)

High-side gate drive output (PWM controller)

Regulator compensation (PWM controller)

Filter pin for internal voltage regulator (3.3 V)

Input supply for BUCK2 (must be tied to VINB3, VINBQ)

I/O

Т

Т

T

Т

L

T

Т

0

Т

0

0

0

Т

Т

T

Т

Т

T

Т

T

I

I

Texas Instruments

#### www.ti.com

# ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup> <sup>(2)</sup>

over operating free-air temperature range (unless otherwise noted)

|                  | Input voltage range at VIN                                        | ,                                            | -0.3 to 25                                                                                                                                                                                                    | V    |  |

|------------------|-------------------------------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|

|                  | Input voltage range at VINB, VINBQ                                |                                              | -0.3 to 7.0                                                                                                                                                                                                   | V    |  |

|                  | Voltage range at EN_BCK1, EN_BCK2, EN_BCK3                        |                                              | -0.3 to 3.6                                                                                                                                                                                                   | V    |  |

|                  | Voltage on HDRV, BST1                                             |                                              | -0.3 to 31                                                                                                                                                                                                    | V    |  |

|                  | Voltage on PH1                                                    | -0.3 to 24                                   | V                                                                                                                                                                                                             |      |  |

|                  | Voltage on FB1, CMP1, FB2, CMP2, FB3, CMP3                        | -0.3 to 3.6                                  | V                                                                                                                                                                                                             |      |  |

|                  | Voltage on PH2, PH3, LDRV                                         | -0.3 to 7.0                                  | V                                                                                                                                                                                                             |      |  |

|                  | Voltage on BST2, BST3                                             | -0.3 to 15                                   | V                                                                                                                                                                                                             |      |  |

|                  | Output current at BUCK2, BUCK3                                    | 3.8                                          | А                                                                                                                                                                                                             |      |  |

|                  | Peak output current                                               | Peak output current                          |                                                                                                                                                                                                               |      |  |

|                  | ESD rating                                                        | Human body model (HBM)                       | 2k                                                                                                                                                                                                            | V    |  |

|                  | ESD failing                                                       | Charged device model (CDM)                   | 500                                                                                                                                                                                                           | v    |  |

| 0                | Thermal resistance – Junction to ambient <sup>(3)</sup>           | TSSOP                                        | -0.3 to 7.0<br>-0.3 to 3.6<br>-0.3 to 31<br>-0.3 to 24<br>-0.3 to 3.6<br>-0.3 to 7.0<br>-0.3 to 7.0<br>-0.3 to 15<br>3.8<br>Internally limite<br>2k<br>500<br>25<br>18.1<br>2.6<br>2.5<br>0 to 150<br>0 to 85 | °C/W |  |

| $\theta_{JA}$    |                                                                   | QFN                                          | 18.1                                                                                                                                                                                                          | C/W  |  |

|                  | Continuous total power dissipation 55°C <sup>(3)</sup> no thermal | TSSOP                                        | 2.6                                                                                                                                                                                                           | w    |  |

|                  | warning                                                           | QFN                                          | 2.5                                                                                                                                                                                                           | vv   |  |

| TJ               | Operating virtual junction temperature range                      | Operating virtual junction temperature range |                                                                                                                                                                                                               | °C   |  |

| T <sub>A</sub>   | Operating ambient temperature range                               |                                              | 0 to 85                                                                                                                                                                                                       | °C   |  |

| T <sub>STG</sub> | Storage temperature range                                         |                                              | -65 to 150                                                                                                                                                                                                    | °C   |  |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to network ground terminal.

(3) Using JEDEC 51-5 (High K) board. This is based on standard 48DCA package, 4 layers, top/bottom layer: 2 oz Cu, inner layer: 1 oz Cu. Board size: 114.3 x 76.2 mm (4.5 x 3 inches), board thickness: 1.6 mm (0.0629 inch).

SLVSA42-FEBRUARY 2010

### **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range (unless otherwise noted)

|                                              | MIN  | NOM MA | X UNIT |

|----------------------------------------------|------|--------|--------|

| Input voltage range at VIN                   | 10.8 | 12     | 22 V   |

| Input voltage range at VINB                  | 4.75 | e      | .1     |

| Voltage range, EN_BCK1, EN_BCK2, EN_BCK3     | 0    | 3      | .3 V   |

| T <sub>A</sub> Ambient operating temperature | 0    | :      | 50 °C  |

### **ELECTRICAL CHARACTERISTICS**

VIN = 12 V  $\pm$ 5%, VINB2, VINB3 = 5 V  $\pm$ 5%, T<sub>J</sub> = 0°C to 150°C (unless otherwise noted)

|                       | PARAMETER                                    | TEST CONDITIONS                      | MIN               | TYP   | MAX  | UNIT   |

|-----------------------|----------------------------------------------|--------------------------------------|-------------------|-------|------|--------|

| INPUT VOLTA           | GE                                           |                                      |                   |       |      |        |

| VIN                   | Input supply voltage                         |                                      | 10.8              | 12    | 22   | V      |

|                       |                                              | VIN rising                           |                   |       | 10.8 |        |

| UVLO VIN              | UVLO threshold – VIN (main supply)           | VIN falling                          | 4.7               |       |      | V      |

|                       | UVLO threshold – VINB                        | VINB rising                          |                   |       | 4.75 |        |

| UVLO VINB             | (BUCK2/BUCK3 supply)                         | VINB falling                         | 4.25              |       |      | V      |

| INPUT CURRE           | NT                                           |                                      |                   |       |      |        |

| Iccq                  | Input supply current                         | All regulators/USB switches disabled |                   |       | 4    | mA     |

| BUCK ENABLE           | E INPUTS (EN_BCK1,2,3)                       |                                      |                   |       |      |        |

| VEN                   | Enable threshold                             |                                      |                   | 1.2   |      | V      |

| VEN <sub>HYS</sub>    | Enable voltage hysteresis                    |                                      |                   | 100   |      | mV     |

| I <sub>PULLUP</sub>   | Pull-up current                              | $t_{EN} = 0.2 \text{ ms/nF}$         |                   | 6     |      | μΑ     |

| R <sub>D</sub>        | Discharge resistor                           |                                      |                   |       | 1    | kΩ     |

| t <sub>D</sub>        | Discharge time                               | Power-up                             |                   | 5     |      | ms     |

| PWM CONTRO            | LLER (BUCK1)                                 |                                      |                   |       |      |        |

| V <sub>OUT</sub>      | Output voltage range <sup>(1)</sup>          |                                      | 3.3               |       | 6.1  | V      |

| V <sub>FB</sub>       | Feedback voltage                             |                                      | -2%               | 0.804 | 2%   | V      |

| LDRV<br>HDRV          | High and low side drive voltage              | No load                              |                   | 6     |      | V      |

| R_ON <sub>LDRV</sub>  | Low side ON resistance                       |                                      |                   | 8     |      | Ω      |

| R_OFF <sub>LDRV</sub> | Low side OFF resistance                      |                                      |                   | 1     |      | Ω      |

| R_ON <sub>HDRV</sub>  | High side ON resistance                      |                                      |                   | 20    |      | Ω      |

| R_OFF <sub>HDRV</sub> | High side OFF resistance                     |                                      |                   | 1     |      | Ω      |

| d                     | Duty cycle <sup>(2)</sup>                    |                                      | 20                |       | 80   | %      |

| A <sub>MOD</sub>      | Modulator gain                               |                                      |                   | 12    |      |        |

| f <sub>SW</sub>       | Switching frequency                          |                                      |                   | 500   |      | kHz    |

| I <sub>TRIP</sub>     | Current source for setting OCP trip<br>point | T <sub>A</sub> = 25°C                |                   | 10    |      | μA     |

| TC <sub>TRIP</sub>    | Temperature coefficient of ITRIP             |                                      |                   | 3700  |      | ppm/°C |

| R <sub>TRIP</sub>     | Current-limit setting resistor               |                                      | 80                |       | 250  | kW     |

| C <sub>OUT</sub>      | Output capacitance                           |                                      | 22 <sup>(3)</sup> |       |      | μF     |

| L                     | Nominal inductance                           | Recommended                          |                   | 4.7   |      | μH     |

| BUCK2                 |                                              | · · · · ·                            |                   |       |      |        |

| V <sub>OUT</sub>      | Output voltage range <sup>(1)</sup>          |                                      | 0.9               |       | 3.3  | V      |

| V <sub>FB</sub>       | Feedback voltage                             |                                      | - 2%              | 0.804 | 2%   | V      |

Output voltage range is limited by the minimum and maximum duty cycle. V<sub>OUT</sub>(min) ~ d(min) x V<sub>INPUT</sub> and V<sub>OUT</sub>(max) ~ d(max) x V<sub>INPUT</sub>.

(2) Performance outside these limits is not guaranteed.

(3) Absolute value. User should make allowances for tolerance and variations due to component selection.

8 Submit Documentation Feedback

SLVSA42-FEBRUARY 2010

## ELECTRICAL CHARACTERISTICS (continued)

VIN = 12 V ±5%, VINB2, VINB3 = 5 V ±5%,  $T_J$  = 0°C to 150°C (unless otherwise noted)

|                      | PARAMETER                           | TEST CONDITIONS                                      | MIN               | TYP   | MAX  | UNIT |

|----------------------|-------------------------------------|------------------------------------------------------|-------------------|-------|------|------|

| I <sub>OUT</sub>     | Output current                      |                                                      |                   |       | 3000 | mA   |

| η                    | Efficiency                          | I <sub>O</sub> = 2 A, V <sub>OUT</sub> = 3.3V        |                   | 95    |      | %    |

| <b>-</b>             | Low-side MOSFET On resistance       |                                                      |                   | 32    |      | 0    |

| R <sub>DS(ON)</sub>  | High-side MOSFET On resistance      | VIN12V = 12 V                                        |                   | 36    |      | mΩ   |

| I <sub>LIMIT</sub>   | Switch current limit                |                                                      |                   | 5     |      | А    |

|                      | Current limit accuracy              |                                                      | -30               |       | 30   | %    |

| V <sub>LINEREG</sub> | Line regulation - DC<br>ΔVOUT/ΔVINB | VINB = 4.75 V - 6.1 V,<br>I <sub>OUT</sub> = 1 A     |                   |       | 1    | %    |

| V <sub>LOADREG</sub> | Load regulation - DC<br>∆VOUT/∆IOUT | $I_{OUT} = 10 - 90\% I_{OUT,MAX}$                    |                   | 0.5   |      | %/A  |

| V <sub>OUTTOL</sub>  | DC set tolerance                    | Feedback resistor tolerance not included             | -2                |       | 2    | %    |

| d                    | Duty cycle <sup>(2)</sup>           |                                                      | 15                |       | 85   | %    |

| A <sub>MOD</sub>     | Modulator gain                      |                                                      |                   | 5     |      |      |

| f <sub>SW</sub>      | Switching frequency                 |                                                      |                   | 1     |      | MHz  |

| C <sub>OUT</sub>     | Output capacitance                  |                                                      | 10 <sup>(3)</sup> | 47    |      | μF   |

| ESR                  | Capacitor ESR                       |                                                      |                   |       | 50   | mΩ   |

| L                    | Nominal inductance                  |                                                      |                   | 2.2   |      | μH   |

| BUCK3                |                                     |                                                      |                   |       |      |      |

| V <sub>OUT</sub>     | Output voltage range <sup>(4)</sup> |                                                      | 0.9               |       | 3.3  | V    |

| V <sub>FB</sub>      | Feedback voltage                    |                                                      | -2%               | 0.804 | 2%   | V    |

| I <sub>OUT</sub>     | Output current                      |                                                      |                   |       | 3    | А    |

| η                    | Efficiency                          | I <sub>O</sub> = 2 A, V <sub>OUT</sub> = 1.2 V       |                   | 86    |      | %    |

| <b>D</b>             | Low-side MOSFET On resistance       |                                                      |                   | 32    |      |      |

| R <sub>DS(ON)</sub>  | High-side MOSFET On resistance      | VIN12V = 12 V                                        |                   | 36    |      | mΩ   |

| ILIMIT               | Switch current limit                |                                                      |                   | 5     |      | А    |

|                      | Current limit accuracy              |                                                      | -30               |       | 30   | %    |

| V <sub>LINEREG</sub> | Line regulation - DC<br>ΔVOUT/ΔVINB | VINB = 4.75 V - 6.1 V,<br>I <sub>OUT</sub> = 1000 mA |                   |       | 1    | %    |

| V <sub>LOADREG</sub> | Load regulation - DC<br>∆VOUT/∆IOUT | $I_{OUT} = 10 - 90\% I_{OUT,MAX}$                    |                   | 0.5   |      | %/A  |

| Vouttol              | DC Set Tolerance                    | Feedback resistor tolerance not included             | -2                |       | 2    | %    |

| d                    | Duty cycle <sup>(5)</sup>           |                                                      | 15                |       | 85   | %    |

| A <sub>MOD</sub>     | Modulator gain                      |                                                      |                   | 5     |      |      |

| f <sub>SW</sub>      | Switching frequency                 |                                                      |                   | 1     |      | MHz  |

| C <sub>OUT</sub>     | Output capacitance                  |                                                      | 10                |       |      | μF   |

| ESR                  | Capacitor ESR                       |                                                      |                   |       | 50   | mΩ   |

| L                    | Nominal inductance                  |                                                      |                   | 2.2   |      | μH   |

(4) Output voltage range is limited by the minimum and maximum duty cycle.  $V_{OUT}(min) \sim d(min) \times V_{INPUT}$  and  $V_{OUT}(max) \sim d(max) \times V_{INPUT}$ .

(5) Performance outside these limits is not guaranteed.

Texas Instruments

SLVSA42-FEBRUARY 2010

www.ti.com

## ELECTRICAL CHARACTERISTICS (continued)

VIN = 12 V ±5%, VINB2, VINB3 = 5 V ±5%,  $T_J = 0^{\circ}C$  to 150°C (unless otherwise noted)

|                      | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TEST CONDITIONS              | MIN | TYP | MAX    | UNIT |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----|-----|--------|------|

| SOFT START (B        | ART (BUCK1, 2, and 3)       Soft start current source       2       µ         Soft start current source       Ramp end       0.8       0.8         Soft start capacitor       t <sub>SS</sub> = 0.4 ms/nF       2       3.3       4.7       r         BK       Deglitch time       2.5       r         DCH       SS discharge time       500       µ         L SHUTDOWN       Image: Start star |                              |     |     |        |      |

| I <sub>SS</sub>      | Soft start current source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                              |     | 2   |        | μA   |

| V <sub>SS, MAX</sub> | Soft start ramp voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Ramp end                     |     | 0.8 |        | V    |

| C <sub>SS</sub>      | Soft start capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $t_{SS} = 0.4 \text{ ms/nF}$ | 2   | 3.3 | 4.7    | nF   |

| SSDONE_BK            | Deglitch time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                              |     | 2.5 |        | ms   |

| SSDONE_DCH           | SS discharge time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                              |     | 500 |        | μS   |

| THERMAL SHUT         | DOWN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                              |     |     | ,<br>, |      |

| T <sub>hot</sub>     | Thermal warning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              |     | 120 |        | °C   |

| T <sub>trip</sub>    | Thermal s/d trip point                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              |     | 160 |        | °C   |

| T <sub>hyst</sub>    | Thermal s/d hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              |     | 20  |        | °C   |

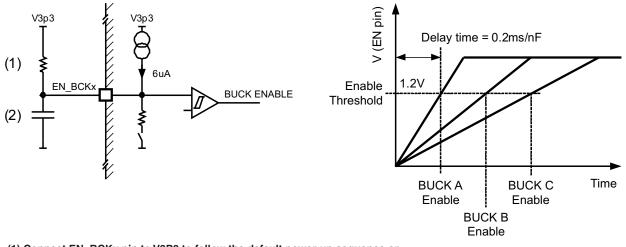

### **POWER-UP SEQUENCING**

ON/OFF control and power sequencing of the three buck regulators is controlled through EN\_BCK1, EN\_BCK2, and EN\_BCK3 enable pins. Each pin is internally connected to a  $6-\mu$ A constant-current source and monitored by a comparator with Schmitt trigger input with defined threshold. Connecting EN\_BCKn pin to ground disables BUCKn and connecting EN\_BCKn to V3p3 will enable the respective buck without delay. If more than one buck enable pin is connected to V3p3 the default startup sequence is BUCK1, BUCK2, BUCK3 and the minimum startup delay between rails is the soft-start time (typical 1.5 ms) plus 1 ms.

To create a startup-sequence different from the default, capacitors are connected between the EN\_BUCKn pins and ground. At power-up the capacitors are first discharged and then charged to V3p3 level by internal current sources (6  $\mu$ A typical) creating a constant-slope voltage ramp. A regulator is enabled when its EN pin voltage crosses the enable threshold (typical 1.2 V). A delay of 0.2 ms is generated for each 1-nF of capacitance connected to the enable pin. If two enable pins are pulled high while the third regulator is starting up, the default sequence will be applied to enable the remaining two regulators. To override default power-up sequence it is recommended that delay times differ by more than the soft-start time (typical 1.3 ms) plus 1 ms.

(1) Connect EN\_BCKx pin to V3P3 to follow the default power-up sequence or (2) Connect a capacitor from EN\_BCKx to GND to generate a custom power-up sequence.

#### Figure 1. Customizing the Power-Up Sequence

### OVER CURRENT PROTECTION

Over current protection (OCP) for BUCK1 is achieved by comparing the drain-to-source voltage of the low-side MOSFET to a set-point voltage, which is defined by both the internal current source, ITRIP, and the external resistor connected between the TRIP pin and ground. Over current threshold is calculated as follows:

$$I_{LIM} = \frac{R_{TRIP} \bullet I_{TRIP}}{10 \bullet R_{DS(ON)}}$$

(1)

ITRIP has a typical value of 10  $\mu$ A at 25°C and a temperature coefficient of 3700 ppm/°C to compensate the temperature dependency of the MOS R<sub>DS(ON)</sub>. The TPS65232 supports cycle-by-cycle over current limiting control which means that the controller compares the drain-to-source voltage of the low-side FET to the set-point voltage once per switching cycle and blanks out the next switching cycle if an over-current condition is detected. If in the following cycle over current condition is detected again, the controller blanks out 2, then 4, 8, and up to 16 cycles before turning on the high-side driver again. In an over current condition the current to the load exceeds the current to the output capacitor thus the output voltage will drop, and eventually cross the under voltage protection threshold and shut down the BUCK controller. Buck 2 and 3 show a similar mode of operation. All converters operate in "hiccup mode": Once an over-current is sensed, the controller shuts off the converter for a given time and then tries to start again. If the overload has been removed, the converter will ramp up and operate normally. If this is not the case, the converter will see another over-current event and shuts down again repeating the cycle until the failure is cleared.

#### SOFT START

Soft start for all three BUCKs is controlled by a single capacitor connected to the SS pin and an internal current source. When one of the BUCKs is enabled, the SS capacitor is pre-charged to the output voltage divided by the feed-back ratio before the internal SS current source starts charging the external capacitor. The output voltage of the BUCK ramps up as the SS pin voltage increased from its pre-charged value to 0.8 V. The soft start time is calculated from the SS supply current (ISS) and the capacitor value and has a typical value of 0.4 ms/nF or 1.3 ms for a 3.3-nF capacitor connected to the SS pin. Before the next rail is enabled, the SS cap is discharged and the SS cycle starts over again.

### UNDER VOLTAGE LOCKOUT (UVLO)

TPS65232 monitors VIN and VINB pin voltages and will disable one or more power paths depending on the current use condition:

- If VIN drops below 4.7 V, BUCK1, 2, and 3 are disabled.

- If VINB drops below 4.25 V and either BUCK2 or BUCK3 are enabled, all three output rails are disabled.

UVLO state is not latched and the system recovers as soon as the input voltage rises above its respective threshold. All three BUCK\_ENx pins are discharged and remain discharged during UVLO to ensure proper power sequencing when the system recovers.

### THERMAL SHUTDOWN (TSD)

TPS65232 monitors junction temperature and will disable the power path (BUCK1-3) if junction temperature rises above the specified trip point. All three BUCK\_ENx pins are discharged and remain discharged during TSD to ensure proper power sequencing when the system recovers.

#### LOOP COMPENSATION

All three BUCKs are voltage mode converters designed to be stable with ceramic capacitors. Refer to Component Selection Procedure section for calculating feedback components.

### 3.3-V REGULATOR

The TPS65232 has a built-in 3.3-V regulator for powering internal circuitry. The 3.3-V rail can also be used for enabling the BUCK regulators and/or the USB switches, but is not intended for supplying any other external circuitry.

### 6-V REGULATOR

The TPS65232 has a built-in 6-V regulator for powering internal circuitry.

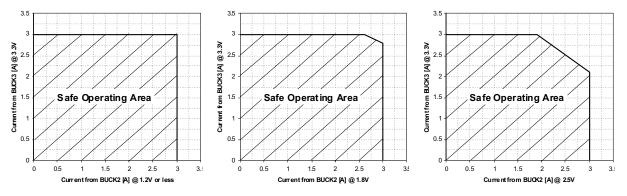

#### THERMAL MANAGEMENT AND SAFE OPERATING AREA

Total power dissipation inside TPS65232 is limited not to exceed the maximum allowable junction temperature of 150°C. The maximum allowable power dissipation is a function of the thermal resistance of the package ( $\theta_{JA}$ ) and ambient temperature.  $\theta_{JA}$  itself is highly dependent on board layout. The maximum allowable power inside the IC for operation at maximum ambient temperature without exceeding the temperature warning flag using the JEDEC High-K board is calculated as follows.

$$\Delta T = \Theta_{I4} \bullet P$$

For TSSOP:

$$P_{MAX} = \frac{T_{MAX} - T_{ambient}}{\theta_{JA}} = \frac{120^{\circ}\text{C} - 55^{\circ}\text{C}}{25^{\circ}\text{C/W}} \approx 2.6 \text{ W}$$

For QFN:

$$P_{MAX} = \frac{T_{MAX} - T_{ambient}}{\theta_{IA}} = \frac{120^{\circ}\text{C} - 75^{\circ}\text{C}}{18.1^{\circ}\text{C/W}} \approx 2.5 \text{ W}$$

For different PCB layout arrangements the thermal resistance ( $\theta_{JA}$ ) will change as the following table shows.

| BOARD TYPE                    | STACK-UP                                                                                                                 | $\theta_{JA}$ |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------|

| 8" x 10" FR4 PCB, four layers | 1.5-oz Cu, 60% Cu coverage top layer, 80% Cu coverage bottom<br>layer, no airflow<br>0.5-oz 30% Cu coverage inner layers | 29            |

| 8" x 10" FR4 PCB, two layers  | 1-oz Cu, 20% Cu coverage top layer, 90% Cu coverage bottom layer, no airflow                                             | 44            |

A minimum of two layers of 1-oz Cu with 20% Cu coverage on the top and 90% coverage on the bottom and the use of thermal vias to connect the thermal pad to the bottom layer is recommended. Note that the maximum allowable power inside the device will depend on the board layout. For recommendations on board layout for thermal management using TPS65232 consult your TI field application engineer.

In the example shown above the maximum allowable power dissipation for the IC has been calculated. This figure includes all heat sources inside the device including the power dissipated in BUCK1, BUCK2, BUCK3 and all supporting circuitry. Power dissipated in BUCK1 and all supporting circuitry is approximately 0.4 W and almost independent of the application. Power dissipated in BUCK2 and BUCK3 depends on the output voltage, output current, and efficiency of the switching converters. The following examples of safe operating area assume 90% efficiency for BUCK2 and BUCK3, 3.3-V output from BUCK3 and 1.2-V, 1.8-V, and 2.5-V output from BUCK2, respectively.

For any voltage / current comination inside the shaded area, the dissipated power inside the chip is below the allowable maximum. The examples assume T<sub>amblent</sub> < 60°C,  $\eta$  = 90% and  $\theta_{JA}$  < 44°C/W.

Figure 2. Examples of Thermal Safe Operating Area for V(BUCK3) = 3.3 V and V(BUCK1) = 1.2 V, 1.8 V and 2.5 V, Respectively

**EXAS**

(4)

(2)

(3)

#### **COMPONENT SELECTION PROCEDURE**

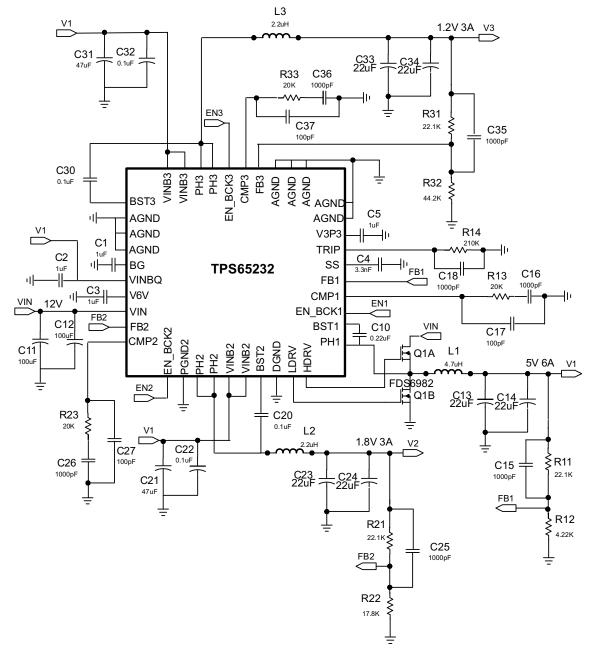

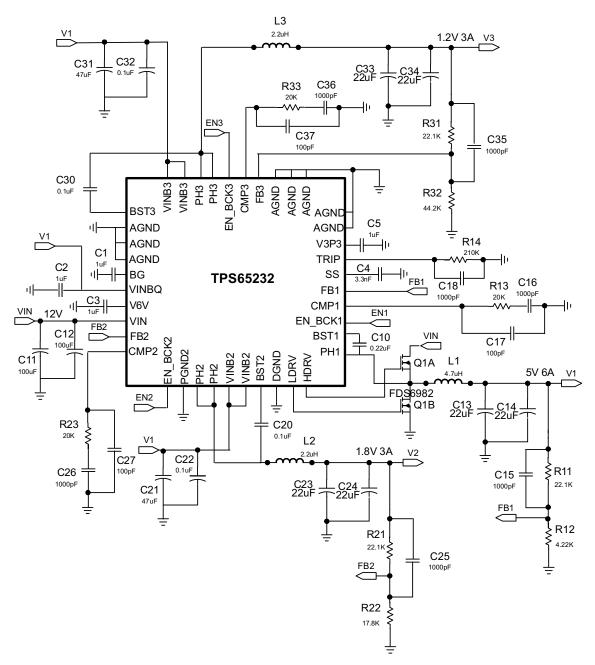

The following example illustrates the design procedure for selecting external components for the three buck converters. The example focuses on BUCK1 but the procedure can be directly applied to BUCK2 and BUCK3 as well. The design goal parameters are given in the table below. A list of symbol definitions is found at the end of this section. For this example the schematic in Figure 3 will be used.

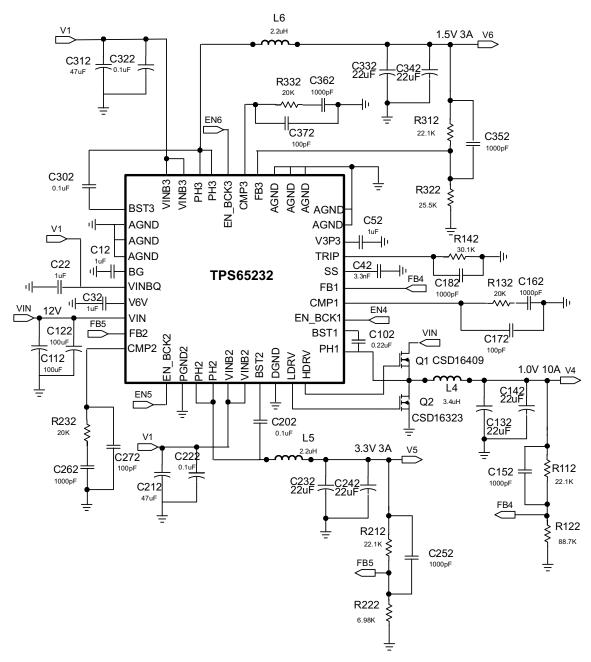

Figure 3. Sample Schematic for TPS65232

# BUCK1 DESIGN GUIDELINE

SLVSA42-FEBRUARY 2010

|                    | PARAMETER            | TEST CONDITIONS                          | MIN  | TYP | MAX  | UNIT |

|--------------------|----------------------|------------------------------------------|------|-----|------|------|

| V <sub>IN</sub>    | Input supply voltage |                                          | 10.8 | 12  | 13.2 | V    |

| VIN RIPPLE         | Input voltage ripple | I <sub>OUT, BUCK1</sub> = 6 A            |      |     | 75   | mV   |

| V <sub>OUT</sub>   | Output voltage       |                                          | 4.75 | 5   | 5.25 | V    |

|                    | Line regulation      | $V_{IN} = 10.8 V$ to 13.2 V              |      | 25  |      | mV   |

|                    | Load regulation      | $I_{OUT, BUCK1} = 0 A \text{ to } 6 A$   |      | 25  |      | mV   |

| VOUT RIPPLE        | Output ripple        | I <sub>OUT, BUCK1</sub> = 6 A            |      |     | 75   | mV   |

| V <sub>TRANS</sub> | Transient deviation  | $I_{OUT, BUCK1} = 1.5 A \text{ to } 3 A$ |      | 50  |      | mV   |

| I <sub>OUT</sub>   | Output current       | V <sub>IN</sub> = 10.8 V to 13.2 V       | 0    |     | 6    | А    |

| f <sub>SW</sub>    | Switching frequency  |                                          |      | 500 |      | kHz  |

#### **INDUCTOR SELECTION (L1)**

The inductor is typically sized for < 30% peak-to-peak ripple current ( $I_{RIPPLE}$ ). Given this target ripple current, the required inductor size is calculated by Equation 5.

$$L = \frac{V_{IN(MAX)} - V_{OUT}}{0.3 \cdot I_{OUT}} \cdot \frac{V_{OUT}}{V_{IN(MAX)}} \cdot \frac{1}{f_{SW}}$$

(5)

Solving Equation 5 with  $V_{IN(MAX)}$  = 13.2 V, an inductor value of 3.5 µH is obtained. A standard value of 4.7 µH is selected, resulting in 1.25-A peak-to-peak ripple. The RMS current through the inductor is approximated by Equation 6.

$$I_{L(RMS)} = \sqrt{\left(I_{L(avg)}^{2} + \frac{1}{12}(I_{RIPPLE})^{2}\right)} = \sqrt{\left(I_{OUT}\right)^{2} + \frac{1}{12}(I_{RIPPLE})^{2}}$$

(6)

Using Equation 6, the maximum RMS current in the inductor is about 6.01 A.

#### **OUTPUT CAPACITOR SELECTION (C13, C14)**

The selection of the output capacitor is typically driven by the output load transient response requirement.

Equation 7 and Equation 8 estimate the output capacitance required for a given output voltage transient deviation.

$$C_{OUT(MIN)} = \frac{I_{TRAN(MAX)}^{2} \cdot L}{(V_{IN(MIN)} - V_{OUT}) \cdot V_{TRAN}} \quad \text{when } V_{IN(MIN)} < 2 \cdot V_{OUT}$$

$$C_{OUT(MIN)} = \frac{I_{TRAN(MAX)}^{2} \cdot L}{V_{OUT} \cdot V_{TRAN}} \quad \text{when } V_{IN(MIN)} > 2 \cdot V_{OUT}$$

(8)

For this example, Equation 8 is used in calculating the minimum output capacitance.

Based on a 1.5-A load transient with a maximum 50-mV deviation, a minimum of 42- $\mu$ F output capacitance is required. We choose two 22- $\mu$ F capacitors in parallel for a total capacitance of 44  $\mu$ F.

The output ripple is divided into two components. The first is the ripple generated by the inductor ripple current flowing through the output capacitor's capacitance, and the second is the voltage generated by the ripple current flowing in the output capacitor's ESR. The maximum allowable ESR is then determined by the maximum ripple voltage and is approximated by Equation 9.

$$ESR_{MAX} = \frac{V_{RIPPLE(total)} - V_{RIPPLE(cap)}}{I_{RIPPLE}} = \frac{V_{RIPPLE(total)} - \left(\frac{I_{RIPPLE}}{C_{OUT} \bullet f_{SW}}\right)}{I_{RIPPLE}}$$

(9)

Based on 44- $\mu$ F of capacitance, 1.25-A ripple current, 500-kHz switching frequency and a design goal of 75-mV ripple voltage, we calculate a capacitive ripple component of 56 mV and an maximum ESR of 15 m $\Omega$ . Two 1210, 47- $\mu$ F, 10-V X5R ceramic capacitors are selected to provide significantly less than 15-m $\Omega$  of ESR.

#### PEAK CURRENT RATING OF THE INDUCTOR

(11)

(16)

With output capacitance known, it is now possible to calculate the charging current during start-up and determine the minimum saturation current rating of the inductor. The start-up charging current is approximated by Equation 10.

$$I_{CHARGE} = \frac{V_{OUT} \bullet C_{OUT}}{T_{SS}}$$

(10)

Using the TPS65232's recommended 1.3-ms soft-start time,  $C_{OUT} = 44 \ \mu\text{F}$  and  $V_{OUT} = 5 \ \text{V}$ ,  $I_{CHARGE}$  is found to be 169 mA. The peak current rating of the inductor is now found by Equation 11.

$$I_{L(PEAK)} = I_{OUT(MAX)} + \frac{1}{2} I_{RIPPLE} + I_{CHARGE}$$

For this example an inductor with a peak current rating of 6.79 A is required.

#### **INPUT CAPACITOR SELECTION (C11, C12)**

The input voltage ripple is divided between capacitance and ESR. For this design,  $V_{RIPPLE(CAP)} = 50 \text{ mV}$  and  $V_{RIPPLE(ESR)} = 25 \text{ mV}$ . The minimum capacitance and maximum ESR are estimated by Equation 12 and Equation 13.

$$C_{IN(MIN)} = \frac{I_{LOAD} \bullet V_{OUT}}{V_{RIPPLE(cap)} \bullet V_{IN} \bullet f_{SW}}$$

$$ESR_{MAX} = \frac{V_{RIPPLE(ESR)}}{I_{LOAD} + \frac{1}{2}I_{RIPPLE}}$$

(12)

For this design,  $C_{IN} > 100 \ \mu\text{F}$  and ESR < 3.7 m $\Omega$ . The RMS current in the output capacitors is estimated by Equation 14.

$$I_{RMS(CIN)} = I_{IN(RMS)} - I_{IN(avg)} = \sqrt{\left( (I_{OUT})^2 + \frac{1}{12} (I_{RIPPLE})^2 \right) \cdot \frac{V_{OUT}}{V_{IN}}} - \frac{V_{OUT} \cdot I_{OUT}}{V_{IN}}$$

(14)

With  $V_{IN} = V_{IN(MAX)}$ , the input capacitors must support a ripple current of 1.4-A RMS. The two 1210, 47- $\mu$ F X5R ceramic capacitors with about 5-m $\Omega$  ESR and 2-A RMS current rating are selected. It is important to check the DC bias voltage de-rating curves to ensure the capacitors provide sufficient capacitance at the working voltage.

#### **BOOTSTRAP CAPACITOR (C10)**

To ensure proper charging of the high-side MOSFET gate, limit the ripple voltage on the bootstrap capacitor to < 5% of the minimum gate drive voltage.

$$C_{BOOST} = \frac{20 \cdot Q_{GS, HSD}}{V_{IN(MIN)}}$$

(15)

Based on the FDS6982 MOSFET with a maximum total gate charge of 12 nC, calculate a minimum of 22-nF of capacitance. A standard value of 220 nF is selected.

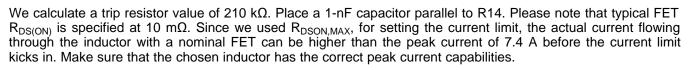

#### SHORT CIRCUIT PROTECTION (R14, C18) (BUCK1 ONLY)

The TPS65232 uses the forward drop across the low-side MOSFET during the OFF time to measure the inductor current. The voltage drop across the low-side MOSFET is given by Equation 16.

$$V_{DS} = I_{L(PEAK)} \bullet R_{DSON, LSD}$$

When  $V_{IN} = 10.8$  V to 13.2 V,  $I_{PEAK} = 7.4$  A. Using the FDS6982 MOSFET with a  $R_{DSON,MAX}$  at  $T_J = 25^{\circ}$ C of 20 m $\Omega$  we calculate the peak voltage drop to be 148 mV. Solving Equation 1 for  $R_{TRIP}$  and using  $I_{TRIP} = 10 \ \mu$ A:  $R14 = R_{TRIP} = R_{DS(ON)} \cdot I_{LIM} \cdot 10^{6}$ (17)

#### SLVSA42-FEBRUARY 2010

### FEEDBACK LOOP DESIGN

TPS65232 loop compensation looks like a type-II compensation network because an internal zero-pole pair can provide additional phase boost to stabilize this voltage mode control DC/DC controller. The internal zero is located at 45 kHz and the pole is located at 240 kHz. Ideally, the best cross-over frequency is around 1/10th of the switching frequency.

# FEEDBACK DIVIDER (R11, R12)

Select R11 between 10 k $\Omega$  and 100 k $\Omega$ . For this design select 22.1 k $\Omega$ . Next, R12 Is selected to produce the desired output voltage when  $V_{FB} = 0.8$  V using the following formula:

$$R12 = \frac{V_{FB} \cdot R11}{V_{OUT} - V_{FB}}$$

(18)

$V_{FB} = 0.8 \text{ V}$  and R11 = 22.1 K $\Omega$  for  $V_{OUT} = 5.0 \text{ V}$ , R12 = 4.22 k $\Omega$ .

# **Error Amplifier Pole-Zero Selection**

The design guidelines for TPS65232 Buck1 loop compensation are as follows:

- 1. Place a compensation zero at 8 kHz to boost the phase margin at the anticipated cross-over frequency.

- 2. Set the value of R and C of this to zero: C16 = 1000 pF and R13 = 20 k $\Omega$ .

- 3. Add an additional pole by making C17 = 100 pF. This pole is used to attenuate high frequency noise.

- 4. If V<sub>IN</sub> is 20 V 24 V, make C17 = 200 pF.

# **BUCK2 DESIGN GUIDELINE**

|                    | PARAMETER            | TEST CONDITIONS                        | MIN  | TYP   | MAX | UNIT |

|--------------------|----------------------|----------------------------------------|------|-------|-----|------|

| V <sub>IN</sub>    | Input supply voltage |                                        | 4.75 | 5     | 6   | V    |

| VIN RIPPLE         | Input voltage ripple | I <sub>OUT, BUCK1</sub> = 3 A          |      |       | 75  | mV   |

| V <sub>OUT</sub>   | Output voltage       |                                        |      | 5 5 6 | V   |      |

|                    | Line regulation      | $V_{IN} = 3 V \text{ to } 6 V$         |      | 18    |     | mV   |

|                    | Load regulation      | I <sub>OUT, BUCK1</sub> = 0 A to 3 A   |      | 18    |     | mV   |

| VOUT RIPPLE        | Output ripple        | I <sub>OUT, BUCK1</sub> = 3 A          |      |       | 36  | mV   |

| V <sub>TRANS</sub> | Transient deviation  | I <sub>OUT, BUCK1</sub> = 1.5 A to 3 A |      | 50    |     | mV   |

| I <sub>OUT</sub>   | Output current       | $V_{IN} = 3 V \text{ to } 6 V$         | 0    |       | 3   | Α    |

| f <sub>SW</sub>    | Switching frequency  |                                        |      | 1000  |     | kHz  |

## **INDUCTOR SELECTION (L2)**

The inductor is typically sized for < 30% peak-to-peak ripple current (I<sub>RIPPLE</sub>). Given this target ripple current, the required inductor size is calculated by Equation 5.

$$L = \frac{V_{IN(MAX)} - V_{OUT}}{0.3 \bullet I_{OUT}} \bullet \frac{V_{OUT}}{V_{IN(MAX)}} \bullet \frac{1}{f_{SW}}$$

Solving Equation 19 with  $V_{IN(MAX)}$  = 6 V, an inductor value of 1.4 µH is obtained. A standard value of 2.2 µH is selected, resulting in 0.37-A peak-to-peak ripple. The RMS current through the inductor is approximated by Equation 6.

$$I_{L(RMS)} = \sqrt{\left(I_{L(avg)}^{2} + \frac{1}{12}(I_{RIPPLE})^{2}\right)} = \sqrt{\left(I_{OUT}^{2}\right)^{2} + \frac{1}{12}(I_{RIPPLE}^{2})^{2}}$$

(20)

Using Equation 20, the maximum RMS current in the inductor is about 3.002 A.

www.ti.com

(19)

#### **OUTPUT CAPACITOR SELECTION (C23, C24)**

$V_{OUT} \bullet V_{TRAN}$

The selection of the output capacitor is typically driven by the output load transient response requirement.

Equation 21 and Equation 22 estimate the output capacitance required for a given output voltage transient deviation.

$$C_{OUT(MIN)} = \frac{I_{TRAN(MAX)}^{2} \cdot L}{(V_{IN(MIN)} - V_{OUT}) \cdot V_{TRAN}} \quad \text{when } V_{IN(MIN)} < 2 \cdot V_{OUT}$$

$$C_{OUT(MIN)} = \frac{I_{TRAN(MAX)}^{2} \cdot L}{V} \quad \text{when } V_{IN(MIN)} > 2 \cdot V_{OUT}$$

(21)

For this example, Equation 22 is used in calculating the minimum output capacitance.

Based on a 1-A load transient with a maximum 54-mV deviation, a minimum of 26-uF output capacitance is required. We choose two 22- $\mu$ F capacitors in parallel for a total capacitance of 44  $\mu$ F.

The output ripple is divided into two components. The first is the ripple generated by the inductor ripple current flowing through the output capacitor's capacitance, and the second is the voltage generated by the ripple current flowing in the output capacitor's ESR. The maximum allowable ESR is then determined by the maximum ripple voltage and is approximated by Equation 23.

$$ESR_{MAX} = \frac{V_{RIPPLE(total)} - V_{RIPPLE(cap)}}{I_{RIPPLE}} = \frac{V_{RIPPLE(total)} - \left(\frac{I_{RIPPLE}}{C_{OUT} \bullet f_{SW}}\right)}{I_{RIPPLE}}$$

(23)

Based on 44-µF of capacitance, 0.37-A ripple current, 1-MHz switching frequency and a design goal of 36-mV ripple voltage, we calculate a maximum ESR of 76 mΩ. Two 1210, 22-μF, 10-V X5R ceramic capacitors are selected to provide significantly less than 76-m $\Omega$  of ESR.

#### PEAK CURRENT RATING OF THE INDUCTOR

With output capacitance known, it is now possible to calculate the charging current during start-up and determine the minimum saturation current rating of the inductor. The start-up charging current is approximated by Equation 24.

$$I_{CHARGE} = \frac{V_{OUT} \bullet C_{OUT}}{T_{SS}}$$

(24)

Using the common start time (1 ms),  $C_{OUT} = 44 \ \mu F$  and  $V_{OUT} = 1.8 \ V$ ,  $I_{CHARGE}$  is found to be 79 mA. The peak current rating of the inductor is now found by Equation 25.

$$I_{L(PEAK)} = I_{OUT(MAX)} + \frac{1}{2} I_{RIPPLE} + I_{CHARGE}$$

(25)

For this example an inductor with a peak current rating of 3.264 A is required.

#### **INPUT CAPACITOR SELECTION (C21, C22)**

The input voltage ripple is divided between capacitance and ESR. For this design, V<sub>RIPPLE(CAP)</sub> = 50 mV and V<sub>RIPPLE(ESR)</sub> = 25 mV. The minimum capacitance and maximum ESR are estimated by Equation 26 and Equation 27

$$C_{IN(MIN)} = \frac{I_{LOAD} \bullet V_{OUT}}{V_{RIPPLE(cap)} \bullet V_{IN} \bullet f_{SW}}$$

$$ESR_{MAX} = \frac{V_{RIPPLE(ESR)}}{I_{LOAD} + \frac{1}{2}I_{RIPPLE}}$$

(26)

(27)

For this design,  $C_{IN} > 32 \ \mu$ F and ESR < 7.8 m $\Omega$ . The RMS current in the output capacitors is estimated by Equation 28.

(22)

SLVSA42-FEBRUARY 2010

Copyright © 2010, Texas Instruments Incorporated

$V_{IN} = V_{IN} (28)$ With  $V_{IN} = V_{IN(TYP)}$ , the input capacitors must support a ripple current of 0.58-A RMS. The two 1210, 47-μF X5R ceramic capacitors with about 5-mΩ ESR and 2-A RMS current rating are selected. It is important to check the DC bias voltage de-rating curves to ensure the capacitors provide sufficient capacitance at the working voltage.

#### **BOOTSTRAP CAPACITOR (C20)**

A standard value of 100 nF is selected.

#### SHORT CIRCUIT PROTECTION

Current limits for BUCK2 are internally set to 5 A.

#### FEEDBACK LOOP DESIGN

TPS65232 loop compensation looks like a type-II compensation network because an internal zero-pole pair can provide additional phase boost to stabilize this voltage mode control DC/DC controller. The internal zero is located at 45 kHz and the pole is located at 240 kHz. Ideally, the best cross-over frequency is around 1/10th of the switching frequency.

#### FEEDBACK DIVIDER (R21, R22)

Select R21 between 10 k $\Omega$  and 100 k $\Omega$ . For this design select 22.1 k $\Omega$ . Next, R22 Is selected to produce the desired output voltage when V<sub>FB</sub> = 0.8 V using the following formula:

$$R22 = \frac{V_{FB} \cdot R21}{V_{OUT} - V_{FB}}$$

(29)

$V_{FB}$  = 0.8 V and R21 = 22.1 K $\Omega$  for  $V_{OUT}$  = 1.8 V, R22 = 17.8 k $\Omega$ .

$I_{RMS(CIN)} = I_{IN(RMS)} - I_{IN(avg)} = \sqrt{\left( (I_{OUT})^2 + \frac{1}{12} (I_{RIPPLE})^2 \right) \cdot \frac{V_{OUT}}{V_{IN}}} - \frac{V_{OUT} \cdot I_{OUT}}{V_{IN}}$

#### **Error Amplifier Pole-Zero Selection**

The design guidelines for TPS65232 BUCK2 loop compensation are as follows:

- 1. Place a compensation zero at 8 kHz to boost the phase margin at the anticipated cross-over frequency.

- 2. Set the value of R and C of this to zero: C26 = 1000 pF and R23 = 20 k $\Omega$ .

- 3. Add an additional pole by making C27 = 100 pF. This pole is used to attenuate high frequency noise.

### **BUCK3 DESIGN GUIDELINE**

Both BUCK2 and BUCK3 have the same internal structure. Thus, BUCK2's design guideline can be applied to BUCK3's design directly.

#### **OTHER COMPONENTS**

A 1-µF ceramic capacitor should be connected as close as possible to the following pins:

- BG: Bandgap reference

- VIN: Bypass capacitor

- V6V: Internal 6-V supply

- V3P3: Internal 3.3-V supply

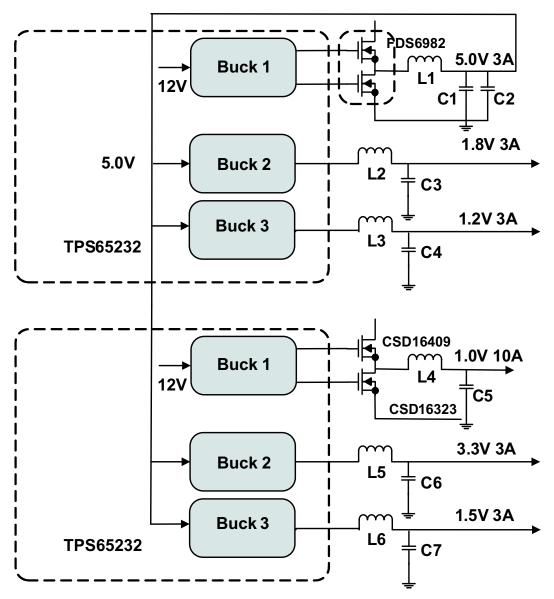

#### SIX RAIL POWER SYSTEM

The following example illustrates two TPS65232 ICs can provide six power rails and the low output voltage rail is capable of delivering 10-A load current with high efficiency.

www.ti.com

SLVSA42-FEBRUARY 2010

Figure 4. Six Rail Power System Part I: 5 V, 1.8 V and 1.2 V

# TPS65232

#### SLVSA42-FEBRUARY 2010

www.ti.com

Figure 5. Six Rail Power System Part II: 3.3 V, 1.5 V and 1 V

SLVSA42-FEBRUARY 2010

www.ti.com