# ANALOG DEVICES

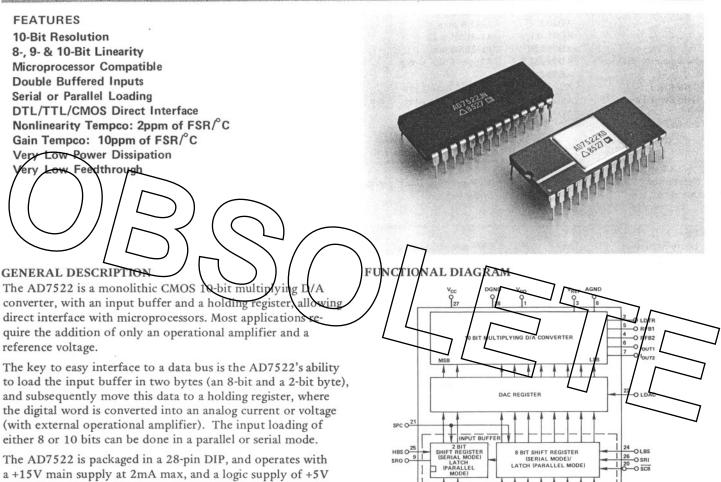

# CMOS 10-Bit, Buffered Multiplying D/A Converter

AD7522

for TTL interface, or +10 to +15V for CMOS interface.

A thin film on high density CMOS process, using silicon nitride passivation, ensures high reliability and excellent stability.

#### **ORDERING INFORMATION**

|                 | Temperature Range   |                                  |                                   |

|-----------------|---------------------|----------------------------------|-----------------------------------|

| Nonlinearity    | 0 to $+70^{\circ}C$ | $-25^{\circ}C$ to $+85^{\circ}C$ | $-55^{\circ}C$ to $+125^{\circ}C$ |

| 2LSB (8-Bit)    | AD7522JN            | AD7522JD                         | AD7522SD                          |

| 1LSB (9-Bit)    | AD7522KN            | AD7522KD                         | AD7522TD                          |

| 1/2LSB (10-Bit) | AD7522LN            | AD7522LD                         | AD7522UD                          |

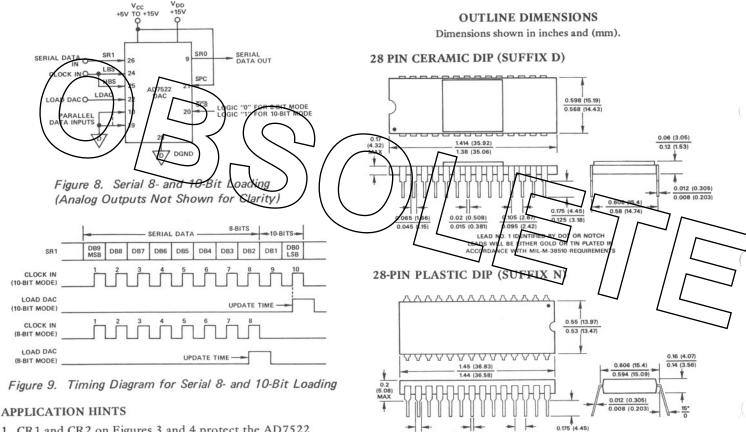

#### PACKAGE IDENTIFICATION

Suffix "D": Ceramic DIP Package Suffix "N": Plastic DIP Package PIN CONFIGURATION

| VDD C    | 1. | 28 | DGND     |

|----------|----|----|----------|

| LDTR     | 2  | 27 | Vcc      |

| VREF     | 3  | 26 | SR1      |

| RFB2     | 4  | 25 | HBS      |

| RFB1     | 5  | 24 | LBS      |

| OUT1     | 6  | 23 | NC       |

| IOUT2    | 7  | 22 | LDAC     |

| AGND     | 8  | 21 | SPC      |

| SR0      | 9  | 20 | SC8      |

| MSB) DB9 | 10 | 19 | DB0 (LSB |

| DB8      | 11 | 18 | DB1      |

| D87      | 12 | 17 | DB2      |

| DB6      | 13 | 16 | DB3      |

| DB5      | 14 | 15 | DB4      |

|          |    |    |          |

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way; Norwood, MA 02062-9106 U.S.A.

Tel: 617/329-4700

Twx: 710/394-6577

Telex: 174059

Cables: ANALOG NORWOODMASS

# **SPECIFICATIONS** ( $V_{DD} = +15V$ , $V_{CC} = +5V$ , $V_{REF} = +10V$ , TA = +25°C unless otherwise noted)

| IFIED<br>GE TEST CONDITIONS<br>SC8 = "1" |

|------------------------------------------|

|                                          |

| SC8 = "1"                                |

| 500 = 1                                  |

|                                          |

|                                          |

|                                          |

|                                          |

|                                          |

|                                          |

|                                          |

| C max                                    |

| C max                                    |

| g max                                    |

| ading/°C max                             |

| eading/°C max                            |

| $I_{OUT1}$ : DB0 through DB9 = 0         |

| $I_{OUT2}$ : DB0 through DB9 = 1         |

|                                          |

|                                          |

| V <sub>REF</sub> = 20V p-p; 10kHz        |

| To 0.05% of FSR for a FSR Step.          |

| HBS and LBS Low to High                  |

| LDAC = 1                                 |

| LDAC - 1                                 |

| Q max                                    |

|                                          |

|                                          |

|                                          |

| Alt Data Input High                      |

|                                          |

| All Data Inputs Iow                      |

| An Day inputs now                        |

|                                          |

| $V_{1} = +5V$                            |

| V <sub>CC</sub> = +15V                   |

| V <sub>CC</sub> = +5V                    |

| $V_{CC} = +3V$<br>$V_{CC} = +15V$        |

| V <sub>CC</sub> = +15V                   |

|                                          |

| LDAC: 0 to $+3V$                         |

| HBS, LBS: 0 to $+3V$                     |

|                                          |

|                                          |

|                                          |

|                                          |

|                                          |

| )                                        |

|                                          |

Notes

<sup>1</sup> Guaranteed by design. Not tested.

<sup>2</sup> Data setup time is the minimum amount of time required for DB0 - DB9 to be stable prior to strobing HBS, LBS.

<sup>3</sup> Data hold time is the minimum amount of time required for DB0 - DB9 to be stable after strobing HBS, LBS.

#### ABSOLUTE MAXIMUM RATINGS

|           | V <sub>REE</sub> to GND±25V                                                                                                             |   |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|---|

|           | V <sub>REF</sub> to GND±25V<br>V <sub>DD</sub> to GND+17V                                                                               |   |

|           | V <sub>CC</sub> to GND                                                                                                                  |   |

|           | V <sub>CC</sub> to V <sub>DD</sub> +0.4V                                                                                                |   |

|           | Output Voltage (pins 6 & 7)0.3V to V <sub>DD</sub>                                                                                      |   |

|           | Operating Temperature                                                                                                                   |   |

|           | JN, KN, LN versions 0 to +70°C                                                                                                          |   |

|           | JD, KD, LD versions $\dots \dots \dots$ |   |

|           | SD, TD, UD versions $\dots \dots \dots$ |   |

|           | Storage Temperature $\dots \dots \dots$ |   |

|           | Power Dissipation (Package)                                                                                                             |   |

|           | Up to $+50^{\circ}$ C:                                                                                                                  |   |

|           |                                                                                                                                         |   |

|           | Plastic (Suffix N)                                                                                                                      |   |

| /         | Ceramic (Suffix D)                                                                                                                      |   |

|           | Derate Above +50°C by                                                                                                                   |   |

| 1         | Plastic (Suffix N)                                                                                                                      |   |

| 1         | Ceramic (Suffix D)                                                                                                                      |   |

|           | Digital Input Voltage Range                                                                                                             |   |

| $\langle$ |                                                                                                                                         |   |

|           | CAUTION                                                                                                                                 |   |

|           | 1. Do not apply voltages higher than $V_{OC}$ to SIO.<br>2. Do not apply voltages higher than $V_{DD}$ or less than GND to              |   |

|           | 2. Do not apply voltages higher than V pr or less than GND to                                                                           |   |

|           | any other input/output terminal except VREF, RFB1 or                                                                                    | L |

|           | R <sub>FB2</sub> .                                                                                                                      | V |

|           | 3. The digital control inputs are zener protected, however                                                                              | A |

|           | permanent damage may occur on unconnected units                                                                                         | I |

|           | under high energy electrostatic fields. Keep unused units                                                                               | t |

|           | in conductive foam at all times.                                                                                                        | 1 |

|           | 4. $V_{CC}$ should never exceed $V_{DD}$ by more than 0.4V,                                                                             |   |

|           | especially during power ON or OFF sequencing.                                                                                           |   |

|           |                                                                                                                                         |   |

#### TERMINOLOGY

#### RESOLUTION

Value of the LSB. For example, a unipolar n-bit converter has a resolution of  $(2^{-n})$  ( $V_{REF}$ ). A bipolar n-bit converter has a resolution of  $[2^{-(n-1)}]$  [ $V_{REF}$ ]. Resolution in no way implies linearity.

#### GAIN

The "gain" of a converter is that analog scale factor setting that establishes the nominal conversion relationship, e.g., 10V full scale. It is a linear error which can be externally adjusted (see gain adjustment on next page).

#### **OUTPUT LEAKAGE CURRENT**

Current which appears on the OUT1 terminal when the DAC register is loaded with all "0's" or on the OUT2 terminal when the DAC register is loaded with all "1's."

#### DAC CIRCUIT DESCRIPTION

#### GENERAL CIRCUIT INFORMATION

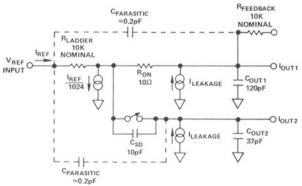

The AD7522's DAC functional block consists of a highly stable Silicon Chromium thin film R-2R ladder, and ten SPDT N-channel current steering switches. Most applications require the addition of only an output operational amplifier and a voltage or current reference.

The simplified D/A circuit is shown in Figure 1. An inverted R-2R ladder structure is used – that is, the binarily weighted currents are switched between the  $I_{OUT1}$  and  $I_{OUT2}$  bus lines, thus maintaining a constant current in each ladder leg independent of the switch state.

Figure 2. Equivalent Circuit (Shown for all Digital Inputs High)

|   | PIN           | FUNCTION          | UN DESCRIPTION                                                                                                                                                                                                |

|---|---------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | PIN           | MNEMONIC          | DESCRIPTION                                                                                                                                                                                                   |

|   | 1             | V <sub>DD</sub>   | +15V (nominal) Main Supply.                                                                                                                                                                                   |

|   | 2             | LDTR              | R-2R Ladder Termination Resistor. Normally grounded for unipolar operation or terminated at I <sub>OUT2</sub> for bipolar operation.                                                                          |

|   | 3             | V <sub>REF</sub>  | Reference Voltage Input. Since the AD7522 is a multiplying DAC, $V_{REF}$ may vary over the range of ±10V.                                                                                                    |

|   | 4             | RFB2              | $R_{FEEDBACK} \div 2$ ; gives full scale equal to $V_{REF}/2$ .                                                                                                                                               |

|   | 5             | RFB1              | R <sub>FEEDBACK</sub> , used for normal unity gain (at full scale) D/A conversion.                                                                                                                            |

|   | 6             | I <sub>OUT1</sub> | DAC Current OUT1 Bus. Normally terminated at virtual ground of output amplifier.                                                                                                                              |

|   | 7             | I <sub>OUT2</sub> | DAC Current OUT2 Bus, terminated at ground for unipolar operation, or virtual ground of op amp for bipolar operation.                                                                                         |

|   | 8             | AGND              | Analog Ground. Back gate of DAC N-channel SPDT current steering switches.                                                                                                                                     |

|   | 9             | SRO               | Serial Output. An auxiliary output for recovering data in the input buffer.                                                                                                                                   |

|   | 10            | DB9               | Data Bit 9. Most significant parallel data input.                                                                                                                                                             |

|   | 11            | DB8               | Data Bit 8.                                                                                                                                                                                                   |

|   | 12            | DB7               | Data Bit 7.                                                                                                                                                                                                   |

|   | 13            | DB6               | Data Bit 6.                                                                                                                                                                                                   |

|   | 14            | DB5  <br>Note 1   | Data Bit 5.                                                                                                                                                                                                   |

|   | 15            | DB4               | Data Bit 4.                                                                                                                                                                                                   |

|   | 16            | DB3               | Data Bit 3.                                                                                                                                                                                                   |

|   | 17            | DB2               | Data Bit 2.                                                                                                                                                                                                   |

| / | 18            | DBI               | Data Bit 1.                                                                                                                                                                                                   |

| [ | 10            | DB0               | Data Bit 0. Least significant parallel data input.                                                                                                                                                            |

|   | 20            | SC8               | Bit/Short Cycle Control. When in serial mode, if SC8 is held to Logic "0", the two least significant input latches in the input buffer                                                                        |

|   |               |                   | are bypassed to provide proper serial loading of 8-bit serial words. If SC8 is held to Logic "1", the AD7522 will accept a 10-bit serial words                                                                |

|   | $\overline{}$ |                   | Data bits 0 (LSB) and DB1 are in a parallel load mode when $\overline{SC8} = 0$ and should be tied to a logic low state to prevent false data                                                                 |

|   |               | $\sim$ 1          | from being loaded.                                                                                                                                                                                            |

|   | 21            | SPC               | Secial/Parallel control. If SPC is a Logic "0" the AD752 will load parallel data appearing on DB0 through DB9 into the input buffer when the appropriate structure inputs are exercised (see HBS and LBS).    |

|   |               |                   | If SPC is a Logic "1", the AD7522 will load serial data appearing on Fin 26 into the input Duffers. Each serial data bit must be                                                                              |

|   |               |                   | "strobed" into the buffer with the HBS and LSS.                                                                                                                                                               |

|   | 22            | LDAC              | Load DAC: When LDAC is a Logic "0", the AD7522 is in the 'hold" mode, and digital activity in the input buffer is locked out.                                                                                 |

|   |               | NG                | When LDAC is a Logic "1", the AD7522 is in the "load" mode, and data in the input Juffer loads the DAC egister.                                                                                               |

|   | 23            | NC                | No Connection.                                                                                                                                                                                                |

|   | 24            | LBS               | Low Byte Strobe. When in "parallel load" mode (SPC = 0), parallel data appearing on the DB9 (LSB) through DB7 inputs will be "clocked" into the input buffer on the positive going edge of the LBS.           |

|   |               |                   | When in "serial load" mode (SPC = 1), serial data bits appearing at the serial input terminal, Pin 26, will be "clocked" into the input                                                                       |

|   |               |                   | buffer on the positive going edge of HBS and LBS. (HBS and LBS must be clocked simultaneously when in "serial load" mode.)                                                                                    |

|   | 25            | HBS               | High Byte Strobe. When in "parallel load" mode (SPC = 0), parallel data appearing on the DB9 (MSB) and DB8 data inputs will be                                                                                |

|   |               |                   | "clocked" into the input buffer on the positive going edge of HBS.<br>When in "serial load" mode (SPC = 1), serial data bits appearing at the serial input terminal, Pin 26, will be "clocked" into the input |

|   |               |                   | buffer on the positive going edges of HBS and LBS. (HBS and LBS must be clocked simultaneously when in "serial load" mode.)                                                                                   |

|   | 26            | SRI               | Serial Input.                                                                                                                                                                                                 |

|   | 27            | V <sub>CC</sub>   | Logic Supply. If +5V is applied, all digital inputs/outputs are TTL compatible. If +10V to +15V is applied, digital inputs/outputs                                                                            |

|   |               |                   | are CMOS compatible.                                                                                                                                                                                          |

|   | 28            | DGND              | Digital Ground                                                                                                                                                                                                |

|   |               |                   |                                                                                                                                                                                                               |

Note 1: Logic "1" applied to a data bit steers that bit's current to the I<sub>OUT</sub>1 terminal.

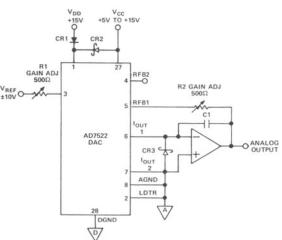

(Note: Protection Schottky CR3 in Figure 3 and Figure 4 is not required when using TRI-FET amps such as the AD542 or AD544).

### UNIPOLAR OPERATION

APPLICATIONS

PIN FUNCTION DESCRIPTION

Figure 3 shows the analog circuit connections required for unipolar operation. The input code/output voltage relationship is shown in Table I.

#### Zero Offset Adjustment

1. Adjust the op amp's offset potentiometer for  $\leq 1 \text{mV}$  on the amplifier junction.

#### Gain Adjustment

- 1. Set R1 and R2 to 0Ω. Load the DAC register with all "1's."

- 2. If analog out is greater than  $-V_{REF}$ , increase R1 for required full scale output. If analog out is less than  $-V_{REF}$ , increase R2 for required full scale output.

Figure 3. Unipolar Binary Operation (2-Quadrant Multiplication)

-4-

| DIGITAL INPUT | ANALOG OUTPUT                     |

|---------------|-----------------------------------|

| 11111111111   | $-V_{\rm REF} (1 - 2^{-10})$      |

| 1000000001    | $-V_{\text{REF}} (1/2 + 2^{-10})$ |

| 10000000000   | -V <sub>REF</sub> /2              |

| 0111111111    | $-V_{\rm REF} (1/2 - 2^{-10})$    |

| 0000000001    | $-V_{REF} (2^{-10})$              |

| 00000000000   | 0                                 |

Table I. Unipolar Code Table

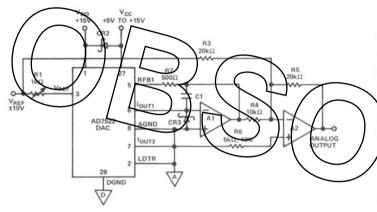

#### **BIPOLAR OPERATION**

Figure 4 shows the analog circuit connections required for bipolar operation. The input code/ouput voltage relationship is shown in Table II.

Figure 4. Bipolar Operation

With the DAC register loaded to 10 0000 0000 adjust R1 so that ANALOG OUTPUT = 0V. Alternatively, R1, R2 may be omitted and the ratios of R3, R4 varied for ANALOG OUTPUT = 0V. Full-scale trimming can be accomplished by adjusting the amplitude of  $V_{REF}$  or by varying the value of R5.

If R1, R2 are not used, then resistors R3, R4 and R5 should be ratio matched to 0.05% to ensure gain error performance to the data sheet specification. When operating over a wide temperature range, it is important that the resistors be of the same type so that their temperature coefficients match.

| DIGITAL INPUT | ANALOG OUTPUT               |

|---------------|-----------------------------|

| 1111111111    | $+V_{\rm REF} (1 - 2^{-9})$ |

| 1000000001    | $+V_{REF} (2^{-9})$         |

| 10000000000   | 0                           |

| 01111111111   | $-V_{REF} (2^{-9})$         |

| 0000000001    | $-V_{\rm REF} (1 - 2^{-9})$ |

| 000000000000  | -V <sub>REF</sub>           |

Table II. Bipolar Code Table

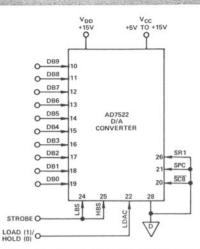

## SINGLE BYTE PARALLEL LOADING

Figure 5 illustrates the logic connections for loading single byte parallel data into the input buffer. DB0 should be grounded on "K" and "T" versions, and DB0 and DB1 should be grounded on "J" and "S" versions for monotonic operation of the DAC. DB9 is always the MSB, whether 8-bit, 9-bit, or 10-bit linear AD7522's are used.

Figure 5. Single Byte Parallel Loading

When data is stable on the parallel inputs (DB0-DB9), it can be transferred into the input buffer on the positive edge of the strobe pulse.

Data is transferred from the input buffer to the DAC register when LDAC is a Logic "1." LDAC is a level-actuated (versus edge-triggered) function and must be held "high" at least 0.5µs for data transfer to occur

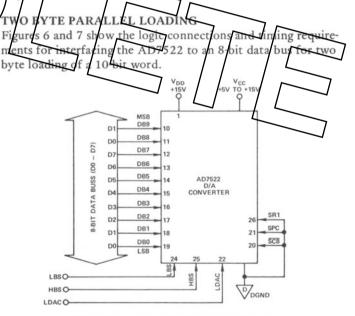

Figure 6. Two Byte Parallel Loading

Figure 7. Timing Diagram

First, the least significant data byte (DB0 through DB7) is loaded into the input buffer on the positive edge of LBS. Subsequently, the data bus is used for status indication and instruction fetching by the CPU. When the most significant data byte (DB8 and DB9) is available on the bus, the input buffer is loaded on the positive edge of HBS. The DAC register updates to the new 10-bit word when LDAC is "high." LDAC may be exercised coincident with, or at any time after HBS loads the second byte of data into the input buffer.

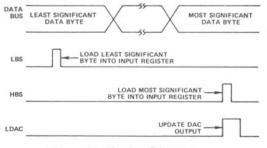

#### SERIAL LOADING

Figure 8 and Figure 9 show the connections and timing diagram for serial loading.

To load a 10-bit word (SC8 = 1), HBS and LBS must be strobed simultaneously with exactly 10 positive edges to clock the serial data into the input buffer. For 8-bit words (SC8 = 0), only 8 positive edges are required.

- 2. Diode CR3 on Figure 3 and Figure 4 clamps the amplifier junction to -300mV if it attempts to swing negative during power up or power down. The input structures of some high-speed op amps can supply substantial current under the transient conditions encountered during power sequencing. It is recommended that the PC layout be able to accommodate the diodes.

- 3. Fast op amps will require phase compensation for stability due to the pole formed by COUT1 or COUT2 and RFEEDBACK.

- 4. During serial loading, all data inputs (DB0 through BD9), should be grounded.

(1.66)

0.045 (1.15

0.02 (0.508)

0.015 (0.381)

0.105 (2.67)

0.095 (2.42) LEAD NO. 1 IDENTIFIED BY DOT OR NOTCH LEADS ARE SOLDER OR TIN PLATED KOVAR OR ALLOY 42

0.12 (3.05)

1. CR1 and CR2 on Figures 3 and 4 protect the AD7522 against latch-up V<sub>CC</sub> exceeds V<sub>DD</sub>, and may be omitted if V<sub>DD</sub> and V<sub>CC</sub> are driven from the same voltage.

(

5/26

Ц

1111 U