# life.augmented

### STAP16DPPS05

## Automotive-grade low voltage 16-bit constant current LED sink driver with output error detection and auto power-saving

Datasheet - production data

#### **Features**

- AECQ100 qualified

- Low voltage power supply down to 3 V

- 16 constant current output channels

- Adjustable output current through external resistor

- Short and open output error detection

- Serial data IN/parallel data OUT

- 3.3 V micro driver-able

- Auto power-saving

- Output current: 3 40 mA

- Auto power-saving

- Max. clock frequency: 30 MHz

- 20 V current generator rated voltage

- Power supply voltage: from 3 V to 5.5 V

- Thermal shutdown for overtemperature protection

- ESD protection 2.0 KV HBM

### **Applications**

- Dashboard and infotainment backlighting

- Exterior/interior lighting

- DTRLs

### **Description**

The STAP16DPPS05 is a monolithic, low voltage, low current power 16-bit shift register

designed for LED panel displays. The device contains a 16-bit serial-in, parallel-out shift register that feeds a 16-bit D-type storage register. In the output stage, sixteen regulated current sources are designed to provide 3 to 40 mA of constant current to drive the LEDs.

The STAP16DPPS05 features the open and short LED detection on the outputs. The detection circuit checks 3 different conditions which may occur on the output line: short to GND, short to Vo or open line. The data detection results are loaded in the shift register and shifted out via the serial line output. The detection functionality is implemented without increasing the pin number through a secondary function of the output enable and latch pin (DM1 and DM2) respectively). A dedicated logic sequence allows the device to enter or leave detection mode. Through an external resistor, users can adjust the output current of the STP16DPPS05 thus controlling the light intensity of the LEDs. In addition, the user can adjust the intensity of the brightness of the LED's from 0 % to 100 %

through the OE/DM2 pin. The auto power shutdown and auto power-ON feature allows the device to save power with no external intervention. The STAP16DPPS05 guarantees a 20 V output driving capability, allowing users to connect more LEDs in series. The high clock frequency, 30 MHz also satisfies the system requirement of high volume data transmission. The 3.3 V of voltage supply is very useful for applications interfacing any microcontroller from 3.3 V micro. Compared with a standard TSSOP package, the TSSOP exposed pad increases the capability of heat dissipation by a factor of 2.5.

Table 1: Device summary

| Order code       | Package               | Packing             |  |

|------------------|-----------------------|---------------------|--|

| STAP16DPPS05XTTR | TSSOP24 (exposed pad) | 2500 parts per reel |  |

November 2017 DocID024306 Rev 7 1/29

### Contents

|   | Sullillia                                 | ry description                                                       | 3                    |

|---|-------------------------------------------|----------------------------------------------------------------------|----------------------|

|   | 1.1                                       | Pin connections and description                                      | 3                    |

| 2 | Electric                                  | al ratings                                                           | 4                    |

|   | 2.1                                       | Absolute maximum ratings                                             |                      |

|   | 2.2                                       | Thermal data                                                         | 4                    |

|   | 2.3                                       | Recommended operating conditions                                     | 5                    |

| 3 | Electric                                  | al characteristics                                                   | 6                    |

| 4 | Equival                                   | ent circuit and outputs                                              | 8                    |

| 5 | •                                         | diagramsdiagrams                                                     |                      |

| 6 | •                                         | characteristics                                                      |                      |

| 7 |                                           | etection mode functionality                                          |                      |

|   |                                           |                                                                      |                      |

|   | 7.1                                       | Phase one: entering error detection mode                             | 18                   |

|   | 7.1<br>7.2                                | Phase one: entering error detection mode  Phase two: error detection |                      |

|   |                                           |                                                                      | 19                   |

|   | 7.2                                       | Phase two: error detection                                           | 19<br>21             |

|   | 7.2<br>7.3                                | Phase two: error detection                                           | 19<br>21             |

| 8 | 7.2<br>7.3<br>7.4<br>7.5                  | Phase two: error detection                                           | 19<br>21<br>21       |

| 8 | 7.2<br>7.3<br>7.4<br>7.5                  | Phase two: error detection                                           | 19<br>21<br>23       |

| 8 | 7.2<br>7.3<br>7.4<br>7.5<br><b>Packag</b> | Phase two: error detection                                           | 19<br>21<br>23<br>24 |

### 1 Summary description

**Table 2: Typical current accuracy**

| Output voltage | Current accuracy |             | Output ourrent | V <sub>DD</sub> | Temperature |  |

|----------------|------------------|-------------|----------------|-----------------|-------------|--|

| Output voltage | Between bits     | Between ICs | Output current | V DD            | remperature |  |

| ≥ 1.3 V        | ± 1 %            | ± 2 %       | 5 to 40 mA     | 3.3 V to 5 V    | 25 °C       |  |

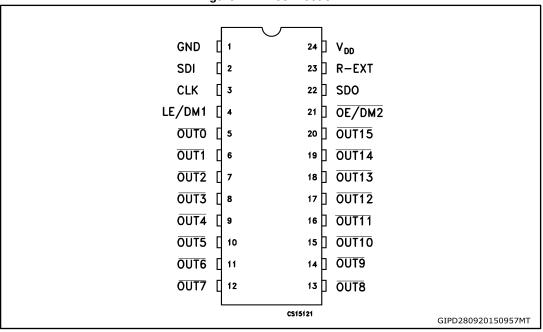

### 1.1 Pin connections and description

Figure 1: Pin connection

The exposed pad is electrically connected to a metal layer electrically isolated or connected to ground.

Table 3: Pin description

| Pin n° | Symbol                                                                                           | Name and function                                                        |  |  |  |

|--------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--|--|--|

| 1      | GND                                                                                              | Ground terminal                                                          |  |  |  |

| 2      | SDI                                                                                              | Serial data input terminal                                               |  |  |  |

| 3      | CLK                                                                                              | Clock input terminal                                                     |  |  |  |

| 4      | LE/DM1                                                                                           | Latch input terminal - detect mode 1 (see operation principle)           |  |  |  |

| 5-20   | OUT-15                                                                                           | Output terminal                                                          |  |  |  |

| 21     | 21 OE/DM2 Input terminal of output enable (active low) - detect mode 1 (see operation principle) |                                                                          |  |  |  |

| 22     | SDO                                                                                              | Serial data out terminal                                                 |  |  |  |

| 23     | R-EXT                                                                                            | Input terminal for an external resistor for constant current programming |  |  |  |

| 24     | $V_{DD}$                                                                                         | Supply voltage terminal                                                  |  |  |  |

Electrical ratings STAP16DPPS05

### 2 Electrical ratings

### 2.1 Absolute maximum ratings

Stressing the device above the rating listed in the "absolute maximum ratings" table may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Table 4: Absolute m | aximum ratir | nas |

|---------------------|--------------|-----|

|---------------------|--------------|-----|

| Symbol           | Parameter                   | Value                   | Unit |

|------------------|-----------------------------|-------------------------|------|

| $V_{dd}$         | Supply voltage              | 0 to 7                  | V    |

| Vo               | Output voltage              | -0.5 to 20              | V    |

| lo               | Output current              | 50                      | mA   |

| Vı               | Input voltage               | -0.4 to $V_{\text{dd}}$ | V    |

| I <sub>GND</sub> | GND terminal current        | 800                     | mA   |

| f <sub>CLK</sub> | Clock frequency             | 50                      | MHz  |

| T <sub>OPR</sub> | Operating temperature range | -40 to +150             | °C   |

| T <sub>STG</sub> | Storage temperature range   | -55 to +150             | °C   |

#### 2.2 Thermal data

Table 5: Thermal data

| Symbol               | Parar                                              | Value                     | Unit |      |

|----------------------|----------------------------------------------------|---------------------------|------|------|

| R <sub>thj-amb</sub> | Thermal resistance junction-ambient <sup>(1)</sup> | TSSOP24 (exposed pad) (2) | 37.5 | °C/W |

<sup>&</sup>lt;sup>(1)</sup>According to JEDEC standard 51-7B.

<sup>(2)</sup>The exposed pad should be soldered to the PCB in order to derive the thermal benefits.

STAP16DPPS05 Electrical ratings

### 2.3 Recommended operating conditions

**Table 6: Recommended operating conditions**

| Symbol            | Parameter            | Test condition                             | Min.                | Тур. | Max.                | Unit |

|-------------------|----------------------|--------------------------------------------|---------------------|------|---------------------|------|

| V <sub>DD</sub>   | Supply voltage       |                                            | 3.0                 | -    | 5.5                 | V    |

| Vo                | Output voltage       |                                            |                     | -    | 20                  | ٧    |

| lo                | Output current       | OUTn                                       | 3                   | -    | 40                  | mA   |

| Іон               | Output current       | SeriaL-OUT                                 |                     | -    | +1                  | mA   |

| loL               | Output current       | Serial-OUT                                 |                     | -    | -1                  | mA   |

| V <sub>IH</sub>   | Input voltage        |                                            | 0.7 V <sub>DD</sub> | -    | $V_{DD}$            | V    |

| VIL               | Input voltage        |                                            | -0.3                | -    | 0.3 V <sub>DD</sub> | V    |

| t <sub>wLAT</sub> | LE/DM1 pulse width   |                                            | 20                  | -    |                     | ns   |

| twclk             | CLK pulse width      |                                            | 10                  | -    |                     | ns   |

| twen              | OE/DM2 pulse width   | $V_{DD} = 3.0 \text{ V to } 5.0 \text{ V}$ | 100                 | -    |                     | ns   |

| tsetup(d)         | Setup time for DATA  |                                            | 8                   | -    |                     | ns   |

| thold(d)          | Hold time for DATA   |                                            | 5                   | -    |                     | ns   |

| tsetup(L)         | Setup time for LATCH |                                            | 8                   | -    |                     | ns   |

| fclk              | Clock frequency      | Cascade operation (1)                      |                     | -    | 30                  | MHz  |

$<sup>^{(1)}</sup>$ If the device is connected in cascade, it may not be possible to achieve the maximum data transfer. Please consider the timings carefully.

Electrical characteristics STAP16DPPS05

### 3 Electrical characteristics

$V_{DD}$  = 5 V,  $T_{j}$  = -40 °C to 125 °C, unless otherwise specified.

**Table 7: Electrical characteristics**

| Symbol                 | Parameter                                  | Test condition                                                                        | Min.                 | Тур. | Max.                | Unit |

|------------------------|--------------------------------------------|---------------------------------------------------------------------------------------|----------------------|------|---------------------|------|

| ViH                    | Input voltage high level                   |                                                                                       | 0.7·V <sub>DD</sub>  |      | $V_{DD}$            |      |

| V <sub>IL</sub>        | Input voltage<br>low level                 |                                                                                       | GND                  |      | 0.3·V <sub>DD</sub> | V    |

| Vol                    | Serial data output voltage                 | $I_{OL} = + 1 \text{ mA}$                                                             |                      | 0.03 | 0.4                 |      |

| $V_{OH}$               | (SDO)                                      | $I_{OH} = -1 \text{ mA}$                                                              | V <sub>DD</sub> -0.4 |      |                     |      |

| Іон                    | Output leakage current                     | Vo =19 V, OUTn = OFF                                                                  |                      | 0.5  | 2                   | μΑ   |

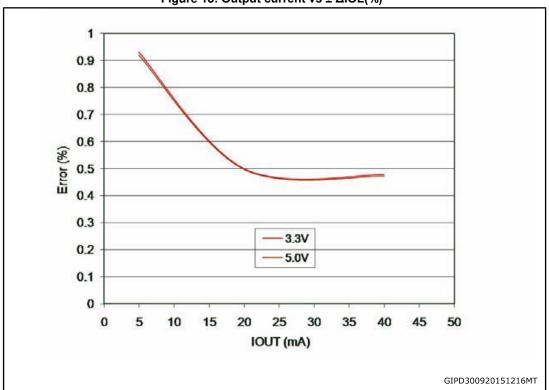

| ∆l <sub>OL1</sub>      |                                            | $V_{DD} = 3.3 \text{ V}, V_O = 0.3 \text{ V},$ $R_{\text{ext}} = 3.9 \text{ k}\Omega$ |                      | ±1   | ±5                  |      |

| ∆l <sub>OL2</sub>      | Current accuracy channel-to-channel (1)(2) | $V_{DD} = 3.3 \text{ V}, V_O = 0.6 \text{ V},$ $R_{\text{ext}} = 980 \Omega$          |                      | ±0.5 | ±4                  |      |

| ΔІ <sub>ОL3</sub>      |                                            | $V_{DD} = 3.3 \text{ V}, V_{O} = 1.3 \text{ V},$ $R_{ext} = 490 \Omega$               |                      | ±0.5 | ±4                  | %    |

| ∆l <sub>OL2</sub>      | Current accuracy device-                   | $V_{DD} = 3.3 \text{ V}, V_{O} = 0.6 \text{ V},$ $R_{ext} = 980 \Omega$               |                      |      | ±5                  |      |

| ΔІ <sub>ОL3</sub>      | to-device <sup>(1)</sup>                   | $V_{DD} = 3.3 \text{ V}, V_{O} = 1.3 \text{ V},$ $R_{ext} = 490 \Omega$               |                      |      | ±6                  |      |

| R <sub>IN</sub> (up)   | Pull-up resistor for OE pin                |                                                                                       | 150                  | 300  | 600                 |      |

| R <sub>IN</sub> (down) | Pull-down resistor for LE pin              |                                                                                       | 100                  | 200  | 400                 | kΩ   |

| IDD(AutoOff)           |                                            | $R_{ext}$ = 980 $\Omega$ , OE = low,<br>OUT0 to OUT7 = OFF                            |                      | 200  | 300                 | μΑ   |

| IDD(OFF1)              | Supply current (OFF)                       | $R_{ext}$ = 980 $\Omega$ , OE = high,<br>OUT0 to OUT7 = ON                            |                      | 5    | 7.5                 |      |

| IDD(OFF2)              |                                            | $R_{ext}$ = 490 $\Omega$ , OE = high,<br>OUT0 to OUT15 = ON                           |                      | 8    | 11                  | ^    |

| IDD(ON1)               | Supply oursent (CNI)                       | $R_{\text{ext}}$ = 980 $\Omega$ , OE = low,<br>OUT0 to OUT15 = ON                     |                      | 6    | 7.5                 | mA   |

| IDD(ON2)               | Supply current (ON)                        | $R_{\text{ext}}$ = 490 $\Omega$ , OE = low,<br>OUT0 to OUT15 = ON                     |                      | 8    | 11                  |      |

| Tsd                    | Thermal shutdown <sup>(3)</sup>            |                                                                                       |                      | 170  |                     | °C   |

<sup>&</sup>lt;sup>(1)</sup>Test performed with all outputs turned on, but only one output loaded at a time.

$<sup>^{(2)}\</sup>Delta_{IOL}$  = (( $I_{OLmax}$  -  $I_{OLmean}$ ) /  $I_{OLmean}$ ) \* 100,  $\Delta_{IOL}$  - = (( $I_{OLmin}$  -  $I_{OLmean}$ ) /  $I_{OLmean}$ ) \*100, where  $I_{OLmean}$  = ( $I_{OLout1}$ + $I_{OLout2}$ +...+ $I_{OLout16}$ ) / 16

<sup>(3)</sup>Not tested, guaranteed by design.

$V_{DD} = 5 \text{ V}, T_j = 25 \text{ °C}, \text{ unless otherwise specified.}$

Table 8: Switching characteristics (all table limits are guaranteed by design. Not tested in production.)

| Symbol            | Parameter                                                    | Test cond                                                                                                                                |                          | Min. | Тур. | Max. | Unit |

|-------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|------|------|------|

| f <sub>clk</sub>  | Clock frequency                                              | Cascade operation                                                                                                                        |                          |      |      | 30   | MHz  |

|                   | CLK- OUTn ,                                                  |                                                                                                                                          | $V_{DD} = 3.3 \text{ V}$ |      | 55   | 90   |      |

| t <sub>PLH1</sub> | $\frac{\text{LE/DM1} = \text{H,}}{\text{OE/DM2}} = \text{L}$ |                                                                                                                                          | $V_{DD} = 5 \text{ V}$   |      | 30   | 50   | ns   |

|                   | LE/DM1- OUTn ,                                               |                                                                                                                                          | V <sub>DD</sub> = 3.3 V  |      | 48   | 80   |      |

| tpLH2             | OE/DM2 = L                                                   |                                                                                                                                          | $V_{DD} = 5 V$           |      | 30   | 45   | ns   |

|                   | OE/DM2 - OUTn ,                                              |                                                                                                                                          | V <sub>DD</sub> = 3.3 V  |      | 70   | 120  |      |

| t <sub>PLH3</sub> | LE\\DM1 = H                                                  |                                                                                                                                          | $V_{DD} = 5 V$           |      | 45   | 65   | ns   |

| <b>+</b>          | CLK-SDO                                                      |                                                                                                                                          | V <sub>DD</sub> = 3.3 V  |      | 21   | 35   | ns   |

| t <sub>PLH</sub>  | CLK-SDO                                                      |                                                                                                                                          | $V_{DD} = 5 V$           |      | 15   | 25   |      |

|                   | CLK OUTn ,                                                   |                                                                                                                                          | V <sub>DD</sub> = 3.3 V  |      | 28   | 35   |      |

| t <sub>PHL1</sub> | $\frac{\text{LE/DM1} = \text{H,}}{\text{OE/DM2}} = \text{L}$ | $\label{eq:Vihamiltonian} \begin{split} V_{IH} &= V_{DD} \\ V_{IL} &= GND & C_L = 10 \ pF \\ I_O &= 20 \ mA & V_L = 3.0 \ V \end{split}$ | V <sub>DD</sub> = 5 V    |      | 22   | 40   | ns   |

|                   | LE/DM1- OUTn ,                                               | R <sub>L</sub> = 60 Ω                                                                                                                    | V <sub>DD</sub> = 3.3 V  |      | 13   | 35   |      |

| tPHL2             | OE/DM2 = L                                                   |                                                                                                                                          | V <sub>DD</sub> = 5 V    |      | 12   | 18   | ns   |

|                   | OE /DM2- OUTn ,                                              |                                                                                                                                          | $V_{DD} = 3.3 \text{ V}$ |      | 24   | 35   |      |

| t <sub>PHL3</sub> | LE/DM1 = H                                                   |                                                                                                                                          | $V_{DD} = 5 V$           |      | 21   | 30   | ns   |

|                   | CLK CDO                                                      |                                                                                                                                          | V <sub>DD</sub> = 3.3 V  |      | 24   | 40   |      |

| t <sub>PHL</sub>  | CLK-SDO                                                      |                                                                                                                                          | $V_{DD} = 5 V$           |      | 17   | 25   | ns   |

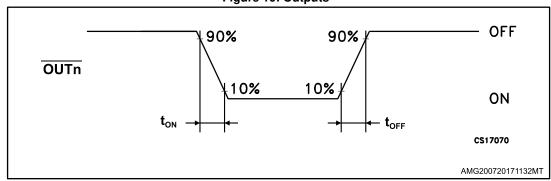

|                   | Output fall time                                             |                                                                                                                                          | V <sub>DD</sub> = 3.3 V  |      | 30   | 55   |      |

| ton               | 10~90 % of voltage waveform                                  |                                                                                                                                          | $V_{DD} = 5 V$           |      | 10   | 20   | ns   |

|                   | Output rise time                                             |                                                                                                                                          | $V_{DD} = 3.3 \text{ V}$ |      | 4    | 10   |      |

| toff              | 90~10 % of voltage<br>waveform                               |                                                                                                                                          | $V_{DD} = 5 V$           |      | 3    | 8    | ns   |

| tr                | CLK rise time (1)                                            |                                                                                                                                          |                          |      |      | 5    | μs   |

| t <sub>f</sub>    | CLK fall time <sup>(1)</sup>                                 |                                                                                                                                          |                          |      |      | 5    | μο   |

#### Notes:

<sup>(1)</sup>If devices are connected in cascade and tr or tf is large, it may be critical to achieve the timing required for data transfer between two cascaded devices.

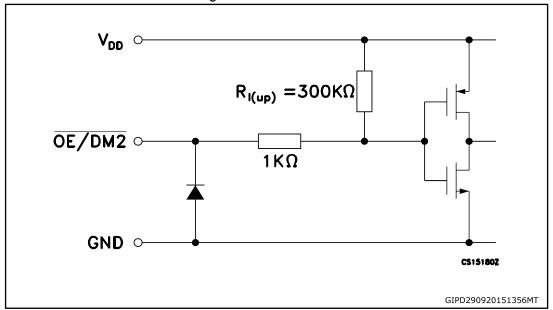

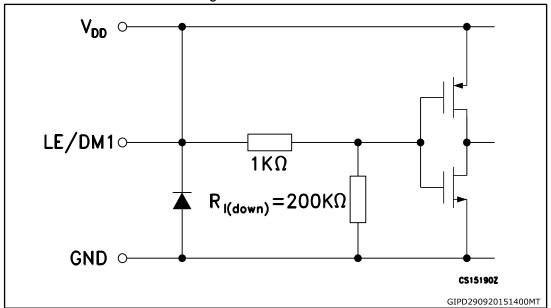

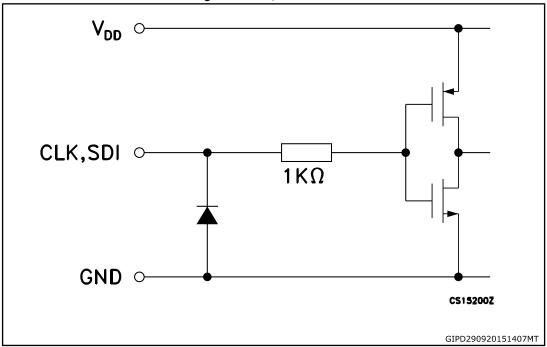

### 4 Equivalent circuit and outputs

Figure 2: OE/DM2 terminal

Figure 3: LE/DM1 terminal

Figure 4: CLK, SDI terminal

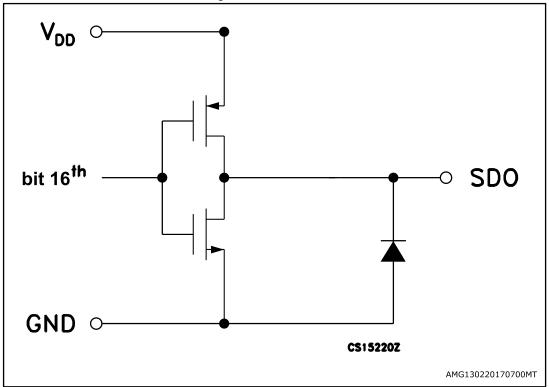

Figure 5: SDO terminal

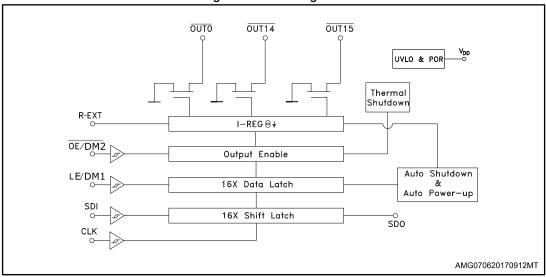

Figure 6: Block diagram

STAP16DPPS05 Timing diagrams

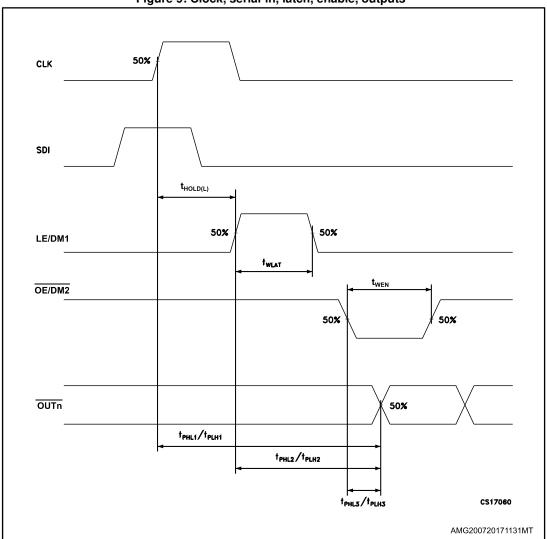

### 5 Timing diagrams

Table 9: Truth table

| Clock | LE/DM1 | OE/DM2 | Serial-IN | OUT0OUT7             | SDO     |

|-------|--------|--------|-----------|----------------------|---------|

| _ -   | Η      | L      | Dn        | Dn Dn - 7 Dn -15     | Dn - 15 |

| _ -   | L      | L      | Dn + 1    | No change            | Dn - 14 |

| _ -   | Η      | L      | Dn + 2    | Dn + 2 Dn - 5 Dn -13 | Dn - 13 |

| -  _  | X      | L      | Dn + 3    | Dn + 2 Dn - 5 Dn -13 | Dn - 13 |

| -  _  | Х      | Н      | Dn + 3    | OFF                  | Dn - 13 |

OUTn = ON when Dn = H OUTn = OFF when Dn = L.

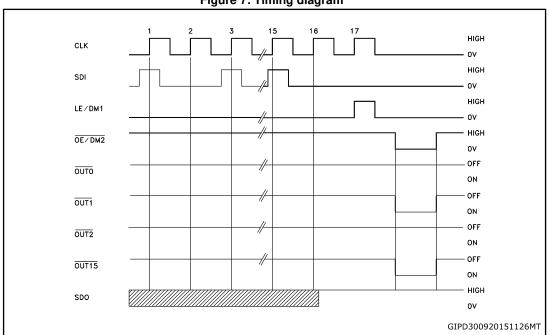

Figure 7: Timing diagram

Latch and output enable terminals are level-sensitive and are not synchronized with rising or falling edge of LE/DM1 signal. When LE/DM1 terminal is low level, the latch circuit holds previous set of data. When LE/DM1 terminal is high level, the latch circuit refreshes new set of data from SDI chain. When  $\overline{OE/DM2}$  terminal is at low level, the output terminals Out 0 to Out 15 respond to data in the latch circuits, either '1' ON or '0' OFF. When  $\overline{OE/DM2}$  terminal is at high level, all output terminals are switched OFF.

Timing diagrams STAP16DPPS05

Table 10: Enable IO: shutdown truth table

| Clock | LE/DM1 | SDI <sub>0</sub> SDI <sub>7</sub> SDI <sub>15</sub> | SH         | Auto power-up             | OUTn             |

|-------|--------|-----------------------------------------------------|------------|---------------------------|------------------|

| _ -   | Н      | AII = L                                             | Active     | Not active <sup>(1)</sup> | OFF              |

| _ -   | L      | No change                                           | No change  | No change                 | No change        |

| _ -   | Н      | One or more = H                                     | Not active | Active                    | X <sup>(2)</sup> |

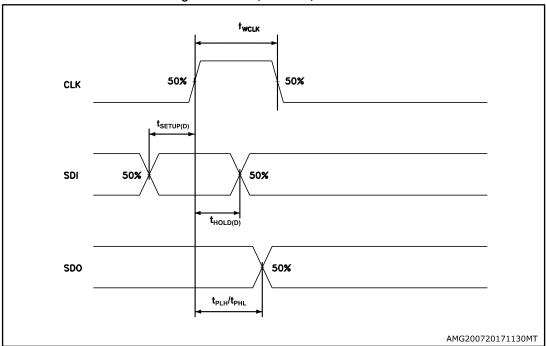

Figure 8: Clock, serial-in, serial-out

$<sup>^{(1)}\!\</sup>text{At}$  power-up, the device starts in shutdown mode.

<sup>(2)</sup>Undefined.

STAP16DPPS05 Timing diagrams

Figure 9: Clock, serial-in, latch, enable, outputs

Figure 10: Outputs

### **6** Typical characteristics

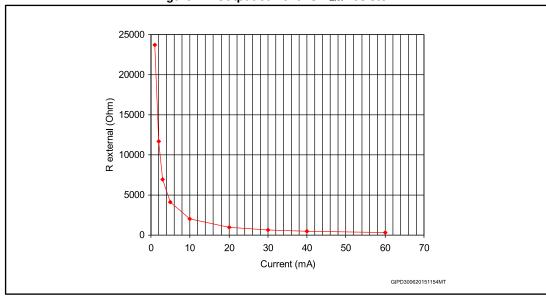

Figure 11: Output current vs Rext resistor

Table 11: Output current vs Rext resistor

| R <sub>EXT</sub> (Ω) | Output current (mA) |

|----------------------|---------------------|

| 23700                | 1                   |

| 11730                | 2                   |

| 6930                 | 3                   |

| 4090                 | 5                   |

| 2025                 | 10                  |

| 1000                 | 20                  |

| 667                  | 30                  |

| 497                  | 40                  |

| 331                  | 60                  |

#### Conditions:

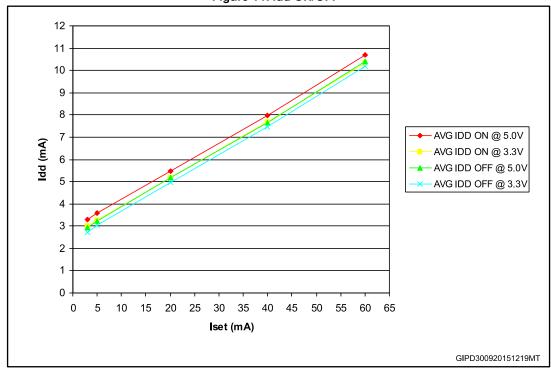

temperature = 25 °C, V<sub>DD</sub> = 3.3 V; 5.0 V, I<sub>SET</sub> = 3 mA; 5 mA; 10 mA; 20 mA; 50 mA; 60 mA.

Figure 12: I<sub>SET</sub> vs dropout voltage (V<sub>drop</sub>)

Table 12: I<sub>SET</sub> vs dropout voltage (V<sub>drop</sub>)

| lout (mA) | Avg (mV) @ 3.3 V | Avg (mV) @ 5.0 V |

|-----------|------------------|------------------|

| 3         | 36               | 37               |

| 5         | 71               | 72               |

| 10        | 163              | 163              |

| 20        | 346              | 347              |

| 40        | 724              | 726              |

| 60        | 1080             | 1110             |

$T_A = 25 \, ^{\circ}C, \, V_{DD} = 3.3 \, V; \, 5 \, V.$

Figure 13: Output current vs ± ΔIOL(%)

Figure 14: Idd ON/OFF

$P_D(W)$ 3.5 3.0 2.5 TSSOP EXP-PAD 2.0 1.5 SOP 1.0 0.5 **TSSOP** 25 75 100 125 T<sub>P</sub>(°C) GIPD300920151225MT

Figure 15: Power dissipation vs package temperature

The exposed pad should be soldered to the PCB to obtain the thermal benefits.

#### Notes:

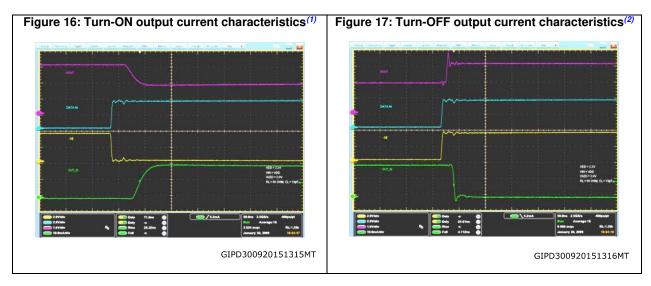

#### Electrical conditions:

- $V_{DD} = 3.3 \text{ V}$ ,  $Vin = V_{DD}$ , Vled = 3.0 V,  $RL = 60 \Omega$ , CL = 10 pF.

- Ch1 (yellow) = OE/DM2, Ch2 (blue) = SDI, Ch3 (purple) = VOUT, Ch4 (green) = OUT.

$<sup>^{(1)}</sup>$ The reference level for the TON characteristics is 50 % of OE/DM2 signal and 90 % of output current.

$<sup>^{(2)}</sup>$ The reference level for the TOFF characteristics is 50 % of OE/DM2 signal and 10 % of output current.

### 7 Error detection mode functionality

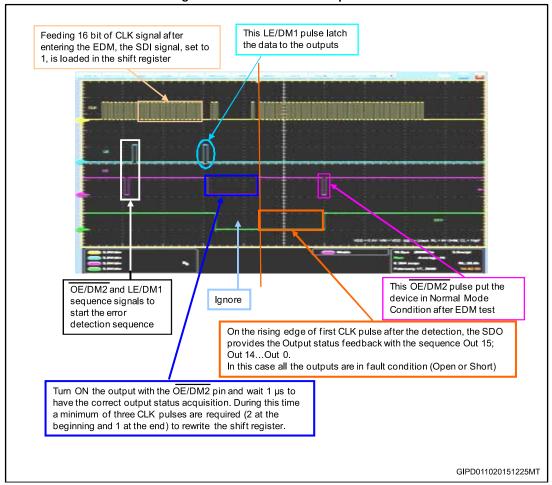

### 7.1 Phase one: entering error detection mode

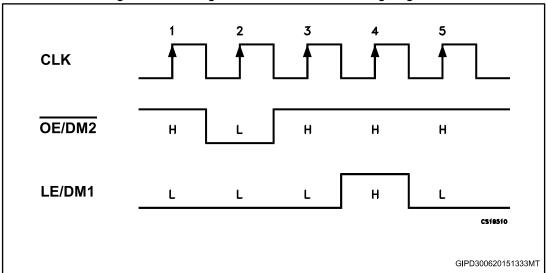

From the "normal mode" condition the device can switch to "error mode" by a logic sequence on the  $\overline{\text{OE}/\text{DM2}}$  and LE/DM1 pins, as shown in the following table and diagram:

Table 13: Entering error detection mode - truth table

| CLK    | 1° | <b>2</b> ° | 3° | 4° | 5° |

|--------|----|------------|----|----|----|

| OE/DM2 | Н  | L          | Н  | Н  | Н  |

| LE/DM1 | L  | L          | L  | Н  | L  |

Figure 18: Entering error detection mode - timing diagram

After these five CLK cycles, the device goes into the "error detection mode" and at the 6<sup>th</sup> rising edge of the CLK, the SDI data are ready for sampling.

18/29 DocID024306 Rev 7

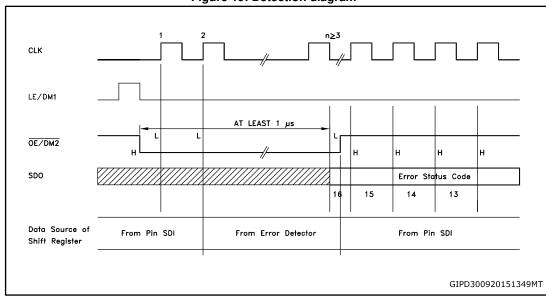

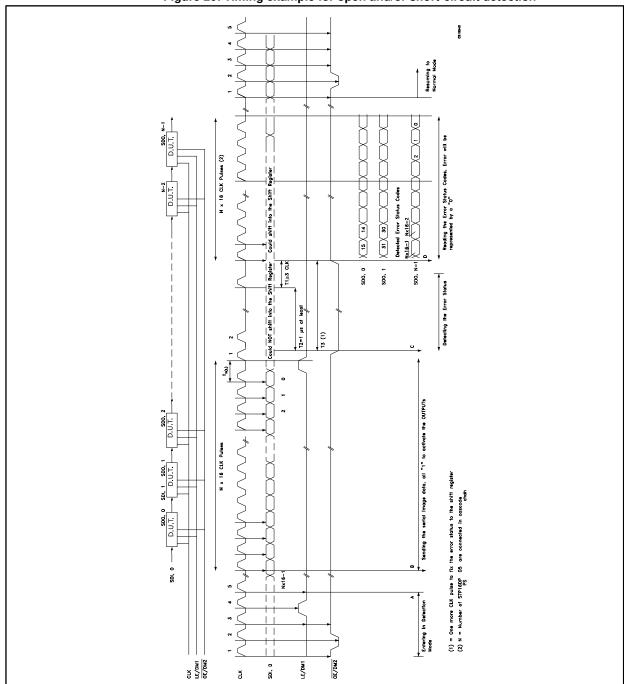

#### 7.2 Phase two: error detection

The 16 data bits must be set to "1" in order to set ON all the outputs during detection. The data are latched by LE/DM1 and after that the outputs are ready for the detection process.

When the microcontroller switches the  $\overline{OE/DM2}$  to LOW, the device drives the LEDs in order to analyze if an OPEN or SHORT condition has occurred.

Figure 19: Detection diagram

The LED status is detected in 1 microsecond (minimum) and after this time the microcontroller sets  $\overline{\text{OE}/\text{DM2}}$  in HIGH state and the output data detection results go to the microprocessor via SDO.

Detection mode and normal mode both use the same data format. As soon as all the detection data bits are available on the serial line, the device may go back to normal mode of operation. To re-detect the status, the device must go back in normal mode and re-enter error detection mode.

Figure 20: Timing example for open and/or short-circuit detection

#### 7.3 Phase three: resuming normal mode

The sequence for re-entering normal mode is shown in the following table:

Table 14: Resuming normal mode - timing diagram

| CLK    | 1° | 2° | 3° | <b>4</b> ° | 5° |

|--------|----|----|----|------------|----|

| OE/DM2 | Н  | L  | Н  | Н          | Н  |

| LE/DM1 | L  | L  | L  | L          | L  |

For proper device operation, the "entering error detection" sequence must be followed by a "resume mode" sequence, it is not possible to insert consecutive equal sequences.

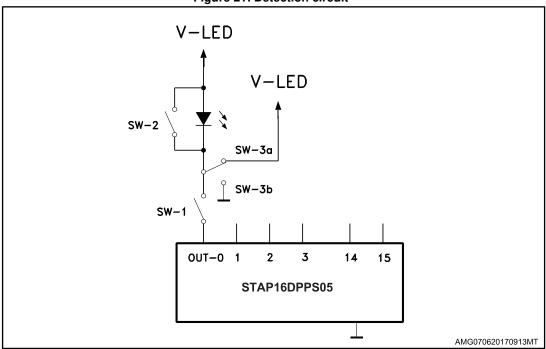

#### 7.4 Error detection conditions

Table 15: Detection conditions (VDD = 3.3 to 5 V, temperature range -40 to 125 °C)

| Configuration    | Detect mode                                 | De                         | tection resul        | Its                  |

|------------------|---------------------------------------------|----------------------------|----------------------|----------------------|

| SW-1 or<br>SW-3b | Open line or output short to GND detected   | ==> lodec ≤ 0.5 x lo       | No error<br>detected | ==> lodec ≥ 0.5 x lo |

| SW-2 or<br>SW-3a | Short on LED or short to V-<br>LED detected | ==> V <sub>0</sub> ≥ 2.6 V | No error<br>detected | ==> Vo ≤ 2.3 V       |

Where:  $I_0$  = the output current programmed by the  $R_{\text{EXT}}$ ,  $I_{\text{ODEC}}$  = the detected output current in detection mode.

Figure 21: Detection circuit

Figure 22: Error detection sequence

#### 7.5 Auto power-saving

The auto power-saving feature minimizes the quiescent current if no active data is detected on the latches and auto powers-up the device as the first active data is latched.

AMG070620170914MT

Figure 23: Auto power-saving feature

#### Conditions:

- Temp. =  $25 \, ^{\circ}\text{C}$ ,  $V_{DD} = 3.3 \, \text{V}$ ,  $Vin = V_{DD}$ ,  $VLed = 3.0 \, \text{V}$ ,  $Iset = 20 \, \text{mA}$

- Ch1 (yellow) = CLK, Ch2 (blue) = SDI, Ch3 (purple) = LE/DM1, Ch4 (green) = IDD

#### Idd consumption:

- Idd (normal operation) = 2.93 mA

- Idd (shutdown condition) = 170 μA

AMG070620170915MT

Figure 24: Auto power-saving feature: first output TON

#### Conditions:

- Temp. = 25 °C, V<sub>DD</sub> = 3.3 V, Vin = V<sub>DD</sub>, VLed = 3.0 V, Iset = 20 mA

- Ch1 (yellow) = CLK, Ch2 (blue) = SDI, Ch3 (purple) = LE/DM1, Ch4 (green) = IDD

When the device goes from auto power-saving to normal operating condition, the first output switching ON shows the  $T_{ON}$  condition as seen in the plot above.

### 8 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: **www.st.com**. ECOPACK® is an ST trademark.

STAP16DPPS05 Package information

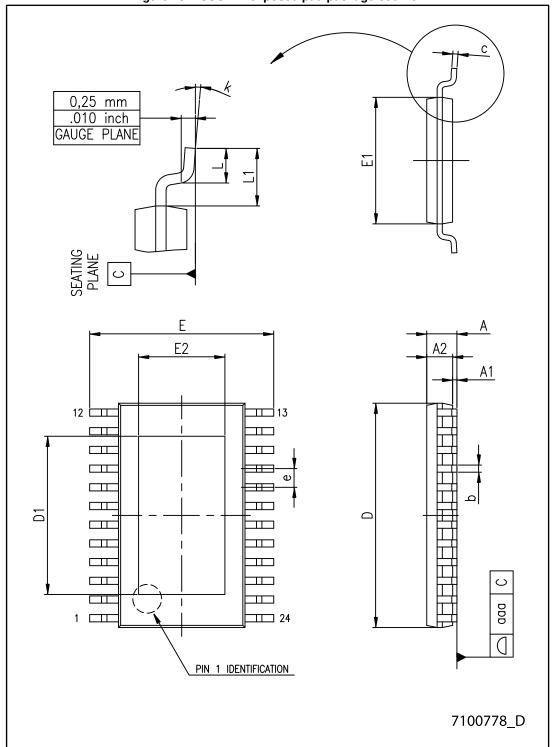

### 8.1 TSSOP24 exposed pad package information

Figure 25: TSSOP24 exposed pad package outline

Table 16: TSSOP24 exposed pad mechanical data

| Dim.   | mm   |      |      |  |  |

|--------|------|------|------|--|--|

| Diiii. | Min. | Тур. | Max. |  |  |

| А      |      |      | 1.20 |  |  |

| A1     |      |      | 0.15 |  |  |

| A2     | 0.80 | 1.00 | 1.05 |  |  |

| b      | 0.19 |      | 0.30 |  |  |

| С      | 0.09 |      | 0.20 |  |  |

| D      | 7.70 | 7.80 | 7.90 |  |  |

| D1     | 4.80 | 5.00 | 5.2  |  |  |

| Е      | 6.20 | 6.40 | 6.60 |  |  |

| E1     | 4.30 | 4.40 | 4.50 |  |  |

| E2     | 3.00 | 3.20 | 3.40 |  |  |

| е      |      | 0.65 |      |  |  |

| L      | 0.45 | 060  | 0.75 |  |  |

| L1     |      | 1.00 |      |  |  |

| k      | 0°   |      | 8°   |  |  |

| aaa    |      |      | 0.10 |  |  |

STAP16DPPS05 Package information

### 8.2 TSSOP24 packing information

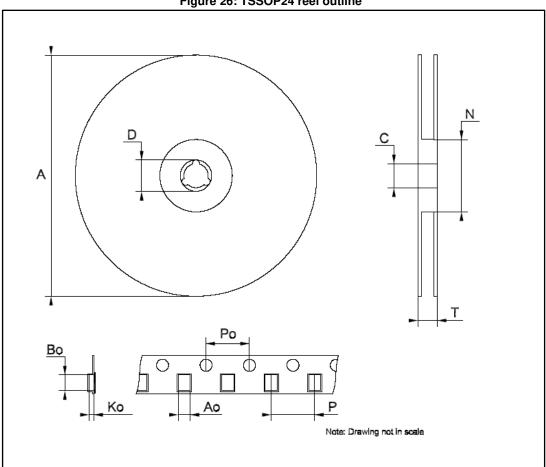

Figure 26: TSSOP24 reel outline

Table 17: TSSOP24 tape and reel mechanical data

| Dim.   | mm   |           |      |  |  |

|--------|------|-----------|------|--|--|

| Dilli. | Min. | Min. Typ. |      |  |  |

| А      |      | -         | 330  |  |  |

| С      | 12.8 | -         | 13.2 |  |  |

| D      | 20.2 | -         |      |  |  |

| N      | 60   | -         |      |  |  |

| Т      |      | -         | 22.4 |  |  |

| Ao     | 6.8  | -         | 7    |  |  |

| Во     | 8.2  | -         | 8.4  |  |  |

| Ko     | 1.7  | -         | 1.9  |  |  |

| Po     | 3.9  | -         | 4.1  |  |  |

| Р      | 11.9 | -         | 12.1 |  |  |

Revision history STAP16DPPS05

### 9 Revision history

Table 18: Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                                   |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21-May-2013 | 1        | Initial release.                                                                                                                                                                                                          |

| 01-Jul-2013 | 2        | Added footnote in Table 8: Switching characteristics.                                                                                                                                                                     |

| 11-Oct-2013 | 3        | Modified TOPR value in Table 4: Absolute maximum ratings.                                                                                                                                                                 |

| 10-Mar-2014 | 4        | Modified footnote 1 in Table 8: Switching characteristics.  Added footnote 2 in Table 8: Switching characteristics.  Updated Table 1: Pin connections and Table 3: Pin description.                                       |

| 05-Jun-2014 | 5        | Updated Table 16: TSSOP24 exposed pad mechanical data. Minor text changes.                                                                                                                                                |

| 10-Nov-2015 | 6        | Updated features in cover page. Minor text changes.                                                                                                                                                                       |

| 07-Nov-2017 | 7        | Updated title in cover page.  Updated Figure 5: "SDO terminal", Figure 8: "Clock, serial-in, serial-out", Figure 9: "Clock, serial-in, latch, enable, outputs" and Section 8: "Package information".  Minor text changes. |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics - All rights reserved