## HD-4702

## NOT RECOMMENDED FOR NEW DESIGNS NO RECOMMENDED REPLACEMENT contact our Technical Support Center at

1-888-INTERSIL or www.intersil.com/tsc

DATASHEET

FN2954 Rev 2.00 August 24, 2006

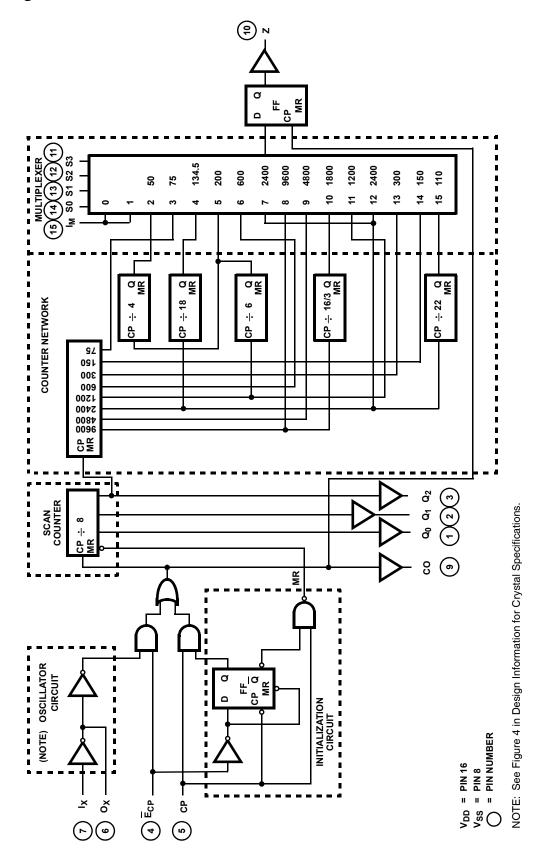

The HD-4702 Bit Rate Generator provides the necessary clock signals for digital data transmission systems, such as a UART. It generates 13 commonly used bit rates using an onchip crystal oscillator or an external input. For conventional operation generating 16 output clock pulses per bit period. the input clock frequency must be 2.4576MHz (i.e. 9600 Baud x 16 x 16, since there is an internal 3 16 prescaler). A lower input frequency will result in a proportionally lower output frequency.

CMOS Programmable Bit Rate Generator

The HD-4702 can provide multi-channel operation with a minimum of external logic by having the clock frequency CO and the 3 8 prescaler outputs Q0, Q1, Q2 available externally. All signals have a 50% duty cycle except 1800 Baud, which has less than 0.39% distortion.

The four rate select inputs (S0-S3) select which bit rate is at the output (Z). See Truth Table for Rate Select Inputs for select code and output bit rate. Two of the 16 select codes for the HD-4702 do not select an internally generated frequency, but select an input into which the user can feed either a different frequency, or a static level (High or Low) to generate "ZERO BAUD".

The bit rates most commonly used in modern data terminals (110, 150, 300, 1200, 2400 Baud) require that no more than one input be grounded for the HD-4702, which is easily achieved with a single 5-position switch.

The HD-4702 has an initialization circuit which generates a master reset for the scan counter. This signal is derived from a digital differentiator that senses the first high level on the CP input after the ECP input goes low. When ECP is high, selecting the crystal input, CP must be low. A high level on CP would apply a continuous reset. See Clock Modes and Initialization below.

#### **Features**

- HD-4702 Provides 13 Commonly Used Bit Rates

- · Uses a 2.4576MHz Crystal/Input for Standard Frequency Output (16 Times Bit Rate)

- · Low Power Dissipation

- · Conforms to EIA RS-404

- One HD-4702 Controls up to Eight Transmission Channels

- Initialization Circuit Facilitates Diagnostic Fault Isolation

- On-Chip Input Pull-Up Circuit

## Ordering Information

| PACKAGE           | TEMP.<br>RANGE<br>(°C) | PART<br>NUMBER | PART<br>MARKING | PKG.<br>NO. |

|-------------------|------------------------|----------------|-----------------|-------------|

| PDIP              | -40 to +85             | HD3-4702-9     | HD3-4702-9      | E16.3       |

| PDIP<br>(Pb-free) | -40 to +85             | HD3-4702-9Z*   | HD3-4702-9Z     | E16.3       |

| CerDIP<br>SMD#    | -55 to +125            | 5962-9051801ME | ĒΑ              | F16.3       |

\*Pb-free PDIPs can be used for through hole wave solder processing only. They are not intended for use in Reflow solder processing applications.

## Truth Table TRUTH TABLE FOR RATE SELECT INPUTS (Using 2.4576MHz Crystal)

| (== 3 = = , ==, , |    |    |    |                 |  |  |

|-------------------|----|----|----|-----------------|--|--|

| S3                | S2 | S1 | S0 | OUTPUT RATE (Z) |  |  |

| L                 | L  | L  | L  | MUX Input (IM)  |  |  |

| L                 | L  | L  | Н  | MUX Input (IM)  |  |  |

| L                 | L  | Н  | L  | 50 Baud         |  |  |

| L                 | L  | Н  | Н  | 75 Baud         |  |  |

| L                 | Н  | L  | L  | 134.5 Baud      |  |  |

| L                 | Н  | L  | Н  | 200 Baud        |  |  |

| L                 | Н  | Н  | L  | 600 Baud        |  |  |

| L                 | Н  | Н  | Н  | 2400 Baud       |  |  |

| Н                 | L  | L  | L  | 9600 Baud       |  |  |

| Н                 | L  | L  | Н  | 4800 Baud       |  |  |

| Н                 | L  | Н  | L  | 1800 Baud       |  |  |

| Н                 | L  | Н  | Н  | 1200 Baud       |  |  |

| Н                 | Н  | L  | L  | 2400 Baud       |  |  |

| Н                 | Н  | L  | Н  | 300 Baud        |  |  |

| Н                 | Н  | Н  | L  | 150 Baud        |  |  |

| Н                 | Н  | Н  | Н  | 110 Baud        |  |  |

NOTE: 19200 Baud by connecting Q2 to IM.

### **Pinout**

#### HD-4702 (16 Ld PDIP) TOP VIEW Q0 1 16 V<sub>CC</sub> 15 I<sub>M</sub> 14 S0 Q2 13 S1 12 S2 11 S3 6 Oy 10 Z I<sub>X</sub> 7 9 CO GND 8

## Pin Description

| PIN NUMBER     | TYPE | SYMBOL                          | DESCRIPTION                                                                                                         |  |

|----------------|------|---------------------------------|---------------------------------------------------------------------------------------------------------------------|--|

| 16             |      | V <sub>CC</sub>                 | $V_{CC}$ : Is the +5V power supply pin. A $0.1\mu F$ capacitor between pins 16 and 8 is recommended for decoupling. |  |

| 8              |      | GND                             | GROUND                                                                                                              |  |

| 5              | I    | CP                              | EXTERNAL CLOCK INPUT                                                                                                |  |

| 4              | I    | E <sub>CP</sub>                 | EXTERNAL CLOCK ENABLE: A low signal on this input allows the baud rate to be generated from the CP input.           |  |

| 7              | I    | lχ                              | CRYSTAL INPUT                                                                                                       |  |

| 6              | 0    | O <sub>X</sub>                  | CRYSTAL DRIVE OUTPUT                                                                                                |  |

| 15             | I    | I <sub>M</sub>                  | MULTIPLEXED INPUT                                                                                                   |  |

| 11, 12, 13, 14 | I    | S0 - S3                         | BAUD RATE SELECT INPUTS                                                                                             |  |

| 9              | 0    | co                              | CLOCK OUTPUT                                                                                                        |  |

| 1, 2, 3        | 0    | Q <sub>0</sub> - Q <sub>2</sub> | SCAN COUNTER OUTPUTS                                                                                                |  |

| 10             | 0    | Z                               | BIT RATE OUTPUT                                                                                                     |  |

### **CLOCK MODES AND INITIALIZATION**

| IX | E <sub>CP</sub> | СР                 | OPERATION                          |

|----|-----------------|--------------------|------------------------------------|

| 7  | Н               | L                  | Clocked from I <sub>X</sub>        |

| Х  | L               | 77                 | Clocked from CP                    |

| Х  | Н               | H Continuous Reset |                                    |

| Х  | L               |                    | Reset During 1st CP = High<br>Time |

H = HIGH Level

L = LOW Level

X = Don't Care

\_\_\_\_ = Clock Pulse

$\bot$  = 1st HIGH Level Clock Pulse after  $\overline{E}_{CP}$  goes LOW

NOTE: Actual output frequency is 16 times the indicated Output Rate, assuming a clock frequency of 2.4576MHz.

## **Block Diagram**

## Application Information

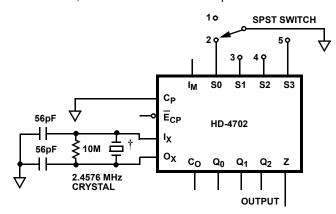

#### Single Channel Bit Rate Generator

Figure 1 shows the simplest application of the HD-4702. This circuit generates one of five possible bit rates as determined by the setting of a single pole, 5-position switch. The Bit Rate Output (Z) drives one standard TTL load or four low power Schottky loads over the full temperature range. The possible output frequencies correspond to 110, 150, 300, 1200, and 2400 Baud. For many low cost terminals, these five bit rates are adequate.

† See Table 1.

| SWITCH POSITION | HD-4702 BIT RATE |

|-----------------|------------------|

| 1               | 110 Baud         |

| 2               | 150 Baud         |

| 3               | 300 Baud         |

| 4               | 1200 Baud        |

| 5               | 2400 Baud        |

FIGURE 1. SWITCH SELECTABLE BIT RATE GENERATOR CON-FIGURATION PROVIDING FIVE BIT RATES

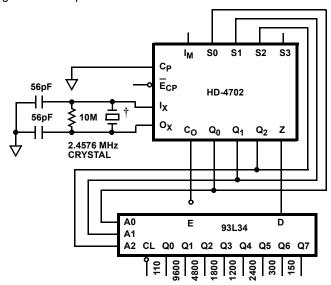

#### **Simultaneous Generation of Several Bit Rates**

Figure 2 shows a simple scheme that generates eight bit rates on eight output lines, using one HD-4702 and one 93L34 Bit Addressable Latch. This and the following applications take advantage of the built-in scan counter (prescaler) outputs. As shown in the block diagram, these outputs ( $Q_0$  to  $Q_2$ ) go through a complete sequence of eight states for every half-period of the highest output frequency (9600 Baud). Feeding these Scan Counter Outputs back to the Select Inputs of the multiplexer causes the HD-4702 to interrogate sequentially eight different frequency signals. The 93L34 8-bit addressable Latch, addressed by the same Scan Counter Outputs, re-converts the multiplexed single Output (Z) of the HD-4702 into eight parallel output frequency signals. In the simple scheme of Figure 2, input S3 is left open (HIGH) and the following bit rates are generated:

Q0: 110 Baud Q1: 9600 Baud Q2: 4800 Baud Q3: 1800 Baud Q4: 1200 Baud Q5: 2400 Baud

Other bit rate combinations can be generated by changing the

Scan Counter to Selector interconnection or by inserting logic gates into this path.

† See Table 1.

FIGURE 2. BIT RATE GENERATOR CONFIGURATION WITH EIGHT SIMULTANEOUS FREQUENCIES

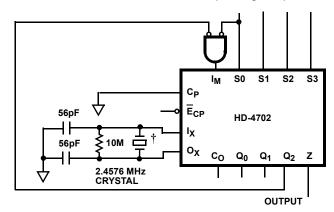

#### 19200 Baud Operation

Though a 19200 Baud signal is not internally routed to the multiplexer, the HD-4702 can be used to generate this bit rate by connecting the  $\rm Q_2$  output to IM input and applying select code. An additional 2-input NOR gate can be used to retain the "Zero Baud" feature on select code 1 for the HD-4702 (See Figure 3).

† See Table 1.

FIGURE 3. 19200 BAUD OPERATION

TABLE 1. CRYSTAL SPECIFICATIONS

| PARAMETERS              | TYPICAL CRYSTAL SPEC |

|-------------------------|----------------------|

| Frequency               | 2.4576MHz "AT" Cut   |

| Series Resistance (Max) | 250                  |

| Unwanted Modes          | -6.0dB (Min)         |

| Type of Operation       | Parallel             |

| Load Capacitance        | 32pF +0.5            |

### **Absolute Maximum Ratings**

| Supply Voltage               | +8.0V                              |

|------------------------------|------------------------------------|

| Input, Output or I/O Voltage | GND -0.5V to V <sub>CC</sub> +0.5V |

| ESD Classification           |                                    |

| Typical Derating Factor      | 1mA/MHz Increase in ICCOP          |

#### Thermal Information

| Thermal Resistance (Typical)           | $\theta_{\sf JA}$ | $\theta$ JC         |

|----------------------------------------|-------------------|---------------------|

| CERDIP Package                         | 78°C/W            | 23°C/W              |

| PDIP Package                           | 90°C/W            | N/A                 |

| Storage Temperature Range              | 65 <sup>0</sup>   | C to +150°C         |

| Maximum Junction Temperature           |                   |                     |

| Ceramic Package                        |                   | +175 <sup>0</sup> C |

| Plastic Package                        |                   | +150 <sup>o</sup> C |

| Maximum Lead Temperature (Soldering 10 | s)                | +300 <sup>o</sup> C |

#### **Die Characteristics**

Gate Count .......720 Gates

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

### **Operating Conditions**

Operating Voltage Range .....+4.5V to +5.5V

Operating Temperature Range HD-4702-9 . . . . . -40°C to +85°C

$V_{CC} = 5V \pm 10\%, \ T_A = -40^{o}C \ to \ +85^{o}C \ (HD-4702-9), \ T_A = -55^{o}C \ to \ +125^{o}C \ (HD-4702-8)$ **Electrical Specifications**

|                  |                                            | LIMITS               |                     |       |                                                                                                        |

|------------------|--------------------------------------------|----------------------|---------------------|-------|--------------------------------------------------------------------------------------------------------|

| SYMBOL           | PARAMETER                                  | MIN                  | MAX                 | UNITS | TEST CONDITIONS                                                                                        |

| $V_{IH}$         | Input High Voltage                         | V <sub>CC</sub> 70%  | -                   | V     | V <sub>CC</sub> = 4.5V                                                                                 |

| $V_{IL}$         | Input Low Voltage                          | -                    | V <sub>CC</sub> 30% | V     | V <sub>CC</sub> = 4.5V                                                                                 |

| V <sub>OH1</sub> | Output High Voltage                        | V <sub>CC</sub> -0.1 | -                   | V     | $I_{OH} \le -1 \mu A$ , $V_{CC} = 4.5 V$ , (Note 1)                                                    |

| V <sub>OL1</sub> | Output Low Voltage                         | -                    | 0.1                 | V     | $I_{OL} \le +1 \mu A$ , $V_{CC} = 4.5 V$ , (Note 1)                                                    |

| I <sub>IH</sub>  | Input High Current                         | -1                   | +1                  | μΑ    | $V_{IN} = V_{CC}$ , All 0ther Pins = 0V, $V_{CC} = 5.5$ V                                              |

| I <sub>ILX</sub> | Input Low Current (I <sub>X</sub> Input)   | -1                   | +1                  | μА    | $V_{IN}$ = 0V, All Other Pins = $V_{CC}$ , $V_{CC}$ = 5.5V                                             |

| I <sub>IL</sub>  | Input Low Current<br>(All Other Inputs)    | -                    | -100                | μА    | $V_{IN}$ = 0V, All Other Pins = $V_{CC}$ , $V_{CC}$ = 5.5V (Note 2)                                    |

| I <sub>OHX</sub> | Output High Current (O <sub>X</sub> )      | -0.1                 | -                   | mA    | $V_{OUT} = V_{CC}$ - 0.5, $V_{CC} = 4.5V$ , Input at 0V or $V_{CC}$ per Logic Function or Truth Table  |

| I <sub>OH1</sub> | Output High Current<br>(All Other Outputs) | -1.0                 | -                   | mA    | $V_{OUT}$ = 2.5V, $V_{CC}$ = 4.5V, Input at 0V or $V_{CC}$ per Logic Function or Truth Table           |

| I <sub>OH2</sub> | Output High Current<br>(All Other Outputs) | -0.3                 | -                   | mA    | $V_{OUT} = V_{CC}$ -0.5, $V_{CC} = 4.5V$ , Input at 0V or $V_{CC}$ per Logic Function or Truth Table   |

| l <sub>OLX</sub> | Output Low Current (O <sub>X</sub> )       | 0.1                  | -                   | mA    | $V_{OUT} = 0.4V$ , $V_{CC} = 4.5V$ , Input at 0V or $V_{CC}$ per Logic Function or Truth Table         |

| l <sub>OL</sub>  | Output Low Current<br>(All Other Outputs)  | 1.6                  | -                   | mA    | $V_{OUT}$ = 0.4V, $V_{CC}$ = 4.5V Input, at 0V or $V_{CC}$ per Logic Function or Truth Table           |

| lcc              | Supply Current<br>(Static)                 | -                    | 1500                | μА    | $\overline{E}_{CP} = V_{CC}$ , $CP = 0V$ , $V_{CC} = 5.5V$ ,<br>All Other Inputs = GND, (Note 2)       |

|                  |                                            | -                    | 1000                | μА    | $\overline{E}_{CP} = V_{CC}$ , $CP = 0V$ , $V_{CC} = 5.5V$ ,<br>All Other Inputs = $V_{CC}$ , (Note 2) |

#### NOTES:

- 1. Interchanging of force and sense conditions is permitted.

- 2. Input Current and Quiescent Power Supply Current are relatively higher for this device because of active pull-up circuits on all inputs except IX.

## **Electrical Specifications** $V_{CC} = 5V \pm 10\%$ , $T_A = -40^{\circ}C$ to $+85^{\circ}C$ (HD-4702-9), $T_A = -55^{\circ}C$ to $+125^{\circ}C$ (HD-4702-8)

|                      |                                                   | LI  | MITS     |       | TEGT                                              |

|----------------------|---------------------------------------------------|-----|----------|-------|---------------------------------------------------|

| SYMBOL               | AC PARAMETER                                      | MIN | MAX      | UNITS | TEST<br>CONDITIONS                                |

| t <sub>PLH</sub>     | Propagation Delay, I <sub>X</sub> to CO           | -   | 350      | ns    |                                                   |

| <sup>t</sup> PHL     |                                                   | -   | 275      | ns    |                                                   |

| <sup>t</sup> PLH     | Propagation Delay, CP to CO                       | -   | 260      | ns    |                                                   |

| <sup>t</sup> PHL     |                                                   | -   | 220      | ns    |                                                   |

| <sup>t</sup> PLH     | Propagation Delay, CO to Qn                       | -   | (Note 2) | ns    |                                                   |

| <sup>t</sup> PHL     |                                                   | -   | (Note 2) | ns    |                                                   |

| <sup>t</sup> PLH     | Propagation Delay, CO to Z                        | -   | 85       | ns    |                                                   |

| t <sub>PHL</sub>     |                                                   | -   | 75       | ns    |                                                   |

| tTLH                 | Output Transition Time (Except O <sub>X</sub> )   | -   | 160      | ns    | $V_{CC} = 4.5V$ $C_{L} \le 7pF \text{ on } O_{X}$ |

| t <sub>THL</sub>     | 7                                                 | -   | 75       | ns    | C <sub>L</sub> = 50pF<br>(Note 1)                 |

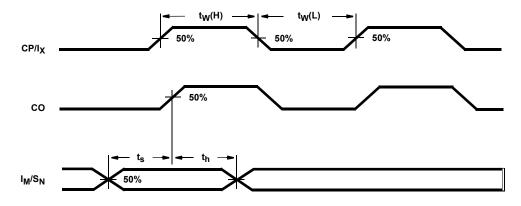

| t <sub>s</sub>       | Set-Up Time, Select to CO                         | 350 | -        | ns    | (1.6.6.1)                                         |

| t <sub>h</sub>       | Hold Time, Select to CO                           | 0   | -        | ns    |                                                   |

| t <sub>s</sub>       | Set-Up Time, I <sub>M</sub> to CO                 | 350 | -        | ns    |                                                   |

| t <sub>h</sub>       | Hold Time, I <sub>M</sub> to CO                   | 0   | -        | ns    |                                                   |

| t <sub>wCP</sub> (L) | Minimum Clock Pulse Width, Low (Notes 3, 4)       | 120 | -        | ns    |                                                   |

| t <sub>wCP</sub> (H) | Minimum Clock Pulse Width, High (Notes 3, 4)      | 120 | -        | ns    |                                                   |

| t <sub>wCP</sub> (L) | Minimum I <sub>X</sub> Pulse Width, Low (Note 4)  | 160 | -        | ns    |                                                   |

| t <sub>wCP</sub> (H) | Minimum I <sub>X</sub> Pulse Width, High (Note 4) | 160 | -        | ns    |                                                   |

| t <sub>PLH</sub>     | Propagation Delay I <sub>X</sub> to CO            | -   | 300      | ns    |                                                   |

| t <sub>PHL</sub>     |                                                   | -   | 250      | ns    |                                                   |

| t <sub>PLH</sub>     | Propagation Delay CP to CO                        | -   | 215      | ns    |                                                   |

| t <sub>PHL</sub>     | 7                                                 | -   | 195      | ns    |                                                   |

| t <sub>PLH</sub>     | Propagation Delay CO to Qn                        | -   | (Note 2) | ns    | $V_{CC} = 4.5V$ $C_{L} \le 7pF \text{ on } O_{X}$ |

| t <sub>PHL</sub>     | 7                                                 | -   | (Note 2) | ns    | C <sub>L</sub> = 15pF<br>(Note 1)                 |

| t <sub>PLH</sub>     | Propagation Delay CO to Z                         | -   | 75       | ns    | (                                                 |

| t <sub>PHL</sub>     |                                                   | -   | 65       | ns    |                                                   |

| t <sub>TLH</sub>     | Output Transition Time (Except O <sub>X</sub> )   | -   | 80       | ns    |                                                   |

| t <sub>THL</sub>     |                                                   | -   | 40       | ns    |                                                   |

#### NOTES:

- 1. Propagation Delays (t<sub>PLH</sub> and t<sub>PHL</sub>) and Output Transition Times (t<sub>TLH</sub> and t<sub>THL</sub>) will change with Output Load Capacitance (C<sub>L</sub>). Setup Times (t<sub>S</sub>), Hold Times (t<sub>h</sub>), and Minimum Pulse Widths (t<sub>W</sub>) do not vary with load capacitance.

- 2. For multichannel operation, Propagation Delay (CO to Qn) plus Set-Up Time, Select to CO, is guaranteed to be  $\leq$  367ns.

- 3. The first High Level Clock Pulse after  $\overline{E}_{CP}$  goes Low must be at least 350ns long to guarantee reset of all Counters.

- 4. It is recommended that input rise and fall times to the clock inputs (CP,  $I_{\chi}$ ) be less than 15ns.

## **Capacitance** $T_A = +25^{\circ}C$ ; Frequency = 1MHz

| SYMBOL           | PARAMETER          | TYPICAL | UNITS | CONDITIONS                                     |

|------------------|--------------------|---------|-------|------------------------------------------------|

| C <sub>IN</sub>  | Input Capacitance  | 7       | pF    | All measurements are referenced the device GND |

| C <sub>OUT</sub> | Output Capacitance | 15      | pF    | device divis                                   |

## Switching Waveforms

#### NOTE:

1. Setup and Hold times are shown as positive values but may be specified as negative values.

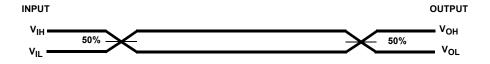

## AC Testing Input, Output Waveform

### NOTE:

1. AC Testing: All input signals must switch between  $V_{IL}$  and  $V_{IH}$ . Input rise and fall times are driven at 1ns per volt.

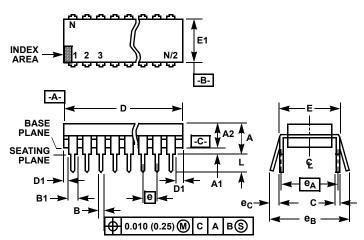

## Dual-In-Line Plastic Packages (PDIP)

#### NOTES:

- Controlling Dimensions: INCH. In case of conflict between English and Metric dimensions, the inch dimensions control.

- 3. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- 4. Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication No. 95.

- Dimensions A, A1 and L are measured with the package seated in JE-DEC seating plane gauge GS-3.

- D, D1, and E1 dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

- E and e<sub>A</sub> are measured with the leads constrained to be perpendicular to datum -C-.

- e<sub>B</sub> and e<sub>C</sub> are measured at the lead tips with the leads unconstrained.

e<sub>C</sub> must be zero or greater.

- B1 maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 inch (0.25mm).

- 10. N is the maximum number of terminal positions.

- 11. Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3, E42.6 will have a B1 dimension of 0.030 0.045 inch (0.76 1.14mm).

# E16.3 (JEDEC MS-001-BB ISSUE D) 16 LEAD DUAL-IN-LINE PLASTIC PACKAGE

|                | INC   | HES   | MILLIM | ETERS |       |

|----------------|-------|-------|--------|-------|-------|

| SYMBOL         | MIN   | MAX   | MIN    | MAX   | NOTES |

| Α              | -     | 0.210 | -      | 5.33  | 4     |

| A1             | 0.015 | -     | 0.39   | -     | 4     |

| A2             | 0.115 | 0.195 | 2.93   | 4.95  | -     |

| В              | 0.014 | 0.022 | 0.356  | 0.558 | -     |

| B1             | 0.045 | 0.070 | 1.15   | 1.77  | 8, 10 |

| С              | 0.008 | 0.014 | 0.204  | 0.355 | -     |

| D              | 0.735 | 0.775 | 18.66  | 19.68 | 5     |

| D1             | 0.005 | -     | 0.13   | -     | 5     |

| Е              | 0.300 | 0.325 | 7.62   | 8.25  | 6     |

| E1             | 0.240 | 0.280 | 6.10   | 7.11  | 5     |

| е              | 0.100 | BSC   | 2.54   | BSC   | -     |

| e <sub>A</sub> | 0.300 | BSC   | 7.62   | BSC   | 6     |

| e <sub>B</sub> | -     | 0.430 | -      | 10.92 | 7     |

| L              | 0.115 | 0.150 | 2.93   | 3.81  | 4     |

| N              | 1     | 6     | 1      | 6     | 9     |

Rev. 0 12/93

© Copyright Intersil Americas LLC 2002-2006. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see <a href="https://www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>