**Features**

# **Timing Element**

#### **General Description**

The DS1124 is an 8-bit programmable timing element similar in function to the DS1021-25. The 256-delay intervals are programmed by using a 3-wire serial interface. With a 0.25ns step size, the DS1124 can provide a delay time from 20ns up to 84ns with an integral nonlinearity of ±3ns.

### **Applications**

LCD Televisions

**Telecommunications**

Digital Test Equipment

Digital Video Projection

Signal Generators and Analyzers

#### ♦ 0.25ns Step Size

- ♦ Leading- and Trailing-Edge Accuracy

- **♦ CMOS/TTL Compatible**

- ♦ Can Delay Signals by a Full Period or More

- ♦ 3-Wire Serial Programming Interface

- ♦ Single 5.0V Power Supply

- ♦ 10-pin µSOP Package

#### **Pin Configuration**

#### TOP VIEW IN 1 10 V<sub>CC</sub> Ε $V_{CC}$ NIXIN 8 D Q DS1124 7 CLK GND GND 5 6 OUT **µSOP**

### **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE |  |  |

|--------------|----------------|-------------|--|--|

| DS1124U-25+  | -40°C to +85°C | 10 μSOP     |  |  |

| DS1124U-25+T | -40°C to +85°C | 10 μSOP     |  |  |

+Denotes a lead(Pb)-free/RoHS-compliant package. T = Tape and reel.

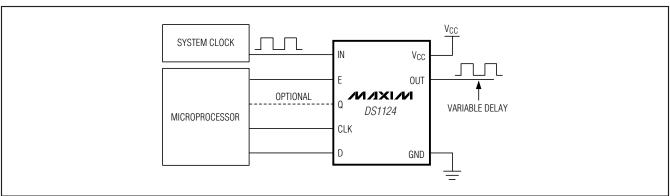

## **Typical Operating Circuit**

#### **ABSOLUTE MAXIMUM RATINGS**

Voltage Range on V<sub>CC</sub> Pin Relative to Ground .....-0.5V to +6.0V Voltage Range on IN, E, D, and CLK Relative to Ground\* .....-0.5V to (V<sub>CC</sub> + 0.5V) Operating Temperature Range ....-40°C to +85°C

Storage Temperature Range ......55°C to +125°C Short-Circuit Output Current ......50mA for 1 second Soldering Temperature .....See J-STD-020 Specification

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C)$

| PARAMETER      | SYMBOL          | CONDITIONS | MIN  | TYP | MAX                   | UNITS |

|----------------|-----------------|------------|------|-----|-----------------------|-------|

| Supply Voltage | Vcc             | (Note 1)   | 4.75 |     | 5.25                  | V     |

| Input Logic 1  | VIH             |            | 2.2  |     | V <sub>CC</sub> + 0.3 | V     |

| Input Logic 0  | V <sub>IL</sub> |            | -0.3 | •   | +0.8                  | V     |

#### DC ELECTRICAL CHARACTERISTICS

( $V_{CC}$  = +4.75V to +5.25V,  $T_A$  = -40°C to +85°C, unless otherwise noted.)

| PARAMETER                 | SYMBOL | CONDITIONS                                             | MIN  | TYP | MAX  | UNITS |

|---------------------------|--------|--------------------------------------------------------|------|-----|------|-------|

| Active Current            | ICCA   |                                                        |      | 15  | 30   | mA    |

| High-Level Output Current | ГОН    | $V_{CC} = min, V_{OH} = 2.3V$                          |      |     | -1.0 | mA    |

| Low Lovel Output Current  | lo     | Q pin, V <sub>CC</sub> = min, V <sub>OL</sub> = 0.5V   |      |     | 4.0  | m A   |

| Low-Level Output Current  | lor    | OUT pin, V <sub>CC</sub> = min, V <sub>OL</sub> = 0.5V |      |     | 8.0  | - mA  |

| Input Leakage             | IL     |                                                        | -1.0 |     | +1.0 | μΑ    |

#### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +4.75V \text{ to } +5.25V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ unless otherwise noted.})$

| PARAMETER                  | SYMBOL                            | CONDITIONS | MIN | TYP | MAX | UNITS |

|----------------------------|-----------------------------------|------------|-----|-----|-----|-------|

| Serial Clock Frequency     | fclk                              |            |     |     | 10  | MHz   |

| Input Pulse Width (E, CLK) | t <sub>EW</sub> , t <sub>CW</sub> |            | 50  |     |     | ns    |

| Data Setup to Clock        | tDSC                              |            | 30  |     |     | ns    |

| Data Hold from Clock       | tDHC                              |            | 0   |     |     | ns    |

| Data Setup to Enable       | tDSE                              |            | 30  |     |     | ns    |

| Data Hold to Enable        | tDHE                              |            | 0   |     |     | ns    |

| Enable Setup to Clock      | tES                               |            | 0   |     |     | ns    |

| Enable Hold from Clock     | tEH                               |            | 30  |     |     | ns    |

| E to Q Valid               | tEQV                              |            |     |     | 50  | ns    |

| E to Q High Impedance      | tEQZ                              |            | 0   |     | 50  | ns    |

| CLK to Q Valid             | tcqv                              |            |     |     | 50  | ns    |

| CLK to Q Invalid           | tcax                              |            | 0   |     |     | ns    |

<sup>\*</sup>Not to exceed +6.0V.

### **AC ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +4.75V \text{ to } +5.25V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.})$

| PARAMETER                                               | SYMBOL                          | CONDITIONS                                            | MIN   | TYP   | MAX  | UNITS |

|---------------------------------------------------------|---------------------------------|-------------------------------------------------------|-------|-------|------|-------|

| E to Delay Valid                                        | t <sub>EDV</sub>                |                                                       |       |       | 50   | μs    |

| E to Delay Invalid                                      | t <sub>EDX</sub>                |                                                       | 0     |       |      | ns    |

| Power-Up Time                                           | tpu                             |                                                       |       |       | 100  | ms    |

| Delay Step Size                                         | tstep                           | $T_A = +25^{\circ}C$                                  | -0.75 | +0.25 | +1   | ns    |

| Step 0 Delay                                            | t <sub>D0</sub>                 | (Note 2)                                              | 17    | 20    | 23   | ns    |

| Step 0 Delay Initial Accuracy                           |                                 | V <sub>CC</sub> = 5V, T <sub>A</sub> = +25°C          | -0.6  |       | +0.6 | ns    |

| Step 0 Voltage Variation                                |                                 |                                                       | -0.4  |       | +0.4 | ns    |

| Step 0 Temperature Variation                            |                                 | 0°C to +70°C                                          | -1    |       | +1   | ns    |

| Step 0 Temperature Variation                            |                                 | -40°C to +85°C                                        | -1    |       | +1   | ns    |

| Step 255 Delay                                          | t <sub>D255</sub>               | (Note 2)                                              | 77    | 83.75 | 88   | ns    |

| Step 255 Delay Initial Accuracy                         |                                 | V <sub>CC</sub> = 5V, T <sub>A</sub> = +25°C          | -0.6  |       | +0.6 | ns    |

| Step 255 Voltage Variation                              |                                 |                                                       | -0.4  |       | +0.4 | ns    |

| Step 255 Temperature Variation                          |                                 | 0°C to +70°C                                          | -3    |       | +3   | ns    |

| Step 255 Temperature Variation                          |                                 | -40°C to +85°C                                        | -5    |       | +5   | ns    |

| Integral Nonlinearity<br>(Deviation from Straight Line) | terr                            | V <sub>CC</sub> = 5V, T <sub>A</sub> = +25°C (Note 3) | -2    | 0     | +2   | ns    |

| Minimum Input Pulse Width                               | twı                             | (Note 4)                                              | 40    |       |      | ns    |

| Minimum Input Period                                    | tper                            | (Note 5)                                              | 80    |       |      | ns    |

| Input Rise and Fall Times                               | t <sub>R</sub> , t <sub>F</sub> | (Note 6)                                              | 0     |       | 1    | μs    |

- Note 1: All voltages are referenced to ground.

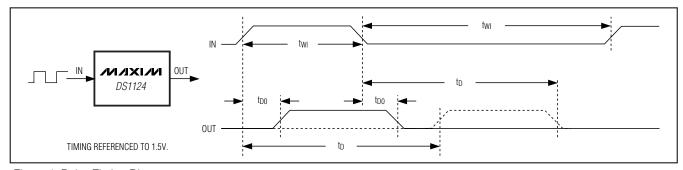

- Note 2: Measured from rising edge of the input to the rising edge of the output. The programmed delay, t<sub>D</sub>, can be programmed with values from 0 to 255. See Figure 1.

- Note 3: See the Integral Nonlinearity section and Figure 5.

- **Note 4:** This is the minimum allowable interval between transitions on the input to ensure accurate device operation. This parameter can be violated but timing accuracy may be impaired and ultimately very narrow pulse widths will result in no output from the device. See Figure 1.

- **Note 5:** When a 50% duty cycle input clock is used, this defines the highest usable clock frequency. When asymmetrical clock inputs are used, the maximum usable clock frequency must be reduced to conform to the minimum input pulse-width requirement. See Figure 1.

- **Note 6:** Faster rise and fall times give the greatest accuracy in measured delay. Slow edges (outside the specification maximum) can result in erratic operations.

Figure 1. Delay Timing Diagram

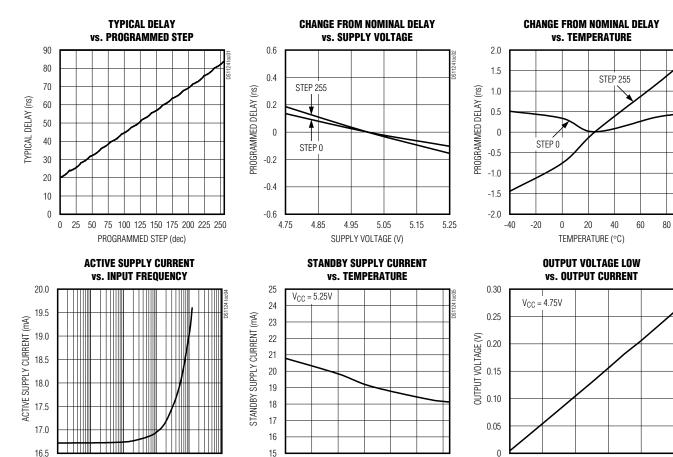

### **Typical Operating Characteristics**

( $V_{CC} = +5.0V$ ,  $T_A = +25$ °C, unless otherwise noted.)

1000

100 INPUT (IN) FREQUENCY (kHz)

10000

-40 -20 0 20 40 80

60

TEMPERATURE (°C)

6

OUTPUT CURRENT (mA)

10

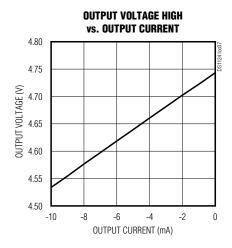

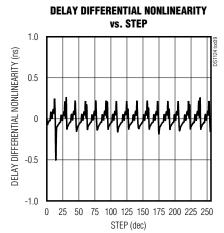

### Typical Operating Characteristics (continued)

( $V_{CC} = +5.0V$ ,  $T_A = +25$ °C, unless otherwise noted.)

## **Pin Description**

| PIN   | NAME             | FUNCTION                                       |  |  |

|-------|------------------|------------------------------------------------|--|--|

| 1     | IN               | Delay Input Signal                             |  |  |

| 2     | E                | Input Enable                                   |  |  |

| 3     | Q                | Serial Data Output                             |  |  |

| 4, 5  | GND              | ound. Both grounds must be connected.          |  |  |

| 6     | OUT              | lay Output Signal                              |  |  |

| 7     | CLK              | Serial Clock Input                             |  |  |

| 8     | D                | Serial Data Input                              |  |  |

| 9, 10 | V <sub>C</sub> C | Power Supply. Both supplies must be connected. |  |  |

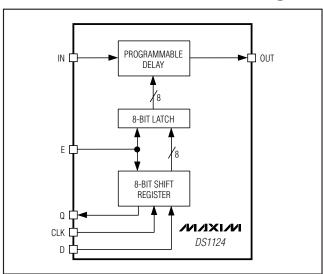

#### **Block Diagram**

#### **Detailed Description**

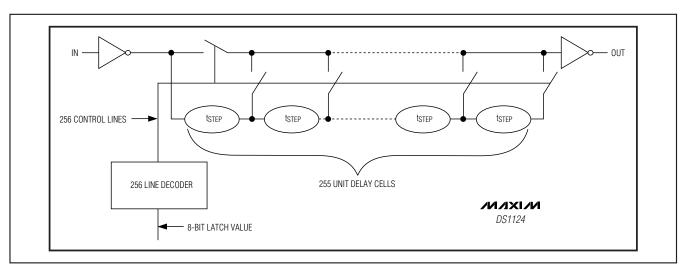

The DS1124 is an 8-bit programmable delay line that can be adjusted between 256 different delay intervals. The DS1124 architecture (see Figure 2) allows some signals to be delayed by more than one period, which lets the phase of the signal to be adjusted up to a full 360°. Programming is performed by a 3-wire serial interface. Using the 3-wire interface, it is possible to cascade multiple devices together for systems requiring multiple programmable delays without using additional I/O resources.

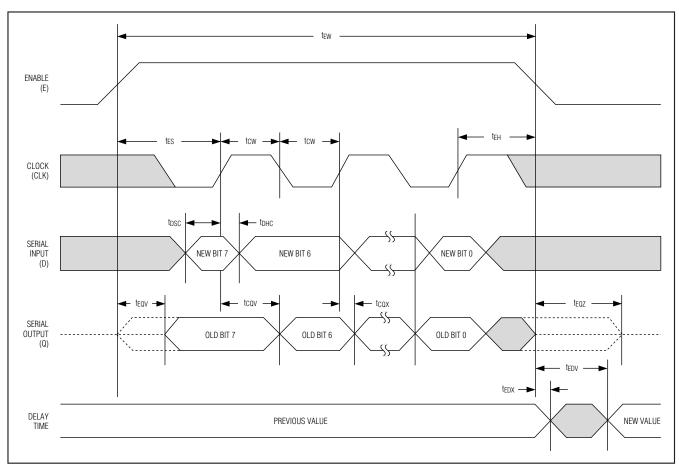

#### **Using the Serial Programming Interface**

Serial mode operates similar to a shift register. When the E pin is set at a high logic level, it enables the shift register and CLK clocks the data, D, into the register one bit at a time starting with the most significant bit. After all 8 bits are shifted into the DS1124, E must be pulled low to end the data transfer and activate the new value. A settling time (ted) is required after E is pulled low before the signal delay will meet its specified accuracy. A timing diagram for the serial interface is shown in Figure 3.

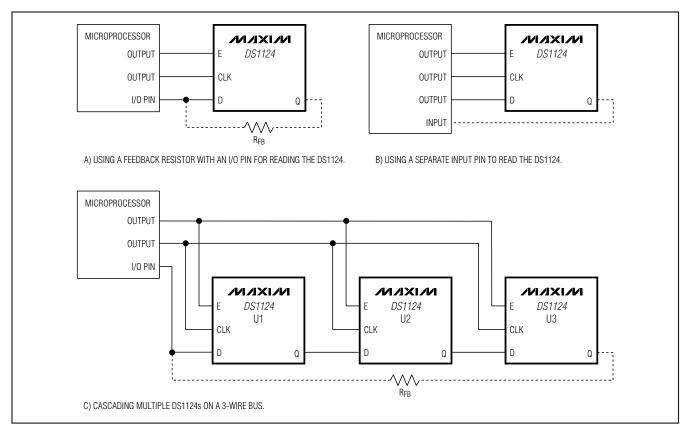

The 3-wire interface also has an output (Q) that can be used to cascade multiple 3-wire devices, and it can be used to read the current value of the devices on the bus. To read the current values stored by the 3-wire device(s), the latch must be enabled and the value of Q must be read and then written back to D before the register is clocked. This causes the current value of the register to be written back into the DS1124 as it is being read. This can be accomplished in a couple of different ways. If the microprocessor has an I/O pin that is high impedance when set as an input, a feedback resistor (R<sub>FB</sub>, generally between  $1k\Omega$  and  $10k\Omega$ ) can be used to write the data on Q back to D as the value is read, see Figure 4A. If the microprocessor has an internal pullup on its I/O pins, or only offers separate input and output pins, the value in the register can still be read. The circuit shown in Figure 4B allows the Q values to read by the microprocessor, which must write the Q value to D before it can clock the bus to read the next bit. If the Q values are read without writing them to D (with the pullup or otherwise), the read will be destructive. A destructive read cycle likely results in an undesirable change in the delay setting.

Figure 2. Conceptual Design

Figure 3. Serial Interface Timing Diagram

Figure 4C shows how to cascade multiple DS1124s onto the same 3-wire bus. One important detail of writing software for cascaded 3-wire devices is that all the devices on the bus must be written to or read from during each read or write cycle. Attempting to write to only the first device (U1) would cause the data stored in U1 to be shifted to U2, U2's data would be shifted to U3, etc. As shown, the microprocessor would have to shift 24 bits during each read or write cycle to avoid inadvertently changing the settings in any of the 3-wire devices. Also note that the feedback resistor or a separate input (not shown) can still be used to read the 3-wire device settings when multiple devices are cascaded.

#### **Integral Nonlinearity**

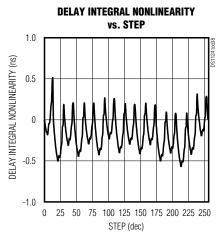

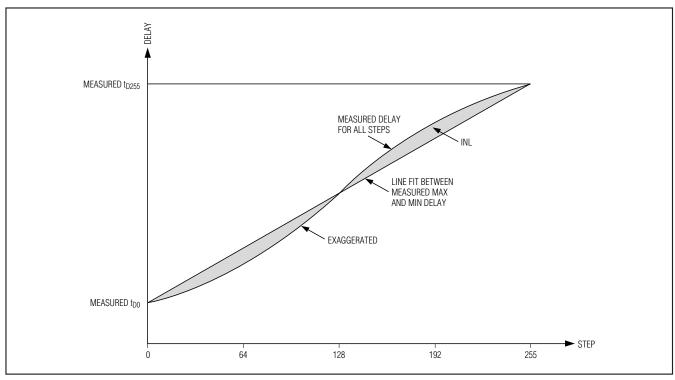

Integral nonlinearity (INL) is defined as the deviation from a straight line response drawn between the measured step zero delay (t<sub>D0</sub>) and the measured step 255 delay (t<sub>D255</sub>) with respect to the step 0 delay. Figure 5 shows INL's effect on delay performance graphically.

## \_Application Information

#### **Power-Supply Decoupling**

To achieve the best results when using the DS1124, decouple the power supply with a  $0.01\mu\text{F}$  and a  $0.1\mu\text{F}$  capacitor. Use high-quality, ceramic, surface mount capacitors, and mount the capacitors as close as possible to the V<sub>CC</sub> and GND pins of the DS1124 to minimize lead inductance. The DS1124 may not perform as specified if good decoupling practices are not followed.

Figure 4. Examples Using the Serial Interface

#### **Test Conditions**

Input:

Ambient Temperature:  $25^{\circ}\text{C} \pm 3^{\circ}\text{C}$ Supply Voltage (V<sub>CC</sub>):  $5.0\text{V} \pm 0.1\text{V}$

Input Pulse: High =  $3.0V \pm 0.1V$

$Low = 0.0V \pm 0.1V$

Source Impedance:  $50\Omega$  max

Rise and Fall Times: 3.0ns max (measured between 0.6V and 2.4V)

Pulse Width: 250ns

Period: 10µs

**Output:** The outputs are loaded with 15pF. Delay is measured between the 1.5V level of the rising or falling edge of the input signal and the corresponding edge of the output signal.

**Note:** Above conditions are for test only and do not restrict the operation of the device under other data sheet conditions.

Figure 5. Integral Nonlinearity

## **Package Information**

For the latest package outline information and land patterns, go to <a href="www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 10 μSOP      |              | <u>21-0061</u> |

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                                    | PAGES<br>CHANGED |

|--------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0                  | 7/07             | Initial release.                                                                                                                                                               | _                |

| 1                  | 4/09             | Added $V_{CC}$ = 5V to the t <sub>ERR</sub> specification in the <i>Electrical Characteristics</i> table, indicating that it is only tested at $T_A$ = 25°C and $V_{CC}$ = 5V. | 3                |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.