# LTC3777

150V V<sub>IN</sub> and V<sub>OUT</sub> Synchronous 4-Switch Buck-Boost Controller + Switching Bias Supply

## FEATURES

- 4-Switch Current Mode Single Inductor Architecture Allows V<sub>IN</sub> Above, Below or Equal to V<sub>OUT</sub>

- Wide V<sub>IN</sub> Range: 4.5V to 150V

- Wide Output Voltage Range:  $1.2V \le V_{OUT} \le 150V$

- Synchronous Rectification: Up to 99% Efficiency

- ±1% 1.2V Voltage Reference

- Input or Output Average Current Limit

- Integrated 12µA IQ, 150V, 85mA, Switching Bias for Optimal Thermal Performance

- Programmable 6V to 10V DRV<sub>CC</sub> Optimizes Efficiency

- No Top FET Refresh Noise in Boost or Buck Mode

- V<sub>OUT</sub> Disconnected from V<sub>IN</sub> During Shutdown

- Phase-Lockable Fixed Frequency (50kHz to 600kHz)

- No Reverse Current During Start-Up

- 150V Rated RUN Pin with Accurate Turn-On Threshold

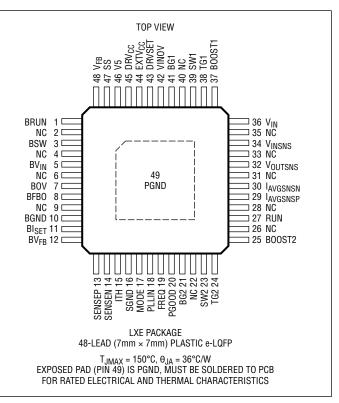

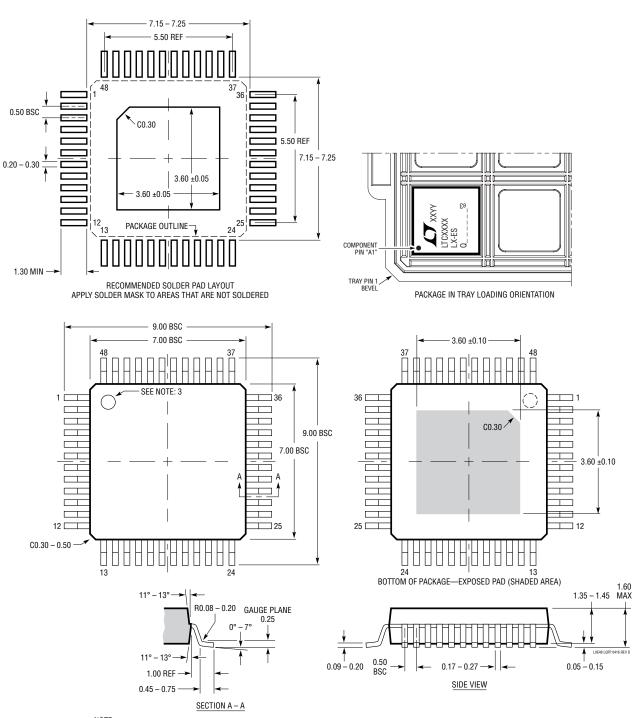

- Thermally Enhanced 48-Lead e-LQFP Package

# **APPLICATIONS**

Industrial, Transportation, Medical, Military, Avionics

All registered trademarks and trademarks are the property of their respective owners.

# DESCRIPTION

The LTC®3777 is a high performance buck-boost switching regulator controller that operates from input voltages above, below or equal to the output voltage. The constant frequency current mode architecture allows a phase-lockable frequency of up to 600kHz, while an input/output constant current loop provides support for battery charging. The 150V integrated switching bias supply is a high efficiency step-down regulator that draws only 12µA typical DC supply current with a regulated output voltage at no load.

With a wide 4.5V to 150V input and output range and seamless transfers between operating regions, the LTC3777 is ideal for industrial, telecom and battery-powered systems.

The LTC3777 features a power good output indicator and a MODE pin to select between pulse-skipping mode or forced continuous mode of operation. The PLLIN pin allows the IC to be synchronized to an external clock. The SS pin ramps the output voltage during start-up. Current foldback limits MOSFET heat dissipation during shortcircuit conditions.

# **ABSOLUTE MAXIMUM RATINGS**

| (Note | 1) |

|-------|----|

|-------|----|

| Input Supply Voltage (V <sub>IN</sub> ), BV <sub>IN</sub><br>Topside Driver Voltage | 150V to -0.3V  |

|-------------------------------------------------------------------------------------|----------------|

| BOOST1, BOOST2                                                                      | 161V to -0.3V  |

| Switch Voltage SW1, SW2                                                             |                |

| RUN, BRUN                                                                           |                |

| IAVGSNSP, IAVGSNSN                                                                  |                |

| VINSNS, VOUTSNS                                                                     |                |

| EXTV <sub>CC</sub> Voltage                                                          | 36V to -0.3V   |

| DRV <sub>CC</sub> Voltage                                                           | 11V to -0.3V   |

| BOOST1-SW1, BOOST2-SW2                                                              | 11V to -0.3V   |

| TG1-SW1, TG2-SW2, BG1, BG2                                                          | (Note 8)       |

| V5, BOV, BFBO, BV <sub>FB</sub> , BI <sub>SET</sub> Voltage                         | 6V to -0.3V    |

| MODE, PLLIN, SS, PGOOD                                                              |                |

| ITH, FREQ, DRVSET                                                                   | V5 to -0.3V    |

| SENSEP, SENSEN, VINOV                                                               | V5 to -0.3V    |

| V <sub>FB</sub> Voltage                                                             | 2.7V to -0.3V  |

| Operating Junction Temperature                                                      |                |

| Range (Notes 2, 3)                                                                  | –40°C to 150°C |

| Storage Temperature Range                                                           | –65°C to 150°C |

| EXTV <sub>CC</sub> /DRV <sub>CC</sub> Peak Current                                  | 100mA          |

# PIN CONFIGURATION

# ORDER INFORMATION

| LEAD FREE FINISH | PART MARKING* | PACKAGE DESCRIPTION                | TEMPERATURE RANGE |

|------------------|---------------|------------------------------------|-------------------|

| LTC3777ELXE#PBF  | LTC3777 LXE   | 48-Lead (7mm × 7mm) Plastic e-LQFP | -40°C to 125°C    |

| LTC3777ILXE#PBF  | LTC3777 LXE   | 48-Lead (7mm × 7mm) Plastic e-LQFP | -40°C to 125°C    |

Contact the factory for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 2),  $V_{IN} = 15V$ ,  $V_{RUN} = 5V$ ,  $V_{EXTVCC} = 0V$ ,  $V_{DRVSET} = 0V$ ,  $V_{VINOV} = 0V$  unless otherwise noted.

| SYMBOL                                       | PARAMETER                                                            | CONDITIONS                                                                |   | MIN   | ТҮР        | MAX   | UNITS |

|----------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------|---|-------|------------|-------|-------|

| V <sub>IN</sub>                              | Input Supply Operating Voltage Range                                 | (Note 4)                                                                  |   | 4.5   |            | 150   | V     |

| V <sub>OUT</sub>                             | Output Supply Operating Voltage Range                                |                                                                           | İ | 1.2   |            | 150   | V     |

|                                              | Regulated Feedback Voltage                                           | (Note 5); ITH Voltage = 1.4V                                              | • | 1.188 | 1.2        | 1.212 | V     |

|                                              | Feedback Current                                                     | (Note 5)                                                                  |   |       | -15        | -50   | nA    |

|                                              | Reference Voltage Line Regulation                                    | (Note 5); V <sub>IN</sub> = 7V to 100V                                    |   |       | 0.02       | 0.2   | %     |

|                                              | Output Voltage Load Regulation                                       | (Note 5); Measured in Servo Loop; ∆ITH<br>Voltage = 1.5V to 2V            | • |       | 0.01       | 0.2   | %     |

|                                              | Transconductance Amplifier gm                                        | (Note 5); ITH = 1.4V; Sink/Source 5µA                                     |   |       | 1.5        |       | mmho  |

| IQ                                           | Input DC Supply Current                                              | (Note 6)                                                                  |   |       | 3.6        | 5.5   | mA    |

|                                              | Shutdown                                                             | RUN = 0V                                                                  |   |       | 40         | 75    | μA    |

|                                              | Undervoltage Lockout                                                 | V5 Ramping Up                                                             |   | 4.1   | 4.35       | 4.6   | V     |

|                                              |                                                                      | V5 Ramping Down                                                           |   | 3.6   | 3.85       | 4.1   | V     |

|                                              | RUN Pin ON Threshold                                                 | V <sub>RUN</sub> Rising                                                   |   | 1.1   | 1.2        | 1.3   | V     |

|                                              | RUN Pin Hysteresis                                                   |                                                                           |   |       | 100        |       | mV    |

|                                              | RUN Pin Source Current                                               | V <sub>RUN</sub> < 1.2V                                                   |   |       | 2.5        |       | μA    |

|                                              | RUN Pin Hysteresis Current                                           | V <sub>RUN</sub> > 1.2V                                                   |   |       | 6.5        |       | μA    |

|                                              | V <sub>IN</sub> Overvoltage Lockout Threshold<br>(Rising)            | V <sub>VINOV</sub> Rising                                                 |   | 1.18  | 1.28       | 1.38  | V     |

|                                              | V <sub>IN</sub> Overvoltage Hysteresis                               |                                                                           |   |       | 50         |       | mV    |

|                                              | SENSE Pins Current                                                   | V <sub>SENSEP</sub> = V <sub>SENSEN</sub> = 0                             |   |       |            | ±2    | μA    |

| I <sub>AVGSNSP</sub><br>I <sub>AVGSNSN</sub> | IAVGSNS Pins Current                                                 | V <sub>IAVGSNSP</sub> = V <sub>IAVGSNSN</sub> = 10V                       |   |       |            | 15    | μA    |

|                                              | Soft-Start Charge Current                                            | $V_{SS} = 0V$                                                             |   | 4     | 5          | 6     | μA    |

| V <sub>SENSE(MAX)</sub>                      | Maximum Current Sense Threshold<br>(Buck Region Valley Current Mode) | V <sub>FB</sub> = 1V                                                      | • | 70    | 90         | 110   | mV    |

|                                              | Maximum Current Sense Threshold<br>(Boost Region Peak Current Mode)  | V <sub>FB</sub> = 1V                                                      | • | 120   | 140        | 160   | mV    |

|                                              | Maximum Input / Output Average<br>Current Sense Threshold            | V <sub>IAVGSNSP</sub> = V <sub>IAVGSNSN</sub> = 10V, V <sub>FB</sub> = 1V |   | 47.5  | 50         | 52.5  | mV    |

| DC(MAX, BOOST)                               | Maximum Duty Factor                                                  | % Switch C On                                                             |   |       | 90         |       | %     |

| DC(MIN, BOOST)                               | Minimum Duty Factor for Main Switch in<br>Boost Operation            | % Switch C On                                                             |   |       | 9          |       | %     |

| DC(MIN, BUCK)                                | Minimum Duty Factor for Main Switch in Buck Operation                | % Switch B On                                                             |   |       | 9          |       | %     |

| Gate Driver                                  |                                                                      |                                                                           |   |       |            |       |       |

|                                              | TG Pull-Up On Resistance<br>TG Pull-Down On Resistance               | V <sub>DRVCC</sub> = 6V                                                   |   |       | 3.1<br>1.5 |       | Ω     |

|                                              | BG Pull-Up On Resistance<br>BG Pull-Down On Resistance               | V <sub>DRVCC</sub> = 6V                                                   |   |       | 5.5<br>3   |       | Ω     |

|                                              | TG Transition Time:<br>Rise Time<br>Fall Time                        | $V_{DRVCC} = 6V$ (Note 7)<br>$C_{LOAD} = 3300 pF$                         |   |       | 60         |       | ns    |

|                                              | BG Transition Time:<br>Rise Time<br>Fall Time                        | V <sub>DRVCC</sub> = 6V (Note 7)<br>C <sub>LOAD</sub> = 3300pF            |   |       | 60         |       | ns    |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 2),  $V_{IN} = 15V$ ,  $V_{RUN} = 5V$ ,  $V_{EXTVCC} = 0V$ ,  $V_{DRVSET} = 0V$ ,  $V_{VINOV} = 0V$  unless otherwise noted.

| SYMBOL                  | PARAMETER                                                                                      | CONDITIONS                                                                                                                                                                                                                                                                       | MIN                               | ТҮР                             | MAX                                | UNITS                 |

|-------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------------|------------------------------------|-----------------------|

|                         | Top Gate Off to Bottom Gate On Delay Synchronous Switch-On Delay Time                          | C <sub>LOAD</sub> = 3300pF Each Driver, V <sub>DRVCC</sub> = 6V                                                                                                                                                                                                                  |                                   | 60                              |                                    | ns                    |

|                         | Bottom Gate Off to Top Gate On Delay<br>Top Switch-On Delay Time                               | $C_{LOAD} = 3300 pF Each Driver, V_{DRVCC} = 6V$                                                                                                                                                                                                                                 |                                   | 60                              |                                    | ns                    |

| DRV <sub>CC</sub> LDO R | egulator                                                                                       |                                                                                                                                                                                                                                                                                  |                                   |                                 |                                    |                       |

| V <sub>DRVCC</sub>      | DRV <sub>CC</sub> Regulation Voltage from Internal V <sub>IN</sub> LDO                         | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                           | 5.5<br>6.5<br>7.5<br>8.45<br>9.15 | 5.8<br>6.8<br>7.8<br>8.8<br>9.5 | 6.1<br>7.1<br>8.1<br>9.15<br>9.85  | V<br>V<br>V<br>V<br>V |

|                         | DRV <sub>CC</sub> Load Regulation from V <sub>IN</sub> LDO                                     | $I_{CC} = 0$ mA to 50mA, $V_{EXTVCC} = 0$ V                                                                                                                                                                                                                                      |                                   | 0.5                             | 2                                  | %                     |

| VEXTVCC                 | DRV <sub>CC</sub> Regulation Voltage from Internal EXTV <sub>CC</sub> LDO                      | $\begin{array}{l} 7V < V_{EXTVCC} < 30V, \ V_{DRVSET} = 0V\\ 8V < V_{EXTVCC} < 30V, \ V_{DRVSET} = 1/4 \ V_{V5}\\ 9V < V_{EXTVCC} < 30V, \ V_{DRVSET} = Float\\ 10V < V_{EXTVCC} < 30V, \ V_{DRVSET} = 3/4 \ V_{V5}\\ 11V < V_{EXTVCC} < 30V, \ V_{DRVSET} = V_{V5} \end{array}$ | 5.8<br>6.8<br>7.8<br>8.75<br>9.65 | 6.1<br>7.1<br>8.1<br>9.1<br>10  | 6.4<br>7.4<br>8.4<br>9.45<br>10.35 | V<br>V<br>V<br>V<br>V |

|                         | $\frac{\text{DRV}_{\text{CC}}}{\text{EXTV}_{\text{CC}}} \text{ Load Regulation from Internal}$ | I <sub>CC</sub> = 0mA to 50mA, V <sub>EXTVCC</sub> = 12V<br>V <sub>DRVSET</sub> = 0V                                                                                                                                                                                             |                                   | 0.5                             | 2                                  | %                     |

|                         | EXTV <sub>CC</sub> LDO Switchover Voltage                                                      | EXTV <sub>CC</sub> Ramping Positive                                                                                                                                                                                                                                              |                                   | DRV <sub>CC</sub> – 0.8         | 5                                  | V                     |

|                         | EXTV <sub>CC</sub> Hysteresis                                                                  | % of DRV <sub>CC</sub> Regulation Voltage                                                                                                                                                                                                                                        |                                   | 10                              |                                    | %                     |

| V5 Linear Reg           | julator                                                                                        |                                                                                                                                                                                                                                                                                  |                                   |                                 |                                    |                       |

|                         | V5 Regulation Voltage                                                                          | 6V < V <sub>DRVCC</sub> < 10V                                                                                                                                                                                                                                                    | 5.3                               | 5.5                             | 5.7                                | V                     |

|                         | V5 Load Regulation                                                                             | $I_{V5}$ = 0mA to 20mA, $V_{DRVCC}$ = 7V                                                                                                                                                                                                                                         |                                   | 0.5                             | 1                                  | %                     |

| Oscillator and          | l Phase-Locked Loop                                                                            |                                                                                                                                                                                                                                                                                  |                                   |                                 |                                    |                       |

|                         | Nominal Frequency                                                                              | $R_{FREQ} = 68.5 k\Omega$                                                                                                                                                                                                                                                        | 225                               | 250                             | 275                                | kHz                   |

|                         | Low Fixed Frequency                                                                            | $R_{FREQ} \le 20 k \Omega$                                                                                                                                                                                                                                                       | 30                                | 40                              | 50                                 | kHz                   |

|                         | High Fixed Frequency                                                                           | R <sub>FREQ</sub> = 135kΩ                                                                                                                                                                                                                                                        | 450                               | 500                             | 550                                | kHz                   |

|                         | PLLIN Input Threshold                                                                          | V <sub>PLLIN</sub> Rising<br>V <sub>PLLIN</sub> Falling                                                                                                                                                                                                                          | 2                                 |                                 | 1.2                                | V<br>V                |

|                         | PLLIN Input Resistance                                                                         |                                                                                                                                                                                                                                                                                  |                                   | 200                             |                                    | kΩ                    |

|                         | Synchronizable Oscillator Frequency                                                            | PLLIN = External Clock                                                                                                                                                                                                                                                           | • 50                              |                                 | 600                                | kHz                   |

| I <sub>FREQ</sub>       | Frequency Setting Current                                                                      |                                                                                                                                                                                                                                                                                  | • 18                              | 20                              | 22                                 | μA                    |

| PGOOD Outpu             | t                                                                                              |                                                                                                                                                                                                                                                                                  |                                   |                                 |                                    |                       |

|                         | PGOOD Voltage Low                                                                              | I <sub>PG00D</sub> = 2mA                                                                                                                                                                                                                                                         |                                   | 0.1                             | 0.3                                | V                     |

|                         | PGOOD Leakage Current                                                                          | $V_{PGOOD} = 5.5V$                                                                                                                                                                                                                                                               |                                   |                                 | ±1                                 | μA                    |

|                         | PGOOD Trip Level                                                                               | V <sub>FB</sub> with Respect to Set Regulated Voltage                                                                                                                                                                                                                            |                                   |                                 |                                    |                       |

|                         |                                                                                                | V <sub>FB</sub> Ramping Negative                                                                                                                                                                                                                                                 |                                   | -10                             |                                    | %                     |

|                         |                                                                                                | V <sub>FB</sub> Ramping Positive                                                                                                                                                                                                                                                 |                                   | 10                              |                                    | %                     |

|                         | PGOOD delay                                                                                    | V <sub>PGOOD</sub> High to Low                                                                                                                                                                                                                                                   |                                   | 125                             |                                    | μs                    |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at T<sub>A</sub> = 25°C (Note 2). BV<sub>IN</sub> = 12V, unless otherwise noted.

| SYMBOL                | PARAMETER                                                                | CONDITIONS                                                        |   | MIN         | ТҮР                | MAX             | UNITS          |

|-----------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------|---|-------------|--------------------|-----------------|----------------|

| Switching B           | ias Supply                                                               | ·                                                                 | • |             |                    |                 |                |

| V <sub>BVIN</sub>     | Input Voltage Operating Range                                            |                                                                   |   | 4           |                    | 150             | V              |

| V <sub>BVOUT</sub>    | Output Voltage Operating Range                                           | (Note 9)                                                          |   | 0.8         |                    | V <sub>IN</sub> | V              |

| BUVLO                 | BV <sub>IN</sub> Undervoltage Lockout                                    | BV <sub>IN</sub> Rising<br>BV <sub>IN</sub> Falling<br>Hysteresis |   | 3.5<br>3.3  | 3.8<br>3.6<br>250  | 4.15<br>3.95    | V<br>V<br>mV   |

| I <sub>QB</sub>       | DC Supply Current (Note 6)<br>Active Mode<br>Sleep Mode<br>Shutdown Mode | No Load<br>BV <sub>RUN</sub> = 0V                                 |   |             | 150<br>12<br>1.4   | 350<br>22<br>6  | μΑ<br>μΑ<br>μΑ |

| V <sub>BRUN</sub>     | BRUN Pin Threshold                                                       | BRUN Rising<br>BRUN Falling<br>Hysteresis                         |   | 1.1<br>0.99 | 1.2<br>1.09<br>110 | 1.3<br>1.19     | V<br>V<br>mV   |

| I <sub>BRUN</sub>     | BRUN Pin Leakage Current                                                 | BRUN = 1.3V (Note 9)                                              |   | -10         | 0                  | 10              | nA             |

| V <sub>BOV</sub>      | BOV Pin Threshold                                                        | BOV Rising<br>BOV Falling<br>Hysteresis                           |   | 1.1<br>0.99 | 1.2<br>1.09<br>110 | 1.3<br>1.19     | V<br>V<br>mV   |

| Output Supp           | ly (BV <sub>FB</sub> )                                                   |                                                                   |   |             |                    |                 |                |

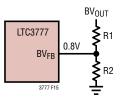

| V <sub>BVFB</sub>     | Feedback Comparator Threshold                                            | BV <sub>FB</sub> Rising                                           |   | 0.786       | 0.800              | 0.814           | V              |

| V <sub>BVFBH</sub>    | Feedback Comparator Hysteresis                                           | BV <sub>FB</sub> Falling (Note 9)                                 |   | 3           | 5                  | 9               | mV             |

| I <sub>BVFB</sub>     | Feedback Pin Current                                                     | BV <sub>FB</sub> = 1V (Note 9)                                    |   | -10         | 0                  | 10              | nA             |

| Operation             | ·                                                                        | ·                                                                 |   |             |                    |                 |                |

| I <sub>PEAKB</sub>    | Peak Current Comparator Threshold                                        | BI <sub>SET</sub> Floating<br>BI <sub>SET</sub> Shorted to GND    |   | 170<br>17   | 240<br>25          | 310<br>33       | mA<br>mA       |

| I <sub>LBSWB</sub>    | Switch Pin Leakage Current                                               | BV <sub>IN</sub> = 150V, BSW = 0V                                 |   |             | 0.1                | 1               | μA             |

| t <sub>INT(SS)B</sub> | Internal Soft-Start Time                                                 | (Note 9)                                                          |   |             | 1                  |                 | ms             |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: The LTC3777 is tested under pulsed load conditions such that T<sub>J</sub>  $\approx T_A$ . The LTC3777E is guaranteed to meet performance specifications from 0°C to 85°C junction temperature. Specifications over the -40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LTC37771 is guaranteed over the full -40°C to 125°C operating junction temperature range. Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance and other environmental factors. The junction temperature T<sub>J</sub> is calculated from the ambient temperature T<sub>A</sub> and power dissipation P<sub>D</sub> according to the formula:

$$\mathsf{T}_\mathsf{J} = \mathsf{T}_\mathsf{A} + (\mathsf{P}_\mathsf{D} \bullet \theta_\mathsf{J}_\mathsf{A}),$$

where  $\theta_{JA} = 36^{\circ}C/W$  for the e-LQFP package.

**Note 3:** This IC includes over temperature protection that is intended to protect the device during momentary overload conditions. The maximum rated junction temperature will be exceeded when this protection is active. Continuous operation above the specified absolute maximum operating junction temperature may impair device reliability or permanently damage the device.

Note 4: When biased from an auxiliary supply through the EXTV<sub>CC</sub> pin, the LTC3777 can operate from a  $V_{IN}$  voltage lower than 4.5V. Otherwise the minimum V<sub>IN</sub> operational voltage is 4.5V after startup.

Note 5: The LTC3777 is tested in a feedback loop that servos  $V_{ITH}$  to a specified voltage and measures the resultant V<sub>FB</sub>.

**Note 6:** Dynamic supply current is higher due to the gate charge being delivered at the switching frequency. See Applications information. Note 7: Rise and fall times are measured using 10% and 90% levels. Delay times are measured using 50% levels.

Note 8: Do not apply a voltage or current source to these pins. They must be connected to capacitive loads only, otherwise permanent damage may occur. These pins are rated for an absolute maximum voltage of -0.3V to 11V.

**Note 9:** Guaranteed by design and wafer level measurements.

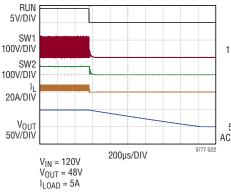

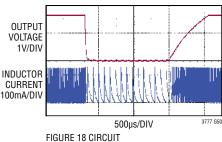

$V_{OUT} = 48V$

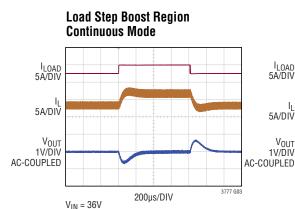

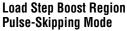

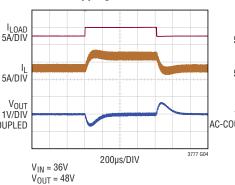

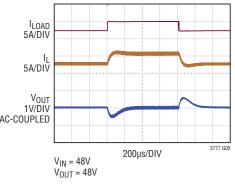

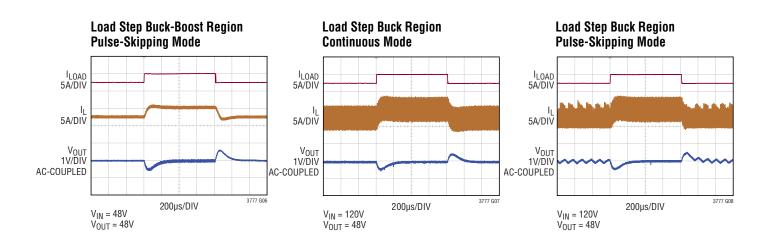

Load Step Buck-Boost Region Continuous Mode

$I_{LOAD} = 0A$

$I_{LOAD} = 0A$

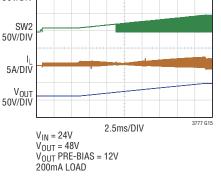

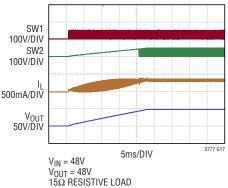

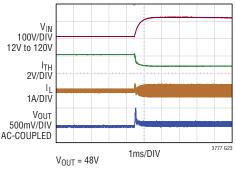

#### Start-Up Forced Continuous Mode Buck-Boost Region

$I_{LOAD} = 0A$

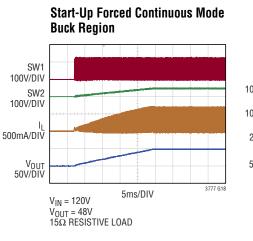

Forced Continuous Mode Boost Region

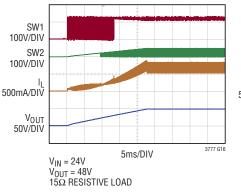

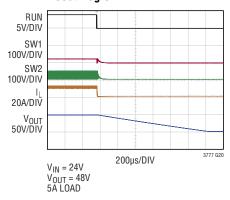

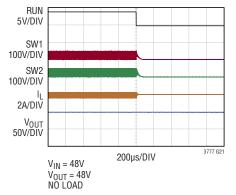

Shutdown from RUN

#### Shutdown from RUN Forced Continuous Mode Buck-Boost Region

#### Shutdown from RUN Forced Continuous Mode Buck Region

Line Transient Rising Edge

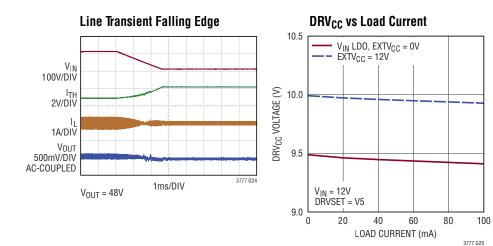

#### DRV<sub>CC</sub> vs Load Current 6.5 $V_{IN}$ LDO, EXTV<sub>CC</sub> = 0V EXTV<sub>CC</sub> = 8.5V DRV<sub>CC</sub> VOLTAGE (V) 6.0 5.5 $V_{IN} = 12V$ DRVSET = 0V 5.0 40 20 60 80 100 0 LOAD CURRENT (mA) 3777 G26

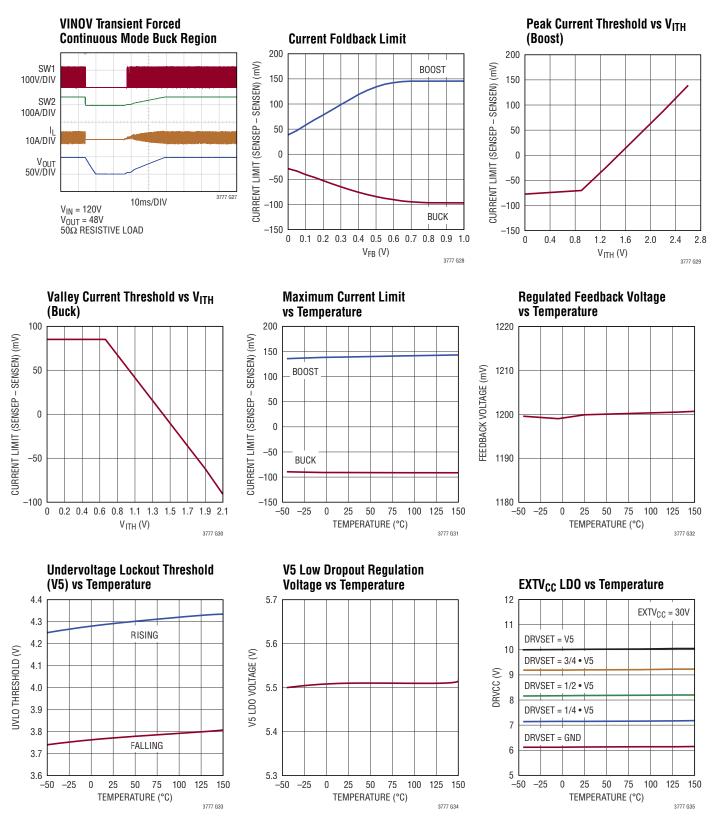

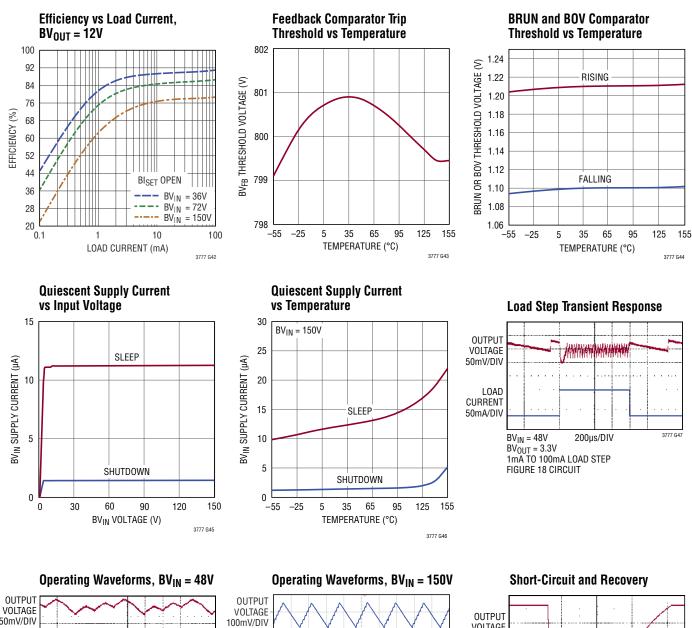

# **TYPICAL PERFORMANCE CHARACTERISTICS – SWITCHING BIAS SUPPLY**

# PIN FUNCTIONS

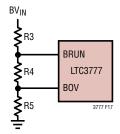

**BRUN (Pin 1):** Bias Supply Run Control Input. A voltage on this pin above 1.21V enables normal operation. Forcing this pin below 0.7V shuts down the switching bias supply, reducing quiescent current to approximately  $1.4\mu$ A. Optionally, connect to the input supply through a resistor divider to set the undervoltage lockout.

**BSW (Pin 3):** Bias Supply Switch Node Connection to Inductor. This pin connects to the drains of the internal power MOSFET switches.

**BV**<sub>IN</sub> (**Pin 5**): Bias Supply Main Supply Pin. A ceramic bypass capacitor should be tied between this pin and GND.

**BOV (Pin 7):** Bias Supply Overvoltage Lockout Input. Connect to the input supply through a resistor divider to set the overvoltage lockout level. A voltage on this pin above 1.21V disables the internal MOSFET switches. Normal operation resumes when the voltage on this pin decreases below 1.10V. Exceeding the OVLO lockout threshold triggers a soft-start reset, resulting in a graceful recovery from an input supply transient. Tie this pin to ground if the overvoltage is not used.

**BFBO (Pin 8):** Bias Supply Feedback Comparator Output. The typical pull-up current is  $20\mu$ A. The typical pull-down impedance is  $70\Omega$ . This output signal can be used to synchronize other ICs.

#### BGND (Pin 10): Ground.

**BI<sub>SET</sub> (Pin 11):** Bias Supply Peak Current Set Input. Leave floating for the maximum peak current (230mA typical) or short to ground for minimum peak current (25mA typical). The maximum output current is one-half the peak current.

**BV<sub>FB</sub> (Pin 12):** Bias Supply Output Voltage Feedback. Connect to an external resistive divider to divide the output voltage down for comparison to the 0.8V reference.

**SENSEP (Pin 13):** The positive input to the differential current comparator. This pin is normally connected to a sense resistor at the source of the power MOSFET. The ITH pin voltage and controlled offsets between the SENSEP and SENSEN pins, in conjunction with R<sub>SENSE</sub>, set the current trip threshold.

**SENSEN (Pin 14):** The negative input to the differential current sense comparator. This pin is normally connected to the ground side of the sense resistor.

**ITH (Pin 15):** Error Amplifier Output. The current comparator trip threshold increases with the ITH control voltage. The ITH pin is also used for compensating the control loop of the converter.

**SGND (Pin 16):** Signal ground. All feedback and soft-start connections should return to SGND. For optimum load regulation, the SGND pin should be Kelvin connected to the PCB location between the negative terminals of the output capacitors.

**MODE (Pin 17):** Mode Selection pin. Tying this pin to SGND or below 0.8V enables forced continuous mode. Tying it to V5 enables pulse-skipping mode.

**PLLIN (Pin 18):** External Synchronization Input to Phase Detector. For external sync, apply a clock signal to this pin and the internal PLL will synchronize the internal oscillator to the clock. The PLL compensation network is integrated into the IC. When synchronized to an external clock, the regulator can operate either in forced continuous or pulseskipping mode. The mode of operation is controlled by the setting on the MODE pin.

**FREQ (Pin 19):** The frequency control pin for the internal VCO. Frequencies between 40kHz and 500kHz can be programmed by using a resistor between FREQ and SGND. The resistor and an internal 20µA source current create a voltage used by the internal oscillator to set the frequency.

**PGOOD (Pin 20):** Fault indicator Output. Open-drain output that pulls to ground when the voltage on the  $V_{FB}$  pin is not within ±10% of its set point.

**BG1/BG2 (Pins 41 and 21):** Bottom Gate Driver Outputs. This pin drives the gate(s) of the bottom N-Channel MOSFET between PGND to DRV<sub>CC</sub>.

SW1, SW2 (Pins 39 and 23): Switch Node Connections to the Inductors.

## PIN FUNCTIONS

**TG1, TG2 (Pin 38 and 24):** High Current Gate Drives for Top N-Channel MOSFETs. These are the outputs of floating high side drivers with a voltage swing equal to DRV<sub>CC</sub> superimposed on the switch node voltage SW.

**BOOST1. BOOST2 (Pin 37 and 25):** Boosted Floating Driver Supplies. The (+) terminal of the bootstrap capacitor connects to this pin. This pin swings from a diode drop below  $DRV_{CC}$  up to  $V_{IN} + DRV_{CC}$ .

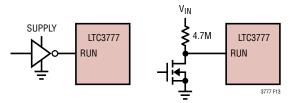

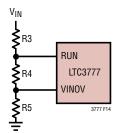

**RUN (Pin 27):** Enable Control Input. A voltage above 1.2V turns on the IC. There is a  $2.5\mu$ A pull-up current on this pin. Once the RUN pin rises above the 1.2V threshold the pull-up current increases to  $6.5\mu$ A. Forcing this pin below 1.1V shuts down the controller. This pin can be tied to V<sub>IN</sub> for always-on operation. Do not float this pin.

**I<sub>AVGSNSP</sub> (Pin 29):** The positive input to the Input / Output Average Current Sense Amplifier.

**I**<sub>AVGSNSN</sub> (**Pin 30**): The negative input to the Input / Output Average Current Sense Amplifier. Short  $I_{AVGSNSP}$  and  $I_{AVGSNSN}$  pins together, and tie them to V5, if this average current loop function is not used.

$V_{OUTSNS}$  (Pin 32):  $V_{OUT}$  Sense Input to the Buck-Boost Transition comparator. Connect this pin to the drain of the top N-channel MOSFET on the output side through a 1k $\Omega$  resistor.

**V**<sub>INSNS</sub> (**Pin 34**): V<sub>IN</sub> Sense Input to the Buck-Boost Transition comparator. Connect this pin to the drain of the top N-channel MOSFET on the input side.

**V**<sub>IN</sub> (**Pin 36**): Main Supply Pin. A bypass capacitor should be tied between this pin and the PGND pin.

**VINOV (Pin 42):** Connect to the input supply through a resistor divider to set the over-voltage lockout level. A voltage on this pin above 1.28V disables all switching, and the top GATE pins are held low, the bottom GATE pins are held high, and  $V_{OUT}$  is disconnected from  $V_{IN}$ . DRV<sub>CC</sub> and V5 regulation is maintained during an over-voltage event. Normal operation resumes when the voltage on this pin decreases below 1.23V. Exceeding the VINOV lockout

threshold triggers a soft-start reset, resulting in a graceful recovery from an input supply transient. Tie this pin to ground if the overvoltage function is not used.

**DRVSET (Pin 43):** Sets the regulated output voltage of the DRV<sub>CC</sub> linear regulator from 6V to 10V in 1V increments. Tying this pin to SGND sets DRV<sub>CC</sub> to 6V, tying it to  $1/4 \cdot V5$  sets DRV<sub>CC</sub> to 7V, while floating this pin sets DRV<sub>CC</sub> to 8V, tying it to  $3/4 \cdot V5$  sets DRV<sub>CC</sub> to 9V, and tying it to V5 sets DRV<sub>CC</sub> to 10V.

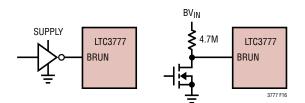

**EXTV<sub>CC</sub> (Pin 44):** External Power Input to an Internal LDO Connected to  $DRV_{CC}$ . When the voltage on this pin is greater than the  $DRV_{CC}$  LDO setting minus 500mV, this LDO bypasses the internal LDO powered from  $V_{IN}$ . Tie this pin to ground if the EXTV<sub>CC</sub> is not used.

**DRV<sub>CC</sub> (Pin 45):** Output of the Internal or External Low Dropout Regulator. The gate drivers are powered from this voltage source. The DRV<sub>CC</sub> voltage is set by the DRVSET pin. A low ESR  $4.7\mu$ F (X5R or better) ceramic bypass capacitor should be connected between DRV<sub>CC</sub> and PGND, as close as possible to the IC. Do not use the DRV<sub>CC</sub> pin for any other purpose.

**V5 (Pin 46):** Output of the Internal 5.5V Low Dropout Regulator. The control circuits are powered from this voltage. Bypass this pin to SGND with a minimum of  $2.2\mu$ F low ESR tantalum or ceramic capacitor, as close as possible to the IC.

**SS (Pin 47):** Soft-Start Input. The voltage ramp rate at this pin sets the voltage ramp rate of the regulated voltage. This pin has a  $5\mu$ A pull-up current. A capacitor to ground at this pin sets the ramp time to final regulated output voltage.

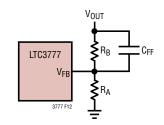

$V_{FB}$  (Pin 48): Error Amplifier Input. The FB pin should be connected through a resistive divider network to  $V_{OUT}$  to set the output voltage.

**PGND (Exposed Pad Pin 49):** Driver Power Ground. Connects to the (–) terminal of  $C_{IN}$ ,  $C_{OUT}$  and  $R_{SENSE}$ . The exposed pad must be soldered to PCB ground for electrical contact and rated thermal performance.

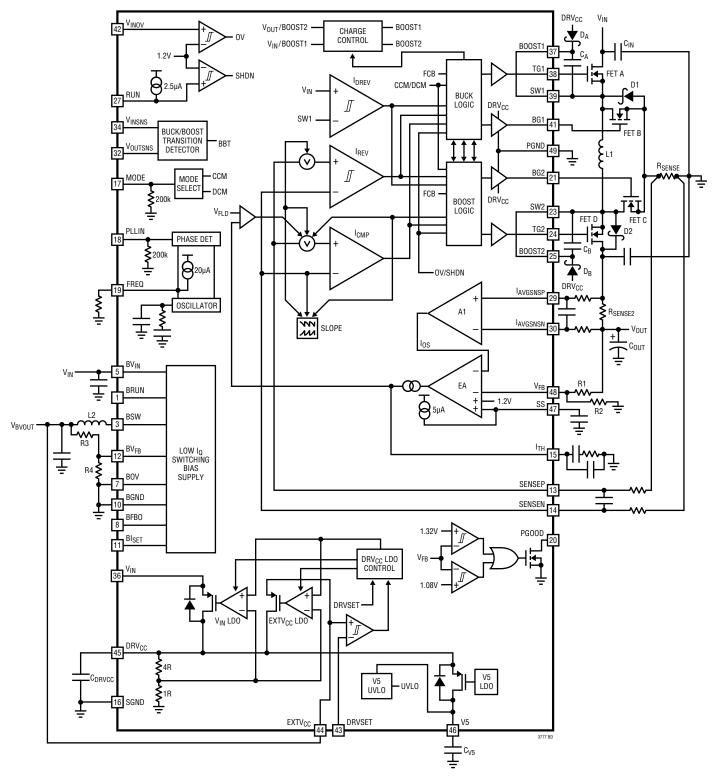

# **BLOCK DIAGRAM**

#### MAIN CONTROL LOOP

The LTC3777 is a 150V synchronous buck-boost controller with an integrated 150V, 85mA, high efficiency synchronous switching bias supply. The 150V switching bias supply draws only 12 $\mu$ A typical DC supply current while maintaining a regulated output voltage at no load.

The 150V synchronous buck-boost is a current mode controller that provides an output voltage above, equal to or below the input volt- age. The ADI proprietary topology and control architecture employs a current-sensing resistor. The inductor current is controlled by the voltage on the  $I_{TH}$  pin, which is the output of the error amplifier EA. The V<sub>FB</sub> pin receives the voltage feedback signal, which is compared to the internal reference voltage by the EA. If the input/output current regulation loop is implemented, the sensed inductor current is controlled by either the sensed feedback voltage or the input/output current.

#### DRV<sub>CC</sub>/EXTV<sub>CC</sub>/V5 Power

Power for the top and bottom MOSFET drivers is derived from the DRV<sub>CC</sub> pin. The DRV<sub>CC</sub> supply voltage can be programmed from 6V to 10V in 1V steps using the DRVSET pin. The internal V<sub>IN</sub> LDO (low dropout linear regulator) can provide power from V<sub>IN</sub> to DRV<sub>CC</sub>. The internal V<sub>IN</sub> LDO uses an internal P-channel pass device between the V<sub>IN</sub> and DRV<sub>CC</sub> pins. To prevent high on-chip power dissipation in high input voltage applications, the LTC3777 also includes an integrated 150V, low I<sub>Q</sub> 85mA synchronous step-down regulator to bias the buck-boost controller. See Integrated Switching Bias Supply in the Operation section for more information.

When the EXTV<sub>CC</sub> pin is tied to a voltage below its switchover voltage (DRV<sub>CC</sub>-500mV), the V<sub>IN</sub> LDO is enabled and supplies power from V<sub>IN</sub> to DRV<sub>CC</sub>. If EXTV<sub>CC</sub> is taken above its switchover voltage, the V<sub>IN</sub> LDO is turned off and an EXTV<sub>CC</sub> LDO is turned on. Once enabled, the EXTV<sub>CC</sub> LDO supplies power from EXTV<sub>CC</sub> to DRV<sub>CC</sub>. Using the EXTV<sub>CC</sub> pin allows the DRV<sub>CC</sub> power to be derived from a high efficiency supply such as the low I<sub>Q</sub> integrated step-down regulator bias supply or the LTC3777 switching regulator output if the output voltage is less than 36V.

Most of the internal circuitry is powered from the V5 rail that is generated by an internal linear regulator from DRV<sub>CC</sub>. The V5 pin needs to be bypassed with a 1µF to 10µF external capacitor between V5 and SGND. This pin provides a 5.5V output that can supply up to 20mA of current. See the Applications Information section for more details.

#### Top MOSFET DRIVER and Internal Charge Path

Each of the two top MOSFET drivers is biased from its floating bootstrap capacitor, which is normally recharged by DRV<sub>CC</sub> through an external diode when the top MOSFET is turned off and when SW goes low. When the LTC3777 operates exclusively in the buck or boost regions, one of the top MOSFETs is constantly on. An internal charge path, from  $V_{OUT}$  and BOOST2 to BOOST1 or from  $V_{IN}$  and B00ST1 to B00ST2, charges the bootstrap capacitor so that the top MOSFET can be kept on. However, if a high leakage external diode is used such that the internal charge path cannot provide sufficient charge to the external bootstrap capacitor, an internal UVLO comparator, which constantly monitors the drop across the capacitor, will sense the (BOOST – SW) voltage when it is below the boost capacitor refresh threshold. This will turn off its top MOSFET for about one-twelfth of the clock period every four cycles to allow the bootstrap capacitor to recharge. The boost capacitor refresh threshold varies with the DRVSET pin setting.

#### Shutdown and Start-Up

The LTC3777 can be shut down by pulling the RUN pin low. Pulling RUN below 1.1V shuts down the main control loop for the controller and most internal circuits, including the DRV<sub>CC</sub> and V5 regulators. Releasing RUN allows an internal 2.5 $\mu$ A current to pull-up the pin and enable the controller. When RUN is above the accurate threshold of 1.2V, the internal LDO will power up DRV<sub>CC</sub>. At the same time, a 6.5 $\mu$ A pull-up current will kick in to provide more RUN pin hysteresis. The RUN pin may be externally pulled up or driven directly by logic. The RUN pin can tolerate up to 150V (absolute maximum), so it can be conveniently tied to V<sub>IN</sub> in always-on applications where the controller is enabled continuously and never shut down. The RUN

pin will have no internal pull-up current when externally driven to a voltage above 4V.

#### Soft-Start

The start-up of the controller's output voltage  $V_{OUT}$  is controlled by the voltage on the SS pin. When the voltage on the SS pin is less than the 1.2V internal reference, the LTC3777 regulates the V<sub>FB</sub> voltage to the SS voltage instead of the 1.2V reference. This allows the SS pin to be used to program soft-start by connecting an external capacitor from the SS pin to SGND. An internal 5µA pull-up current charges this capacitor, creating a voltage ramp on the SS pin. As the SS voltage rises linearly from OV to 1.2V (and beyond), the output voltage V<sub>OUT</sub> rises smoothly from zero to its final value. When RUN is pulled low to disable the controller, or during an overvoltage event on the V<sub>IN</sub> input supply or during an overtemperature shutdown event, or when V5 drops below its undervoltage lockout threshold of 3.85V, the SS pin is pulled low by an internal MOSFET. When in undervoltage lockout, the controller is disabled and the external MOSFETs are held off.

Certain applications can require the start-up of the converter into a non-zero load voltage, where residual charge is stored on the  $V_{OUT}$  capacitor at the onset of converter switching. In order to prevent the  $V_{OUT}$  from discharging under these conditions, the part will be forced into discontinuous mode of operation until the SS voltage crosses  $V_{FB}$  or 1.32V, whichever is lower.

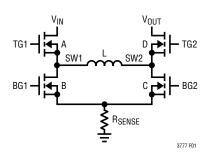

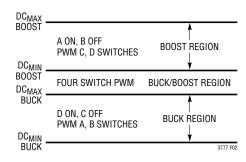

#### **Power Switch Control**

Figure 1 shows a simplified diagram of how the four power switches are connected to the inductor,  $V_{IN}$ ,  $V_{OUT}$  and GND. Figure 2 shows the regions of operation for the LTC3777 as a function of  $V_{OUT} - V_{IN}$  or switch duty cycle, DC. The power switches are properly controlled so the transfer between regions is continuous. Hysteresis is added to prevent chattering when transitioning between regions.

Figure 1. Simplified Diagram of the Output Switches

Figure 2. Operating Region vs Duty Cycle

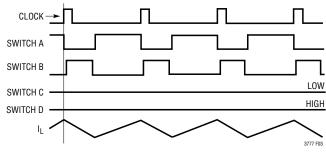

### Buck Region ( $V_{IN} >> V_{OUT}$ )

When  $V_{IN}$  is significantly higher than  $V_{OUT}$ , the part will run in the buck region. In this region switch C is always off. At the start of every cycle, synchronous switch B is turned on first. Inductor current is sensed when synchronous switch B is turned on. After the sensed inductor valley current falls below a reference voltage, which is proportional to  $V_{ITH}$ , synchronous switch B is turned off and switch A is turned on for the remainder of the cycle. Switches A and B will alternate, behaving like a typical synchronous buck regulator. The duty cycle of Switch A increases until the maximum duty cycle of the converter reaches  $DC_{(MAX_BUCK)}$ , given by:

$$DC_{(MAX,BUCK)} = \left(1 - \frac{1}{12}\right) \bullet 100\% = 91.67\%$$

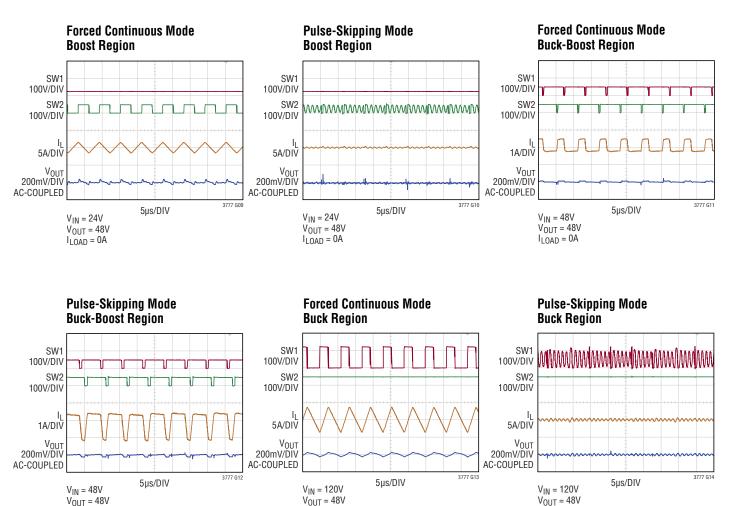

Figure 3 shows the typical buck region waveforms. If  $V_{\text{IN}}$  approaches  $V_{\text{OUT}},$  the buck-boost region is reached.

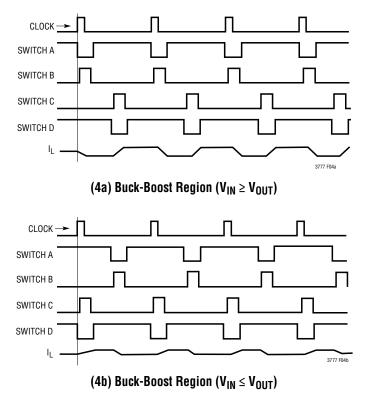

#### Buck-Boost Region (V<sub>IN</sub> $\approx$ V<sub>OUT</sub>)

When  $V_{IN}$  is close to  $V_{OUT}$ , the controller enters the buckboost region. Figure 4 shows the typical waveforms in this region. At the beginning of a clock cycle, if the controller starts with B and D on, the controller first operates as if in the buck region. When  $I_{CMP}$  trips, switch B is turned off, and switch A is turned on. At 120° clock phase, switch C is turned on. The LTC3777 starts to operate as a boost until  $I_{CMP}$  trips. Then, switch D is turned on for the remainder of the clock period. If the controller starts with switches

Figure 4. Buck-Boost Region

A and C on, the controller first operates as a boost, until  $I_{CMP}$  trips and switch D is turned on. At 120°, switch B is turned on, making it operate as a buck. Then,  $I_{CMP}$  trips, turning switch B off and switch A on for the remainder of the clock period.

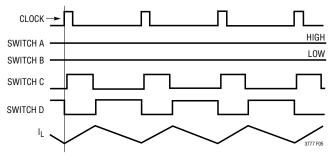

#### Boost Region (V<sub>IN</sub> << V<sub>OUT</sub>)

Switch A is always on and synchronous switch B is always off in the boost region. In every cycle, switch C is turned on first. Inductor current is sensed when synchronous switch C is turned on. After the sensed inductor peak current exceeds what the reference voltage demands, which is proportional to  $V_{\rm ITH}$ , switch C is turned off and synchronous switch D is turned on for the remainder of the cycle. Switches C and D will alternate, behaving like a typical synchronous boost regulator.

The duty cycle of switch C decreases until the minimum duty cycle of the converter reaches  $\text{DC}_{(\text{MIN},\text{BOOST})}$ , given by:

$$DC_{(MIN,BOOST)} = \left(\frac{1}{12}\right) \cdot 100\% = 8.33\%$$

Figure 5 shows typical boost region waveforms. If  $V_{\text{IN}}$  approaches  $V_{\text{OUT}},$  the buck-boost region is reached.

Figure 5. Boost Region ( $V_{IN} \ll V_{OUT}$ )

### Light Load Current Operation (MODE Pin)

The LTC3777 can be enabled to enter pulse-skipping mode or forced continuous conduction mode. To select forced continuous operation, tie the MODE pin to a DC voltage below 0.8V (e.g., SGND). To select pulse-skipping mode of operation, tie the MODE pin to V5.

**Pulse-Skipping Mode:** When the LTC3777 enters pulseskipping or discontinuous mode, in the boost region, synchronous switch D is held off whenever reverse current through switch A is detected. At very light loads, the current comparator, I<sub>CMP</sub>, may remain tripped for several cycles and force switch C to stay off for the same number of cycles (i.e., skipping pulses). In the buck region, the inductor current is not allowed to reverse. Synchronous switch B is held off whenever reverse current on the inductor is detected. At very light loads, the current comparator, I<sub>CMP</sub>, may remain untripped for several cycles, holding switch A off for the same number of cycles. Synchronous switch B also remains off for the skipped cycles. In the buck-boost region, the controller operates alternatively in boost and buck regions in one clock cycle, as in continuous operation. A small amount of reverse current is allowed, to minimize ripple. For the same reason, a narrow band of continuous buck and boost operation is allowed on the high and low line ends of the buck-boost region.

**Forced Continuous Mode:** The forced continuous mode allows the inductor current to reverse directions without any switches being forced "off" to prevent this from happening. At very light load currents the inductor current will swing positive and negative as the appropriate average current is delivered to the output. During softstart, if the SS pin is lower than  $V_{FB}$ , the part will be forced into discontinuous mode to prevent pulling current from the output to the input. After SS voltage crosses  $V_{FB}$  or 1.32V, whichever is lower, forced continuous mode will be enabled.

#### Output Overvoltage

If the output voltage is higher than the value commanded by the V<sub>FB</sub> resistor divider, the LTC3777 will respond according to the mode and region of operation. In continuous conduction mode, the LTC3777 will sink current into the input. If the input supply is capable of sinking current, the LTC3777 will allow up to about 80mV/  $R_{SENSE}$  to be sunk into the input. In pulse-skipping mode and in the buck or boost regions, switching will stop and the output will be allowed to remain high. In pulseskipping mode, and in the buck-boost region as well as the narrow band of continuous boost operation that adjoins it, current sunk into the input through switch A is limited to approximately 40mV/  $R_{DS(0N)}$  of switch A. If this level is reached, switching will stop and the output will rise. In pulse-skipping mode, and in the narrow continuous buck region that adjoins the buck/ boost region, current sunk into the input through  $R_{SENSE}$  is limited to approximately 40mV/ $R_{SENSE}$ .

#### Voltage Regulation Loop

The LTC3777 provides a constant-voltage regulation loop, for regulating the output voltage. A resistor divider between V<sub>OUT</sub>, V<sub>FB</sub> and GND senses the output voltage. As with traditional voltage regulators, when V<sub>FB</sub> rises near or above the reference voltage of EA (1.2V typical, see Block Diagram), the ITH voltage is reduced to command the amount of current that keeps V<sub>OUT</sub> regulated to the desired voltage.

# Constant-Current Regulation ( $I_{AVGSNSP}$ and $I_{AVGSNSN}$ Pins)

The LTC3777 provides a constant-current regulation loop for either input or output current. A sensing resistor close to the input or output capacitor will sense the input or output current. When the current exceeds the programmed current limit, the voltage on the ITH pin will be pulled down to maintain the desired maximum input or output current. The input current limit function prevents overloading the DC input source, while the output current limit provides a building block for battery charger or LED driver applications. It can also serve as an extra current limit protection for a constant-voltage regulation application. The input or output current limit function bas an operating voltage range of GND to the absolute maximum  $V_{IN}$  or  $V_{OUT}$ , respectively.

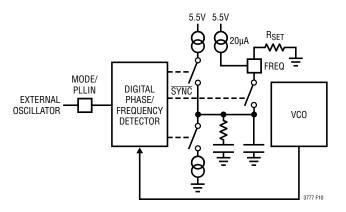

# Frequency Selection and Phase-Locked Loop (FREQ and PLLIN Pins)

The selection of switching frequency is a trade-off between efficiency and component size. Low frequency operation increases efficiency by reducing MOSFET switching losses, but requires larger inductance and/or capacitance to maintain low output ripple voltage. The switching frequency of the LTC3777's controllers can be selected using the FREQ pin. If the SYNC pin is not being Rev A

driven by an external clock source, the FREQ pin can be used to program the controller's operating frequency from 50kHz to 600kHz.

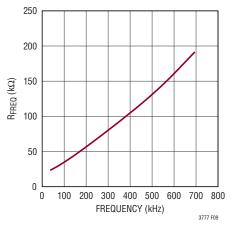

Switching frequency is determined by the voltage on the FREQ pin. Since there is a precision 20µA current flowing out of the FREQ pin, the user can program the controller's switching frequency with a single resistor to SGND. Figure 9 in the Applications Information section shows the relationship between the FREQ pin resistor value and the switching frequency.

A phase-locked loop (PLL) is integrated on the LTC3777 to synchronize the internal oscillator to an external clock source driving the PLLIN pin. While LTC3777 is being synchronized to an external clock source, depending on the voltage of the MODE pin, it can be enabled to enter pulse-skipping mode or forced continuous conduction mode. The PLL filter network is integrated inside the LTC3777.

The PLL is capable of locking to any frequency within the range of 50kHz to 600kHz. The frequency setting resistor should always be present to set the controller's initial switching frequency before locking to the external clock.

#### Power Good (PGOOD) Pins

The PGOOD pin is connected to the open drain of an internal N-channel MOSFET. When  $V_{FB}$  is not within ±10% of the 1.2V reference voltage, the PGOOD pin is pulled low. The PGOOD pin is also pulled low when RUN is below 1.1V or when the LTC3777 is in the soft-start phase. There is an internal 125µs power good or bad mask when  $V_{FB}$  goes in or out of the ±10% window. The PGOOD pin is allowed to be pulled up by an external resistor to V5 or an external source of up to 6V.

# Short-Circuit Protection, Current Limit and Current Limit Foldback

The maximum current threshold of the controller is limited by a voltage clamp on the ITH pin. In every boost cycle, the sensed maximum peak voltage is limited to 140mV. In every buck cycle, the sensed maximum valley voltage is limited to 90mV. In the buck-boost region, only peak sensed voltage is limited by the same threshold as in the boost region. The LTC3777 includes current foldback to help limit load current when the output is shorted to ground. If the output falls below 50% of its nominal output level, then the maximum sense voltage is progressively lowered from its maximum value to one-third of the maximum value. Foldback current limiting is disabled during the soft-start. Under short-circuit conditions, the LTC3777 will limit the current by operating as a buck with very low duty cycles, and by skipping cycles. In this situation, synchronous switch B will dissipate most of the power (but less than in normal operation).

#### **Thermal Shutdown**

The LTC3777 has a temperature sensor integrated on the IC, to sense the die temperature near the gate driver circuits. When the die temperature exceeds 175°C, all switching actions stop, the top GATE pins are held low, and the bottom GATE pins are held high, and  $V_{OUT}$  is disconnected from  $V_{IN}$ . At the same time, the SS pin is pulled low by an internal MOSFET. When the temperature drops 10°C below the trip threshold, the part goes through a SS reset cycle and normal operation resumes.

#### Input Undervoltage and Overvoltage Lockout

The LTC3777 implements a protection feature that inhibits switching when the input voltage rises above a programmable operating range. By using a resistor divider from the input supply to ground, the RUN and VINOV pins serve as a precise input supply voltage monitor. Switching is disabled when either the RUN pin falls below 1.1V or the VINOV pin rises above 1.28V, which can be configured to limit switching to a specific range of input supply voltage.

When switching is disabled, the LTC3777 can safely sustain input voltages on the RUN pin up to the absolute maximum rating of 150V. Input supply undervoltage or overvoltage events trigger a soft-start reset, which results in a graceful recovery from an input supply transient.

#### Integrated Switching Bias Supply

The switching bias supply is a synchronous step-down DC/DC regulator with internal power switches that uses Burst Mode<sup>®</sup> control, combining low quiescent current with high switching frequency, which results in high

efficiency across a wide range of load currents. Burst Mode operation functions by using short "burst" cycles to switch the inductor current through the internal power MOSFETs, followed by a sleep cycle where the power switches are off and the load current is supplied by the output capacitor. During the sleep cycle, it draws only  $12\mu$ A of supply current. At light loads, the burst cycles are a small percentage of the total cycle time which minimizes the average supply current, greatly improving efficiency.

If the voltage on the BRUN pin is less than 0.7V, the switching bias supply enters a shutdown mode in which all internal circuitry is disabled, reducing the DC supply current to 1.4 $\mu$ A. When the voltage on the BRUN pin exceeds 1.21V, normal operation of the main control loop is enabled. The BRUN pin comparator has 110mV of internal hysteresis, and therefore must fall below 1.1V to disable the main control loop.

An internal 1ms soft-start function limits the ramp rate of the output voltage on start-up to prevent excessive input supply droop. The internal soft-start function is reset on start-up and after an undervoltage or overvoltage event on the input supply. The peak current comparator has a maximum current limit of at least 170mA, which guarantees a maximum average current of 85mA. Shorting the BI<sub>SET</sub> pin to ground programs the current limit to 25mA, and leaving it floating sets the current limit to the maximum value of 240mA.

Input undervoltage and overvoltage lockout protection features will inhibit switching when the input voltage is not within a programmable operating range. By use of a resistive divider from the input supply to ground, the BRUN and BOV pins serve as a precise input supply voltage monitor. Switching is disabled when either the BRUN pin falls below 1.1V or the BOV pin rises above 1.21V, which can be configured to limit switching to a specific range of input supply voltage. Furthermore, if the input voltage falls below 3.5V typical (3.8V maximum), an internal undervoltage detector disables switching.

Input supply undervoltage or overvoltage events trigger a soft-start reset, which results in a graceful recovery from an input supply transient.

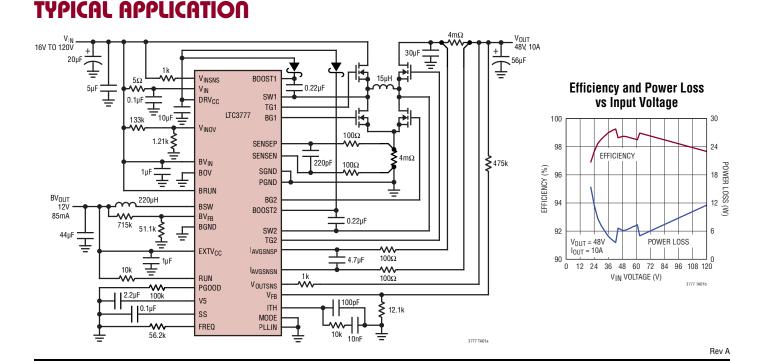

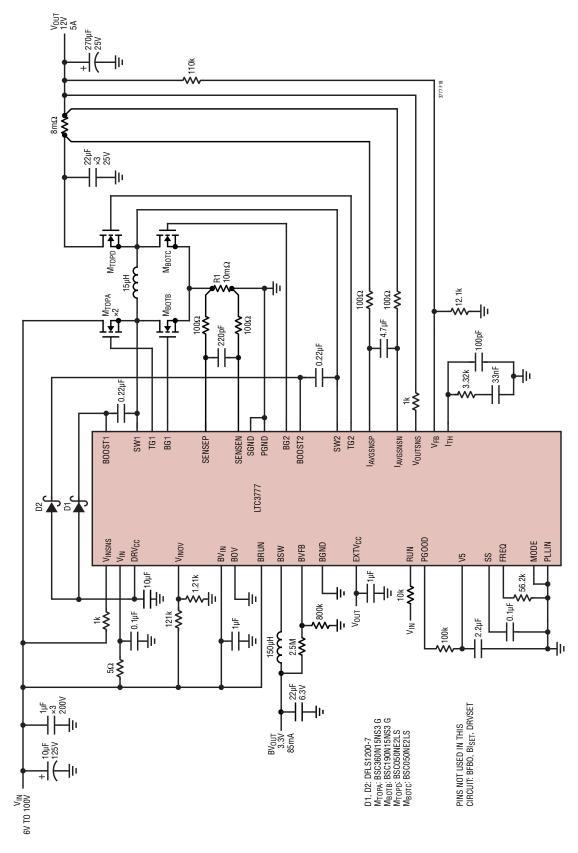

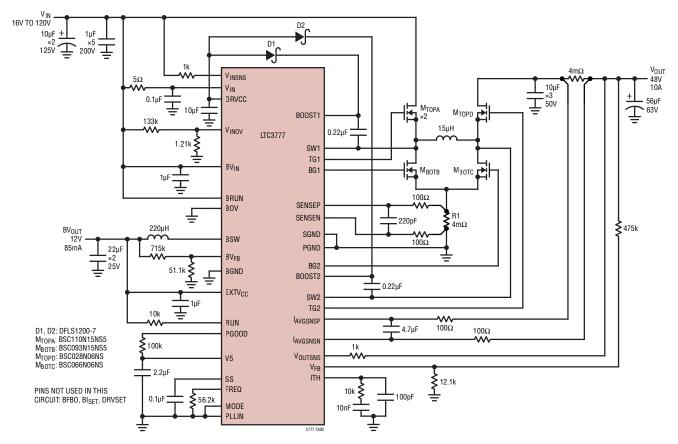

The Typical Application on the first page is a basic LTC3777 application circuit. External component selection is driven by the load requirement, and begins with the selection of  $R_{SENSE}$  and the inductor value. Next, the power MOSFETs are selected. Finally,  $C_{IN}$  and  $C_{OUT}$  are selected. This circuit can be configured for operation up to an input voltage of 150V.

#### **Inductor Current Sensing and Slope Compensation**

The LTC3777 operates using inductor current mode control. The LTC3777 measures the peak of the inductor current waveform in the boost region and the valley of the inductor current waveform in the buck region. The inductor current is sensed across the  $R_{SENSE}$  resistor with pins SENSEP and SENSEN. During any given cycle, the peak (boost region) or valley (buck region) of the inductor current is controlled by the ITH pin voltage.

Slope compensation provides stability in constant frequency architectures by preventing subharmonic oscillations at high duty cycles in boost operation and at low duty cycles in buck operation. This is accomplished internally by adding a compensating ramp to the inductor current signal at duty cycles in excess of 40% in the boost region, or subtracting a ramp from the inductor current signal at lower than 40% duty cycles in the buck region. Normally, this results in a reduction of maximum inductor peak current for duty cycles >40% in the boost region, or an increase of maximum inductor current for duty cycles <40% in the buck region. However, the LTC3777 uses a scheme that counteracts this compensating ramp, which allows the maximum inductor current to remain unaffected throughout all duty cycles.

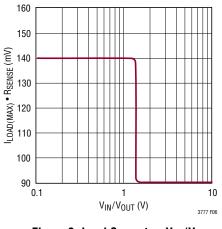

#### **R<sub>SENSE</sub> Selection and Maximum Output Current**

The R<sub>SENSE</sub> resistance must be chosen properly to achieve the desired amount of output current. Too much resistance can limit the output current below the application requirements. Start by determining the maximum allowed R<sub>SENSE</sub> resistance in the boost region, R<sub>SENSE</sub>(MAX,BOOST). Follow this by finding the maximum allowed R<sub>SENSE</sub> resistance in the buck region,  $R_{SENSE(MAX,BUCK)}$ . The selected  $R_{SENSE}$  resistance must be smaller than both. Figure 6 shows how  $I_{LOAD(MAX)} \bullet R_{SENSE}$  varies with input and output voltage.

Figure 6. Load Current vs  $V_{\text{IN}}/V_{\text{OUT}}$

**Boost Region:** In the boost region, the maximum output current capability is the least when  $V_{IN}$  is at its minimum and  $V_{OUT}$  is at its maximum. Therefore  $R_{SENSE}$  must be chosen to meet the output current requirements under these conditions.

Start by finding the boost region duty cycle when  $V_{\text{IN}}$  is minimum and  $V_{\text{OUT}}$  is maximum using:

$$DC_{(MAX,C,BOOST)} \cong \left(1 - \frac{V_{IN(MIN)}}{V_{OUT(MAX)}}\right) \bullet 100\%$$

For example, an application with a  $V_{\text{IN}}$  range of 12V to 48V and  $V_{\text{OUT}}$  set to 36V will have:

$$DC_{(MAX,C,BOOST)} \cong \left(1 - \frac{12V}{36V}\right) \bullet 100\% = 67\%$$

Next, the inductor ripple current in the boost region must be determined. If the main inductor L is not known, the maximum ripple current  $\Delta I_{L(MAX,BOOST)}$  can be estimated

by choosing  $\Delta I_{L(MAX,BOOST)}$  to be 30% to 50% of the maximum inductor current in the boost region as follows:

$$\Delta I_{L(MAX,BOOST)} \cong \frac{V_{OUT(MAX)} \bullet I_{OUT(MAX,BOOST)}}{V_{IN(MIN)} \bullet \left(\frac{100\%}{\% Ripple} - 0.5\right)} A$$

where:

$I_{OUT(MAX,BOOST)}$  is the maximum output load current required in the boost region

%Ripple is 30% to 50%

For example, using  $V_{OUT(MAX)} = 36V$ ,  $V_{IN(MIN)} = 12V$ ,  $I_{OUT(MAX,BOOST)} = 2A$  and %Ripple = 40% we can estimate:

$$\Delta I_{L(MAX,BOOST)} \cong \frac{36V \cdot 2A}{12V \cdot \left(\frac{100\%}{40\%} - 0.5\right)} = 3A$$

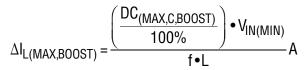

Otherwise, if the inductor value is already known then  $\Delta I_{L(MAX,BOOST)}$  can be more accurately calculated as follows:

where:

$\text{DC}_{(\text{MAX},\text{C},\text{BOOST})}$  is the maximum duty cycle percentage in the boost region as calculated previously.

f is the switching frequency

L is the inductance of the main inductor

After the maximum ripple current is known, the maximum allowed  $R_{\text{SENSE}}$  in the boost region can be calculated as follows:

$R_{SENSE(MAX,BOOST)} =$

$$\frac{2 \bullet V_{\text{RSENSE}(\text{MAX},\text{BOOST},\text{MAXDC})} \bullet V_{\text{IN}(\text{MIN})}}{\left(2 \bullet I_{\text{OUT}(\text{MAX},\text{BOOST})} \bullet V_{\text{OUT}(\text{MIN})}\right) + \left(\Delta I_{\text{L}(\text{MAX},\text{BOOST})} \bullet V_{\text{IN}(\text{MIN})}\right)}\Omega$$

where  $V_{\text{RSENSE}(\text{MAX},\text{BOOST},\text{MAXDC})}$  is the maximum inductor current sense voltage as discussed in the previous section.

Using values from the previous examples:

$$R_{\text{SENSE(MAX,BOOST)}} = \frac{2 \cdot 140 \text{mV} \cdot 12}{(2 \cdot 2\text{A} \cdot 36\text{V}) + (3\text{A} \cdot 12\text{V})} = 18.66 \text{m}\Omega$$

**Buck Region:** The duty cycle for buck operation can be calculated using:

$$DC_{(MAX,B,BUCK)} \cong \left(1 - \frac{V_{OUT(MIN)}}{V_{IN(MAX)}}\right) \bullet 100\%$$

Before calculating the maximum  $R_{SENSE}$  resistance, however, the inductor ripple current must be determined. If the main inductor L is not known, the ripple current  $\Delta I_{L(MIN,BUCK)}$  can be estimated by choosing  $\Delta I_{L(MIN,BUCK)}$  to be 10% of the maximum inductor current in the buck region as follows:

$$\Delta I_{L(MIN,BUCK)} \cong \frac{I_{OUT(MAX,BUCK)}}{\left(\frac{100\%}{10\%} - 0.5\right)} A$$

where:

$I_{\text{OUT}(\text{MAX},\text{BUCK})}$  is the maximum output load current required in the buck region.

If the inductor value is already known then  $\Delta I_{L(MIN,BUCK)}$  can be calculated as follows:

$$\Delta I_{L(MIN,BUCK)} = \frac{\left(\frac{DC_{(MIN,B,BUCK)}}{100\%}\right) \bullet V_{OUT(MIN)}}{f \bullet L} A$$

where:

$\text{DC}_{(\text{MIN},\text{B},\text{BUCK})}$  is the minimum duty cycle percentage in the buck region as calculated previously.

f is the switching frequency

L is the inductance of the main inductor

After the inductor ripple current is known, the maximum allowed  $\mathsf{R}_{\mathsf{SENSE}}$  in the buck region can be calculated as follows:

$$R_{\text{SENSE}(\text{MAX},\text{BUCK})} = \frac{2 \cdot V_{\text{RSENSE}(\text{MAX},\text{BUCK},\text{MINDC})}}{\left(2 \cdot I_{\text{OUT}(\text{MAX},\text{BUCK})}\right) - \Delta I_{\text{L}(\text{MIN},\text{BUCK})}} \Omega$$

#### Programming Input/Output Current Limit

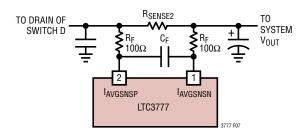

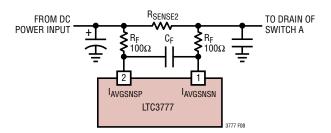

As shown in Figure 7 and Figure 8, input/output current sense resistor  $R_{SENSE2}$  should be placed between the bulk capacitor for  $V_{IN}$  or  $V_{OUT}$  and the decoupling capacitor. A lowpass filter formed by  $R_F$  and  $C_F$  is recommended to reduce the switching noise and stabilize the current loop. The input/output current limit is set internally to 50mV. If input/output current limit is not desired, the  $I_{AVGSNSP}$  and  $I_{AVGSNSN}$  pins should be shorted together to V5.

Figure 7. Programming Output Current Limit

Figure 8. Programming Input Current Limit

With the typical  $100\Omega$  resistors shown here, the value of capacitor C<sub>F</sub> should be  $1\mu$ F to  $4.7\mu$ F. The current loop's transfer function should approximate that of the voltage loop. Crossover frequency should be one-tenth the switching frequency, and gain should decrease by 20dB/decade. Similar current and voltage loop transfer functions will ensure overall system stability.

When the  $I_{AVGSNS}$  common mode voltage is above ~4V, the  $I_{AVGSNSN}$  pin sources 10µA. The  $I_{AVGSNSP}$  pin, however, sources 15µA, when a constant current is being regulated. The error introduced by this mismatch can be offset to a first order by scaling the  $I_{AVGSNSP}$  and  $I_{AVGSNSN}$  resistors accordingly. For example, if the  $I_{AVGSNSP}$  branch has a 100 $\Omega$  resistor, the 1.50mV across it can be replicated in the  $I_{AVGSNSN}$  branch by using a 150 $\Omega$  resistor.

When the  $I_{AVGSNS}$  common mode voltage falls below ~4V, the  $I_{AVGSNS}$  current decreases linearly; it reaches approximately -300µA at zero volts. The maximum current sinking can vary by 20% to 30% due to process variation. Ensure that  $I_{AVGSNS}$  common mode voltage never exceeds its absolute maximum of -10V below ground. Pay special attention to short-circuit conditions in high power applications.

#### Phase-Locked Loop and Frequency Synchronization

The LTC3777 has a phase-locked loop (PLL) comprised of an internal voltage-controlled oscillator (VCO) and a phase detector. This allows the turn-on of the bottom MOSFET of the controller to be locked to the rising edge of an external clock signal applied to the PLLIN pin. The phase detector is an edge sensitive digital type that provides zero degrees phase shift between the external and internal oscillators. This type of phase detector does not exhibit false locking to harmonics of the external clock.

The output of the phase detector is a pair of complementary current sources that charge or discharge the internal filter network. There is a precision 20µA of current flowing out of the FREQ pin. This allows a single resistor to SGND to set the switching frequency when no external clock is applied to the PLLIN pin. The internal switch between FREQ and the integrated PLL filter network is on, allowing the filter network to be pre-charged at the same voltage as the FREQ pin. The relationship between the voltage on the FREQ pin and operating frequency is shown in Figure 9 and specified in the Electrical Characteristics table. If an external clock is detected on the PLLIN pin, the internal switch previously mentioned will turn off and isolate the influence of the FREQ pin.

Note that the LTC3777 can only be synchronized to an external clock whose frequency is within range of the LTC3777's internal VCO. This is guaranteed to be between 50kHz and 600kHz. A simplified block diagram is shown in Figure 10.

Figure 9. FREQ Pin Resistor Value vs Frequency

Figure 10. Phase-Locked Loop Block Diagram

If the external clock frequency is greater than the internal oscillator's frequency,  $f_{OSC}$ , then current is sourced continuously from the phase detector output, pulling up the filter network. When the external clock frequency is less than  $f_{OSC}$ , current is sunk continuously, pulling down the filter network. If the external and internal frequencies are the same but exhibit a phase difference, the current sources turn on for the amount of time corresponding to the phase difference. The voltage on the filter network is

adjusted until the phase and frequency of the internal and external oscillators are identical. At the stable operating point, the phase detector output is high impedance and the filter capacitor holds the voltage.

Typically, the external clock (on the PLLIN pin) input high threshold is 2V, while the input low threshold is 1.2V.

The operating frequency of the LTC3777 can be approximated using the following formula:

$R_{FREQ} = 0.000115(f_{OSC})^2 + 0.174(f_{OSC}) + 18.5$

where  $f_{OSC}$  is in kHz and  $R_{FREQ}$  is in k $\Omega$ .

#### **Inductor Selection**

The operating frequency and inductor selection are interrelated in that higher operating frequencies allow the use of smaller inductor and capacitor values. The inductor value has a direct effect on ripple current. The inductor current ripple  $\Delta I_L$  is typically set to 20% to 40% of the maximum inductor current in the boost region at V<sub>IN(MIN)</sub>. For a given ripple the inductance terms in continuous mode are as follows:

$$\begin{split} L_{BOOST} &> \frac{V_{IN(MIN)}}{f \bullet I_{OUT(MAX)}} \frac{2 \bullet \left(V_{OUT} - V_{IN(MIN)}\right) \bullet 100}{f \bullet I_{OUT(MAX)}} H, \\ L_{BUCK} &> \frac{V_{OUT} \bullet \left(V_{IN(MAX)} - V_{OUT}\right) \bullet 100}{f \bullet I_{OUT(MAX)}} H \end{split}$$

where:

f is operating frequency, Hz

% Ripple is allowable inductor current ripple

V<sub>IN(MIN)</sub> is minimum input voltage, V

VIN(MAX) is maximum input voltage, V

V<sub>OUT</sub> is output voltage, V

I<sub>OUT(MAX)</sub> is maximum output load current, A