19-4985; Rev 2; 7/10

EVALUATION KIT AVAILABLE

industry-standard 36MHz IF.

oscillator.

DVB-T/DVB-T2 +

DVB-C + PAL/SECAM

PAL/SECAM

**General Description**

**Applications**

DTMB/GB20600 + PAL

ATSC + NTSC

The MAX3543 hybrid broadband single-conversion tele-

vision tuner is designed for use in analog (PAL, SECAM)

+ digital (DVB-T, GB20600) television sets and terrestrial

receivers. It receives all television bands from 47MHz

to 862MHz and converts the selected channel to an

The MAX3543 includes a variable-gain low-noise input

amplifier; an RF tracking filter; an image rejection mixer;

a peak detector; an optional internal, self-contained

RF gain-control loop (RFAGC); a VCO with fractional-N

PLL; an IF bandpass filter; an IF variable-gain amplifier;

separate analog and digital IF outputs; and a crystal

The MAX3543 is available in a small, 6mm x 6mm, thin QFN package, and the application circuit fits in 20mm x 25mm on

a two-layer board with single-sided component mounting.

### Multiband Analog and Digital Television Tuner

#### \_Features

- Standard IF Architecture Ensures < -70dBc Spurs</p>

- Integrated RF Tracking Filter

- Integrated IF Bandpass Filter

- ♦ Full-Band Coverage (47MHz to 862MHz)

- ♦ 70dB Image Rejection

- ♦ 4dB Noise Figure

- Fast-Locking, Low Phase-Noise PLL Supports 256QAM

- Crystal Oscillator and Buffer/Divider to Drive Baseband IC

- ♦ 745mW Power Dissipation

#### Ordering Information

| PART        | TEMP RANGE   | PIN-PACKAGE |

|-------------|--------------|-------------|

| MAX3543CTL+ | 0°C to +70°C | 40 TQFN-EP* |

+Denotes a lead(Pb)-free/RoHS-compliant package. \*EP = Exposed paddle.

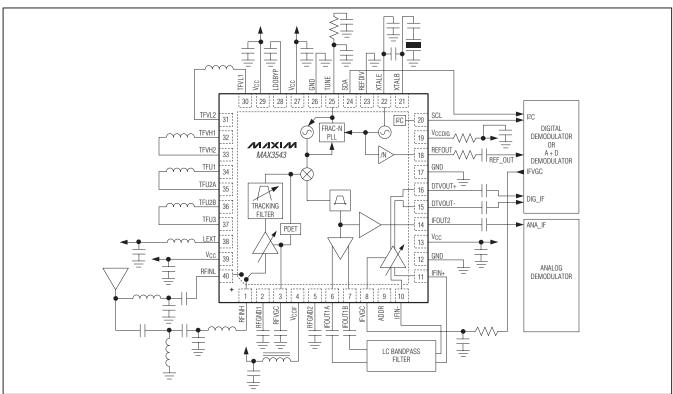

### Block Diagram/Typical Application Circuit/Pin Configuration

###

Maxim Integrated Products 1

MAX354:

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

#### **ABSOLUTE MAXIMUM RATINGS**

| VCC to GND0.3V to +3.6V                                  |

|----------------------------------------------------------|

| RFINL, RFINH, IFIN+, IFIN-, DTVOUT+, DTVOUT-,            |

| IFOUT1A, IFOUT1B, IFOUT20.3V to (V <sub>CC</sub> + 0.3V) |

| SDA, SCLK, IFAGC, RFVGA0.3V to +3.6V                     |

| Short-Circuit Protection: DTVOUT+, DTVOUT-,              |

| IFOUT1A, IFOUT1B, IFOUT2Indefinite                       |

| RF Input Power+10dBm                                     |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

|-------------------------------------------------------|----------------|

| (derate 35.7mW/°C above +70°C)                        | 2857mW         |

| Operating Temperature Range                           | 0°C to +70°C   |

| Junction Temperature                                  | +150°C         |

| Storage Temperature Range                             | 65°C to +165°C |

| Lead Temperature (soldering, 10s)                     | +300°C         |

| Soldering Temperature (reflow)                        | +260°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

(MAX3543 Evaluation Kit,  $V_{CC} = 3.1V$  to 3.5V,  $T_A = 0^{\circ}C$  to +70°C, registers set according to Table 1. Typical values are at  $V_{CC} = 3.3V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                           | CONDITIONS                             | MIN                      | ТҮР | MAX                      | UNITS |

|-------------------------------------|----------------------------------------|--------------------------|-----|--------------------------|-------|

| SUPPLY VOLTAGE AND CURP             | ENT                                    | ·                        |     |                          |       |

| Supply Voltage                      |                                        | 3.1                      |     | 3.5                      | V     |

| Supply Current                      | IF VGA enabled                         |                          | 225 | 270                      | mA    |

| Supply Current                      | Standby (REF oscillator on) R08[7] = 1 |                          | 5   |                          |       |

| RF and IF VGC Input<br>Bias Current |                                        | -100 to<br>+100          |     | μA                       |       |

| RF and IF VGC Control Voltage       | Maximum gain                           | 3.0                      |     |                          | V     |

| RF and IF VGC Control Voltage       | Minimum gain                           |                          |     | 0.5                      | V     |

| SERIAL INTERFACE                    |                                        |                          |     |                          |       |

| Input Logic-Level Low               |                                        |                          |     | 0.3 x<br>V <sub>CC</sub> | V     |

| Input Logic-Level High              |                                        | 0.7 x<br>V <sub>CC</sub> |     |                          | V     |

| Output Logic-Level Low              | 3mA sink current                       |                          |     | 0.4                      | V     |

| Output Logic-Level High             |                                        | VCC -<br>0.5V            |     |                          | V     |

| Maximum Clock Rate                  |                                        | 400                      |     |                          | kHz   |

### AC ELECTRICAL CHARACTERISTICS

(MAX3543 Evaluation Kit, RF center frequency = 666MHz, IF center frequency = 36.15MHz, registers set according to Table 1, fREF = 16MHz, VRFVGC = VIFVGC = 3.0V, VCC = 3.3V, TA =  $+25^{\circ}$ C, unless otherwise noted.)

| PARAMETER                                    | CONDITIONS               |     | TYP | MAX | UNITS |  |  |  |  |  |

|----------------------------------------------|--------------------------|-----|-----|-----|-------|--|--|--|--|--|

| OVERALL REQUIREMENTS (RF INPUT TO IF OUTPUT) |                          |     |     |     |       |  |  |  |  |  |

| RFINL Operating<br>Frequency Range           | Tunable frequency range  | 47  |     | 345 | MHz   |  |  |  |  |  |

| RFINH Operating<br>Frequency Range           | Tunable frequency range  | 345 |     | 862 | MHz   |  |  |  |  |  |

| Maximum Voltage<br>Gain to IFOUT1            | DVB-T mode (see Table 1) |     | 50  |     | dB    |  |  |  |  |  |

**MAX3543**

#### AC ELECTRICAL CHARACTERISTICS (continued)

(MAX3543 Evaluation Kit, RF center frequency = 666MHz, IF center frequency = 36.15MHz, registers set according to Table 1, fREF = 16MHz, VRFVGC = VIFVGC = 3.0V, VCC = 3.3V, TA =  $+25^{\circ}$ C, unless otherwise noted.)

| PARAMETER                                          | CONDITI                                             | MIN                                           | TYP | MAX   | UNITS         |      |

|----------------------------------------------------|-----------------------------------------------------|-----------------------------------------------|-----|-------|---------------|------|

| RF Gain Control Range                              | (gain at VRFVGC = 3.0V) - (gain                     |                                               | 53  |       | dB            |      |

| Noise Figure                                       |                                                     |                                               |     |       |               |      |

| Image Rejection                                    | Image applied at 77.8MHz above desired channel's    | 47MHz to 470MHz                               |     | > 70  |               | dB   |

| inage nejection                                    | center frequency                                    | 470MHz to 862MHz                              |     | > 65  |               | GD   |

| IF VARIABLE-GAIN AMPLIFI                           | ER                                                  |                                               |     |       |               |      |

| Maximum Voltage Gain                               | Output load impedance > $2k\Omega$                  | II3pF, differential load                      |     | 60    |               | dB   |

| Minimum Voltage Gain                               | Output load impedance > $2k\Omega$<br>VIFVGC = 0.5V | ll3pF, differential load,                     |     | 19    |               | dB   |

| In-Channel Output V1dB                             | 36.15MHz CW output signal                           |                                               |     | > 2.5 |               | VP-P |

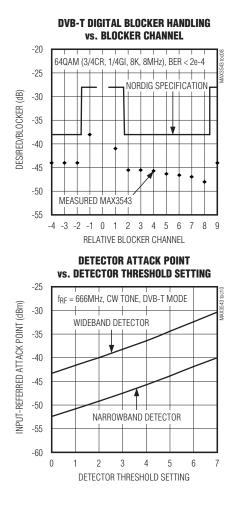

| DETECTOR                                           |                                                     |                                               |     |       |               |      |

| Wideband Detector<br>Input-Referred Attack Point   | Programmable, R0B[6:4] = 100                        | Programmable, R0B[6:4] = 100, CW input signal |     |       |               | dBm  |

| Narrowband Detector<br>Input-Referred Attack Point | Programmable, R0B[2:0] = 011                        | Programmable, R0B[2:0] = 011, CW input signal |     |       |               | dBm  |

| SIGMA-DELTA FRAC-N SYN                             | THESIZER                                            |                                               | ,   |       |               |      |

| N-Divider Value                                    |                                                     |                                               | 19  |       | 251           |      |

| Fractional-N Resolution                            |                                                     |                                               |     | 20    |               | Bits |

| Phase-Detector Frequency                           | f <sub>XTAL</sub> /2                                |                                               | 8   |       | 10.5          | MHz  |

| Phase-Detector Frequency                           | f <sub>XTAL</sub> /1                                |                                               | 16  |       | 21            | MHz  |

| REFERENCE OSCILLATOR                               |                                                     |                                               |     |       |               |      |

| Frequency                                          | (Note 2)                                            |                                               | 16  |       | 32            | MHz  |

| External Overdrive Level                           | AC-coupled sine-wave input                          |                                               | 0.5 |       | 1.5           | VP-P |

| REFERENCE OSCILLATOR                               | OUTPUT BUFFER                                       |                                               |     |       |               |      |

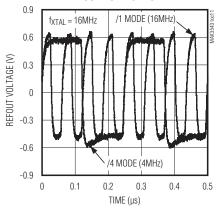

| Output Frequency                                   | /1, /4 modes                                        |                                               | 4   | 4     | <b>f</b> XTAL | MHz  |

| Output Level                                       | Load Impedance > 20kΩll3pF                          |                                               |     | 1.1   |               | VP-P |

Note 1: Guaranteed by production test at +25°C. 0°C and +70°C are guaranteed by design and characterization.

Note 2: Guaranteed by design and characterization.

### Typical Register Summary

Table 1 shows register settings to configure the MAX3543 for operation with a 16MHz crystal frequency and 666MHz RF frequency with a differential LC bandpass filter.

### **Table 1. Typical Register Settings**

| REGISTER<br>NAME | NAME ADDRESS REGISTER FUNCTION |                          | DVB-T MODE, 8MHz<br>DIFFERENTIAL IF<br>(hex) | PAL MODE,<br>ATV OUTPUT<br>(hex) |

|------------------|--------------------------------|--------------------------|----------------------------------------------|----------------------------------|

| R00              | 0x00                           | VCO                      | 4C                                           | 4C                               |

| R01              | 0x01                           | NDIV INT                 | 2B                                           | 57                               |

| R02              | 0x02                           | NDIV FRAC2               | 8E                                           | 9C                               |

| R03              | 0x03                           | NDIV FRAC1               | 26                                           | 4C                               |

| R04              | 0x04                           | NDIV FRAC0 (VAS Trigger) | 66                                           | CD                               |

| R05              | 0x05                           | MODE CTRL                | D8                                           | DA                               |

| R06              | 0x06                           | TFS                      | Calculated from ROM values                   | Calculated from ROM values       |

| R07              | 0x07                           | TFP                      | Calculated from ROM values                   | Calculated from ROM values       |

| R08              | 0x08                           | SHUTDOWN                 | 00                                           | 08                               |

| R09              | 0x09                           | REF CONFIG               | OA                                           | 0A                               |

| R0A              | 0x0A                           | VAS CONFIG               | 16                                           | 16                               |

| R0B              | 0x0B                           | PWRDET CFG1              | 43                                           | 43                               |

| R0C              | 0x0C                           | PWRDET CFG2              | 01                                           | 03                               |

| ROD              | 0x0D                           | FILT CF ADJ              | Read from ROM                                | Read from ROM                    |

| R0E              | 0x0E                           | ROM ADDR                 | 00                                           | 00                               |

| R0F              | 0x0F                           | IRHR                     | Read from ROM                                | Read from ROM                    |

| R10              | 0x10                           | ROM READBACK             | Read only                                    | Read only                        |

| R11              | 0x11                           | VAS STATUS               | Read only                                    | Read only                        |

| R12              | 0x12                           | GEN STATUS               | Read only                                    | Read only                        |

| R13              | 0x13                           | BIAS ADJ                 | 56                                           | 16                               |

| R14              | 0x14                           | TEST1                    | 40                                           | 40                               |

| R15              | 0x15                           | ROM WRITE DATA           | Maxim use only                               | Maxim use only                   |

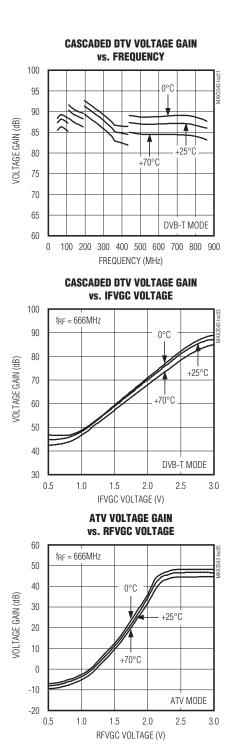

### **Typical Operating Characteristics**

(MAX3543 Evaluation Kit, V<sub>CC</sub> = 3.3V, T<sub>A</sub> = +25°C, registers set according to Table 1, unless otherwise noted.)

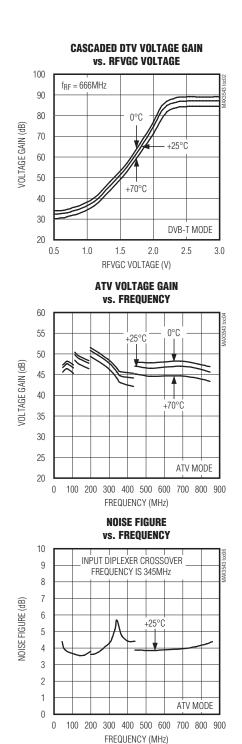

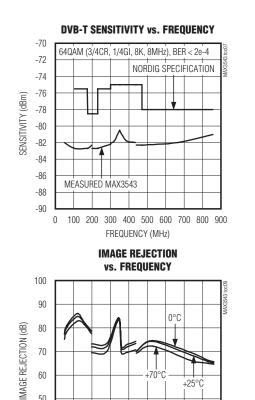

### **Typical Operating Characteristics (continued)**

(MAX3543 Evaluation Kit, V<sub>CC</sub> = 3.3V, T<sub>A</sub> = +25°C, registers set according to Table 1, unless otherwise noted.)

+25°C

DVB-T MODE

100 200 300 400 500 600 700 800 900

FREQUENCY (MHz)

60

50

40

30

0

**REFOUT VOLTAGE vs. TIME**

Pin Description

| 2         RFGND1         RF Ground. Bypass to the PCB's ground plane with a 1000pF capacitor. Keep traces as short as possible to minimize inductance to ground plane. Do not connect RFGND1 and RFGND2 together.           3         RFVGC         RF VGA Gain Control Voltage. Accepts a DC voltage from 0.5V to 3V.           4         VCCIF         IF Power Supply. Requires a 6000 series ferrite bead to a bypass capacitor to ground.           5         RFGND2         RF Ground. Bypass to the PCB's ground plane with a 1000pF capacitor. Keep traces as short as possible to minimize inductance to ground plane. Do not connect RFGND1 and RFGND2 together.           6         IFOUT1A         Dual-Mode DTV IF Output. In single-ended mode, this pin is the IF signal output. In differential mode, this pin is the positive terminal of the differential IF output.           7         IFOUT1B         Dual-Mode DTV IF Output. In single-ended mode, this pin is the SAW filter bandwidth switch. In differential mode, this pin is the positive terminal of the differential IF output.           8         IFVGC         IF VGA Gain Control Voltage. Accepts a DC voltage from 0.5V to 3V.           9         ADDR         Iterface. There are three selectable addresses based on the state of this pin: logic-low, logic-lingh, or unconnected.           10, 11         IFIN-, IFIN+         Differential IF VGA Input. Connect to the IF filter output.           13, 27, 29, 39         Vcc         Power-Supply Connections. Bypass each supply pin with a separate 1000pF capacitor to ground.           14 <th>PIN</th> <th>NAME</th> <th>FUNCTION</th>                                                       | PIN        | NAME         | FUNCTION                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2         PH'GNU1         possible to minimize inductance to ground plane. Do not connect RFGND1 and RFGND2 together,           3         RFVGC         RF VGA Gain Control Voltage. Accepts a DC voltage from 0.5V to 3V.           4         VCCIF         IF Power Supply. Requires a 6000 series ferrite bead to a bypass capacitor to ground.           5         RFGND2         RFGND2         RFGND2           6         IFOUT1A         Dual-Mode DTV IF Output. In single-ended mode, this pin is the IF signal output. In differential mode, the pin is the positive terminal of the differential IF output.           7         IFOUT1A         Dual-Mode DTV IF Output. In single-ended mode, this pin is the SAW filter bandwidth switch. In differential mode, this pin is the negative terminal of the differential IF output.           8         IFVGC         IF VGA Gain Control Voltage. Accepts a DC voltage from 0.5V to 3V.           9         ADDR         Qual-Mode DTV IF Output. In single-ended mode, this pin is the SAW filter bandwidth switch. In differential IF vGA Gain Control Voltage. Accepts a DC voltage from 0.5V to 3V.           9         ADDR         IFVGA Gain Control Voltage. Accepts a DC voltage from 0.5V to 3V.           9         ADDR         Interface. There are three selectable addresses based on the state of this pin: logic-low, logic-high, or unconnected.           10, 11         IFIN., IFIN.         Differential IF VGA Input. Connect to the lifeliter output.           12, 17, 26         GND                                                                                                                                                                       | 1          | RFINH        | High-Frequency RF Input. Matched to 75 $\Omega$ over the operating band. Requires a DC-blocking capacitor.                                                                                                       |

| 4         VCcIF         IF Power Supply. Requires a 600Ω series ferrite bead to a bypass capacitor to ground.           5         RFGND2         RF Ground. Bypass to the PCB's ground plane with a 1000pF capacitor. Keep traces as short as possible to minimize inductance to ground plane. Do not connet RFGND1 and RFGND2 together.           6         IFOUT1A         Dual-Mode DTV IF Output. In single-ended mode, this pin is the IF signal output. In differential mode, the pin is the positive terminal of the differential IF output.           7         IFOUT1A         Dual-Mode DTV IF Output. In single-ended mode, this pin is the SAW filter bandwidth switch. In differential mode, this pin is the negative terminal of the differential IF output.           8         IFVGC         IF VGA Gain Control Voltage. Accepts a DC voltage from 0.5V to 3V.           2-Wire Serial-Interface Address Line. This pin sets the device address for the IPC-compatible serial interface. There are three selectable addresses based on the state of this pin: logic-low, logic-high, or unconnected.           10, 11         IFIN., IFIN+         Differential IF VGA Input. Connect to the IF filter output.           12, 17, 26         GND         Ground. Connect pin to paddle ground to minimize trace inductance.           13, 27, 29, 39         Vcc         Power-Supply Connections. Bypass each supply pin with a separate 1000pF Capacitor to ground.           14         IFOUT2         Single-Ended IF Output. Connect to the demodulator input. Requires a 1000pF DC-blocking capacitor.           20         ScL </td <td>2</td> <td>RFGND1</td> <td></td>                                                | 2          | RFGND1       |                                                                                                                                                                                                                  |

| 5         RFGND2         RF Ground. Bypass to the PCB's ground plane with a 1000pF capacitor. Keep traces as short as possible to minimize inductance to ground plane. Do not connect RFGND1 and RFGND2 together.           6         IFOUT1A         Dual-Mode DTV IF Output. In single-ended mode, this pin is the IF signal output. In differential mode, the jin is the possible terminal of the differential IF output.           7         IFOUT1B         Dual-Mode DTV IF Output. In single-ended mode, this pin is the SAW filter bandwidth switch. In differential mode, this pin is the possible terminal of the differential IF output.           8         IFVGC IF VGA Gain Control Voltage. Accepts a DC voltage from 0.5V to 3V.           9         ADDR         Inferential IF VGA Input. Connect to the IF filter output.           10.11         IFIN-, IFIN+         Differential IF VGA Input. Connect to the IF filter output.           12, 17, 26         GND         Ground. Connect pin to paddle ground to minimize trace inductance.           13, 27, 29, 39         Vcc         Power-Supply Connections. Bypass each supply pin with a separate 1000pF capacitor to ground.           14         IFOUT2         Single-Ended IF Output. Connect to the analog demodulator input. Requires a 1000pF DC-blocking capacitor.           18         REFOUT         Crystal Output to Drive Baseband IC. Output frequency is fxrAL or fxrAL/4.           19         VccDI         Differential IF VGA Output. Connect to the serial bus and ensure the bus includes an approximately 5kQ pullup resistor. </td <td>3</td> <td>RFVGC</td> <td>RF VGA Gain Control Voltage. Accepts a DC voltage from 0.5V to 3V.</td> | 3          | RFVGC        | RF VGA Gain Control Voltage. Accepts a DC voltage from 0.5V to 3V.                                                                                                                                               |

| 5         HFGND2         possible to minimize inductance to ground plane. Do not connect RFGND1 and RFGND2 together.           6         IFOUT1A         Dual-Mode DTV IF Output. In single-ended mode, this pin is the IF signal output. In differential mode, the pin is the positive terminal of the differential IF output.           7         IFOUT1B         Dual-Mode DTV IF Output. In single-ended mode, this pin is the SAW filter bandwidth switch. In differential mode, this pin is the negative terminal of the differential IF output.           8         IFVGC         IF VGA Gain Control Voltage. Accepts a DC voltage from 0.5V to 3V.           9         ADDR         2-Wire Serial-Interface Address Line. This pin sets the device address for the IPC-compatible serial interface. There are three are three selectable addresses based on the state of this pin: logic-low, logic-lingh, or unconnected.           10.11         IFIN-F         Differential IF VGA Input. Connect to the IF filter output.           12, 17, 26         GND         Ground. Connect pin to paddle ground to minimize trace inductance.           13, 27, 29, 33         Vcc         Power-Supply Connections. Bypass each supply pin with a separate 1000pF capacitor to ground.           14         IFOUT2         Single-Ended IF Output. Connect to the analog demodulator input. Requires a 1000pF DC-blocking capacitor.           15         DTVOUT-<br>DTVOUT-<br>DIFortnal IF VGA Output to Drive Baseband IC. Output frequency is fxTAL or fxTAL/4.         Output peristor.           20         ScL                                                                                                                    | 4          | VCCIF        | IF Power Supply. Requires a 600 $\Omega$ series ferrite bead to a bypass capacitor to ground.                                                                                                                    |

| b         IFOUTIA         pin is the positive terminal of the differential IF output.           7         IFOUTIB         Dual-Mode DTV IF Output. In single-ended mode, this pin is the SAW filter bandwidth switch. In differential mode, this pin is the negative terminal of the differential IF output.           8         IFVGC         IF VGA Gain Control Voltage. Accepts a DC voltage from 0.5V to 3V.           9         ADDR         2-Wire Serial-Interface Address Line. This pin sets the device address for the I2C-compatible serial interface. There are three selectable addresses based on the state of this pin: logic-low, logic-high, or unconnected.           10.11         IFIN-, IFIN+         Differential IF VGA Input. Connect to the IF filter output.           12, 17, 26         GND         Ground. Connect pin to paddle ground to minimize trace inductance.           13, 27, 29, 39         Vcc         Power-Supply Connections. Bypass each supply pin with a separate 1000pF capacitor to ground.           14         IFOUT1-<br>DTVOUT-<br>DTVOUT-<br>DTVOUT-<br>DTVOUT-<br>DTVOUT-<br>DTVOUT-<br>DTVOUT-<br>DTVOUT-<br>20         Differential IF VGA Output. Connect to the demodulator input. Requires a 1000pF DC-blocking capacitor.           20         SCL         Crystal Output to Drive Baseband IC. Output frequency is fxTAL or fxTAL/4.           19         Vccnig         Digital Supply. Requires a 15Ω series resistor to a 1µF bypass capacitor.           21         XTALB         Crystal Occlillator Base. Connect to the crystal through a DC-blocking capacitor to XTALB.                                                                                                | 5          | RFGND2       |                                                                                                                                                                                                                  |

| 7       IFOUT1B       differential mode, this pin is the negative terminal of the differential IF output.         8       IFVGC       IF VGA Gain Control Voltage. Accepts a DC voltage from 0.5V to 3V.         9       ADDR       Procession Control Voltage. Accepts a DC voltage from 0.5V to 3V.         9       ADDR       Procession Control Voltage. Accepts a DC voltage from 0.5V to 3V.         9       ADDR       Procession Control Voltage. Accepts a DC voltage from 0.5V to 3V.         9       ADDR       Procession Control Voltage. Accepts a DC voltage from 0.5V to 3V.         9       ADDR       Procession Control Voltage. Accepts a DC voltage from 0.5V to 3V.         9       ADDR       Procession Control Voltage. Accepts a DC voltage from 0.5V to 3V.         9       ADDR       Differential IF VGA Input. Connect to the IF filter output.         12, 17, 26       GND       Ground. Connect pin to paddle ground to minimize trace inductance.         13, 27, 29, 39       Vcc       Power-Supply Connections. Bypass each supply pin with a separate 1000pF capacitor to ground.         14       IFOUT2       Single-Ended IF Output. Connect to the analog demodulator input. Requires a 1000pF DC-blocking capacitor.         15, 16       DTVOUT+<br>DTVOUT+<br>DTVOUT+       Differential IF VGA Output. Connect to the demodulator input. Requires a 1000pF DC-blocking capacitor.         20       Scl       Scl       Crystal                                                                                                                                                                                                                                                                   | 6          | IFOUT1A      | Dual-Mode DTV IF Output. In single-ended mode, this pin is the IF signal output. In differential mode, this pin is the positive terminal of the differential IF output.                                          |

| 9       ADDR       2-Wire Serial-Interface Address Line. This pin sets the device address for the I2C-compatible serial interface. There are three selectable addresses based on the state of this pin: logic-low, logic-high, or unconnected.         10, 11       IFIN-, IFIN+       Differential IF VGA Input. Connect to the IF filter output.         12, 17, 26       GND       Ground. Connect pin to paddle ground to minimize trace inductance.         13, 27, 29, 39       Vcc       Power-Supply Connections. Bypass each supply pin with a separate 1000pF capacitor to ground.         14       IFOUT2       Single-Ended IF Output. Connect to the analog demodulator input. Requires a 1000pF DC-blocking capacitor.         15, 16       DTVOUT-, DTVOUT+       Differential IF VGA Output. Connect to the demodulator input. Requires a 1000pF DC-blocking capacitor.         20       SCL       Crystal Output to Drive Baseband IC. Output frequency is fxTAL or fxTAL/4.         19       VccDig       Digital Supply. Requires a 15Ω series resistor to a 1µF bypass capacitor.         20       SCL       2-Wire Serial Clock Interface. Connect to the serial bus and ensure the bus includes an approximately skQ pullup resistor.         21       XTALB       Crystal Oscillator Emitter. Connect a capacitor to ground and a capacitor to XTALB.         22       XTALE       Crystal Oscillator Emitter. Connect a capacitor to ground and a capacitor to XTALB.         23       ReFpIV       Reference Frequency Divider Control. Three m                                                                                                                                                                       | 7          | IFOUT1B      |                                                                                                                                                                                                                  |

| 9ADDRinterface. There are three selectable addresses based on the state of this pin: logic-low, logic-high, or<br>unconnected.10, 11IFIN-, IFIN+Differential IF VGA Input. Connect to the IF filter output.12, 17, 26GNDGround. Connect pin to paddle ground to minimize trace inductance.13, 27,<br>29, 39VccPower-Supply Connections. Bypass each supply pin with a separate 1000pF capacitor to ground.14IFOUT2Single-Ended IF Output. Connect to the analog demodulator input. Requires a 1000pF DC-blocking<br>capacitor.15, 16DTVOUT-<br>DTVOUT+Differential IF VGA Output. Connect to the demodulator input. Requires a 1000pF DC-blocking capacitor.18REFOUTCrystal Output to Drive Baseband IC. Output frequency is f <sub>XTAL</sub> or f <sub>XTAL</sub> /4.19VcCDIGDigital Supply. Requires a 15Ω series resistor to a 1µF bypass capacitor.20SCLCrystal Occl Interface. Connect to the crystal through a DC-blocking capacitor and connect a capacitor<br>to XTALE.21XTALBCrystal Oscillator Base. Connect to the crystal through a DC-blocking capacitor and connect a capacitor<br>to XTALE.23REFDIVReference Frequency Divider Control. Three modes are available depending on the state of this pin:<br>high = f <sub>XTAL</sub> /1, low = f <sub>XTAL</sub> /1, unconnected mode should only be used if the controller car<br>reprogram IPC in any of the divider settings.24SDASDA2-Wire Serial Data Interface. Connect to serial bus and ensure the bus includes an approximately 5kΩ<br>rulup resistor.25TUNEPLL Charge-Pump Output and TUNE Input. Connect to the PLL loop filter.                                                                                                                                       | 8          | IFVGC        | IF VGA Gain Control Voltage. Accepts a DC voltage from 0.5V to 3V.                                                                                                                                               |

| 12, 17, 26       GND       Ground. Connect pin to paddle ground to minimize trace inductance.         13, 27, 29, 39       Vcc       Power-Supply Connections. Bypass each supply pin with a separate 1000pF capacitor to ground.         14       IFOUT2       Single-Ended IF Output. Connect to the analog demodulator input. Requires a 1000pF DC-blocking capacitor.         15, 16       DTVOUT-, DTVOUT-, DTVOUT+       Differential IF VGA Output. Connect to the demodulator input. Requires a 1000pF DC-blocking capacitor.         18       REFOUT       Crystal Output to Drive Baseband IC. Output frequency is fxTAL or fxTAL/4.         19       VccDiG       Digital Supply. Requires a 15Ω series resistor to a 1µF bypass capacitor.         20       SCL       2-Wire Serial Clock Interface. Connect to the serial bus and ensure the bus includes an approximately 5kΩ pullup resistor.         21       XTALB       Crystal Oscillator Emitter. Connect a capacitor to ground and a capacitor to XTALB.         23       REFDIV       Reference Frequency Divider Control. Three modes are available depending on the state of this pin: high = fxTAL/1, low = fxTAL/4, unconnected = state determined by register. Note: Power-up state of register is not guaranteed; therefore, unconnected mode should only be used if the controller car reprogram IPC in any of the divider settings.         24       SDA       2-Wire Serial Data Interface. Connect to serial bus and ensure the bus includes an approximately 5kΩ pullup resistor.         25       TUNE       PLL Charge-Pump Outpu                                                                                                                           | 9          | ADDR         | interface. There are three selectable addresses based on the state of this pin: logic-low, logic-high, or                                                                                                        |

| 13, 27,<br>29, 39VccPower-Supply Connections. Bypass each supply pin with a separate 1000pF capacitor to ground.14IFOUT2Single-Ended IF Output. Connect to the analog demodulator input. Requires a 1000pF DC-blocking<br>capacitor.15, 16DTVOUT-,<br>DTVOUT+Differential IF VGA Output. Connect to the demodulator input. Requires a 1000pF DC-blocking capacitor.18REFOUTCrystal Output to Drive Baseband IC. Output frequency is f <sub>XTAL</sub> or f <sub>XTAL</sub> /4.19VccDiGDigital Supply. Requires a 15Ω series resistor to a 1µF bypass capacitor.20SCL2-Wire Serial Clock Interface. Connect to the serial bus and ensure the bus includes an approximately<br>5kΩ pullup resistor.21XTALBCrystal Oscillator Base. Connect to the crystal through a DC-blocking capacitor to XTALB.23REFDIVReference Frequency Divider Control. Three modes are available depending on the state of this pin:<br>high = f <sub>XTAL</sub> /1, low = f <sub>XTAL</sub> /4, unconnected = state determined by register. Note: Power-up state of<br>register is not guaranteed; therefore, unconnected mode should only be used if the controller car<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10, 11     | IFIN-, IFIN+ | Differential IF VGA Input. Connect to the IF filter output.                                                                                                                                                      |

| 29, 39VCCPower-Supply Connections. Bypass each supply pin with a separate 1000pF capacitor to ground.14IFOUT2Single-Ended IF Output. Connect to the analog demodulator input. Requires a 1000pF DC-blocking<br>capacitor.15, 16DTVOUT-,<br>DTVOUT+Differential IF VGA Output. Connect to the demodulator input. Requires a 1000pF DC-blocking capacitor18REFOUTCrystal Output to Drive Baseband IC. Output frequency is fxTAL or fxTAL/4.19VCCDIGDigital Supply. Requires a 15Ω series resistor to a 1µF bypass capacitor.20SCL2-Wire Serial Clock Interface. Connect to the serial bus and ensure the bus includes an approximately<br>5kΩ pullup resistor.21XTALBCrystal Oscillator Base. Connect to the crystal through a DC-blocking capacitor to XTALE.22XTALECrystal Oscillator Emitter. Connect a capacitor to ground and a capacitor to XTALB.23REFDIVReference Frequency Divider Control. Three modes are available depending on the state of this pin:<br>high = fxTAL/1, low = fxTAL/4, unconnected = state determined by register. Note: Power-up state of<br>register is not guaranteed; therefore, unconnected mode should only be used if the controller can<br>reprogram IPC in any of the divider settings.24SDA2-Wire Serial Data Interface. Connect to serial bus and ensure the bus includes an approximately 5kΩ<br>pullup resistor.25TUNEPLL Charge-Pump Output and TUNE Input. Connect to the PLL loop filter.                                                                                                                                                                                                                                                                                                          | 12, 17, 26 | GND          | Ground. Connect pin to paddle ground to minimize trace inductance.                                                                                                                                               |

| 14IFOUT2capacitor.15, 16DTVOUT-,<br>DTVOUT+Differential IF VGA Output. Connect to the demodulator input. Requires a 1000pF DC-blocking capacitor.18REFOUTCrystal Output to Drive Baseband IC. Output frequency is fxTAL or fxTAL/4.19VCCDIGDigital Supply. Requires a 15Ω series resistor to a 1µF bypass capacitor.20SCL2-Wire Serial Clock Interface. Connect to the serial bus and ensure the bus includes an approximately<br>5kΩ pullup resistor.21XTALBCrystal Oscillator Base. Connect to the crystal through a DC-blocking capacitor to XTALE.22XTALECrystal Oscillator Emitter. Connect a capacitor to ground and a capacitor to XTALB.23REFDIVReference Frequency Divider Control. Three modes are available depending on the state of this pin:<br>high = fxTAL/1, low = fxTAL/4, unconnected = state determined by register. Note: Power-up state of<br>register is not guaranteed; therefore, unconnected mode should only be used if the controller car<br>reprogram I2C in any of the divider settings.24SDA2-Wire Serial Data Interface. Connect to serial bus and ensure the bus includes an approximately 5kΩ<br>pullup resistor.25TUNEPLL Charge-Pump Output and TUNE Input. Connect to the PLL loop filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | VCC          | Power-Supply Connections. Bypass each supply pin with a separate 1000pF capacitor to ground.                                                                                                                     |

| 15, 16DTVOUT+Differential IF VGA Output: Connect to the demodulator input. Hequires a 1000FF DC-blocking capacitor18REFOUTCrystal Output to Drive Baseband IC. Output frequency is f <sub>XTAL</sub> or f <sub>XTAL</sub> /4.19VCCDIGDigital Supply. Requires a 15Ω series resistor to a 1µF bypass capacitor.20SCL2-Wire Serial Clock Interface. Connect to the serial bus and ensure the bus includes an approximately 5kΩ pullup resistor.21XTALBCrystal Oscillator Base. Connect to the crystal through a DC-blocking capacitor and connect a capacitor to XTALE.22XTALECrystal Oscillator Emitter. Connect a capacitor to ground and a capacitor to XTALB.23REFDIVReference Frequency Divider Control. Three modes are available depending on the state of this pin:<br>high = f <sub>XTAL</sub> /1, low = f <sub>XTAL</sub> /4, unconnected mode should only be used if the controller can<br>reprogram I2C in any of the divider settings.24SDA2-Wire Serial Data Interface. Connect to serial bus and ensure the bus includes an approximately 5kΩ<br>pullup resistor.25TUNEPLL Charge-Pump Output and TUNE Input. Connect to the PLL loop filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 14         | IFOUT2       |                                                                                                                                                                                                                  |

| 19VCCDIGDigital Supply. Requires a 15Ω series resistor to a 1µF bypass capacitor.20SCL2-Wire Serial Clock Interface. Connect to the serial bus and ensure the bus includes an approximately<br>5kΩ pullup resistor.21XTALBCrystal Oscillator Base. Connect to the crystal through a DC-blocking capacitor and connect a capacitor<br>to XTALE.22XTALECrystal Oscillator Emitter. Connect a capacitor to ground and a capacitor to XTALB.23REFDIVReference Frequency Divider Control. Three modes are available depending on the state of this pin:<br>high = fxTAL/1, low = fxTAL/4, unconnected = state determined by register. Note: Power-up state of<br>register is not guaranteed; therefore, unconnected mode should only be used if the controller can<br>reprogram I²C in any of the divider settings.24SDA2-Wire Serial Data Interface. Connect to serial bus and ensure the bus includes an approximately 5kΩ<br>pullup resistor.25TUNEPLL Charge-Pump Output and TUNE Input. Connect to the PLL loop filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15, 16     |              | Differential IF VGA Output. Connect to the demodulator input. Requires a 1000pF DC-blocking capacitor.                                                                                                           |

| 20       SCL       2-Wire Serial Clock Interface. Connect to the serial bus and ensure the bus includes an approximately 5kΩ pullup resistor.         21       XTALB       Crystal Oscillator Base. Connect to the crystal through a DC-blocking capacitor and connect a capacitor to XTALE.         22       XTALE       Crystal Oscillator Emitter. Connect a capacitor to ground and a capacitor to XTALB.         23       Reference Frequency Divider Control. Three modes are available depending on the state of this pin: high = fXTAL/1, low = fXTAL/4, unconnected = state determined by register. Note: Power-up state of register is not guaranteed; therefore, unconnected mode should only be used if the controller can reprogram I²C in any of the divider settings.         24       SDA       2-Wire Serial Data Interface. Connect to serial bus and ensure the bus includes an approximately 5kΩ pullup resistor.         25       TUNE       PLL Charge-Pump Output and TUNE Input. Connect to the PLL loop filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 18         | REFOUT       | Crystal Output to Drive Baseband IC. Output frequency is fxTAL or fxTAL/4.                                                                                                                                       |

| 20       SCL       5kΩ pullup resistor.         21       XTALB       Crystal Oscillator Base. Connect to the crystal through a DC-blocking capacitor and connect a capacitor to XTALE.         22       XTALE       Crystal Oscillator Emitter. Connect a capacitor to ground and a capacitor to XTALB.         23       REFDIV       Reference Frequency Divider Control. Three modes are available depending on the state of this pin: high = fxTAL/1, low = fxTAL/4, unconnected = state determined by register. Note: Power-up state of register is not guaranteed; therefore, unconnected mode should only be used if the controller can reprogram I²C in any of the divider settings.         24       SDA       2-Wire Serial Data Interface. Connect to serial bus and ensure the bus includes an approximately 5kΩ pullup resistor.         25       TUNE       PLL Charge-Pump Output and TUNE Input. Connect to the PLL loop filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19         | VCCDIG       | Digital Supply. Requires a 15 $\Omega$ series resistor to a 1 $\mu$ F bypass capacitor.                                                                                                                          |

| 21       XTALB       to XTALE.         22       XTALE       Crystal Oscillator Emitter. Connect a capacitor to ground and a capacitor to XTALB.         23       REFDIV       Reference Frequency Divider Control. Three modes are available depending on the state of this pin:<br>high = f <sub>XTAL</sub> /1, low = f <sub>XTAL</sub> /4, unconnected = state determined by register. Note: Power-up state of<br>register is not guaranteed; therefore, unconnected mode should only be used if the controller can<br>reprogram I <sup>2</sup> C in any of the divider settings.         24       SDA       2-Wire Serial Data Interface. Connect to serial bus and ensure the bus includes an approximately 5kΩ<br>pullup resistor.         25       TUNE       PLL Charge-Pump Output and TUNE Input. Connect to the PLL loop filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 20         | SCL          |                                                                                                                                                                                                                  |

| 23       Reference Frequency Divider Control. Three modes are available depending on the state of this pin:         23       Reference Frequency Divider Control. Three modes are available depending on the state of this pin:         high = f <sub>XTAL</sub> /1, low = f <sub>XTAL</sub> /4, unconnected = state determined by register. Note: Power-up state of         register is not guaranteed; therefore, unconnected mode should only be used if the controller can         24       SDA         25       TUNE         PLL Charge-Pump Output and TUNE Input. Connect to the PLL loop filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 21         | XTALB        | Crystal Oscillator Base. Connect to the crystal through a DC-blocking capacitor and connect a capacitor to XTALE.                                                                                                |

| 23       REFDIV       high = f <sub>XTAL</sub> /1, low = f <sub>XTAL</sub> /4, unconnected = state determined by register. Note: Power-up state of register is not guaranteed; therefore, unconnected mode should only be used if the controller can reprogram I <sup>2</sup> C in any of the divider settings.         24       SDA       2-Wire Serial Data Interface. Connect to serial bus and ensure the bus includes an approximately 5kΩ pullup resistor.         25       TUNE       PLL Charge-Pump Output and TUNE Input. Connect to the PLL loop filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 22         | XTALE        | Crystal Oscillator Emitter. Connect a capacitor to ground and a capacitor to XTALB.                                                                                                                              |

| 24     SDA     pullup resistor.       25     TUNE     PLL Charge-Pump Output and TUNE Input. Connect to the PLL loop filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23         | REFDIV       | high = $f_{XTAL}/1$ , low = $f_{XTAL}/4$ , unconnected = state determined by register. Note: Power-up state of register is not guaranteed; therefore, unconnected mode should only be used if the controller can |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24         | SDA          |                                                                                                                                                                                                                  |

| 28 LDOBYP Bypass for On-Chip VCO LDO. Bypass to ground with a 0.47µF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25         | TUNE         | PLL Charge-Pump Output and TUNE Input. Connect to the PLL loop filter.                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 28         | LDOBYP       | Bypass for On-Chip VCO LDO. Bypass to ground with a 0.47µF capacitor.                                                                                                                                            |

#### **Pin Description (continued)**

| PIN | NAME     | FUNCTION                                                                                                 |

|-----|----------|----------------------------------------------------------------------------------------------------------|

| PIN | INAIVIE  | FONCTION                                                                                                 |

| 30  | TFVL1*   | VHF Low Tracking Filter 1                                                                                |

| 31  | TFVL2*   | VHF Low Tracking Filter 2                                                                                |

| 32  | TFVH1*   | VHF High Tracking Filter 1                                                                               |

| 33  | TFVH2*   | VHF High Tracking Filter 2                                                                               |

| 34  | TFU1*    | UHF Tracking Filter 1                                                                                    |

| 35  | TFU2A*   | UHF Tracking Filter 2A                                                                                   |

| 36  | TFU2B*   | UHF Tracking Filter 2B                                                                                   |

| 37  | TFU3*    | UHF Tracking Filter 3                                                                                    |

| 38  | LEXT*    | RF VGA Supply Voltage. Connect through a 270nH pullup inductor to V <sub>CC</sub> .                      |

| 40  | RFINL    | Low-Frequency RF Input. Matched to $75\Omega$ over the operating band. Requires a DC-blocking capacitor. |

| _   | EP (GND) | Exposed Paddle Ground. Solder evenly to the PCB ground plane for proper operation.                       |

\*Improper placement of these inductors degrades image rejection, gain, and noise figure. Copy Maxim reference design layout exactly in this area.

#### \_Detailed Description

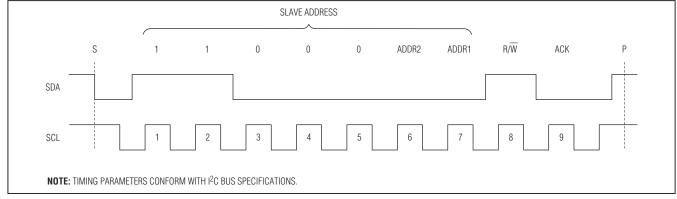

#### **I<sup>2</sup>C-Compatible Serial Interface**

The MAX3543 uses a 2-wire I<sup>2</sup>C-compatible serial interface consisting of a serial data line (SDA) and a serial clock line (SCL). SDA and SCL facilitate bidirectional communication between the MAX3543 and the master at clock frequencies up to 400kHz. The master initiates a data transfer on the bus and generates the SCL signal to permit data transfer. The MAX3543 behaves as a slave device that transfers and receives data to and from the master. Pull SDA and SCL high with external pullup resistors for proper bus operation.

One bit is transferred during each SCL clock cycle. A minimum of nine clock cycles is required to transfer a byte in or out of the MAX3543 (8 data bits and an ACK/ NACK). The data on SDA must remain stable during the high period of the SCL clock pulse. Changes in SDA while SCL is high and stable are considered control signals (see the *START* and *STOP Conditions* section). Both SDA and SCL remain high when the bus is not busy.

#### START and STOP Conditions

The master initiates a transmission with a START condition (S), which is a high-to-low transition on SDA while SCL is high. The master terminates a transmission with a STOP condition (P), which is a low-to-high transition on SDA while SCL is high.

#### Acknowledge and Not-Acknowledge Conditions

Data transfers are framed with an acknowledge bit (ACK) or a not-acknowledge bit (NACK). Both the master and the MAX3543 (slave) generate acknowledge bits. To generate an acknowledge, the receiving device must pull SDA low before the rising edge of the acknowledge-related clock pulse (ninth pulse) and keep it low during the high period of the clock pulse.

To generate a not-acknowledge condition, the receiver allows SDA to be pulled high before the rising edge of the acknowledge-related clock pulse, and leaves SDA high during the high period of the clock pulse. Monitoring the acknowledge bits allows for detection of unsuccessful data transfers. An unsuccessful data transfer happens if a receiving device is busy or if a system fault has occurred. In the event of an unsuccessful data transfer, the bus master must reattempt communication at a later time.

#### Slave Address

The MAX3543 has a 7-bit slave address plus one R/W bit. These 8 bits must be sent to the device following a START condition to initiate communication. The slave address is determined by the state of the ADDR pin as shown in Table 2.

#### **Table 2. Address Configurations**

| ADDR PIN    | ADDR2 | ADDR1 | WRITE<br>ADDRESS | READ<br>ADDRESS |

|-------------|-------|-------|------------------|-----------------|

| 0           | 0     | 0     | 0xC0             | 0xC1            |

| Unconnected | 0     | 1     | 0xC2             | 0xC3            |

| 1           | 1     | 0     | 0xC4             | 0xC5            |

Figure 1. MAX3543 Slave Address Byte. Example shows read address 0x0C1 (ADDR pin grounded).

The MAX3543 continuously awaits a START condition followed by its slave address. When the device recognizes its slave address, it acknowledges by pulling the SDA line low for one clock period; it is ready to accept or send data depending on the  $R/\overline{W}$  bit (Figure 1).

#### Write Cycle

When addressed with a write command, the MAX3543 allows the master to write to a single register or to multiple successive registers.

A write cycle begins with the bus master issuing a START condition followed by the 7 slave address bits and a write bit ( $R/\overline{W} = 0$ ). The MAX3543 issues an ACK if the slave address byte is successfully received. The bus master must then send to the slave the address of the first register it wishes to write to. If the slave acknowledges the address, the master can then write 1 byte to the register at the specified address. Data is written beginning with the most significant bit. The MAX3543 again issues an ACK if the data is successfully written to the register. The master can continue to write data to the successive internal registers with the MAX3543 acknowledging each successful transfer, or it can terminate transmission by issuing a STOP condition. The write cycle does not terminate until the master issues a STOP condition.

Figure 2 illustrates an example in which registers 0, 1, and 2 are written with 0x0E, 0xD8, and 0xE1, respectively.

#### Read Cycle

MAX3543

A read cycle begins with the bus master issuing a START condition followed by the 7 slave address bits and a write bit (R/W = 0). The MAX3543 issues an ACK if the slave address byte is successfully received. The master then sends the 8-bit address of the first register that it wishes to read. The MAX3543 then issues another ACK. Next, the master must issue a START condition followed by the 7 slave address bits and a read bit (R/W = 1). The MAX3543 issues an ACK if it successfully recognizes its address and begins sending data from the specified register address starting with the most significant bit (MSB). Data is clocked out of the MAX3543 on the rising edge of SCL. On the ninth rising edge of SCL, the master can issue an ACK and continue reading successive registers or it can issue a NACK followed by a STOP condition to terminate transmission. The read cycle does not terminate until the master issues a STOP condition. Figure 3 illustrates an example in which registers 0 and 1 are read back.

| START | WRITE DEVICE<br>ADDRESS | R/W | ACK | WRITE REGISTER<br>ADDRESS | ACK | WRITE DATA TO<br>REGISTER 0x00 | ACK | WRITE DATA TO<br>REGISTER 0x01 | ACK | WRITE DATA TO<br>REGISTER 0x02 | ACK | STOP |

|-------|-------------------------|-----|-----|---------------------------|-----|--------------------------------|-----|--------------------------------|-----|--------------------------------|-----|------|

| Onati | 11000[ADDR2][ADDR1]     | 0   | —   | 0x00                      | —   | 0x0E                           | —   | 0xD8                           | —   | 0xE1                           |     | 0101 |

Figure 2. Example: Write registers 0, 1, and 2 with 0x0E, 0xD8, and 0xE1, respectively.

| START | WRITE DEVICE<br>ADDRESS | R/W | ACK | WRITE 1ST REGISTER<br>ADDRESS | ACK | START | WRITE DEVICE<br>ADDRESS | R/W | ACK | READ DATA<br>REG 0 | ACK | READ DATA<br>REG 1 | NACK | STOP |

|-------|-------------------------|-----|-----|-------------------------------|-----|-------|-------------------------|-----|-----|--------------------|-----|--------------------|------|------|

|       | 110000[ADDR2][ADDR1]    | 0   | —   | 0x00                          | _   |       | 110000[ADDR2][ADDR1]    | 1   | —   | D7-D0              | —   | D7-D0              | _    |      |

Figure 3. Example: Read data from registers 0 and 1.

####

#### **Control Register Description**

The MAX3543 includes 18 programmable registers, two status registers (read only), one register for ROM readback (read only), and one for Maxim use only. The programmable registers configure the VCO settings, PLL settings, detector and AGC settings, state control, bias adjustments, individual block shutdown, and the tracking filter frequency. These programmable registers are also readable. The read-only registers include two status registers and a ROM table data register.

Typical bit settings are provided only for user convenience and are not guaranteed at power-up. All registers must be written no earlier than 100µs after power-up or recovery from a brownout event (i.e., when V<sub>CC</sub> drops below 1V) to initialize the registers. Then follow up by rewriting the registers needed for channel/frequency programming (i.e., registers R00–R04). The typical values listed in Table 3 configure the MAX3543 for DTV reception with 16MHz crystal, 8MHz channel BW, 36.15MHz IF center frequency, differential LC bandpass filter, and 666MHz RF center frequency.

| REG  | REG  | REGISTER                    | TYPICAL | MSB       |        |           | BIT LOC | ATION  |        |           | LSB    |

|------|------|-----------------------------|---------|-----------|--------|-----------|---------|--------|--------|-----------|--------|

| ADDR | NAME | FUNCTION                    | SETTING | 7         | 6      | 5         | 4       | 3      | 2      | 1         | 0      |

| 0x00 | R00  | VCO                         | 4C      | VCO       | [1:0]  |           | VSUE    | 3[3:0] |        | VDIV      | /[1:0] |

| 0x01 | R01  | NDIV INT                    | 2B      | NINT[7:0] |        |           |         |        |        |           |        |

| 0x02 | R02  | NDIV FRAC2                  | 8E      | CPS       | CP     | RDIV      | [1:0]   |        | F[19   | 9:16]     |        |

| 0x03 | R03  | NDIV FRAC1                  | 26      |           |        |           | F[1     | 5:8]   |        |           |        |

| 0x04 | R04  | NDIV FRAC0<br>(VAS Trigger) | 66      | F[7:0]    |        |           |         |        |        |           |        |

| 0x05 | R05  | MODE CTRL                   | D8      | LNA2G     | RFIN   | RFLPF     | CHBW    | TFB    | [1:0]  | IFSEI     | _[1:0] |

| 0x06 | R06  | TFS                         | 30      |           |        |           | TFS     | [7:0]  |        |           |        |

| 0x07 | R07  | TFP                         | 12      | —         | —      |           |         | TFP    | [5:0]  |           |        |

| 0x08 | R08  | SHUTDOWN                    | 00      | STBY      | SDRF   | SDMIX     | SDIF    | SDIFVG | SDPD   | SDSYN     | SDVCO  |

| 0x09 | R09  | REF CONFIG                  | 0A      | —         | —      | —         | CPLI    | V[1:0] | ALC    | [1:0]     | XODIV  |

| 0x0A | R0A  | VAS CONFIG                  | 17      | LFDI      | V[1:0] | VASS      | VAS     | ADL    | ADE    | LTC       | [1:0]  |

| 0x0B | R0B  | PWRDET CFG1                 | 43      | DWPD      |        | WPDA[2:0] |         | DNPD   |        | NPDA[2:0] |        |

| 0x0C | ROC  | PWRDET CFG2                 | 01      |           |        | —         | _       |        | PULLUP | RFIF      | D[1:0] |

| 0x0D | ROD  | FILT CF ADJ                 | ROM     |           | —      |           |         | CFSE   | T[5:0] |           |        |

| 0x0E | ROE  | ROM ADDR                    | 00      |           |        | —         | _       |        | ROM    | A[3:0]    |        |

| 0x0F | ROF  | IRHR                        | ROM     |           |        |           | IRHF    | ?[7:0] |        |           |        |

| 0x10 | R10  | ROM READBACK                | RO      |           |        |           | ROM     | R[7:0] |        |           |        |

| 0x11 | R11  | VAS STATUS                  | RO      | VVCC      | D[1:0] |           | VVSE    | 3[3:0] |        | VASA      | VASE   |

| 0x12 | R12  | GEN STATUS                  | RO      | —         | —      | VCP       | TRIM    | POR    | V      | COADC[2:  | 0]     |

| 0x13 | R13  | BIAS ADJ                    | 56      |           | MIXGM  | LNA2      | B[1:0]  | MIXE   | 3[1:0] | FILTB     | IFVGAB |

| 0x14 | R14  | TEST1                       | 40      |           |        |           | RESE    | RVED   |        |           |        |

| 0x15 | R15  | ROM WRITE DATA              | 00      |           |        |           | ROM     | N[7:0] |        |           |        |

#### Table 3. Register Configuration

**Note:** Registers should be written in the order of ascending addresses. When changing frequency, write R00 to R07 in order of ascending addresses to ensure proper VCO setup.

#### **Register and Bit Descriptions**

### Table 4. R00: VCO Register—VCO and LO Divider Control (Address: 00h)