# MC10133

# **Quad Latch**

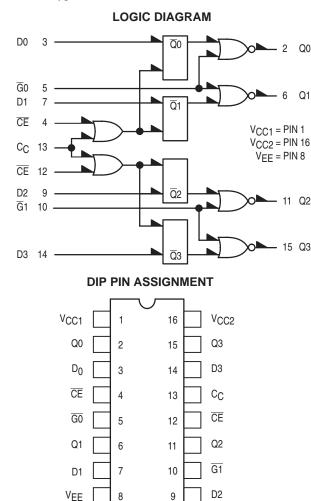

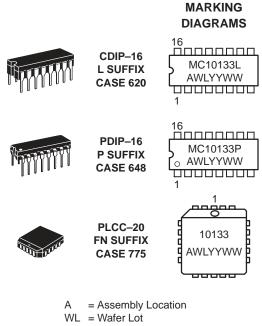

The MC10133 is a high speed, low power, quad latch consisting of four bistable latch circuits with D type inputs and gated Q outputs, allowing direct wiring to a bus. When the clock is high, outputs will follow D inputs. Information is latched on the negative going transition of the clock.

The outputs are gated when the output enable  $(\overline{G})$  is low. All four latches may be clocked at one time with the common clock (C<sub>C</sub>), or each half may be clocked separately with its clock enable ( $\overline{CE}$ ).

- P<sub>D</sub>=310 mW typ/pkg (No Load)

- $t_{pd}$ = 4.0 ns typ

- $t_r$ ,  $t_f = 2.0$  ns typ (20%-80%)

### **ON Semiconductor**

http://onsemi.com

YY = Year

| WW = Work V | Veek |

|-------------|------|

|-------------|------|

| G | С | D | Q <sub>n+1</sub> |

|---|---|---|------------------|

| Н | Х | Х | L                |

| L | L | Х | Qn               |

| L | Н | L | L                |

| L | Н | Н | Н                |

C = CC = CE

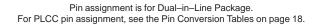

#### **ORDERING INFORMATION**

| Device    | Package | Shipping        |

|-----------|---------|-----------------|

| MC10133L  | CDIP-16 | 25 Units / Rail |

| MC10133P  | PDIP-16 | 25 Units / Rail |

| MC10133FN | PLCC-20 | 46 Units / Rail |

### ELECTRICAL CHARACTERISTICS

|                            | Symbol                                                                                                 | Pin<br>Under<br>Test                        | Test Limits                                                                  |                                                                    |                                                                              |                                 |                                                          |                                                                              |                                                                    |      |

|----------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------|------|

|                            |                                                                                                        |                                             | –30°C                                                                        |                                                                    | +25°C                                                                        |                                 |                                                          | +85°C                                                                        |                                                                    | 1    |

| Characteristic             |                                                                                                        |                                             | Min                                                                          | Max                                                                | Min                                                                          | Тур                             | Max                                                      | Min                                                                          | Max                                                                | Unit |

| Power Supply Drain Current | ΙE                                                                                                     | 8                                           |                                                                              | 82                                                                 |                                                                              |                                 | 75                                                       |                                                                              | 82                                                                 | mAdd |

| Input Current              | linH                                                                                                   | 3<br>4<br>5<br>13                           |                                                                              | 390<br>425<br>560<br>560                                           |                                                                              |                                 | 245<br>265<br>350<br>350                                 |                                                                              | 245<br>265<br>350<br>350                                           | μAdc |

|                            | l <sub>inL</sub>                                                                                       | 3                                           | 0.5                                                                          |                                                                    | 0.5                                                                          |                                 |                                                          | 0.3                                                                          |                                                                    | μAdc |

| Output Voltage Logic 1     | VOH                                                                                                    | 2<br>2                                      | -1.060<br>-1.060                                                             | -0.890<br>-0.890                                                   | -0.960<br>-0.960                                                             |                                 | -0.810<br>-0.810                                         | -0.890<br>-0.890                                                             | -0.700<br>-0.700                                                   | Vdc  |

| Output Voltage Logic 0     | V <sub>OL</sub>                                                                                        | 2<br>2<br>2                                 | -1.890<br>-1.890<br>-1.890                                                   | -1.675<br>-1.675<br>-1.675                                         | -1.850<br>-1.850<br>-1.850                                                   |                                 | -1.650<br>-1.650<br>-1.650                               | -1.825<br>-1.825<br>-1.825                                                   | -1.615<br>-1.615<br>-1.615                                         | Vdc  |

| Threshold Voltage Logic 1  | Voha                                                                                                   | 2<br>2<br>2†<br>2‡<br>2<br>2<br>2<br>2<br>2 | -1.080<br>-1.080<br>-1.080<br>-1.080<br>-1.080<br>-1.080<br>-1.080<br>-1.080 |                                                                    | -0.980<br>-0.980<br>-0.980<br>-0.980<br>-0.980<br>-0.980<br>-0.980<br>-0.980 |                                 |                                                          | -0.910<br>-0.910<br>-0.910<br>-0.910<br>-0.910<br>-0.910<br>-0.910<br>-0.910 |                                                                    | Vdc  |

| Threshold Voltage Logic 0  | V <sub>OLA</sub>                                                                                       | 2<br>2<br>2†<br>2‡<br>2‡                    |                                                                              | -1.655<br>-1.655<br>-1.655<br>-1.655<br>-1.655<br>-1.655<br>-1.655 |                                                                              |                                 | -1.630<br>-1.630<br>-1.630<br>-1.630<br>-1.630<br>-1.630 |                                                                              | -1.595<br>-1.595<br>-1.595<br>-1.595<br>-1.595<br>-1.595<br>-1.595 | Vdc  |

| Switching Times (50Ω Load) |                                                                                                        |                                             |                                                                              |                                                                    |                                                                              |                                 |                                                          |                                                                              |                                                                    | ns   |

| Propagation Delay          | <sup>t</sup> 3+2+<br><sup>t</sup> 4+2+<br><sup>t</sup> 5–2+<br><sup>t</sup> setup<br><sup>t</sup> hold | 2<br>2<br>3<br>3                            | 1.0<br>1.0<br>1.0<br>2.5<br>1.5                                              | 5.6<br>5.4<br>3.2                                                  | 1.0<br>1.0<br>2.5<br>1.5                                                     | 4.0<br>4.0<br>2.0<br>0.7<br>0.7 | 5.4<br>5.4<br>3.1                                        | 1.1<br>1.2<br>1.0<br>2.5<br>1.5                                              | 5.9<br>6.0<br>3.4                                                  |      |

| Rise Time (20 to 80%)      | t2+                                                                                                    | 2                                           | 1.0                                                                          | 3.6                                                                | 1.1                                                                          | 2.0                             | 3.5                                                      | 1.1                                                                          | 3.8                                                                |      |

| Fall Time (20 to 80%)      | t2-                                                                                                    | 2                                           | 1.0                                                                          | 3.6                                                                | 1.1                                                                          | 2.0                             | 3.5                                                      | 1.1                                                                          | 3.8                                                                |      |

$\dagger$  Output level to be measured after a clock pulse has been applied to the clock input (Pin 4)

· — V<sub>IHmax</sub> · — V<sub>ILmin</sub>

‡ Data input at proper high/low level while clock pulse is high so that device latches ar proper high/low level for test. Levels are measured after device has latched.

\* Latch set to zero state before test.

## MC10133

#### ELECTRICAL CHARACTERISTICS (continued)

|                      |             |                                         |               | TEST VOLTAGE VALUES (Volts)               |        |          |           |                 |                |

|----------------------|-------------|-----------------------------------------|---------------|-------------------------------------------|--------|----------|-----------|-----------------|----------------|

|                      |             | @ Test Te                               | mperature     | V <sub>IHmax</sub>                        | VILmin | VIHAmin  | VILAmax   | V <sub>EE</sub> |                |

|                      |             | <b>−30°C</b>                            |               | -0.890                                    | -1.890 | -1.205   | -1.500    | -5.2            | 1              |

|                      |             |                                         | +25°C         | -0.810                                    | -1.850 | -1.105   | -1.475    | -5.2            | 1              |

|                      |             |                                         | +85°C         | -0.700                                    | -1.825 | -1.035   | -1.440    | -5.2            |                |

|                      |             |                                         | Pin           | TEST VOLTAGE APPLIED TO PINS LISTED BELOW |        |          |           |                 |                |

| Characteristic       |             | Symbol                                  | Under<br>Test | V <sub>IHmax</sub>                        | VILmin | VIHAmin  | VILAmax   | VEE             | (VCC)<br>Gnd   |

| Power Supply Drain ( | Current     | ١E                                      | 8             |                                           | 13     |          |           | 8               | 1, 16          |

| Input Current        |             | l <sub>inH</sub>                        | 3             | 3                                         |        |          |           | 8               | 1, 16          |

|                      |             |                                         | 4             | 4                                         |        |          |           | 8               | 1, 16          |

|                      |             |                                         | 5<br>13       | 5<br>13                                   |        |          |           | 8<br>8          | 1, 16<br>1, 16 |

|                      |             |                                         | 3             | 15                                        | 3      |          |           | 8               |                |

| <b>0</b>             |             | l <sub>inL</sub>                        |               |                                           | 3      |          |           |                 | 1, 16          |

| Output Voltage       | Logic 1     | VOH                                     | 2<br>2        | 3, 4<br>3, 13                             |        |          |           | 8<br>8          | 1, 16<br>1, 16 |

| Output Voltage       | Logic 0     | VOL                                     | 2             | 13                                        | 3      |          |           | 8               | 1, 16          |

|                      |             |                                         | 2             | 3, 5, 13                                  |        |          |           | 8               | 1, 16          |

|                      |             |                                         | 2             | 4                                         | 3      |          |           | 8               | 1, 16          |

| Threshold Voltage    | Logic 1     | Vона                                    | 2             | 3, 4                                      |        | 3        | 5         | 8               | 1, 16          |

|                      |             |                                         | 2<br>2        | 4<br>3, 4                                 |        | 3        |           | 8<br>8          | 1, 16<br>1, 16 |

|                      |             |                                         | 2†            | 3                                         |        |          |           | 8               | 1, 16          |

|                      |             |                                         | 2‡            |                                           |        |          |           | 8               | 1, 16          |

|                      |             |                                         | 2‡            |                                           |        |          | 4         | 8               | 1, 16          |

|                      |             |                                         | 2             | 3                                         |        | 4        |           | 8               | 1, 16          |

|                      |             |                                         | 2             | 3                                         |        | 13       |           | 8               | 1, 16          |

| Threshold Voltage    | Logic 0     | VOLA                                    | 2             | 3, 4                                      |        | 5        | 2         | 8               | 1, 16          |

|                      |             |                                         | 2<br>2        | 4<br>4                                    |        |          | 3         | 8<br>8          | 1, 16<br>1, 16 |

|                      |             |                                         | 2†            | -                                         |        |          |           | 8               | 1, 16          |

|                      |             |                                         | 2‡            | 3                                         |        |          |           | 8               | 1, 16          |

|                      |             |                                         | 2‡            | 3                                         |        |          | 13        | 8               | 1, 16          |

| Switching Times      | (50Ω Load)  |                                         |               | +1.11V                                    |        | Pulse In | Pulse Out | –3.2 V          | +2.0           |

| Propagation Delay    |             | t3+2+                                   | 2             | 4                                         |        | 3        | 2         | 8               | 1, 16          |

|                      |             | t4+2+                                   | 2             | 3*                                        |        | 4        | 2         | 8               | 1, 16          |

|                      |             | t <sub>5-2+</sub>                       | 2<br>3        |                                           |        | 5<br>3   | 2<br>2    | 8<br>8          | 1, 16<br>1, 16 |

|                      |             | <sup>t</sup> setup<br><sup>t</sup> hold | 3             |                                           |        | 3        | 2         | 8               | 1, 10          |

| Rise Time            | (20 to 80%) | t <sub>2+</sub>                         | 2             | 4                                         |        | 3        | 2         | 8               | 1, 16          |

| Fall Time            | (20 to 80%) | t2-                                     | 2             | 4                                         |        | 3        | 2         | 8               | 1, 16          |

<sup>†</sup>Output level to be measured after a clock pulse has been applied to the clock input (Pin 4)

----- V<sub>IHmax</sub> · ---- V<sub>ILmin</sub>

Data input at proper high/low level while clock pulse is high so that device latches ar proper high/low level for test. Levels are measured after device has latched.

\* Latch set to zero state before test.

Each MECL 10,000 series circuit has been designed to meet the dc specifications shown in the test table, after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse air flow greater than 500 linear fpm is maintained. Outputs are terminated through a 50–ohm resistor to –2.0 volts. Test procedures are shown for only one gate. The other gates are tested in the same manner.