EVALUATION KIT **AVAILABLE**

# 2.488Gbps/2.667Gbps Clock and **Data Recovery with Limiting Amplifier**

### **General Description**

The MAX3874 is a compact, dual-rate clock and data recovery with limiting amplifier for OC-48 and OC-48 with FEC SONET/SDH applications. Without using an external reference clock, the fully integrated phaselocked loop (PLL) recovers a synchronous clock signal from the serial NRZ data input. The input data is then retimed by this recovered clock, providing a clean data output. An additional serial input (SLBI±) is available for system-loopback diagnostic testing. Alternatively, this input can be connected to a reference clock to maintain a valid clock output in the absence of data transitions. The device also includes a loss-of-lock (LOL) output.

The MAX3874 contains a vertical threshold control to compensate for optical noise due to EDFAs in DWDM transmission systems. The recovered data and clock outputs are CML with on-chip  $50\Omega$  back termination on each line. Its jitter performance exceeds all SONET/ SDH specifications. The MAX3874A is the MAX3874 with a voltage-controlled oscillator (VCO) centered at 2.0212GHz.

The MAX3874 operates from a single +3.3V supply and typically consumes 580mW. It is available in a 5mm x 5mm 32-pin QFN with exposed pad package and operates over the -40°C to +85°C temperature range.

## **Applications**

SONET/SDH Receivers and Regenerators Add/Drop Multiplexers Digital Cross-Connects SONET/SDH Test Equipment **DWDM Transmission Systems** Access Networks

#### **Features**

- ♦ 2.488Gbps and 2.667Gbps Input Data Rates

- **♦** Reference Clock Not Required for Data Acquisition

- ◆ Exceeds ANSI, ITU, and Bellcore SONET/SDH **Jitter Specifications**

- ♦ 2.7mUIRMS Clock Jitter Generation

- ♦ 10mV<sub>P-P</sub> Input Sensitivity Without Threshold **Adjust**

- ♦ 0.65Ulp-p High-Frequency Jitter Tolerance

- ♦ ±170mV Wide Input Threshold Adjust Range

- **Clock Holdover Capability Using Frequency-**Selectable Reference Clock

- ♦ Serial Loopback Input Available for System Diagnostic Testing

- ♦ Loss-of-Lock (LOL) Indicator

- ♦ Small 5mm × 5mm 32-Pin QFN Package

### **Ordering Information**

| PART           | TEMP RANGE     | PIN-<br>PACKAGE | PKG<br>CODE |

|----------------|----------------|-----------------|-------------|

| MAX3874EGJ     | -40°C to +85°C | 32 QFN          | G3255-1     |

| MAX3874AEGJ**  | -40°C to +85°C | 32 QFN          | G3255-1     |

| MAX3874AETJ+** | -40°C to +85°C | 32 TQFN         | T3255-3     |

<sup>\*\*</sup>Contains a VCO centered at 2.0212GHz.

Pin Configuration appears at end of data sheet.

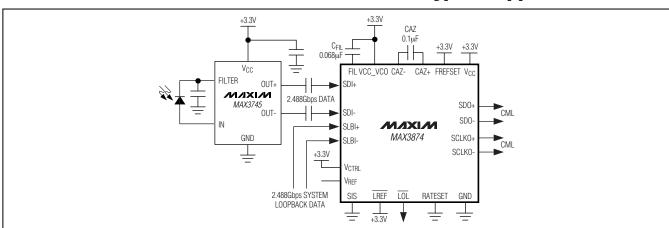

## **Typical Application Circuit**

NIXIN

<sup>+</sup>Denotes lead-free package.

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, V <sub>CC</sub> 0.5V to +5.0V                     |

|-------------------------------------------------------------------|

| Input Voltage Levels (SDI+, SDI-,                                 |

| SLBI+, SLBI-)(V <sub>CC</sub> - 1.0V) to (V <sub>CC</sub> + 0.5V) |

| Input Current Levels (SDI+, SDI-, SLBI+, SLBI-)±20mA              |

| CML Output Current (SDO+, SDO-, SCLKO+, SCLKO-) ±22mA             |

| Voltage at LOL, LREF, SIS, FIL, RATESET, FREFSET,                 |

| VCTRL, VREF, CAZ+, CAZ0.5V to (VCC + 0.5V)                        |

| Continuous Power Dissipation (T <sub>A</sub> = +85°C) |                |

|-------------------------------------------------------|----------------|

| 32-Pin QFN (derate 21.3mW/°C above +85°C)             | )1384mW        |

| Operating Junction Temperature Range5                 | 55°C to +150°C |

| Storage Temperature Range5                            | 55°C to +150°C |

| Processing Temperature (die)                          | +400°C         |

| Lead Temperature (soldering, 10s)                     | +300°C         |

|                                                       |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}. \text{ Typical values at } V_{CC} = +3.3 \text{V}, T_A = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.})$  (Note 1)

| PARAMETER                               | SYMBOL           | CONDITIONS                        | MIN                   | TYP                   | MAX                   | UNITS             |  |

|-----------------------------------------|------------------|-----------------------------------|-----------------------|-----------------------|-----------------------|-------------------|--|

| Supply Current                          | Icc              | (Note 2)                          |                       | 175                   | 215                   | mA                |  |

| INPUT SPECIFICATION (SDI±, SLBI±)       |                  |                                   |                       |                       |                       |                   |  |

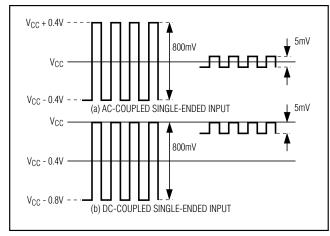

| Single-Ended Input Voltage<br>Range     | VIS              | Figure 1                          | V <sub>CC</sub> - 0.8 |                       | V <sub>CC</sub> + 0.4 | V                 |  |

| Input Common-Mode Voltage               |                  | Figure 1                          | V <sub>CC</sub> - 0.4 |                       | Vcc                   | V                 |  |

| Input Termination to V <sub>CC</sub>    | RIN              |                                   | 42.5                  | 50                    | 57.5                  | Ω                 |  |

| THRESHOLD-SETTING SPECIFIC              | CATION (SDI      | ±)                                | ·                     |                       |                       |                   |  |

| Differential Input Voltage Range (SDI±) |                  | Threshold adjust enabled          | 50                    |                       | 600                   | mV <sub>P-P</sub> |  |

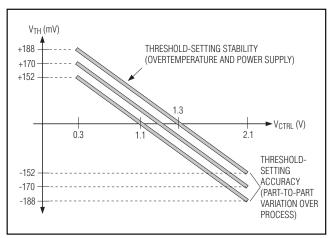

| Threshold Adjustment Range              | V <sub>TH</sub>  | Figure 2                          | -170                  |                       | +170                  | mV                |  |

| Threshold Control Voltage               | VCTRL            | Figure 2 (Note 3)                 | 0.3                   |                       | 2.1                   | V                 |  |

| Threshold Control Linearity             |                  |                                   |                       | ±5                    |                       | %                 |  |

| Threshold Setting Accuracy              |                  | Figure 2                          | -18                   |                       | +18                   | mV                |  |

| Throughold Cotting Ctability            |                  | 15mV ≤ IV <sub>TH</sub> I ≤ 80mV  | -6                    |                       | +6                    | /                 |  |

| Threshold Setting Stabiliity            |                  | 80mV < IV <sub>TH</sub> I ≤ 170mV | -12                   |                       | +12                   | mV                |  |

| Maximum Input Current                   | ICTRL            |                                   | -10                   |                       | +10                   | μΑ                |  |

| Reference Voltage Output                | V <sub>REF</sub> |                                   | 2.14                  | 2.2                   | 2.24                  | V                 |  |

| CML OUTPUT SPECIFICATION (              | SDO±, SCLK       | O±)                               |                       |                       |                       |                   |  |

| CML Differential Output<br>Impedance    | Ro               |                                   | 85                    | 100                   | 115                   | Ω                 |  |

| CML Output Common-Mode<br>Voltage       |                  | (Note 4)                          |                       | V <sub>CC</sub> - 0.2 |                       | V                 |  |

## DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}. \text{ Typical values at } V_{CC} = +3.3 \text{V}, T_A = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.})$  (Note 1)

| PARAMETER                                                      | SYMBOL          | CONDITIONS          | MIN | TYP | MAX | UNITS |

|----------------------------------------------------------------|-----------------|---------------------|-----|-----|-----|-------|

| LVTTL INPUT/OUTPUT SPECIFICATION (LOL, LREF, RATESET, FREFSET) |                 |                     |     |     |     |       |

| LVTTL Input High Voltage                                       | VIH             |                     | 2.0 |     |     | V     |

| LVTTL Input Low Voltage                                        | V <sub>IL</sub> |                     |     |     | 8.0 | V     |

| LVTTL Input Current                                            |                 |                     | -10 |     | +10 | μΑ    |

| LVTTL Output High Voltage                                      | VoH             | $I_{OH} = +20\mu A$ | 2.4 |     |     | V     |

| LVTTL Output Low Voltage                                       | V <sub>OL</sub> | $I_{OL} = -1mA$     |     | •   | 0.4 | V     |

**Note 1:** At -40°C, DC characteristics are guaranteed by design and characterization.

Note 2: CML outputs open.

Note 3: Voltage applied to V<sub>CTRL</sub> pin is from 0.3V to 2.1V when input threshold is adjusted from +170mV to -170mV.

**Note 4:**  $R_L = 50\Omega$  to  $V_{CC}$ .

#### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}. \text{ Typical values at } V_{CC} = +3.3 \text{V}, T_A = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.})$  (Note 5)

| PARAMETER                          | SYMBOL                          | CONDITIONS                                   | MIN  | TYP    | MAX  | UNITS              |  |

|------------------------------------|---------------------------------|----------------------------------------------|------|--------|------|--------------------|--|

|                                    |                                 | MAX3874 (RATESET = GND)                      |      | 2.488  |      |                    |  |

| Serial Input Data Rate             |                                 | MAX3874 (RATESET = VCC)                      |      | 2.667  | Gbps |                    |  |

|                                    |                                 | MAX3874A                                     |      | 2.0212 |      |                    |  |

| Differential Input Voltage (SDI±)  | V <sub>ID</sub>                 | Threshold adjust disabled, Figure 1 (Note 6) | 10   |        | 1600 | mV <sub>P-P</sub>  |  |

| Differential Input Voltage (SLBI±) |                                 | BER ≤ 10 <sup>-10</sup>                      | 50   |        | 800  | mV <sub>P-P</sub>  |  |

|                                    |                                 | MAX3874                                      |      | 1.5    | 2.0  |                    |  |

| Jitter Transfer Bandwidth          | J <sub>BW</sub>                 | MAX3874A                                     |      | 0.7    |      | MHz                |  |

| Jitter Peaking                     | JР                              | f ≤ J <sub>BW</sub>                          | ĺ    |        | 0.1  | dB                 |  |

|                                    |                                 | f = 100kHz                                   | 3.1  | 8.0    |      |                    |  |

| Sinusoidal Jitter Tolerance        |                                 | f = 1MHz                                     | 0.62 | 0.93   |      | Ul <sub>P-P</sub>  |  |

| (MAX3874)                          |                                 | f = 10MHz                                    | 0.44 | 0.65   |      |                    |  |

| Sinusoidal Jitter Tolerance        |                                 | f = 1MHz (Note 7)                            |      | >0.5   |      |                    |  |

| (MAX3874A)                         |                                 | f = 10MHz (Note 7)                           |      | >0.3   |      | Ulp-p              |  |

| Sinusoidal Jitter Tolerance with   |                                 | f = 100kHz                                   | İ    | 7.1    |      |                    |  |

| Threshold Adjust Enabled           |                                 | f = 1MHz                                     |      | 0.82   |      | Ulp-p              |  |

| (Note 8)                           |                                 | f = 10MHz                                    |      | 0.54   |      |                    |  |

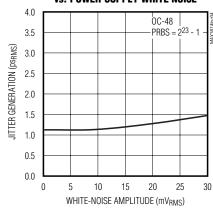

| Jitter Generation                  | JGEN                            | (Note 9)                                     |      | 2.7    | 4.0  | mUI <sub>RMS</sub> |  |

| Differential Input Return Loss     | -20log                          | 100kHz to 2.5GHz                             |      | 16     |      | ID                 |  |

| (SDI±, SLBI±)                      | I S <sub>11</sub> Ĭ             | 2.5GHz to 4GHz                               |      | 15     |      | dB                 |  |

| CML OUTPUT SPECIFICATION (S        | SDO±, SCL                       | (O±)                                         | •    |        |      |                    |  |

| Output Edge Speed                  | t <sub>r</sub> , t <sub>f</sub> | 20% to 80%                                   |      |        | 110  | ps                 |  |

| CML Output Differential Swing      |                                 | $R_L = 100\Omega$ differential               | 600  | 800    | 1000 | mV <sub>P-P</sub>  |  |

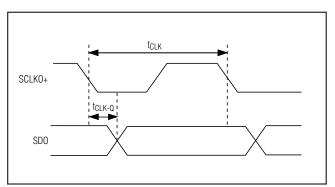

| Clock-to-Q Delay                   | tclk-Q                          | (Note 10)                                    | -40  |        | +40  | ps                 |  |

|                                    |                                 |                                              |      |        |      |                    |  |

### AC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}. \text{ Typical values at } V_{CC} = +3.3 \text{V}, T_A = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.})$  (Note 5)

| PARAMETER                                                | SYMBOL | CONDITIONS              | MIN | TYP     | MAX  | UNITS |

|----------------------------------------------------------|--------|-------------------------|-----|---------|------|-------|

| PLL ACQUISITION/LOCK SPECIFICATION                       |        |                         |     |         |      |       |

| Tolerated Consecutive Identical Digits                   |        | BER ≤ 10 <sup>-10</sup> |     | 2000    |      | Bits  |

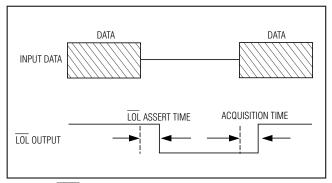

| Acquisition Time                                         |        | Figure 4 (Note 11)      |     |         | 1.0  | ms    |

| LOL Assert Time                                          |        | Figure 4                | 2.3 |         | 10.0 | μs    |

| Low-Frequency Cutoff for DC-<br>Offset Cancellation Loop |        | CAZ = 0.1µF             |     | 4       |      | kHz   |

| CLOCK HOLDOVER SPECIFICATION                             |        |                         |     |         |      |       |

| Reference Clock Frequency                                |        |                         |     | Table 4 |      |       |

| Maximum VCO Frequency Drift                              |        | (Note 12)               |     | •       | 400  | ppm   |

- **Note 5:** Minimum and maximum AC characteristics are guaranteed by design and characterization using the MAX3874. Specifications apply to the MAX3874A only when noted.

- Note 6: Jitter tolerance is guaranteed (BER ≤ 10<sup>-10</sup>) within this input voltage range. Input threshold adjust is disabled with V<sub>CTRL</sub> connected to V<sub>CC</sub>.

- Note 7: Measurements limited by equipment capability.

- Note 8: Measured using a 100mV<sub>P-P</sub> differential swing with a 20mVDC offset and an edge speed of 145ps (4th-order Bessel filter with f<sub>3dB</sub> = 1.8GHz).

- Note 9: Measured with 10mV<sub>P-P</sub> differential input, 2<sup>23</sup> 1 PRBS pattern at OC-48 with bandwidth from 12kHz to 20MHz.

- Note 10: Relative to the falling edge of the SCLKO+ (Figure 3).

- Note 11: Measured at OC-48 data rate using a 0.068µF loop filter capacitor initialized to +3.6V.

- Note 12: Measured at OC-48 data rate under LOL condition with the CDR clock output set by the external reference clock.

### **Timing Diagrams**

Figure 1. Definition of Input Voltage Swing

Figure 2. Relationship Between Control Voltage and Threshold Voltage

## **Timing Diagrams (continued)**

Figure 3. Definition of Clock-to-Q Delay

Figure 4. LOL Assert Time and PLL Acquisition Time Measurement

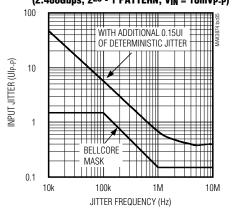

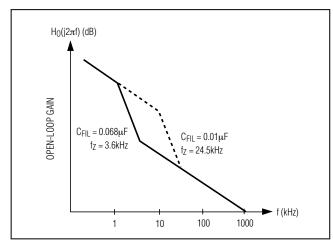

### **Typical Operating Characteristics**

$(V_{CC} = +3.3V, T_A = +25^{\circ}C, unless otherwise noted.)$

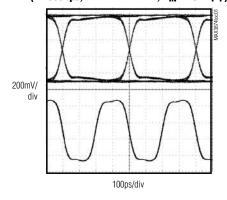

# RECOVERED CLOCK AND DATA (2.488Gbps, $2^{23}$ - 1 Pattern, $V_{IN}$ = 10m $V_{P-P}$ )

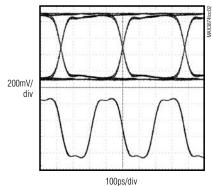

# RECOVERED CLOCK AND DATA (2.67Gbps, 2<sup>23</sup> - 1 Pattern, V<sub>IN</sub> = 10mV<sub>P-P</sub>)

# RECOVERED CLOCK JITTER (2.488Gbps)

TOTAL WIDEBAND RMS JITTER = 1.60ps PEAK-TO-PEAK JITTER = 12.20ps

# JITTER GENERATION vs. POWER-SUPPLY WHITE NOISE

####

### Typical Operating Characteristics (continued)

$(V_{CC} = +3.3V, T_A = +25^{\circ}C, unless otherwise noted.)$

# Pin Description

| PIN                   | NAME             | FUNCTION                                                                                                             |

|-----------------------|------------------|----------------------------------------------------------------------------------------------------------------------|

| 1, 4, 27              | Vcc              | +3.3V Supply Voltage                                                                                                 |

| 2                     | SDI+             | Positive Serial Data Input, CML                                                                                      |

| 3                     | SDI-             | Negative Serial Data Input, CML                                                                                      |

| 5                     | SLBI+            | Positive System Loopback Input or Reference Clock Input, CML                                                         |

| 6                     | SLBI-            | Negative System Loopback Input or Reference Clock Input, CML                                                         |

| 7                     | SIS              | Signal Selection Input, LVTTL. Set low for normal operation, set high for system loopback.                           |

| 8                     | TREF             | Lock-to-Reference Clock Input, LVTTL. Set high for PLL lock to serial data, set low for PLL lock to reference clock. |

| 9                     | LOL              | Loss-of-Lock Output, LVTTL. Active low.                                                                              |

| 10, 11, 16,<br>25, 32 | GND              | Supply Ground                                                                                                        |

| 12                    | FIL              | PLL Loop-Filter Capacitor Input. Connect a 0.068µF capacitor between FIL and VCC_VCO.                                |

| 13, 18                | VCC_VCO          | +3.3V Supply Voltage for the VCO                                                                                     |

| 14, 15                | N.C.             | Not Connected                                                                                                        |

| 17                    | RATESET          | VCO Frequency Select Input, LVTTL (Tables 2, 3, and 4)                                                               |

| 19                    | SCLKO-           | Negative Serial Clock Output, CML                                                                                    |

| 20                    | SCLKO+           | Positive Serial Clock Output, CML                                                                                    |

| 21, 24                | VCC_OUT          | Supply Voltage for the CML Outputs                                                                                   |

| 22                    | SDO-             | Negative Serial Data Output, CML                                                                                     |

| 23                    | SDO+             | Positive Serial Data Output, CML                                                                                     |

| 26                    | FREFSET          | Reference Clock Frequency Select Input, LVTTL (Tables 2, 3, and 4)                                                   |

| 28                    | CAZ+             | Positive Capacitor Input for DC-Offset Cancellation Loop. Connect a 0.1µF capacitor between CAZ+ and CAZ             |

| 29                    | CAZ-             | Negative Capacitor Input for DC-Offset Cancellation Loop. Connect a 0.1µF capacitor between CAZ+ and CAZ             |

| 30                    | V <sub>REF</sub> | +2.2V Bandgap Reference Voltage Output. Optionally used for threshold adjustment.                                    |

| 31                    | VCTRL            | Analog Control Input for Threshold Adjustment. Connect to VCC to disable threshold adjust.                           |

| EP                    | Exposed<br>Pad   | Ground. The exposed pad must be soldered to the circuit board ground for proper thermal and electrical performance.  |

### **Detailed Description**

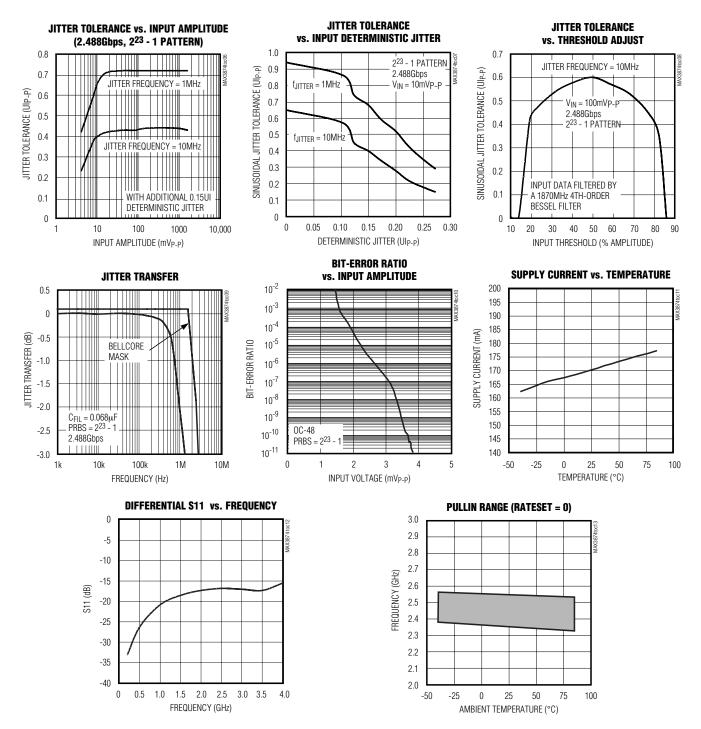

The MAX3874 consists of a fully integrated PLL limiting amplifier with threshold adjust, DC-offset cancellation loop, data retiming block, and CML output buffers (Figure 5). The PLL consists of a phase/frequency detector, a loop filter, and a VCO.

This device is designed to deliver the best combination of jitter performance and power dissipation by using a fully differential signal architecture and low-noise design techniques.

#### **SDI Input Amplifier**

The SDI inputs of the MAX3874 accept serial NRZ data with a differential input amplitude from 10mV<sub>P-P</sub> to 1600mV<sub>P-P</sub>. The input sensitivity is 10mV<sub>P-P</sub>, at which the jitter tolerance is met for a BER of 10<sup>-10</sup> with threshold adjust disabled. The input sensitivity can be as low as 4mV<sub>P-P</sub> and still maintain a BER of 10<sup>-10</sup>. The MAX3874 inputs are designed to directly interface with a transimpedance amplifier such as the MAX3745.

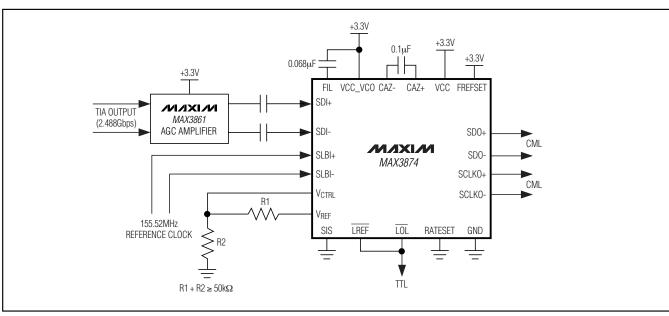

For applications in which vertical threshold adjustment is needed, the MAX3874 can be connected to the output of an AGC amplifier such as the MAX3861. When using the threshold adjust, the input voltage range is 50mV<sub>P-P</sub> to 600mV<sub>P-P</sub> (see the *Design Procedure* section).

#### **SLBI Input Amplifier**

The SLBI input amplifier accepts either NRZ loopback data or a reference clock signal. This amplifier can accept a differential input amplitude from 50mV<sub>P-P</sub> to 800mV<sub>P-P</sub>.

#### **Phase Detector**

The phase detector incorporated in the MAX3874 produces a voltage proportional to the phase difference between the incoming data and the internal clock. Because of its feedback nature, the PLL drives the error voltage to zero, aligning the recovered clock to the center of the incoming data eye for retiming.

#### **Frequency Detector**

The digital frequency detector (FD) acquires frequency lock without the use of an external reference clock. The frequency difference between the received data and the VCO clock is derived by sampling the in-phase and quadrature VCO outputs on both edges of the data-input signal. Depending on the polarity of the frequency difference, the FD drives the VCO until the frequency difference is reduced to zero. Once frequency acquisition is complete, the FD returns to a neutral state. False locking is eliminated by this digital frequency detector.

Figure 5. Functional Diagram

#### **Loop Filter and VCO**

The phase detector and frequency detector outputs are summed into the loop filter. An external capacitor (C<sub>FIL</sub>) connected from FIL to VCC\_VCO is required to set the PLL damping ratio. Note that the PLL jitter bandwidth does not change as the external capacitor changes, but the jitter peaking, acquisition time, and loop stability are affected. See the *Design Procedure* section for guidelines on selecting this capacitor.

The loop filter output controls the two on-chip VCOs. The VCOs provide low phase noise and are trimmed to the 2.488GHz and 2.667GHz frequencies. (The MAX3874A uses a single VCO trimmed to 2.0212GHz.) The RATESET pin is used to select the appropriate VCO. See Tables 2, 3, and 4 for the proper settings.

#### **Loss-of-Lock Monitor**

The  $\overline{\text{LOL}}$  output indicates a PLL lock failure due to excessive jitter present at the data input or due to loss of input data. The  $\overline{\text{LOL}}$  output is asserted low when the PLL loses lock.

#### **DC-Offset Cancellation Loop**

A DC-offset cancellation loop is implemented to remove the DC offset of the limiting amplifier. To minimize the low-frequency pattern-dependent jitter associated with this DC-cancellation loop, the low-frequency cutoff is 10kHz (typ) with CAZ =  $0.1\mu F$ , connected from CAZ+ to CAZ-. The DC-offset cancellation loop operates only when threshold adjust is disabled.

### **Design Procedure**

#### **Decision Threshold Adjust**

In applications in which the noise density is not balanced between logical zeros and ones (i.e., optical amplification using EDFA amplifiers), lower bit-error ratios (BERs) can be achieved by adjusting the input threshold. Varying the voltage at VCTRL from +0.3V to +2.1V achieves a vertical decision threshold adjustment of +170mV to -170mV, respectively (Figure 2). Use the provided bandgap reference voltage output (VREF) with a voltage-divider circuit or the output of a DAC to set the voltage at VCTRL. See Figure 10 when using VREF to generate the voltage for VCTRL (Figure 10). If threshold adjust is not required, disable it by connecting VCTRL directly to VCC and leave VREF floating.

#### **Modes of Operation**

The MAX3874 has three operational modes controlled by the LREF and SIS inputs: normal, system loopback, and clock holdover. Normal operation mode requires a serial data stream at the SDI± inputs, system loopback mode requires a serial data stream at the SLBI± inputs, and clock holdover mode requires a reference clock signal at the SLBI± inputs. See Table 1 for the required LREF and SIS settings. Once an operational mode is chosen, the remaining logic inputs (RATESET, FREFSET) program the input data rate or reference clock frequency.

#### Normal and System Loopback Settings

The RATESET pin is available for setting the SDI± and SLBI± inputs to receive the appropriate data rate. The FREFSET pin can be set to a zero or 1 while in normal or system-loopback mode (Tables 2 and 3).

#### Clock Frequencies in Holdover Mode

Set the incoming reference-clock frequency and outgoing serial-clock frequency by setting RATESET and FREFSET appropriately (Table 3).

**Table 1. Operational Modes**

| MODE            | LREF | SIS    |

|-----------------|------|--------|

| Normal          | 1    | 0      |

| System loopback | 1    | 1      |

| Clock holdover  | 0    | 1 or 0 |

### Table 2. Data-Rate Settings (MAX3874)

| INPUT DATA RATE<br>(Gbps) | RATESET | FREFSET |

|---------------------------|---------|---------|

| 2.667                     | 1       | 1 or 0  |

| 2.488                     | 0       | 1 or 0  |

## Table 3. Data-Rate Settings (MAX3874A)

| INPUT DATA RATE<br>(Gbps) | RATESET | FREFSET |

|---------------------------|---------|---------|

| 2.0212                    | 0       | 1 or 0  |

Table 4. Holdover Frequency Settings

| REFERENCE CLOCK<br>FREQUENCY (MHz) | SCLKO FREQUENCY (GHz) | RATESET | FREFSET |

|------------------------------------|-----------------------|---------|---------|

| 666.51                             | 2.667                 | 1       | 0       |

| 622.08                             | 2.488                 | 0       | 0       |

| 166.63                             | 2.667                 | 1       | 1       |

| 155.52                             | 2.488                 | 0       | 1       |

#### **Setting the Loop Filter**

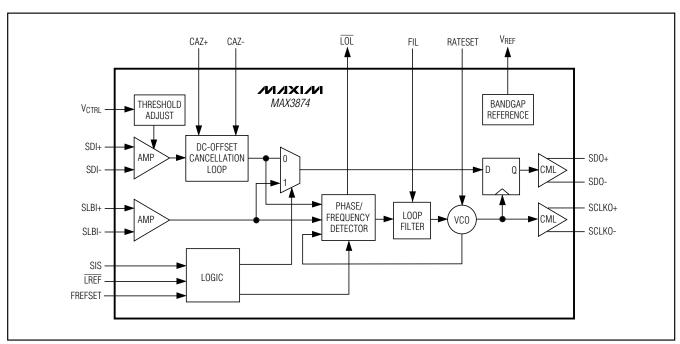

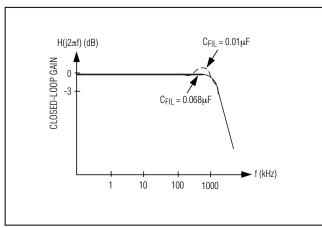

The MAX3874 is designed for both regenerator and receiver applications. Its fully integrated PLL is a classic 2nd-order feedback system, with a jitter transfer bandwidth (JBW) below 2MHz. The external capacitor (CFIL) connected from FIL to VCC\_VCO sets the PLL damping. Note that the PLL jitter transfer bandwidth does not change as CFIL changes, but the jitter peaking, acquisition time, and loop stability are affected. Figures 6 and 7 show the open-loop and closed-loop transfer functions.

The PLL zero frequency, fz, is a function of external capacitor CFIL, and can be approximated according to:

$$f_Z = \frac{1}{2\pi (650\Omega)C_{FIL}}$$

For an overdamped system ( $f_Z$  /  $J_{BW}$  < 0.25), the jitter peaking (JP) of a 2nd-order system can be approximated by:

$$J_{P} = 20 \log \left( 1 + \frac{f_{Z}}{J_{BW}} \right)$$

where J<sub>BW</sub> is the jitter transfer bandwidth for a given data rate.

The recommended value of  $C_{FIL} = 0.068 \mu F$  is to guarantee a maximum jitter peaking of less than 0.1dB. Decreasing  $C_{FIL}$  from the recommended value decreases acquisition time, with the trade-off of increased peaking. Excessive reduction of  $C_{FIL}$  can cause PLL instability.  $C_{FIL}$  must be a low-TC, high-quality capacitor of type X7R or better.

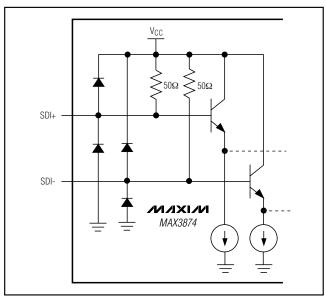

#### **Input Terminations**

The SDI $\pm$  and SLBI $\pm$  inputs of the MAX3874 are current-mode-logic (CML) compatible. The inputs all provide internal 50 $\Omega$  termination to reduce the required number of external components. AC-coupling is recom-

Figure 6. Open-Loop Transfer Function

Figure 7. Closed-Loop Transfer Function

mended. See Figure 8 for the input structure. For additional information about logic interfacing, refer to Maxim Application Note HFAN 1.0: *Introduction to LVDS, PECL, and CML*.

Figure 8. CML Input Model

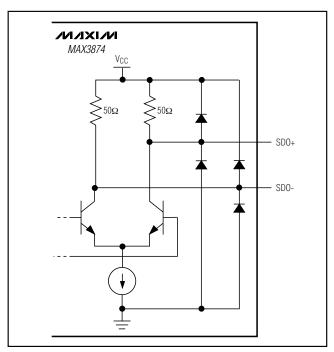

#### **Output Terminations**

The MAX3874 uses CML for its high-speed digital outputs (SDO $\pm$  and SCLKO $\pm$ ). The configuration of the output circuit includes internal 50 $\Omega$  back terminations to V<sub>CC</sub>. See Figure 9 for the output structure. CML outputs can be terminated by 50 $\Omega$  to V<sub>CC</sub>, or by 100 $\Omega$  differential impedance. For additional information on logic interfacing, refer to Maxim Application Note HFAN 1.0: Introduction to LVDS, PECL, and CML.

# \_Applications Information

#### **Clock Holdover Capability**

Clock holdover is required in some applications in which a valid clock must be provided to the upstream device in the absence of data transitions. To provide this function, an external reference clock signal must be applied to the SLBI± inputs and the proper control signals set (see the *Modes of Operation* section). To enter holdover mode automatically when there are no transitions applied to the SDI+ inputs, LOL or the system LOS can be directly connected to LREF.

#### System Loopback

The MAX3874 is designed to allow system-loopback testing. When the device is set for system-loopback mode, the serial output data of a transmitter can be directly connected to the SLBI inputs to run system diagnostics. See Table 1 for selecting system loopback operation mode. While in system loopback mode, LREF should not be connected to LOL.

Figure 9. CML Output Model

#### **Consecutive Identical Digits (CIDs)**

The MAX3874 has a low phase and frequency drift in the absence of data transitions. As a result, long runs of consecutive zeros and ones can be tolerated while maintaining a BER better than  $10^{-10}$ . The CID tolerance is tested using a  $2^{13}$  - 1 PRBS with long runs of ones and zeros inserted in the pattern. A CID tolerance of 2000 bits is typical.

#### Exposed Pad (EP) Package

The EP, 32-pin QFN incorporates features that provide a very low thermal-resistance path for heat removal from the IC. The pad is electrical ground on the MAX3874 and should be soldered to the circuit board for proper thermal and electrical performance.

#### **Layout Considerations**

For best performance, use good high-frequency layout techniques. Filter voltage supplies, keep ground connections short, and use multiple vias where possible. Use controlled-impedance transmission lines to interface with the MAX3874 high-speed inputs and outputs. Place power-supply decoupling as close to V<sub>CC</sub> as possible. To reduce feedthrough, isolate the input signals from the output signals. If a bare die is used, mount the back of die to ground (GND) potential.

Figure 10 shows interfacing with the MAX3861 AGC using threshold adjust.

Figure 10. Interfacing with the MAX3861 AGC Using Threshold Adjust

### **Pin Configuration**

#### FREFSET TOP VIEW GND CAZ-28 27 26 VCC\_OUT $V_{\text{CC}}$ 24 23 2 SDI+ SDO+ 22 SDI-SDO-21 VCC\_OUT $V_{CC}$ MAX3874 20 SLBI+ SCLKO+ 19 SCLKO-SLBI-18 VCC\_VCO SIS 8 LREF RATESET 000 N.C. N.C. 5mm x 5mm

## \_Chip Information

TRANSISTOR COUNT: 5142 PROCESS: SiGe BiPolar SUBSTRATE: SOI

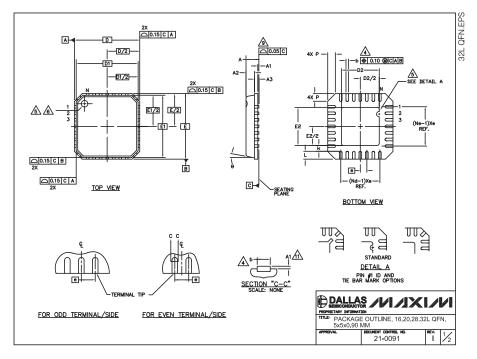

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to www.maxim-ic.com/packages.)

|        |                                 |          |      |          | COMM     | ON DIME | NSIONS            |         |          |          |          |      |  |

|--------|---------------------------------|----------|------|----------|----------|---------|-------------------|---------|----------|----------|----------|------|--|

| PKG    | 16L 5x5 20L 5x5 28L 5x5 32L 5x5 |          |      |          |          |         |                   |         |          |          |          |      |  |

| SYMBOL | MIN.                            | NOM.     | MAX. | MIN.     | NOM.     | MAX.    | MIN.              | NOM.    | MAX.     | MIN.     | NOM.     | MA)  |  |

| Α      | 0.80                            | 0.90     | 1.00 | 0.80     | 0.90     | 1.00    | 0.80              | 0.90    | 1.00     | 0.80     | 0.90     | 1.00 |  |

| A1     | 0.00                            | 0.01     | 0.05 | 0.00     | 0.01     | 0.05    | 0.00              | 0.01    | 0.05     | 0.00     | 0.01     | 0.0  |  |

| A2     | 0.00                            | 0.65     | 1.00 | 0.00     | 0.65     | 1.00    | 0.00              | 0.65    | 1.00     | 0.00     | 0.65     | 1.0  |  |

| A3     |                                 | 0.20 REF | F    |          | 0.20 REF | -       | 0.20 REF 0.20 REF |         |          |          |          |      |  |

| ь      | 0.28                            | 0.33     | 0.40 | 0.23     | 0.28     | 0.35    | 0.18              | 0.23    | 0.30     | 0.18     | 0.23     | 0.3  |  |

| D      | 4.90                            | 5.00     | 5.10 | 4.90     | 5.00     | 5.10    | 4.90              | 5.00    | 5.10     | 4.90     | 5.00     | 5.1  |  |

| D1     |                                 | 4.75 BSC |      | 4.75 BSC |          |         | 4.75 BSC          |         | 4.75 BSC |          |          |      |  |

| E      | 4.90                            | 5.00     | 5.10 | 4.90     | 5.00     | 5.10    | 4.90              | 5.00    | 5.10     | 4.90     | 5.00     | 5.1  |  |

| E1     |                                 | 4.75 BS  | С    |          | 4.75 BS0 |         | 4.75 BSC          |         |          |          | 4.75 BSC |      |  |

| е      |                                 | 0.80 BS  | С    |          | 0.65 BSC | ;       |                   | 0.50 BS | С        | 0.50 BSC |          |      |  |

| k      | 0.25                            | -        | -    | 0.25     | -        | -       | 0.25              | -       | -        | 0.25     | -        | _    |  |

| L      | 0.35                            | 0.55     | 0.75 | 0.35     | 0.55     | 0.75    | 0.35              | 0.55    | 0.75     | 0.30     | 0.40     | 0.5  |  |

| N      |                                 | 16       |      |          | 20       |         | 28                |         |          | 32       |          |      |  |

| ND     |                                 | 4        |      |          | 5        |         |                   | 7       |          | 8        |          |      |  |

| NE     | 4                               |          |      |          | 5        |         | 7                 |         |          | 8        |          |      |  |

| Р      | 0.00                            | 0.42     | 0.60 | 0.00     | 0.42     | 0.60    | 0.00              | 0.42    | 0.60     | 0.00     | 0.42     | 0.6  |  |

| 9      | 0,                              |          | 12*  | 0,       |          | 12*     | 0,                |         | 12*      | 0,       |          | 12   |  |

| EXPOSED PAD VARIATIONS |      |      |      |      |      |         |  |  |  |

|------------------------|------|------|------|------|------|---------|--|--|--|

|                        | E5   |      |      | DS   |      | PKG.    |  |  |  |

| MAX.                   | NDM. | MIN. | MAX. | NDM. | MIN. | CODES   |  |  |  |

| 3.25                   | 3.10 | 2.95 | 3.25 | 3.10 | 2.95 | G1655-3 |  |  |  |

| 2.85                   | 2.70 | 2.55 | 2.85 | 2.70 | 2.55 | G2055-1 |  |  |  |

| 3.25                   | 3.10 | 2.95 | 3.25 | 3.10 | 2.95 | G2055-2 |  |  |  |

| 2.85                   | 2.70 | 2.55 | 2.85 | 2.70 | 2.55 | G2855-1 |  |  |  |

| 3.25                   | 3.10 | 2.95 | 3.25 | 3.10 | 2.95 | G2855-2 |  |  |  |

| 3.25                   | 3.10 | 2.95 | 3.25 | 3.10 | 2.95 | G3255-1 |  |  |  |

|                        |      |      |      |      |      |         |  |  |  |

- DIE THICKNESS ALLOWABLE IS 0.305mm MAXIMUM (.012 INCHES MAXIMUM)

DIMENSIONING & TOLERANCES CONFORM TO ASME Y14.5M. 1994.

- N IS THE NUMBER OF TERMINALS.

N IS THE NUMBER OF TERMINALS IN X-DIRECTION & No IS THE NUMBER OF TERMINALS IN Y-DIRECTION.

DIMENSION b APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.20 AND 0.25mm FROM TERMINAL TIP.

- LEAST THE PIN #1 IDENTIFIER MUST BE EXISTED ON THE TOP SURFACE OF THE PACKAGE BY USING INDENTATION MARK OR INK/LASER MARKED. DETAILS OF PIN #1 IDENTIFIER IS OPTIONAL, BUT MUST BE LOCATED WITHIN ZONE INDICATED.

- 6. EXACT SHAPE AND SIZE OF THIS FEATURE IS OPTIONAL.

- 7. ALL DIMENSIONS ARE IN MILLIMETERS. 8. PACKAGE WARPAGE MAX 0.05mm.

- 9. APPLIED FOR EXPOSED PAD AND TERMINALS.

EXCLUDE EMBEDDED PART OF EXPOSED PAD FROM MEASURING.

- MEETS JEDEC MO220; EXCEPT DIMENSION "b"

- APPLIED FOR EXPOSED PAD AND TERMINALS. EXCLUDE EMBEDDING PART OF EXPOSED PAD FROM MEASURING.

- 12. THIS PACKAGE OUTLINE APPLIES TO ANVIL SINGULATION (STEPPED SIDES).

## Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to www.maxim-ic.com/packages.)

| COMMON DIMENSIONS |         |           |      |      |                         |               |            |         |           |      |           |      |      |      |      |

|-------------------|---------|-----------|------|------|-------------------------|---------------|------------|---------|-----------|------|-----------|------|------|------|------|

| PKG.              | 16L 5x5 |           | 5    | 2    | 20L 5x5 28L 5x5 32L 5x5 |               | <b>(</b> 5 | 40L 5x5 |           |      |           |      |      |      |      |

| SYMBOL            | MIN.    | NOM.      | MAX. | MIN. | NOM.                    | MAX.          | MIN.       | NOM.    | MAX.      | MIN. | NOM.      | MAX. | MIN. | NOM. | MAX. |

| Α                 | 0.70    | 0.75      | 0.80 | 0.70 | 0.75                    | 0.80          | 0.70       | 0.75    | 0.80      | 0.70 | 0.75      | 0.80 | 0.70 | 0.75 | 0.80 |

| A1                | 0       | 0.02      | 0.05 | 0    | 0.02                    | 0.05          | 0          | 0.02    | 0.05      | 0    | 0.02      | 0.05 | 0    | 0.02 | 0.05 |

| A2                | 0.      | 0.20 REF. |      | 0.   | 20 RE                   | F.            | 0.20 REF.  |         | 0.20 REF. |      | 0.20 REF. |      |      |      |      |

| b                 | 0.25    | 0.30      | 0.35 | 0.25 | 0.30                    | 0.35          | 0.20       | 0.25    | 0.30      | 0.20 | 0.25      | 0.30 | 0.15 | 0.20 | 0.25 |

| D                 | 4.90    | 5.00      | 5.10 | 4.90 | 5.00                    | 5.10          | 4.90       | 5.00    | 5.10      | 4.90 | 5.00      | 5.10 | 4.90 | 5.00 | 5.10 |

| E                 | 4.90    | 5.00      | 5.10 | 4.90 | 5.00                    | 5.10          | 4.90       | 5.00    | 5.10      | 4.90 | 5.00      | 5.10 | 4.90 | 5.00 | 5.10 |

| е                 | 0       | .80 BS    | SC.  | 0    | .65 BS                  | SC.           | 0.50 BSC.  |         | 0.50 BSC. |      | 0.40 BSC. |      |      |      |      |

| k                 | 0.25    |           | -    | 0.25 |                         |               | 0.25       |         |           | 0.25 | -         |      | 0.25 |      |      |

| L                 | 0.30    | 0.40      | 0.50 | 0.45 | 0.55                    | 0.65          | 0.45       | 0.55    | 0.65      | 0.30 | 0.40      | 0.50 | 0.30 | 0.40 | 0.50 |

| N                 | 16      |           | 20   |      | 28                      |               | 32         |         |           | 40   |           |      |      |      |      |

| ND                | 4       |           |      | 5    |                         | 7             |            | 8       |           | 10   |           |      |      |      |      |

| NE                | 4       |           |      |      | 5                       |               |            | 7       |           |      | 8         |      | 10   |      |      |

| JEDEC             | WHHB    |           |      | WHH  | C                       | WHHD-1 WHHD-2 |            |         |           |      |           |      |      |      |      |

| 10 | $\Gamma$ | c |  |

|----|----------|---|--|

|    |          |   |  |

- 1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

- 3. N IS THE TOTAL NUMBER OF TERMINALS.

A THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

⚠ DIMENSION b APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25 mm AND 0.30 mm FROM TERMINAL TIP.

M ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

7. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

$\underline{\&}$  COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

9. DRAWING CONFORMS TO JEDEC MO220, EXCEPT EXPOSED PAD DIMENSION FOR T2855-3 AND T2855-6.

WARPAGE SHALL NOT EXCEED 0.10 mm.

11. MARKING IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

12. NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY.

$extcolor{oldsymbol{\Lambda}}{}$  LEAD CENTERLINES TO BE AT TRUE POSITION AS DEFINED BY BASIC DIMENSION "e",  $\pm 0.05$ .

-DRAWING NOT TO SCALE-

| EXPOSED PAD VARIATIONS |      |      |      |      |      |      |  |  |

|------------------------|------|------|------|------|------|------|--|--|

| PKG.                   |      | D2   |      | E2   |      |      |  |  |

| CODES                  | MIN. | NOM. | MAX. | MIN. | NOM. | MAX. |  |  |

| T1655-2                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T1655-3                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T1655N-1               | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T2055-3                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T2055-4                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T2055-5                | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |

| T2855-3                | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |

| T2855-4                | 2.60 | 2.70 | 2.80 | 2.60 | 2.70 | 2.80 |  |  |

| T2855-5                | 2.60 | 2.70 | 2.80 | 2.60 | 2.70 | 2.80 |  |  |

| T2855-6                | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |

| T2855-7                | 2.60 | 2.70 | 2.80 | 2.60 | 2.70 | 2.80 |  |  |

| T2855-8                | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |

| T2855N-1               | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |

| T3255-3                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T3255-4                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T3255-5                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T3255N-1               | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T4055-1                | 3.40 | 3.50 | 3.60 | 3.40 | 3.50 | 3.60 |  |  |

| T4055-2                | 3.40 | 3.50 | 3.60 | 3.40 | 3.50 | 3.60 |  |  |

16, 20, 28, 32, 40L THIN QFN, 5x5x0.8r

21-0140

## **Revision History**

Rev 0: 2/03: Original data sheet release.

Rev 1; 4/03: Page 3: Changed Jitter Transfer Bandwidth (MAX3874A) typ from 0.75MHz to 0.7MHz.

Rev 2: 5/03: Page 1: Deleted -EP from package information.

Rev 3; 1/05: Page 1: Added lead-free package information.

Page 1: Removed future status from MAX3745 in Typical Application Circuit. Rev 4; 7/06:

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_

# MAX3874

#### **Part Number Table**

#### Notes:

- 1. See the MAX3874 QuickView Data Sheet for further information on this product family or download the MAX3874 full data sheet (PDF, 1.1MB).

- 2. Other options and links for purchasing parts are listed at: http://www.maxim-ic.com/sales.

- 3. Didn't Find What You Need? Ask our applications engineers. Expert assistance in finding parts, usually within one business day.

- 4. Part number suffixes: T or T&R = tape and reel; + = RoHS/lead-free; # = RoHS/lead-exempt. More: See full data sheet or Part Naming Conventions.

- 5. \* Some packages have variations, listed on the drawing. "PkgCode/Variation" tells which variation the product uses.

| Part Number    | Free<br>Sample | Buy<br>Direct | Package: TYPE PINS SIZE  DRAWING CODE/VAR *                                         | Temp         | RoHS/Lead-Free?<br>Materials Analysis     |

|----------------|----------------|---------------|-------------------------------------------------------------------------------------|--------------|-------------------------------------------|

| MAX3874AEGJ    |                |               | QFN;32 pin;5x5x0.9mm<br>Dwg: 21-0091I (PDF)<br>Use pkgcode/variation: G3255-1*      | -40C to +85C | RoHS/Lead-Free: No<br>Materials Analysis  |

| MAX3874AEGJ-T  |                |               | QFN;32 pin;5x5x0.9mm<br>Dwg: 21-0091I (PDF)<br>Use pkgcode/variation: G3255-1*      | -40C to +85C | RoHS/Lead-Free: No<br>Materials Analysis  |

| MAX3874EGJ     |                |               | QFN;32 pin;5x5x0.9mm<br>Dwg: 21-0091I (PDF)<br>Use pkgcode/variation: G3255-1*      | -40C to +85C | RoHS/Lead-Free: No<br>Materials Analysis  |

| MAX3874EGJ-T   |                |               | QFN;32 pin;5x5x0.9mm<br>Dwg: 21-0091I (PDF)<br>Use pkgcode/variation: G3255-1*      | -40C to +85C | RoHS/Lead-Free: No<br>Materials Analysis  |

| MAX3874AETJ+D  |                |               | THIN QFN;32 pin;5x5x0.8mm<br>Dwg: 21-0140K (PDF)<br>Use pkgcode/variation: T3255+3* | -40C to +85C | RoHS/Lead-Free: Yes<br>Materials Analysis |

| MAX3874AETJ+TD |                |               | THIN QFN;32 pin;5x5x0.8mm<br>Dwg: 21-0140K (PDF)<br>Use pkgcode/variation: T3255+3* | -40C to +85C | RoHS/Lead-Free: Yes<br>Materials Analysis |

Didn't Find What You Need?

#### CONTACT US: SEND US AN EMAIL

Copyright 2007 by Maxim Integrated Products, Dallas Semiconductor • Legal Notices • Privacy Policy