# **I3C Master IP Core - Lattice Radiant Software**

**User Guide**

FPGA-IPUG-02082-1.2

June 2020

#### Disclaimers

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS and with all faults, and all risk associated with such information is entirely with Buyer. Buyer shall not rely on any data and performance specifications or parameters provided herein. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. No Lattice products should be used in conjunction with mission- or safety-critical or any other application in which the failure of Lattice's product could create a situation where personal injury, death, severe property or environmental damage may occur. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

# Contents

| Acronyms in This Document                    | 6  |

|----------------------------------------------|----|

| 1. Introduction                              | 7  |

| 1.1. Quick Facts                             | 7  |

| 1.2. Features                                | 8  |

| 1.3. Conventions                             | 8  |

| 1.3.1. Nomenclature                          | 8  |

| 1.3.2. Signal Names                          | 8  |

| 2. Functional Description                    | 9  |

| 2.1. Overview                                |    |

| 2.1.1. I3C Master Controller Top Logic       | 11 |

| 2.1.2. LMMI Interface                        |    |

| 2.1.3. AHB-Lite/APB to LMMI Bridge           | 12 |

| 2.1.4. Bus Management Block                  |    |

| 2.1.5. Bus Characteristics Register (BCR)    |    |

| 2.1.6. Device Characteristics Register (DCR) | 15 |

| 2.1.7. Legacy Virtual Register (LVR)         | 15 |

| 2.2. Signal Description                      | 16 |

| 2.3. Attributes Summary                      | 17 |

| 2.4. Register Description                    | 21 |

| 2.4.1. Registers Bits Description            | 24 |

| 2.4.2. Secondary Master Related Registers    | 31 |

| 2.5. Programming Flow                        | 34 |

| 2.6. Transaction Control                     |    |

| 2.7. Combined Transactions                   | 35 |

| 2.8. Transaction Termination                 | 36 |

| 2.9. ENEC, DISEC, SETMWL, SETMRL Commands    | 36 |

| 2.10. IBI and Hot Join Request Results       | 36 |

| 2.10.1. Macro Commands                       | 36 |

| 2.10.2. List of Slaves Found on the I3C Bus  |    |

| 3. IP Generation and Evaluation              | 37 |

| 3.1. Licensing the IP                        | 37 |

| 3.2. Generation and Synthesis                |    |

| 3.3. Running Functional Simulation           | 39 |

| 3.4. Hardware Evaluation                     | 41 |

| 4. Ordering Part Number                      | 42 |

| Appendix A. Resource Utilization             | 43 |

| References                                   | 44 |

| Technical Support Assistance                 | 45 |

| Revision History                             | 46 |

# Figures

| Figure 2.1. I3C Master IP Core Functional Diagram  | 10 |

|----------------------------------------------------|----|

| Figure 2.2. Top Level Block Diagram                | 11 |

| Figure 2.3. Bus Interconnect                       | 12 |

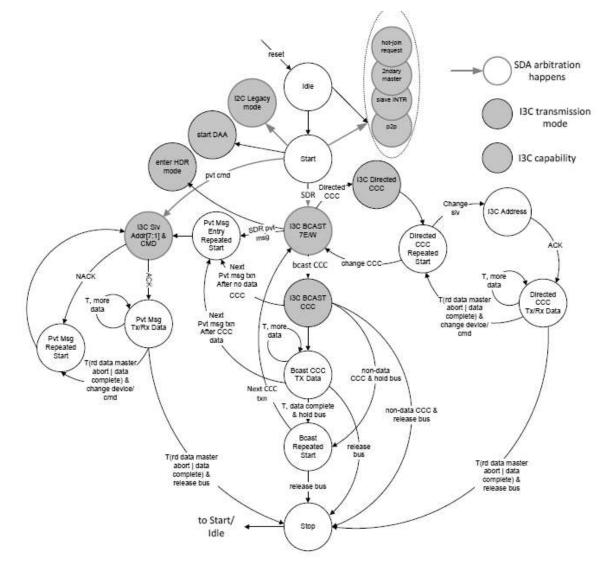

| Figure 2.4. I3C Main Master Key Transmission Modes | 34 |

| Figure 3.1. Configure Block of I3C Master Module   | 37 |

| Figure 3.2. Check Generating Results Window        |    |

| Figure 3.3. Synthesizing Design                    |    |

| Figure 3.4. Simulation Wizard                      |    |

| Figure 3.5. Adding and Reordering Source           | 40 |

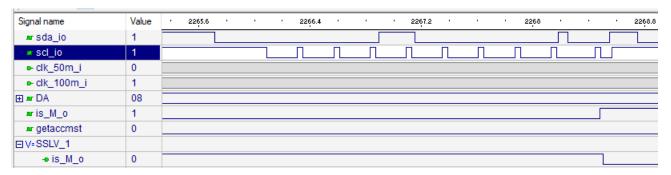

| Figure 3.6. Dynamic Address Assignment             |    |

| Figure 3.7. Master Request from Secondary Master   |    |

| Figure 3.8. Main Master Regains Mastership         | 41 |

# **Tables**

| Table 1.1. Quick Facts                                   |    |

|----------------------------------------------------------|----|

| Table 2.1. Bus Characteristics Register                  | 14 |

| Table 2.2. Device Characteristics Register               | 15 |

| Table 2.3. Legacy Virtual Register                       | 15 |

| Table 2.4. Ports Description                             | 16 |

| Table 2.5. Attributes Table                              | 17 |

| Table 2.6. Attributes Descriptions                       | 19 |

| Table 2.7. Register Address Map                          | 21 |

| Table 2.8. Current Revision                              | 24 |

| Table 2.9. Start Command Strobe                          |    |

| Table 2.10. CCC or Direct Command                        | 24 |

| Table 2.11. Slave Address                                | 24 |

| Table 2.12. Transaction Length in Bytes                  | 24 |

| Table 2.13. Write Buffer (FIFO)                          | 24 |

| Table 2.14. Read Buffer (FIFO)                           | 24 |

| Table 2.15. Command Execution Status                     |    |

| Table 2.16. Combined Commands Mode                       |    |

| Table 2.17. Secondary Master Request Received            | 25 |

| Table 2.18. Read Is Over                                 | 25 |

| Table 2.19. Initial Start of Procedure                   |    |

| Table 2.20. Management State                             | 25 |

| Table 2.21. Coded subset of the command execution status | 26 |

| Table 2.22. Test Register                                | 26 |

| Table 2.23. PID Byte 5 PID Byte 0                        | 26 |

| Table 2.24. BCR of the accessed slave device             | 26 |

| Table 2.25. DCR of the accessed slave device             | 26 |

| Table 2.26. Maximum Write Length MSB                     | 26 |

| Table 2.27. Maximum Write Length LSB                     | 26 |

| Table 2.28. Maximum Read Length MSB                      | 26 |

| Table 2.29. Maximum Read Length LSB                      | 27 |

| Table 2.30. IBI Size Received with Maximum Read Length   |    |

| Table 2.31. Slave Dynamic Address                        |    |

| Table 2.32. Slave Status MSB                             | 27 |

| Table 2.33. Slave Status LSB                             | 27 |

| Table 2.34. Max Write Speed                              |    |

| Table 2.35. Max Read Speed                               | 27 |

| Table 2.36. Max Tu    | Irnaround Time                                  | 27        |

|-----------------------|-------------------------------------------------|-----------|

| Table 2.37. IBI Req   | uest Detected                                   | 27        |

| Table 2.38. HJ Requ   | uest Detected                                   | 27        |

|                       | ed IBI Byte                                     |           |

| Table 2.40. Numbe     | r of Detected Slaves                            | 28        |

| Table 2.41. IBI Slav  | e Address                                       | 28        |

| Table 2.42. Comma     | and Done Flag                                   | 28        |

|                       | HDR Capability                                  |           |

| Table 2.44. Timing    | Control Supported Modes                         | 28        |

| •                     | Control State Byte                              |           |

| Table 2.46. Timing    | Control Frequency Byte                          | 28        |

| Table 2.47. Timing    | Control Inaccuracy Byte                         | <u>29</u> |

| Table 2.48. ENEC E    | vent Data Byte to Send                          | <u>29</u> |

| Table 2.49. DISEC E   | event Data Byte to Send                         | 29        |

| Table 2.50. SETMW     | /L MSB                                          | <u>29</u> |

|                       | /L LSB                                          |           |

|                       | L MSB                                           |           |

| Table 2.53. SETMR     | L LSB                                           | <u>29</u> |

|                       | L IBI Size                                      |           |

| Table 2.55. ENTTM     | Mode byte                                       | <u>29</u> |

| Table 2.56. DA for    | SETDASA and SETNEWDA commands                   | 30        |

|                       | nterrupt Status if Current Master               |           |

| Table 2.58. LMMI I    | nterrupt Enable if Current Master               | 30        |

| Table 2.59. LMMI I    | nterrupt Set if Current Master                  | 30        |

| Table 2.60. SETXTI    | ME Supported Defining Bytes                     | 30        |

| Table 2.61. SETXTI    | ME Additional Data Byte                         | 30        |

| Table 2.62. List of S | Slaves                                          | 31        |

| Table 2.63. ODR Va    | alue                                            | 31        |

| Table 2.64. Max IB    | I Payload Size                                  | 31        |

| Table 2.65. Numbe     | r of Slaves captured from DEFSLVS               | 31        |

| Table 2.66. Regaini   | ng Bus Ownership Request                        | 31        |

| Table 2.67. HDR W     | rite Command Code                               | 31        |

|                       | ad Command Code                                 |           |

| Table 2.69. P2P SET   | TDASA Configuration Indication                  | 32        |

| Table 2.70. Error St  | tatus for SDR when Master is Not Current Master | 32        |

| Table 2.71. Error St  | tatus for HDR when Master is Not Current Master | 32        |

| Table 2.72. LMMI I    | nterrupt Status if not Current Master           | 32        |

| Table 2.73. LMMI I    | nterrupt Enable if not Current Master           | 33        |

| Table 2.74. LMMI I    | nterrupt Set if not Current Master              | 33        |

| Table 2.75. FIFO Cu   | Irrent State if not Current Master              | 33        |

| Table 2.76. State C   | ontrol and Special Commands                     | 34        |

| Table 2.77. Transac   | ction Control Status                            | 35        |

| Table 3.1. Generate   | ed File List                                    | 38        |

| Table A.1. Resource   | e Utilization                                   | 13        |

# Acronyms in This Document

# A list of acronyms used in this document.

| Acronym          | Definition                      |

|------------------|---------------------------------|

| FPGA             | Field Programmable Gate Array   |

| IP               | Intellectual Property           |

| LUT              | Lookup-Table                    |

| I <sup>2</sup> C | Inter-Integrated Circuit        |

| LMMI             | Lattice Memory Mapped Interface |

| SDA              | Serial Data                     |

| SCL              | Serial Clock                    |

| DA               | Dynamic Address                 |

| SA               | Static Address                  |

| DAA              | Dynamic Address Assignment      |

| NVM              | Non Volatile Memory             |

# 1. Introduction

I3C is a two-wire bi-directional serial bus, optimized for multiple sensor Slave devices and controlled by only one I3C Master device at a time. I3C is backward compatible with many legacy I<sup>2</sup>C devices, but I3C devices also support significantly higher speeds, new communication modes, and new device roles, including an ability to change device roles over time. For example, the initial Master can cooperatively pass the mastership to another I3C device on the bus, if the requesting I3C device supports a Secondary Master feature.

The Lattice Semiconductor I3C IP improves upon the features of the I<sup>2</sup>C interface, preserving backward compatibility.

Implementing the I3C specification greatly increases implementation flexibility for an ever-expanding sensor subsystem as efficiently as possible and at a low cost. Implementation follows the MIPI I3C specification to provide a single scalable, cost effective, power efficient protocol to solve issues with high protocol overhead, increased power consumption, nonstandard protocol, separate lines for interrupt, and the rest requirement. The MIPI I3C interface is developed to ease sensor system design architectures in mobile wireless products by providing a fast, low cost, low power, two-wire digital interface for sensors.

Two main concerns are paramount for the I3C IP Core:

- the use of as little energy as possible in transporting data and control, and

- reducing the number of physical pins used by the interface.

The I3C interface provides major efficiencies in bus power while providing greater than 10x speed improvements over  $I^2C$ .

This design is implemented in Verilog. The Lattice Radiant<sup>®</sup> software Place and Route tool, integrated with Synplify Pro<sup>®</sup> synthesis tool, is used for design implementation. The design can be targeted to all CrossLink<sup>™</sup>-NX and Certus<sup>™</sup>-NX family devices. When used on a different device, density, speed or grade, performance and utilization may vary.

# 1.1. Quick Facts

Table 1.1 presents a summary of the I3C Master IP Core.

| IP Requirements      | Supported FPGA Family     | CrossLink-NX, Certus-NX                                                                |  |  |

|----------------------|---------------------------|----------------------------------------------------------------------------------------|--|--|

|                      | Targeted Devices          | LIFCL-40, LIFCL-17, LFD2NX-40                                                          |  |  |

| Resource Utilization | Supported User Interfaces | LMMI (Lattice Memory Mapped Interface), APB, AHB                                       |  |  |

|                      | Lattice Implementation    | IP Core v1.0.x – Lattice Radiant Software 2.1                                          |  |  |

|                      | Curtherain                | Lattice Synthesis Engine (LSE)                                                         |  |  |

| Design Tool Support  | Synthesis                 | Synopsys <sup>®</sup> Synplify Pro for Lattice                                         |  |  |

|                      | Simulation                | For the list of supported simulators, see the Lattice Radiant Software 2.1 User Guide. |  |  |

# Table 1.1. Quick Facts

© 2019-2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# 1.2. Features

An I3C bus requires exactly one I3C device at a time functioning as an I3C Master device. In I3C terms, this I3C Master device is the current master at that time. In typical applications, the current master is the I3C device on the bus that sends the majority of the I3C commands, addressing either all Slaves (Broadcast CCCs) or specific individual Slaves (Directed CCCs). The Current Master is also the only device on the I3C bus allowed to send I<sup>2</sup>C Messages.

The MIPI I3C Master Controller supports the following features:

- Two wire serial interface up to 12.5 MHz using Push-Pull

- Legacy I<sup>2</sup>C device coexist on the same bus (with some limitations)

- Dynamic Addressing while supporting Static Addressing for legacy I<sup>2</sup>C devices

- I<sup>2</sup>C -like SDR messaging

- HDR-DDR messaging

- Multi-Master capability

- In-Band Interrupt support

- Hot-Join support

- Synchronous Timing Support (not available in current release) and Asynchronous Time Stamping

# 1.3. Conventions

# 1.3.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

# 1.3.2. Signal Names

Signal names that end with:

- \_n are active low (asserted when value is logic 0)

- \_*i* are input signals

- \_o are output signals

# 2. Functional Description

# 2.1. Overview

I3C IP Core supports several communication formats, all sharing a two-wire interface: SDA bidirectional data pin, and SCL bidirectional for the Masters.

The I3C communication protocol supports the following modes:

- SDR mode

- HDR-DDR mode

The I3C bus is always initialized and configured in SDR Mode. Current implementation supports SDR and HDR-DDR modes.

SDR Mode is the default Mode of the I3C bus and is primarily used for private messaging from the Current Master device to Slave devices. SDR Mode is also used to enter other modes and for built-in features, such as Common Commands (CCCs), In-Band Interrupts, and transition from I<sup>2</sup>C to I3C by assignment of a Dynamic Address. I3C SDR Mode is significantly similar to the I<sup>2</sup>C protocol in terms of procedures and conditions, as a result, I3C devices and many legacy I<sup>2</sup>C Slave devices (but not I<sup>2</sup>C Master devices) can coexist on the same I3C bus.

Like SDR Mode, HDR-DDR Mode uses SCL as a clock; but unlike SDR, Data and Commands change SDA on both SCL edges, effectively doubling the data rate. By contrast, in SDR Mode SDA is changed only when SCL is Low.

HDR-DDR moves data by Words. A Word generally contains 16 payload bits, as two bytes in a byte stream, and two parity bits.

Four HDR-DDR Word Types are defined:

- Command Word

- User Data

- CRC Word

- Reserved Word

The HDR-DDR Protocol precedes each 18-bit Word with a 2-bit Preamble, for a total of 20 bits per Word. The Preamble:

- Indicates the type of data that follows: either Command, Data, or CRC

- Allows the Master to terminate a Read and to determine whether the Slave is willing to respond to a Read. This is controlled such that the first bit is Parked High and the other side can choose either to drive Low or to leave High

The I3C Master Controller accepts commands from a LMMI interface. These commands are decoded into I3C Slave Device Read/Write transactions. Furthermore, the I3C Master Controller can operate in interrupt or polling mode. This means that the LMMI interface can choose to poll the I3C Master for a change in status at periodic intervals or wait to be interrupted by the I3C Master Controller when data needs to be read or written.

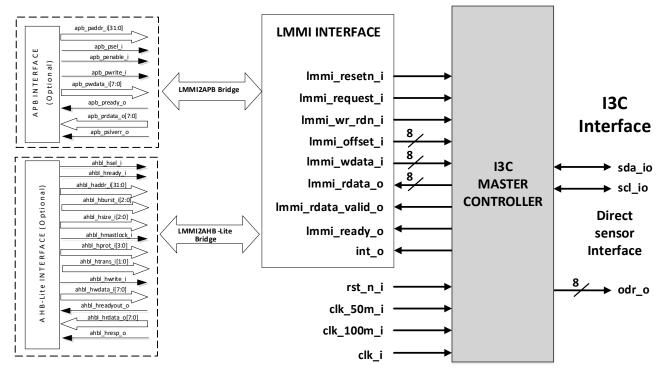

I3C Master IP Core functional diagram is shown in Figure 2.1.

© 2019-2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-IPUG-02082-1.2

Figure 2.1. I3C Master IP Core Functional Diagram

The I3C Master Controller design module contains the following functional blocks:

- LMMI interface

- I3C Master Controller Top

- Bus Management Block

- Configuration Registers

- Dynamic Address and Priority Levels Allocation

- In-Band Interrupt and Hot-Join Management, Master level

- Data Packet Generator HDR-DDR and/or I<sup>2</sup>C

- PHY Layer

- ACTIVE DRIVER and PUR SDA

- ACTIVE DRIVER and PUR SCL

- IO PAD SDA

- IO PAD SCL

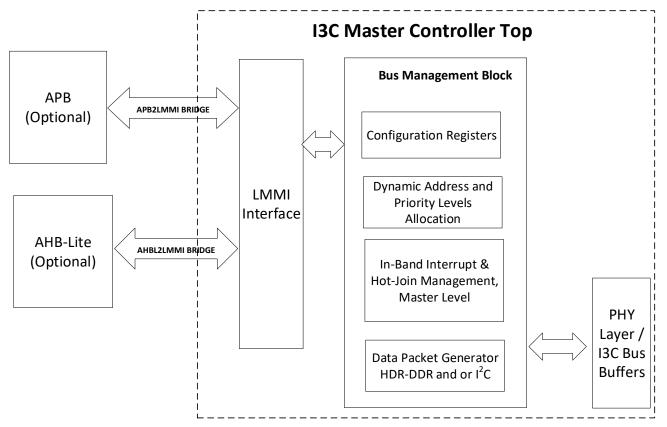

A top-level block diagram of the I3C Master Controller is shown in Figure 2.2.

© 2019-2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

Figure 2.2. Top Level Block Diagram

# 2.1.1. I3C Master Controller Top Logic

This is the top-level HDL block of the I3C Master Controller design module. This block is created to instantiate all modules of the design and control of tristate drivers of the SDA and SCL signals. I3C Master Controller has two Main Master device roles and may also support one of the two Secondary Master device roles.

Two Main Master device roles are listed below.

- Main Master: The I3C Master device on the I3C bus that initially configures the I3C bus and serves as the first Current Master. Only one I3C device on a given I3C bus can take the Main Master role, that is, the role cannot be passed on to any other I3C device on the I3C bus. It supports both SDR Mode and HDR-DDR Mode.

- SDR-Only Main Master: A Main Master that only supports I3C's SDR Mode; does not support any of the HDR-DDR Mode.

There are two Secondary Master device roles, listed below.

- I3C Secondary Master: Any I3C device on the I3C bus, other than the Current Master, with I3C Master Capability. There can be multiple Secondary Masters on an I3C bus at the same time. By definition, a Secondary Master functions as an I3C Slave device until and unless it eventually becomes Current Master. It supports both SDR Mode and HDR-DDR Mode.

- SDR-Only Secondary Master: A Secondary Master that only supports I3C's SDR Mode; does not support any of the HDR-DDR Mode.

# 2.1.2. LMMI Interface

The LMMI device module implements memory mapped registers. This interface is suited for IP blocks which use dynamically programmable configuration/control bits and read/write transactions. LMMI is a memory-mapped address/data interface which supports both single and burst transactions with a maximum throughput of one transaction per clock cycle.

The LMMI Interface module is a fully synchronous module that runs off the LMMI clock. A number of registers are initialized via the LMMI interface to ensure that the I3C Master IP Core functions as intended. LMMI defines a standard set of interface signals for register/memory access. The basic requirement is that any additional interface signals must not duplicate functionality described in this spec, that is, there should be only one interface (LMMI) for register/memory access.

For this particular IP, this block has two main functions:

- Accepts write data from the microprocessor and latches the data into the appropriate registers and read/write buffers.

- Controls data being sent to the microprocessor from the I3C Master Controller.

This block also generates an interrupt signal when either Transmit Buffer Empty flag or Receive Buffer Full flag are set.

The LINTR (Lattice Interrupt Interface) Interface consists of an interrupt signal and a set of interrupt registers which are accessed through LMMI. These interrupt registers follow a standard functional definition, allowing you to implement common hardware/software to handle interrupts from a variety of Hard IP blocks.

For more information on LMMI, see the Lattice Memory Mapped Interface and Lattice Interrupt Interface User Guide (FPGA-UG-02039).

# 2.1.3. AHB-Lite/APB to LMMI Bridge

When AHBL Mode is selected, AHBL2LMMI Bridge is instantiated inside the I3C Master IP and the native LMMI interface is translated to AHB-Lite interface.

When APB Mode is selected, APB2LMMI is instantiated inside the I3C Master IP and the native LMMI interface is translated to APB interface.

These optional bridges are implemented to easily interface the I3C Master IP in APB and AHB-Lite systems while preserving the native LMMI interface for writing and reading to internal registers and FIFO.

# 2.1.4. Bus Management Block

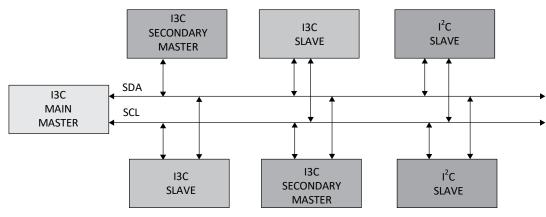

The I3C bus is configured as the link among several clients, in a flexible and efficient manner. At the system architecture level, eight roles are defined for I3C compatible devices. An example block diagram of I3C interconnections is shown in Figure 2.3. In this diagram there is a device with Main Master role, devices with I3C Slave role and devices with I<sup>2</sup>C Slave role. Note that I3C Secondary Master devices are gradient shaded, illustrating their ability to function in both Master and Slave roles (at different times). I3C Master IP Core implements I3C Main Master and Secondary Master roles.

# Figure 2.3. Bus Interconnect

# 2.1.4.1. I3C Configuration Registers

I3C Characteristics Registers describe and define an I3C compatible device's capabilities and functions on the I3C bus, as the device services a given system. devices without I3C Characteristics Registers should not be connected to a common I3C bus.

There are three Characteristics Register types:

- Bus Characteristics Register (BCR)

- Device Characteristics Register (DCR)

- Legacy Virtual Register (LVR)

Every I3C compatible device has associated Characteristics Registers, depending on the device types described below:

- Every I3C compliant device has one bus Characteristics Register, and one device Characteristics Register.

- Every legacy I<sup>2</sup>C device to be connected to an I3C bus has one associated Legacy Virtual Register. Since these are legacy devices, it is understood that this register exists virtually, for example as part of the device's driver.

# 2.1.4.2. Dynamic Address and Priority Levels Allocation

The Main Master is responsible for performing a Dynamic Address Assignment procedure, to provide a unique Dynamic Address to each device connected to the I3C bus.

The Main Master provides Dynamic Address to a device:

- Upon any initialization of the I3C bus, and

- When the device is connected to an already configured I3C bus.

Once a device receives a Dynamic Address, that Dynamic Address is used in all of that device's subsequent transactions on the I3C bus, until and unless the Master changes the device's Dynamic Address. The only way for the Master to change the device's Dynamic Address is by using either the RSTDA CCC command or the SETNEWDA CCC command. The Master might choose to change the device's Dynamic Address due to re-prioritization. The Main Master controls the Dynamic Address Assignment process. This process includes an Address Arbitration procedure similar to I<sup>2</sup>C's. The I3C Arbitration procedure differs from I<sup>2</sup>C by using the values of the 48-bit Provisional ID and the device's I3C Characteristic Registers (that is, BCR and DCR), concatenated. The device on the I3C bus with the lowest concatenated value wins each Arbitration round in turn, and the Main Master assigns a unique Dynamic Address to each winning device.

# 2.1.4.3. In-Band Interrupt and Hot-Join Management block

In I3C, Priority Level controls the order in which Slaves' In-Band Interrupt requests and Master requests are processed. The Priority Level of each Slave in an I3C bus instantiation is encoded in its Slave Address, with lower addresses having higher Priority. That is, Slaves with lower value Addresses and higher Priority Levels have their In-Band Interrupts and Master requests processed sooner than Slaves with higher value Addresses and lower Priority Levels.

During each Dynamic Address Assignment operation, the I3C Master Controller assigns lower Addresses to Slaves for higher Priority In-Band Interrupt requests.

The In-Band Interrupt block does one of the following three things:

- Accept the IBI by providing the ACK bit. The actions available to the Current Master depend upon the value of the Slave's BCR [2] bit (in the Slave's BCR register)

- Refuse the IBI without disabling interrupts. To do this, the Current Master simply passively NACKs to deny the IBI. (The Current Master knows that the Slave should try to interrupt again on the next START, which causes the Current Master to issue a Repeated START.)

- Refuse the IBI and disable interrupts. To do this, the Current Master NACKs to deny the IBI, then sends a Repeated START, and finally sets the DISINT bit in the Command Code Disable Slave Events Command (DISEC) to the interrupting Slave. (The Current Master can set the ENINT bit in the Command Code Enable Slave Events Command (DISEC) in a later time.)

Hot-Join block implements a method that allows the system designer to prevent the I3C Master Controller from attempting to Hot-Join when the device is not being used as a Hot-Join device.

The Hot-Join block may power-up at the same time as the Main Master (e.g. may be connected to the I3C bus when power is applied to the system). In that case, the Main Master might pull SDA Low even before the I3C bus has been started, assuming that SCL and SDA are being pulled up. If a Main Master needs 1ms or more to start acting on the I3C bus, then that Main Master is able to accommodate the situation of SDA being held Low when it is ready to initialize the I3C bus, or it may instead delay pulling SDA High, and/or pulling SCL High, until it is ready.

# 2.1.4.4. Data Packet Generator HDR-DDR

This block generates an I3C HDR-DDR mode data signals. The HDR-DDR Protocol uses the same signaling as SDR, but operates with SDA changing after each SCL edge. Each Command Word and each Data Word is 20 bits in length (20 clock edges) including a two-bit Preamble. HDR-DDR Command Words indicate the direction of data movement: either Write (Master to Slave), or Read (Slave to Master). After the Command Word, zero or more Data Words are sent by the Master or by the Slave (unless NACK-ed) until done, followed by the CRC Word (unless NACK-ed).

In HDR-DDR Mode, just as in SDR Mode, only the I3C bus Master drives the SCL line. For Commands, the SDA line is driven by the Master. For Data, the SDA line is driven either by the Slave or by the Master, depending on the Command direction (Bus Turnaround).

There are three points of Bus Turnaround (between Master and Slave) with HDR-DDR Mode:

- After a Read Command from the Master, the Slave drives SDA to indicate that the Slave plans to return Data.

- After the end of Data from the Slave for a Read Command, the Master drives SDA again.

- There is an optional Bus Turnaround before Data Words are returned by the Slave, allowing the Master to prematurely terminate a Read.

# 2.1.5. Bus Characteristics Register (BCR)

Each I3C device that is connected to the I3C bus has an associated read-only Bus Characteristics Register (BCR). This read-only register describes the I3C compliant device's role and capabilities for use in Dynamic Address assignment and Common Command Codes.

| Bit | Name                       | Description                                                             |

|-----|----------------------------|-------------------------------------------------------------------------|

| 7   | Device Role [1]            | 2'b00 – I3C Slave                                                       |

|     |                            | 2'b01 – I3C Master                                                      |

| 6   | Device Role [0]            | 2'b10 – Reserved for future definition                                  |

|     |                            | 2'b11 – Reserved for future definition                                  |

| 5   | SDR Only / SDR and         | 0 – SDR only                                                            |

| ר   | HDR-DDR Capable            | 1 – HDR-DDR Capable                                                     |

| 4   | Bridge Identifier          | 0 – Not a Bridge device                                                 |

| 4   | Bridge identifier          | 1 – Is a Bridge device                                                  |

| 3   | Offling Canable            | 0 – Device always responds to I3C bus commands                          |

| 5   | Offline Capable            | 1 – Device not always responds to I3C bus commands                      |

|     |                            | 0 – No data byte follows the accepted IBI                               |

| 2   | IBI Payload                | 1 – Mandatory one or more data bytes follow the accepted IBI. Data byte |

|     |                            | continuation is indicated by T-Bit                                      |

| 1   | IBI Request Capable        | 0 – Not Capable                                                         |

| Ŧ   | ibi nequest capable        | 1 – Capable                                                             |

| 0   | May Data Grand Linsitation | 0 – No Limitation                                                       |

| 0   | Max Data Speed Limitation  | 1 – Limitation                                                          |

<sup>© 2019-2020</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

# 2.1.6. Device Characteristics Register (DCR)

Each I3C device that is connected to the I3C bus has an associated read-only Device Characteristics Register (DCR). This read-only register describes the I3C compliant device type (e.g. accelerometer, gyroscope, etc.) for use in Dynamic Address assignment and Common Command Codes.

| Bit | Name          | Description                                                       |

|-----|---------------|-------------------------------------------------------------------|

| 7   | Device ID [7] | 255 available codes for describing the type of sensor, or device. |

| 6   | Device ID [6] | Examples: Accelerometer, gyroscope, composite devices.            |

| 5   | Device ID [5] | Default value is 8'b0: Generic device                             |

| 4   | Device ID [4] |                                                                   |

| 3   | Device ID [3] |                                                                   |

| 2   | Device ID [2] |                                                                   |

| 1   | Device ID [1] |                                                                   |

| 0   | Device ID [0] |                                                                   |

Table 2.2. Device Characteristics Register

# 2.1.7. Legacy Virtual Register (LVR)

Each legacy  $I^2C$  device that can be connected to the I3C bus has an associated read-only Legacy Virtual Register (LVR) describing the device's significant features. Since these are legacy  $I^2C$  devices, it is understood that this register exists virtually, for example as part of the device's driver. When legacy  $I^2C$  devices are present on an I3C bus, LVR data determines allowed Modes and maximum SCL clock frequency. All LVRs are established by the higher-level entity controlling the I3C bus and transferred to the I3C bus Main Master prior to bus configuration. The LVR content for all  $I^2C$  devices is always known by the Main Master.

| Bit | Name                                                                                                                                  | Description                                                   |

|-----|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| 7   | Legacy I <sup>2</sup> C only [2]                                                                                                      | 3'b000 – Index 0                                              |

| 6   | Legacy I <sup>2</sup> C only [1]                                                                                                      | 3'b001 – Index 1                                              |

|     |                                                                                                                                       | 3'b010 – Index 2                                              |

|     |                                                                                                                                       | 3'b011 – Index 3 (Reserved)                                   |

| _   | Legacy I <sup>2</sup> C only [0]                                                                                                      | 3'b100 – Index 4 (Reserved)                                   |

| 5   |                                                                                                                                       | 3'b101 – Index 5 (Reserved)                                   |

|     |                                                                                                                                       | 3'b110 – Index 6 (Reserved)                                   |

|     |                                                                                                                                       | 3'b111 – Index 7 (Reserved)                                   |

| 4   | I <sup>2</sup> C Mode Indicator                                                                                                       | 0 – I <sup>2</sup> C Fm+                                      |

| 4   |                                                                                                                                       | 1 – I <sup>2</sup> C Fm                                       |

| 3   | Reserved                                                                                                                              |                                                               |

| 2   | Reserved         15 available codes for describing the device capabilitie           Reserved         function on the sensors' system. | 15 available codes for describing the device capabilities and |

| 1   |                                                                                                                                       | function on the sensors' system.                              |

| 0   | Reserved                                                                                                                              |                                                               |

# Table 2.3. Legacy Virtual Register

# 2.2. Signal Description

Table 2.4 lists the input and output signals for I3C Master IP Core along with their descriptions.

# Table 2.4. Ports Description

| Name                            | Direction | Description                                                                                                                                                                                                                                                                                                                       |

|---------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Clock and Res            | et        |                                                                                                                                                                                                                                                                                                                                   |

| clk_i                           | Input     | System Clock                                                                                                                                                                                                                                                                                                                      |

| rst_n_i                         | Input     | Master core reset                                                                                                                                                                                                                                                                                                                 |

| Master Clock                    |           |                                                                                                                                                                                                                                                                                                                                   |

| clk_50m_i                       | Input     | Master core clock                                                                                                                                                                                                                                                                                                                 |

| clk_100m_i                      | Input     | Incorporated Slave core clock                                                                                                                                                                                                                                                                                                     |

| I3C Interface                   |           |                                                                                                                                                                                                                                                                                                                                   |

| scl io                          | In/Out    | SCL input for listening, SCL output for driving                                                                                                                                                                                                                                                                                   |

| sda io                          | In/Out    | SDA input to the master from the slave, SDA output from the master to the slave                                                                                                                                                                                                                                                   |

| LMMI Interface <sup>1</sup>     | , • • •   |                                                                                                                                                                                                                                                                                                                                   |

| lmmi_resetn_i                   | Input     | Reset (active low)<br>Resets the LMM interface and sets registers to their default values. Does not reset the<br>internals of the Hard IP block.                                                                                                                                                                                  |

| lmmi_request_i                  | Input     | Start transaction                                                                                                                                                                                                                                                                                                                 |

| lmmi_wr_rdn_i                   | Input     | Write = HIGH, Read = LOW                                                                                                                                                                                                                                                                                                          |

| Immi_offset_i[n:0]              | Input     | Offset (0-31 bits) – register offset within the slave, starting at offset 0.<br>Bit width is hard IP dependent.                                                                                                                                                                                                                   |

| lmmi_wdata_i[n:0]               | Input     | Write data (0-16 bits)<br>Bit width is hard IP dependent.                                                                                                                                                                                                                                                                         |

| Immi_rdata_o[n:0]               | Output    | Read data (0-16 bits)<br>Bit width is hard IP dependent.                                                                                                                                                                                                                                                                          |

| lmmi_rdata_valid_o              | Output    | Read transaction is complete and Immi_rdata[] contains valid data.                                                                                                                                                                                                                                                                |

| Immi_ready_o                    | Output    | Slave is ready to start a new transaction. Slave can insert wait states by holding this signal<br>low.<br>This signal is optional in hardware and mandatory in RTL soft wrappers. Hardware slaves<br>may omit this signal if they do not need wait states. For zero-wait-state slaves, the soft<br>wrapper ties this signal high. |

| LINTR Interface                 | L         |                                                                                                                                                                                                                                                                                                                                   |

| int_o                           | Output    | Interrupt. Hard IP block has an interrupt, which needs to be serviced.<br>Active high, level sensitive. Stays high while as any enabled interrupt is pending.                                                                                                                                                                     |

| AHB-Lite Interface <sup>2</sup> |           |                                                                                                                                                                                                                                                                                                                                   |

| ahbl_hsel_i                     | Input     | AHB-Lite Select signal                                                                                                                                                                                                                                                                                                            |

| ahbl_hready_i                   | Input     | AHB-Lite Ready Input signal                                                                                                                                                                                                                                                                                                       |

| ahbl_haddr_i[31:0]              | Input     | AHB-Lite Address signal (9 LSB used)                                                                                                                                                                                                                                                                                              |

| ahbl_hburst_i[2:0]              | Input     | AHB-Lite Burst Type signal                                                                                                                                                                                                                                                                                                        |

| ahbl_hsize_i[2:0]               | Input     | AHB-Lite Transfer Size signal                                                                                                                                                                                                                                                                                                     |

| ahbl_hmastlock_i                | Input     | AHB-Lite Lock signal                                                                                                                                                                                                                                                                                                              |

| ahbl_hprot_i[3:0]               | Input     | AHB-Lite Protection Control signal                                                                                                                                                                                                                                                                                                |

| ahbl_htrans_i[1:0]              | Input     | AHB-Lite Transfer Type signal                                                                                                                                                                                                                                                                                                     |

| ahbl_hwrite_i                   | Input     | AHB-Lite Direction signal. Write = High, Read = Low                                                                                                                                                                                                                                                                               |

| ahbl_hwdata_i[31:0]             | Input     | AHB-Lite Write Data signal (8 LSB used)                                                                                                                                                                                                                                                                                           |

| ahbl_hreadyout_o                | Output    | AHB-Lite Ready Output signal                                                                                                                                                                                                                                                                                                      |

| ahbl_hrdata_o[31:0]             | Output    | AHB-Lite Read Data signal (8 LSB used)                                                                                                                                                                                                                                                                                            |

| ahbl_hresp_o                    | Output    | AHB-Lite Transfer Response signal                                                                                                                                                                                                                                                                                                 |

© 2019-2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Name                       | Direction                  | Description                        |  |

|----------------------------|----------------------------|------------------------------------|--|

| APB Interface <sup>3</sup> | APB Interface <sup>3</sup> |                                    |  |

| apb_paddr_i[31:0]          | Input                      | APB Address signal. (9 LSB used)   |  |

| apb_psel_i                 | Input                      | APB Select signal                  |  |

| apb_penable_i              | Input                      | APB Enable signal                  |  |

| apb_pwrite_i               | Input                      | APB Direction signal               |  |

| apb_pwdata_i[31:0]         | Input                      | APB Write Data signal (8 LSB used) |  |

| apb_pready_o               | Output                     | APB Ready signal                   |  |

| apb_prdata_o[31:0]         | Output                     | APB Read Data signal (8 LSB used)  |  |

| apb_pslverr_o              | Output                     | APB Slave Error signal             |  |

| Direct Sensor Interfac     | Direct Sensor Interface    |                                    |  |

| sdr_o                      | Output                     | 8-bit ODR data in KSPS             |  |

Notes:

- 1. LMMI Interface is only available when selected from the user interface.

- 2. AHB-Lite Interface is only available when selected from the user interface. Refer to AMBA 3 AHB-Lite Protocol Specification for details of the protocol.

- 3. APB Interface is only available when selected from the user interface. Refer to AMBA 3 APB Protocol v1.0 Specification for details of the protocol.

# 2.3. Attributes Summary

Table 2.5 provides the list of user-selectable and compile time configurable parameters for the I3C Master IP Core.Attributes are described in Table 2.6. The parameter settings are specified using I3C Master IP Core Configuration userinterface in Lattice Radiant.

| Attribute                                            | Selectable Values                | Default     | Dependency on Other Attributes                      |

|------------------------------------------------------|----------------------------------|-------------|-----------------------------------------------------|

| General                                              |                                  |             |                                                     |

| CPU Interface                                        |                                  |             |                                                     |

| Interface                                            | LMMI, APB, AHBL                  | LMMI        | _                                                   |

| Bus Characteristics                                  |                                  |             |                                                     |

| Device Role                                          | Main Master, Secondary<br>Master | Main Master | _                                                   |

| Bus Type                                             | HDR-capable only                 | HDR-capable | _                                                   |

| HDR Type                                             | DDR                              | DDR         | Bus Type = HDR capable                              |

| Offline Capable                                      | Not Checked                      | Not Checked | _                                                   |

| IBI Capable                                          | Checked, Not Checked             | Checked     | Device Role = Secondary Master                      |

| IBI: Number of bytes in a single sample [0–128]      | 0–128                            | 2           | IBI Capable = True,<br>Receive Buffer Address Width |

| Hot-Join Capable                                     | Checked, Not Checked             | Checked     | Device Role = Secondary Master                      |

| Stall Support                                        | Checked, Not Checked             | Checked     | _                                                   |

| Max Data Speed Limitation                            | Checked                          | Checked     | Device Role = Secondary master                      |

| Number of Dynamic Address<br>Devices on Bus [0–8]    | 08                               | 1           | _                                                   |

| Number of Static Address I3C<br>Devices on Bus [0–8] | 08                               | 0           | _                                                   |

## Table 2.5. Attributes Table

| Attribute                                      | Selectable Values  | Default | Dependency on Other Attributes                                                |

|------------------------------------------------|--------------------|---------|-------------------------------------------------------------------------------|

| Settings                                       |                    | ·       |                                                                               |

| I3C Dynamic Address Table                      |                    |         |                                                                               |

| I3C Device 1 DA (hex) [4–7]                    | 4–7D               | 35      | Grayed out when Number of Dynamic<br>Address Devices on Bus is less than 1    |

| I3C Device 2 DA (hex) [4–7]                    | 4–7D               | 4A      | Grayed out when Number of Dynamic<br>Address Devices on Bus is less than 2    |

| I3C Device 3 DA (hex) [4–7]                    | 4–7D               | 4C      | Grayed out when Number of Dynamic<br>Address Devices on Bus is less than 3    |

| I3C Device 4 DA (hex) [4–7]                    | 4–7D               | 5C      | Grayed out when Number of Dynamic<br>Address Devices on Bus is less than 4    |

| I3C Device 5 DA (hex) [4–7]                    | 4–7D               | 5D      | Grayed out when Number of Dynamic<br>Address Devices on Bus is less than 5    |

| I3C Device 6 DA (hex) [4–7]                    | 4–7D               | 68      | Grayed out when Number of Dynamic<br>Address Devices on Bus is less than 6    |

| I3C Device 7 DA (hex) [4–7]                    | 4–7D               | 6A      | Grayed out when Number of Dynamic<br>Address Devices on Bus is less than 7    |

| I3C Device 8 DA (hex) [4–7]                    | 4–7D               | 6C      | Grayed out when Number of Dynamic<br>Address Devices on Bus is less than 8    |

| I3C Static Address Table                       |                    |         |                                                                               |

| I3C Device 1 SA (hex) [4–7D]                   | 4–7D               | 9       | Grayed out when Number of Static Address<br>I3C Devices on Bus is less than 1 |

| I3C Device 2 SA (hex) [4–7D]                   | 4–7D               | А       | Grayed out when Number of Static Address<br>I3C Devices on Bus is less than 2 |

| I3C Device 3 SA (hex) [4–7D]                   | 4–7D               | В       | Grayed out when Number of Static Address<br>I3C Devices on Bus is less than 3 |

| I3C Device 4 SA (hex) [4–7D]                   | 4–7D               | с       | Grayed out when Number of Static Address<br>I3C Devices on Bus is less than 4 |

| I3C Device 5 SA (hex) [4–7D]                   | 4–7D               | D       | Grayed out when Number of Static Address<br>I3C Devices on Bus is less than 5 |

| I3C Device 6 SA (hex) [4–7D]                   | 4–7D               | E       | Grayed out when Number of Static Address<br>I3C Devices on Bus is less than 6 |

| I3C Device 7 SA (hex) [4–7D]                   | 4–7D               | F       | Grayed out when Number of Static Address<br>I3C Devices on Bus is less than 7 |

| I3C Device 8 SA (hex) [4–7D]                   | 4–7D               | 10      | Grayed out when Number of Static Address<br>I3C Devices on Bus is less than 8 |

| Device Characteristics: Run-Time C             | onfigurable        |         |                                                                               |

| DCR Value (hex) [0–FF]                         | 0 - FF             | 0       | Device Role = Secondary Master                                                |

| Static Address Enable                          | Checked, Unchecked | Checked | Device Role = Secondary Master                                                |

| Static Address (hex) [4–7D]`                   | 4–7D               | 28      | Static Address Enable = True and device<br>Role = Secondary Master            |

| Dynamic Address of Main Master<br>(hex) [4–7D] | 4–7D               | 8       | Device Role = Main Master                                                     |

| Manufacturer ID [0–32767]                      | 0–32767            | 414     | Device Role = Secondary Master                                                |

| Part ID [0–65535]                              | 0–65535            | 1       | Device Role = Secondary Master                                                |

| Instance ID [0–15]                             | 0–15               | 1       | Device Role = Secondary Master                                                |

| Additional ID [0-4095]                         | 0–4095             | 0       | Device Role = Secondary Master                                                |

| Clocks                                         |                    |         |                                                                               |

| System Clock Frequency (MHz)<br>[80–125]       | 80 - 125           | 100     | -                                                                             |

| I3C Core Clock Frequency (MHz)                 | N/A                | 50      | Greyed out                                                                    |

|                                                |                    |         | I                                                                             |

<sup>© 2019-2020</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Attribute                            | Selectable Values              | Default | Dependency on Other Attributes                |

|--------------------------------------|--------------------------------|---------|-----------------------------------------------|

| Slave Mode Timing Characteristics    |                                |         |                                               |

| Max Write Data Speed                 | Max, 8MHz, 6MHz, 4MHz,<br>2MHz | Max     | Device Role = Secondary Master                |

| Max Read Data Speed                  | Max, 8MHz, 6MHz, 4MHz,<br>2MHz | Max     | Device Role = Secondary Master                |

| Max Clock to Data Turnaround<br>Time | 8ns, 9ns, 10ns, 11ns, 12ns     | >12 ns  | Greyed out, Device Role = Secondary<br>Master |

| Storage Characteristics              |                                |         |                                               |

| Max Write Address Depth [8–256]      | 8 - 256                        | 256     | Device Role = Secondary Master                |

| Max Read Address Depth [16–256]      | 16 - 256                       | 256     | Device Role = Secondary Master                |

# Table 2.6. Attributes Descriptions

| Attribute                                      | Description                                                                                                                                                                                                                                           |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General                                        |                                                                                                                                                                                                                                                       |

| CPU Interface                                  |                                                                                                                                                                                                                                                       |

| Interface                                      | Selects memory-mapped interface from the list for register access by the host<br>Available values: LMMI (default), APB, AHBL                                                                                                                          |

| Bus Characteristics                            |                                                                                                                                                                                                                                                       |

| Device Role                                    | Selects the role of device according to the I3C Specification v1.0.                                                                                                                                                                                   |

| Bus Type                                       | HDR capability. Always capable (common state machine for all modes). Grayed out.                                                                                                                                                                      |

| HDR Type                                       | HDR supported modes. Only DDR is supported. Grayed out                                                                                                                                                                                                |

| Offline Capable                                | Offline capability support. Currently grayed out, not supported, since the related data must be stored in NVM.                                                                                                                                        |

| IBI Capable                                    | IBI capability selector for Secondary Master.<br>For the Main Master IBI is always supported.                                                                                                                                                         |

|                                                | IBI payload size. Must be less or equal to 2**(Receive Buffer Address Width).                                                                                                                                                                         |

| IBI: Number of bytes in a single sample        | I.e. Main Master's maximum IBI payload size acceptance depends on Master's Receive Buffer<br>Address Width.<br>After IBI request processing first location in FIFO is the DA of the Slave, which requested the<br>interrupt.                          |

| Hot-Join Capable                               | HJ capability for Secondary Master.<br>Main Master always supports HJ.                                                                                                                                                                                |

| Stall Support                                  | If checked, extends T-bit by two core clock cycles. Recommended for robust I3C bus operation.                                                                                                                                                         |

| Max Data Speed<br>Limitation                   | Secondary master feature. Checked for not supported TSL/TSP modes. Grayed out.                                                                                                                                                                        |

| Number of Dynamic<br>Address Devices on Bus    | Activates "I3C Dynamic Address Table" fields for editing.<br>Aggregate number of DA capable and SA capable devices must be from 1 to 8.                                                                                                               |

| Number of Static Address<br>I3C Devices on Bus | Activates "I3C Static Address Table" fields for editing.<br>Aggregate number of DA capable and SA capable devices must be from 1 to 8.                                                                                                                |

| Settings                                       |                                                                                                                                                                                                                                                       |

| I3C Dynamic Address Table                      |                                                                                                                                                                                                                                                       |

| I3C Device 1 DA                                | I3C DA address to be assigned to the Slave device during address assignment procedure. Device 1 default is 0x35.<br>Allowable address range is 0x04-0x7D.<br>User must choose the addresses based on recommendations given in I3C Specification v1.0. |

| I3C Device 2 DA                                | Device 2 default is 0x4A.                                                                                                                                                                                                                             |

| I3C Device 3 DA                                | Device 3 default is 0x4C.                                                                                                                                                                                                                             |

| I3C Device 4 DA                                | Device 4 default is 0x5C.                                                                                                                                                                                                                             |

| I3C Device 5 DA                                | Device 5 default is 0x5D.                                                                                                                                                                                                                             |

|                                                |                                                                                                                                                                                                                                                       |

<sup>© 2019-2020</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Attribute                               | Description                                                                                                                                                        |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I3C Device 6 DA                         | Device 6 default is 0x68.                                                                                                                                          |

| I3C Device 7 DA                         | Device 7 default is 0x6A.                                                                                                                                          |

| I3C Device 8 DA                         | Device 8 default is 0x6C.                                                                                                                                          |

| I3C Static Address Table                |                                                                                                                                                                    |

|                                         | I3C SA address of the Slave device, if known. Device 1 default is 0x09.                                                                                            |

|                                         | Allowable address range is 0x04-0x7D.                                                                                                                              |

| I3C Device 1 SA                         | Currently these values are stored in the Master registers for being accessible from the host side and                                                              |

|                                         | not used in any other way.                                                                                                                                         |

| I3C Device 2 SA                         | Device 2 default is 0x0A.                                                                                                                                          |

| I3C Device 3 SA                         | Device 3 default is 0x0B.                                                                                                                                          |

| I3C Device 4 SA                         | Device 4 default is 0x0C.                                                                                                                                          |

| I3C Device 5 SA                         | Device 5 default is 0x0D.                                                                                                                                          |

| I3C Device 6 SA                         | Device 6 default is 0x0E.                                                                                                                                          |

| I3C Device 7 SA                         | Device 7 default is 0x0F.                                                                                                                                          |

| I3C Device 8 SA                         | Device 8 default is 0x10.                                                                                                                                          |

| Device Characteristics: Run             | -Time Configurable                                                                                                                                                 |

|                                         | Device Characteristics Register. It is recommended to assign a value to this register according to the                                                             |

| DCR Value (hex)                         | list of the devices, which can be found at :                                                                                                                       |

|                                         | https://www.mipi.org/MIPI_I3C_device_characteristics_register.                                                                                                     |

|                                         | If Secondary Master, a SA may be assigned to device, which is accessible to the host.                                                                              |

| Static Address Enable                   | Main Master may assign DA to this device using the SA bypassing the DAA procedure, if knows its SA                                                                 |

|                                         | (designer must pass the SA to the Main Master host application).                                                                                                   |

| Static Address (hex)                    | If Secondary Master and "Static Address Enable" is checked, defines device's SA.                                                                                   |