## **MP2116** 2A, 6V, 100% Duty Cycle Synchronous

Step-Down Converter with 0.5A LDO

The Future of Analog IC Technology

## DESCRIPTION

The MP2116 is an internally compensated 1.25MHz, 2A synchronous step-down switching DC-DC converter plus a standalone low-input voltage, 0.5A low dropout (LDO) linear regulator. It is ideal for powering portable equipment that operates from a single cell Lithium-Ion (Li+) Battery. The MP2116 can provide up to 2A to the switcher output, and 0.5A load current to the LDO output from a 2.5V to 6V input voltage. Both output voltages can be regulated as low as 0.6V.

2A The Synchronous switcher features integrated high-side and low-side switch for high efficiency and small footprint. With peak current mode control and internal compensation. the MP2116 is stable with ceramic capacitors. Fault condition protection includes cycle-bycycle current limiting and thermal shutdown.

The standalone low-input voltage 0.5A LDO is used to power noise sensitive circuitry. The LDO's separate input supply pin (IN2) can be connected to the switcher output to reduce power dissipation and noise from the main switcher.

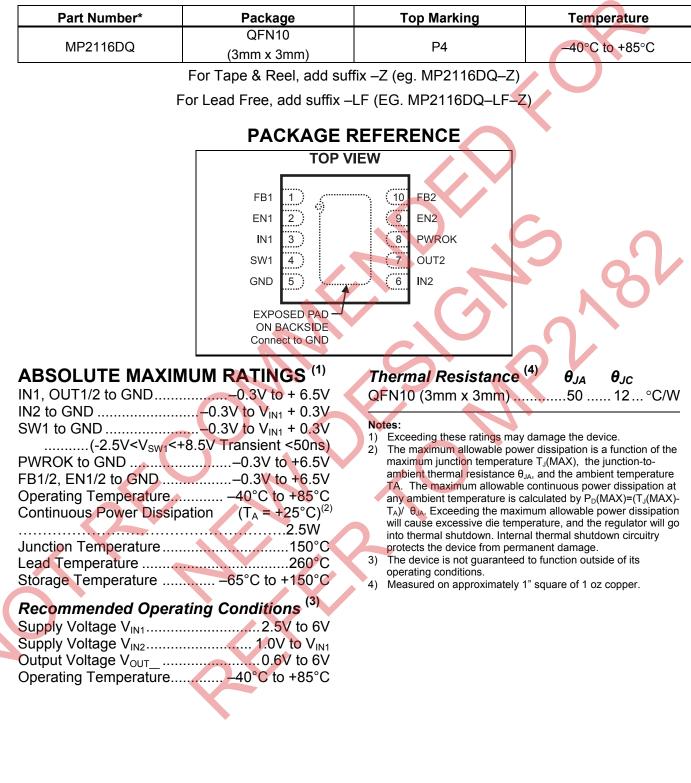

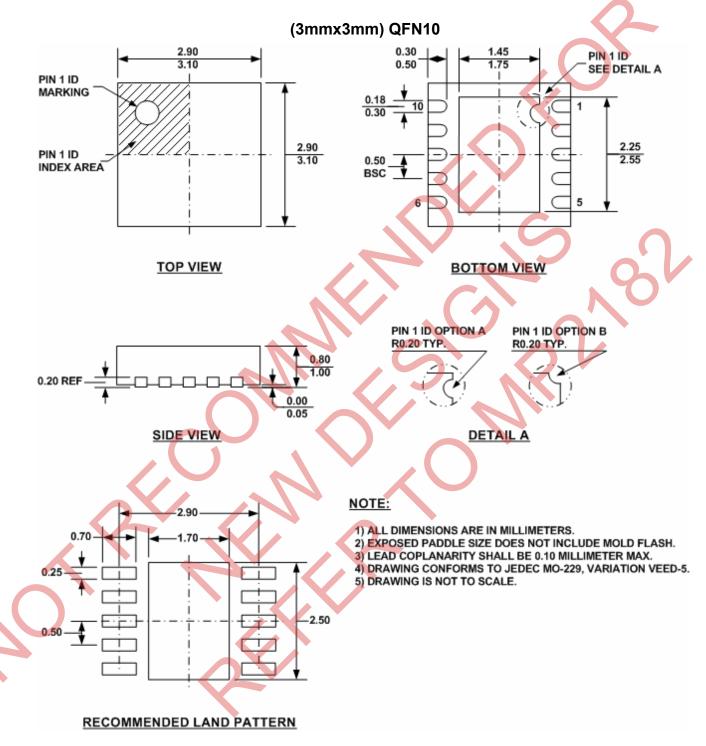

MP2116 is available in the small 10-pin 3mmx3mm QFN package.

## **FEATURES**

- 100% Duty Cycle Low Dropout Operation (High-Side PFET)

- 2A Switcher Output Current at VIN=3V

- Internal Power MOSFET Switches

- Stable with Ceramic Capacitors

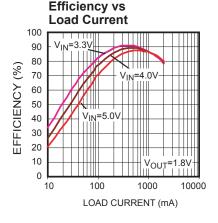

- Up to 95% Efficiency for Switcher

- 1.25MHz Switching Frequency

- Internal Soft-start for Switcher

- 2.5V to 6V Input Range, for Switcher

- 1V to V<sub>IN1</sub> Input Range, for LDO •

- 0.5A LDO Output Current

- 1µA Shutdown Current

- Thermal Shutdown

- Cycle-by-Cycle Over Current Protection

- Short Circuit Protection

- Power OK Output

- Available in 10-Pin QFN Package

### APPLICATIONS

- **DVD+/-RW Drives**

- Smart Phones

- PDAs

- **Digital Cameras**

- Portable Instruments

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green status, please visit MPS website under Products, Quality Assurance page. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication © 2013 MPS. All Rights Reserved.

## **ORDERING INFORMATION**

## ELECTRICAL CHARACTERISTICS (5)

$V_{IN1/2} = V_{EN1/2} = 3.6V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.

| Parameters                          | Condition                                                                | Min   | Тур               | Max              | Units |  |

|-------------------------------------|--------------------------------------------------------------------------|-------|-------------------|------------------|-------|--|

| No Load Supply Current              | $V_{IN1/2} = 3.6V, V_{EN1} = 3.6V, V_{EN2} = 0V$<br>$V_{FB1} = 0.58V$    |       | 300               | 500              | μΑ    |  |

| No Load Supply Current              | $V_{IN1/2}$ = 3.6V, $V_{EN1}$ =0V, $V_{EN2}$ =3.6V<br>$V_{FB2}$ = 0.62V  |       | 70                | 120              | μΑ    |  |

| Shutdown Current                    | $V_{EN1/2} = 0V, V_{IN1/2} = 6V$                                         |       | 0.01              | 1                | μA    |  |

| Thermal Shutdown Trip Threshold     | Hysteresis = 20°C                                                        |       | 150               |                  | °C    |  |

| PWROK Upper Trip Threshold          | FB1/2 with respect to the Nominal Value                                  |       | 10                |                  | %     |  |

| PWROK Lower Trip Threshold          | FB1/2 with respect to the Nominal Value                                  |       | -10               |                  | %     |  |

| PWROK Output Lower Voltage          | I <sub>SINK</sub> = 5mA                                                  |       |                   | 0.3              | V     |  |

| PWROK Deglitch Timer (FB1)          | Switching Regulator                                                      |       | 50                |                  | μs    |  |

| PWROK Deglitch Timer (FB2)          | LDO                                                                      |       | 150               |                  | μs    |  |

| EN1/2 Trip Threshold                | –40°C ≤ T <sub>A</sub> ≤ +85°C                                           | 0.3   | 0.96              | 1.5              | V     |  |

| EN1/2 Pull Down Resistor            |                                                                          |       | 1                 |                  | MΩ    |  |

| Switching Regulator                 |                                                                          |       | $\mathbf{\Gamma}$ |                  | •     |  |

| IN1 Under Voltage Lockout Threshold | d Rising Edge, Hysteresis=0.3V                                           | 1.90  | 2.15              | 2.40             | V     |  |

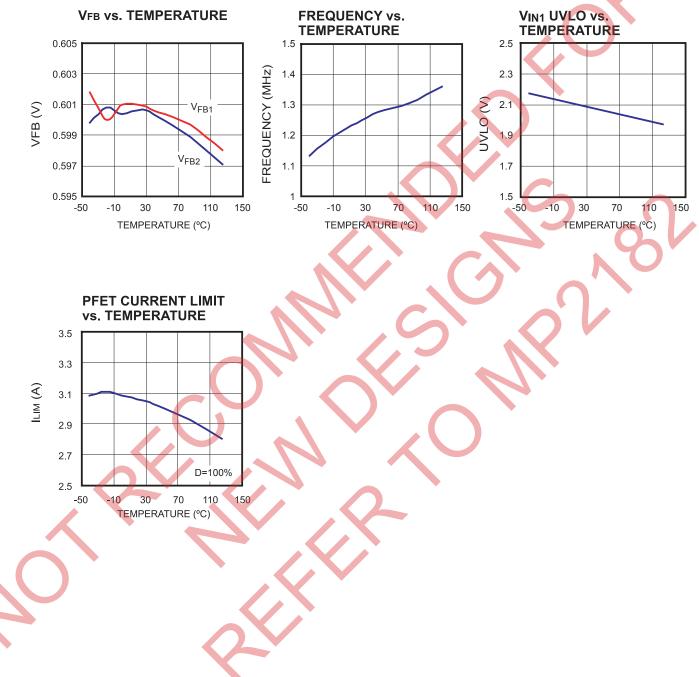

| Regulated FB1Voltage                | T <sub>A</sub> = +25°C                                                   | 0.588 | 0.600             | 0.612            | — V   |  |

| Regulated i Di Voltage              | –40°C ≤ T <sub>A</sub> ≤ +85°C                                           | 0.582 | 0.600             | 0.618            |       |  |

| FB1 Input Bias Current              | V <sub>FB1</sub> = 0.62V                                                 | -50   | -2                | +50              | nA    |  |

| SW1 PFET On Resistance              | I <sub>sw1</sub> = 100mA                                                 |       | 0.20              |                  | Ω     |  |

| SW1 NFET On Resistance              | I <sub>sw1</sub> = -100mA                                                | •     | 0.15              |                  | Ω     |  |

| SW1 Leakage Current                 | V <sub>EN</sub> = 0V, V <sub>IN</sub> = 6V<br>V <sub>SW</sub> = 0V or 6V | -5    |                   | +5               | μA    |  |

| SW1 PFET Peak Current Limit         | Duty Cycle = 100%,<br>Current Pulse Width < 1ms                          | 2.2   | 3.1               | 4.0              | Α     |  |

| Oscillator Frequency                |                                                                          | 1.00  | 1.25              | 1.50             | MHz   |  |

| Linear Regulator LDO                |                                                                          |       |                   |                  |       |  |

| IN2 Input Range                     | $I_{LOAD2} = 10 \text{mA}, V_{OUT2} = V_{FB2}$                           | 1     |                   | V <sub>IN1</sub> | V     |  |

| Regulated FB2 Voltage               | $T_A = +25^{\circ}C$                                                     | 0.588 | 0.600             | 0.612            | - V   |  |

|                                     | $-40^{\circ}C \le T_A \le +85^{\circ}C$                                  | 0.582 | 0.600             | 0.618            |       |  |

| FB2 Input Bias Current              | V <sub>FB2</sub> = 0.6V                                                  | -50   | -2                | +50              | nA    |  |

| OUT2 Maximum Output Current         | V <sub>OUT2</sub> = 1.2V                                                 | 500   | -                 |                  | mA    |  |

| OUT2 Qurrent Limit                  | V <sub>OUT2</sub> = 0V                                                   | 600   | 700               |                  | mA    |  |

| Dropout Voltage                     | I <sub>LOAD</sub> = 0.15A, V <sub>OUT2</sub> = 1.2V                      |       | 100               |                  | mV    |  |

Notes:

5) Production test at +25°C. Specifications over the temperature range are guaranteed by design and characterization.

| mps_ | IP |

|------|----|

|------|----|

| FIN FUNCTIONS |                      |                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|---------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin #         | Name                 | Description                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 1             | FB1                  | Feedback Input for the switcher output VOUT1.                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 2             | EN1                  | Enable Input for the switcher.                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 3             | IN1                  | Main Input Supply Pin. Input supply for both the switcher and the low dropout (LDO) linear regulator, except the LDO output power device.                                                                                                                                                                                                                                                         |  |  |

| 4             | SW1                  | Switch node of the switcher.                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 5             | GND<br>(Exposed Pad) | Ground. Exposed pad must be connected to GND pin.                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 6             | IN2                  | Input Supply for the linear regulator LDO output power device. Bypass with a 2.2uF from IN2 to GND.                                                                                                                                                                                                                                                                                               |  |  |

| 7             | OUT2                 | Output of the 500mA LDO. The LDO is designed to be stable with an external 4.7µF ceramic capacitor (minimum).                                                                                                                                                                                                                                                                                     |  |  |

| 8             | PWROK                | Power OK Open Drain Output. HIGH output indicates that both outputs are within $\pm 10\%$ of the regulation value. LOW output indicates that the output is out of $\pm 10\%$ window. PWROK is pulled down in shutdown. The PWROK window comparators have 50µs deglitch timer for the switcher and 150µs deglitch timer for the linear regulator LDO to avoid false trigger during load transient. |  |  |

| 9             | EN2                  | Enable Input for the low-dropout LDO                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 10            | FB2                  | Feedback Input for the LDO output VOUT2.                                                                                                                                                                                                                                                                                                                                                          |  |  |

## **PIN FUNCTIONS**

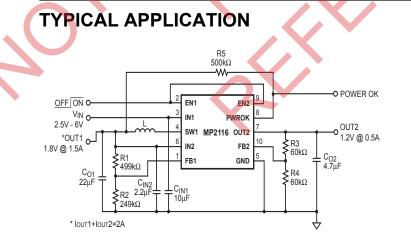

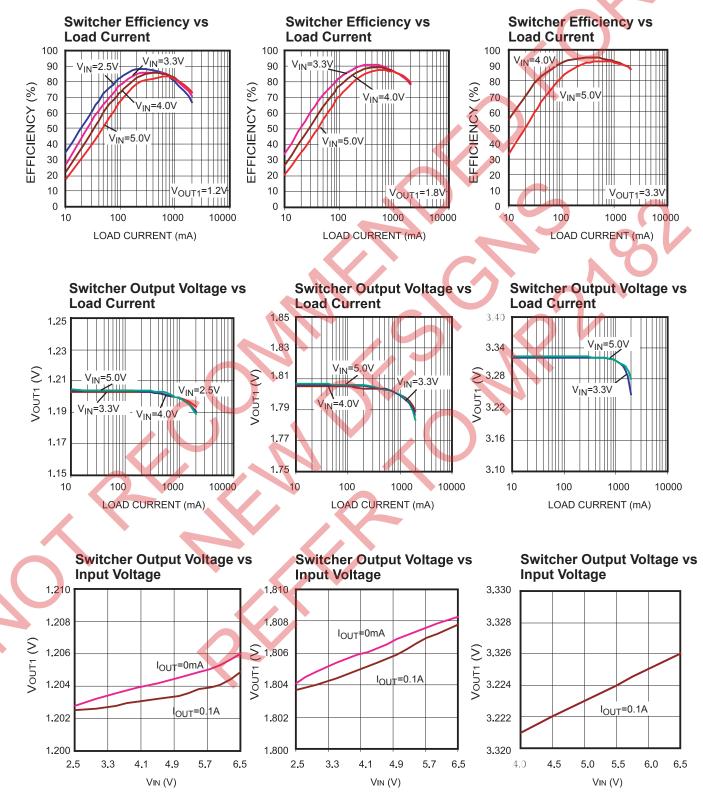

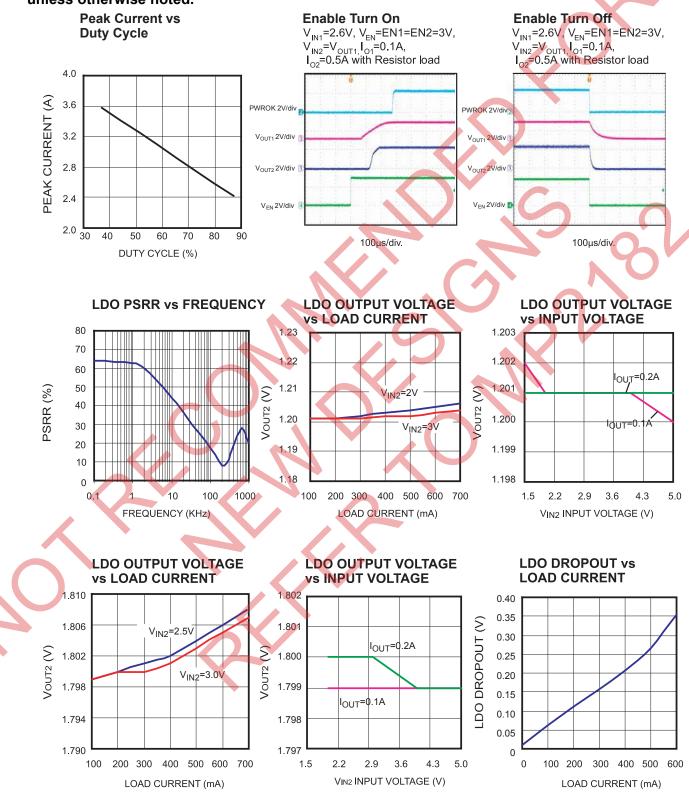

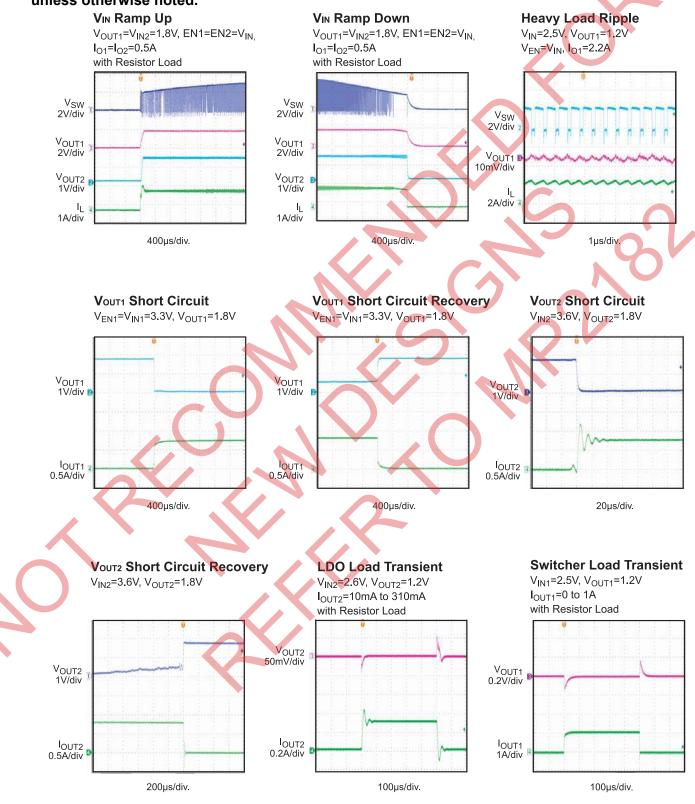

$V_{IN}$ =3.6V,  $V_{OUT1}$ =1.8V,  $V_{OUT2}$ =1.2V,  $C_{IN1}$ =10uF,  $C_{O1}$ =22uF,  $C_{IN2}$ =2.2uF,  $C_{O2}$ =4.7uF, L=1uH,  $T_A$ =25°C, unless otherwise noted.

$V_{IN}$ =3.6V,  $V_{OUT1}$ =1.8V,  $V_{OUT2}$ =1.2V,  $C_{IN1}$ =10uF,  $C_{O1}$ =22uF,  $C_{IN2}$ =2.2uF,  $C_{O2}$ =4.7uF, L=1uH,  $T_A$ =25°C, unless otherwise noted.

$V_{IN}$ =3.6V,  $V_{OUT1}$ =1.8V,  $V_{OUT2}$ =1.2V,  $C_{IN1}$ =10uF,  $C_{O1}$ =22uF,  $C_{IN2}$ =2.2uF,  $C_{O2}$ =4.7uF, L=1uH, T<sub>A</sub>=25°C, unless otherwise noted.

$V_{IN}$ =3.6V,  $V_{OUT1}$ =1.8V,  $V_{OUT2}$ =1.2V,  $C_{IN1}$ =10uF,  $C_{O1}$ =22uF,  $C_{IN2}$ =2.2uF,  $C_{O2}$ =4.7uF, L=1uH, Ta=25°C, unless otherwise noted.

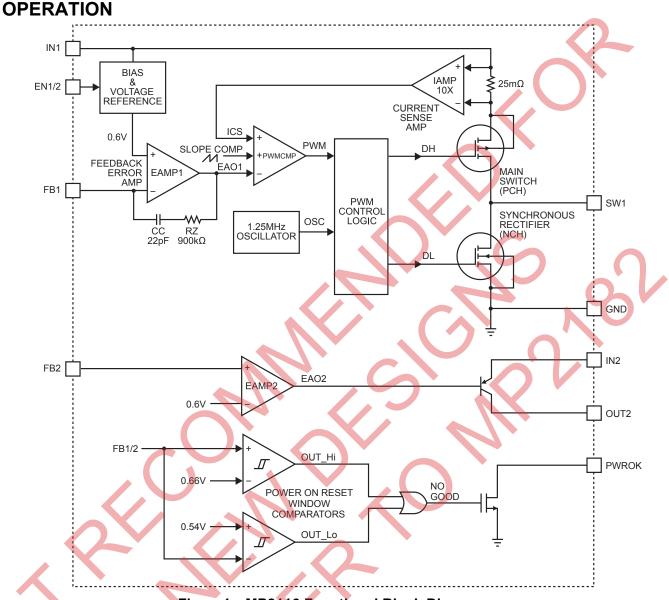

#### Figure1—MP2116 Functional Block Diagramm

The MP2116 is a 1.25MHz current mode 2A synchronous step-down switcher plus a low input 0.5A low dropout (LDO) linear regulator (see Figure1). The MP2116 is optimized for low voltage, Li-lon battery powered applications where high efficiency and small size are critical.

The MP2116 uses an external resistor divider to set both the switcher and LDO output voltage from 0.6V to 6V.

#### 2A Synchronous Step-Down Switcher

The switcher integrates both a main switch and a synchronous rectifier, which provides high efficiency and eliminates an external Schottky diode.

The duty cycle D of a step-down switcher is defined as:

$$D = T_{ON} \times f_{OSC} \times 100\% \approx \frac{V_{OUT}}{V_{IN}} \times 100\%$$

Where  $T_{ON}$  is the main switch on time and  $f_{OSC}$  is the oscillator frequency (1.25MHz).

#### **Current Mode PWM Control**

Slope compensated current mode PWM control provides stable switching and cycle-by-cycle current limiting for superior load and line response in addition to protection of the internal main switch and synchronous rectifier. The MP2116 switches at a constant frequency (1.25MHz) and regulates the output voltage. During each cycle the PWM comparator modulates the power transferred to the load by changing the inductor peak current based on the feedback error voltage. During normal operation, the main switch is turned on for a certain time to ramp the inductor current at each rising edge of the internal oscillator, and switched off when the peak inductor current is above the error voltage. When the main switch is off, the synchronous rectifier will be turned on immediately and stay on until the next cycle starts.

#### **Dropout Operation**

The MP2116 allows the main switch to remain on for more than one switching cycle and increases the duty cycle while the input voltage is dropping close to the output voltage. When the duty cycle reaches 100%, the main switch is held on continuously to deliver current to the output up to the PFET current limit. The output voltage then becomes the input voltage minus the voltage drop across the main switch and the inductor.

#### **Short Circuit Protection**

When the output is shorted to ground, the oscillator frequency is reduced to prevent the inductor current from increasing beyond the PFET current limit. The PFET current limit is also reduced to lower the short circuit current. The frequency and current limit will return to the normal values once the short circuit condition is removed and the feedback voltage reaches 0.6V.

#### Maximum Switcher Output Current

The MP2116 switcher can provide up to 2A output current, and operate down to 3V input voltage; however the maximum output current decreases at lower input voltage due to a large IR drop on the main switch and synchronous rectifier. The slope compensation signal reduces the peak inductor current as a function of the duty cycle to prevent sub-harmonic oscillations at duty cycles greater than 50%. Conversely, the current limit increases as the duty cycle decreases

#### Power OK

The MP2116 provides an open-drain PWROK output that goes high after both channels reach regulation during startup. PWROK goes low after one of the output channels goes out of regulation by  $\pm 10\%$  or when device enters shutdown. There are deglitch timers built in to avoid PWROK false triggered during load transient:  $50\mu$ S for the switcher and  $150\mu$ S for the LDO.

#### Low Input 0.5A Linear Regulator

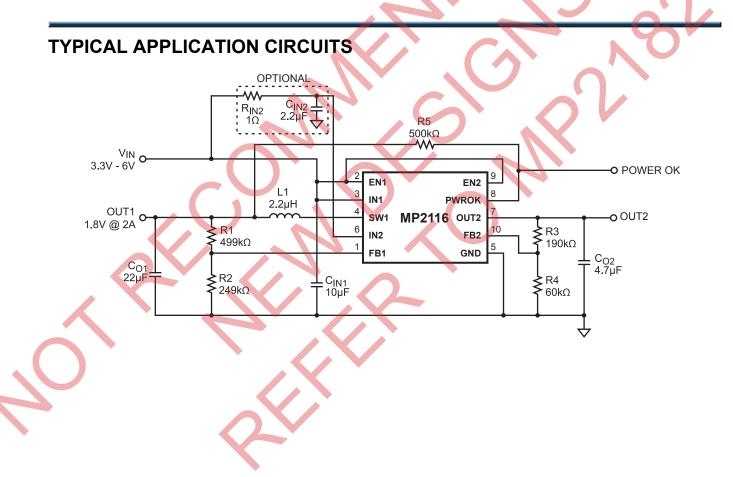

The low input 0.5A low dropout (LDO) linear regulator has separate input IN2 and output OUT2 pins for the internal power PNP device. The control circuitry of the LDO takes power from the main input supply IN1. Both IN1 and IN2 input supplies must be presented for the LDO working properly. The LDO power device input IN2 can be connected to the switcher output (Figure1) or directly to the main supply IN1 (Figure3). If the IN2 tied to the IN1, it is optional to insert a RC filter between IN1 and IN2. The RC filter will reduce switching noise coupling from IN1 to IN2 and power dissipation inside the MP2116

## **APPLICATION INFORMATION**

#### **Output Voltage Setting**

The external resistor divider sets the output voltage. The feedback resistor R1 of the switcher also sets the feedback loop bandwidth with the internal compensation capacitor (see Figure 1).

Choose R1 feedback resistor of the switcher between  $450k\Omega$  and  $800k\Omega$  for optimal transient response. R2 is then given by:

$$R2 = \frac{R1}{\frac{V_{OUT1}}{0.6V} - 1}$$

See Table1 for recommended R1 & R2 resistor values.

Choose R4 of the LDO between  $10k\Omega$  and  $100k\Omega$ . R3 is then given by:

$$R3 = R4 \times (\frac{V_{OUT2}}{0.6V} - 1)$$

#### Table 1—Resistor Selection vs. Output Voltage Setting

| V <sub>OUT</sub> | R1         | R2         |

|------------------|------------|------------|

| 1.2V             | 499kΩ (1%) | 499kΩ (1%) |

| 1.5V             | 499kΩ (1%) | 332kΩ (1%) |

| 1.8V             | 499kΩ (1%) | 249kΩ (1%) |

| 2.5V             | 499kΩ (1%) | 158kΩ (1%) |

#### **Inductor Selection**

A 1 $\mu$ H to 10 $\mu$ H inductor with DC current rating at least 25% higher than the maximum load current is recommended for most applications. For best efficiency, the inductor DC resistance shall be <100m $\Omega$ . See Table 2 for recommended inductors and manufacturers. For most designs, the inductance value can be derived from the following equation:

$$L = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times \Delta I_L \times f_{OSC}}$$

Where  $\Delta I_L$  is inductor ripple current. Choose inductor ripple current approximately 30% of the maximum load current, up to 2A.

The maximum inductor peak current is:

# $I_{L(MAX)} = I_{LOAD(MAX)} + \frac{\Delta I_{L}}{2}$

#### Switcher Input Capacitor CIN1 Selection

The input capacitor reduces the surge current drawn from the input and switching noise from the device. The input capacitor impedance at the switching frequency shall be less than input source impedance to prevent high frequency switching current passing to the input. Ceramic capacitors with X5R or X7R dielectrics are highly recommended because of their low ESR and small temperature coefficients. For most applications, a  $10\mu$ F~22 $\mu$ F capacitor is sufficient.

#### Switcher Output Capacitor C<sub>01</sub> Selection

The output capacitor keeps output voltage ripple small and ensures regulation loop stable. The output capacitor impedance shall be low at the switching frequency. Ceramic capacitors with X5R or X7R dielectrics are recommended. For most applications, a  $22\mu$ F~47 $\mu$ F capacitor is sufficient.

The output ripple  $\Delta V_{OUT}$  is approximately:

$$\Delta V_{\text{OUT1}} \leq \frac{V_{\text{OUT1}} \times (V_{\text{IN1}} - V_{\text{OUT1}})}{V_{\text{IN1}} \times f_{\text{OSC}} \times L} \times \left( \text{ESR} + \frac{1}{8 \times f_{\text{OSC}} \times C_{\text{O1}}} \right)$$

| Manufacturer | Part Number | Inductance (uH) | Max DCR<br>(mΩ) | Saturation<br>Current (A) | Dimensions<br>L x W x H (mm3) |

|--------------|-------------|-----------------|-----------------|---------------------------|-------------------------------|

| ТОКО         | D62LCB      | 1.0             | 17              | 3.5                       | 6.2 X6.3 X 2.0                |

| SUMIDA       | CDRH4D28C   | 1.0             | 17.5            | 3.0                       | 5.1 X 5.1 X 3                 |

| DELTA        | SIL525-1R0  | 1.0             | 38              | 3.2                       | 5.0 X 5.0 X 2.5               |

#### Table 2—Suggested Surface Mount Inductors

## MP2116-2A, 6V, 100% DUTY CYCLE SYNCHROOUS STEP-DOWN CONVERTER WITH 0.5A LDO

#### **Thermal Dissipation**

Power dissipation shall be considered when both channels of the MP2116 provide maximum 2A switcher output current and 0.5A LDO output current to the loads at high ambient temperature. If the junction temperature rises above 150°C, the MP2116 two channels will be shut down.

The junction-to-ambient thermal resistance of the 10-pin QFN (3mm x 3mm)  $R_{\Theta JA}$  is 50°C/W. The maximum power dissipation is about 1.6W when the MP2116 is operating in a 70°C ambient temperature environment.

$$PD_{MAX} = \frac{150^{\circ}C - 70^{\circ}C}{50^{\circ}C/W} = 1.6W$$

#### **PC Board Layout**

The high current paths (GND, IN1/IN2 and SW1) should be placed very close to the device with short, direct and wide traces. Input capacitors should be placed as close as possible to the respective IN and GND pins. The external feedback resistors shall be placed next to the FB pins. Keep the switching nodes SW1 short and away from the feedback network

## PACKAGE INFORMATION

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.