# **General Purpose Low-Power Audio DSP**

# **DESCRIPTION**

WM0011 Audio DSP provides Wolfson HD audio quality, with a power-budget targeted at handheld battery-powered audio devices

WM0011 combines the advanced Tensilica HiFi EP™ audio DSP with an I/O and peripheral set optimized for flexible integration into smartphones, tablets and other portable consumer electronics devices. WM0011 is ideal for extremely power-efficient implementations of advanced voice enhancement, telephony noise reduction, voice and music CODECs and general audio enhancement.

A very wide range of audio CODECs, voice CODECs and third-party algorithms from such companies as Waves Audio, SRS Labs and Dolby are available, providing a rich portfolio of audio-processing options that can be integrated into a device with no additional software development.

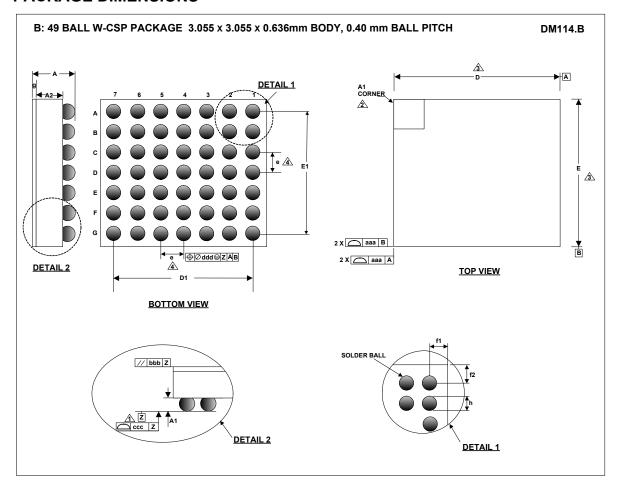

WM0011 comes in a space-saving 3x3mm 49-ball W-CSP package with 0.4mm pitch.

# **APPLICATIONS**

- Wireless audio devices headsets, microphones, speakerphones

- Portable media devices

- Automotive

- General purpose digital signal processor for consumer audio applications

- Smartphones

# **FEATURES**

- 260MHz Tensilica HiFi EP™ 24-bit audio digital signal processor

- C-programmable with advanced debugging and profiling tool set

- 256kB local RAM memory

- 36kB Instruction / Data cache memory

- 384kB general-purpose system RAM

- Flexible boot options with 32kB boot ROM

- 32 Channel DMA

- XTAL or CMOS clock input

- Low-power programmable PLL

- Securit

- Support for HW Authentication

- Random Number Generator (RNG) to assist security algorithms

- Peripherals

- SPI Master / Slave interface

- 3 x multi-channel AIF interfaces, including I2S and TDM

- UART

- I<sup>2</sup>C Master

- I<sup>2</sup>C Slave

- 3 x 32-bit general-purpose timer modules

- Watchdog timer

- On-chip JTAG debug unit and trace buffer

- GPIO

- Software-defined standby modes for extended battery life

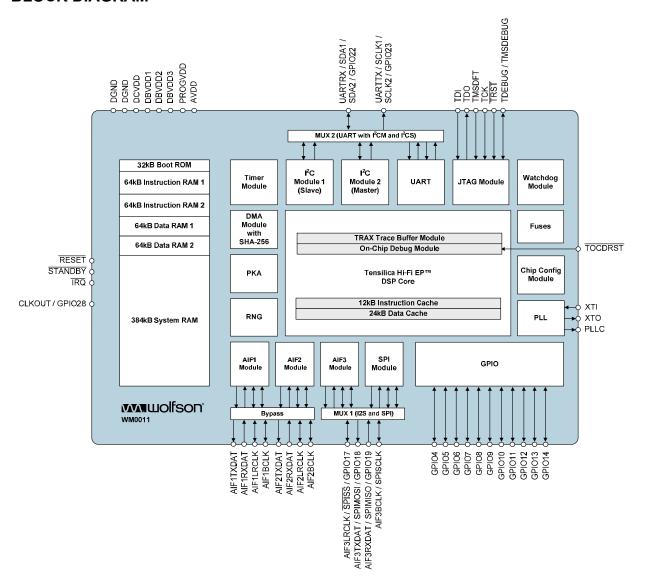

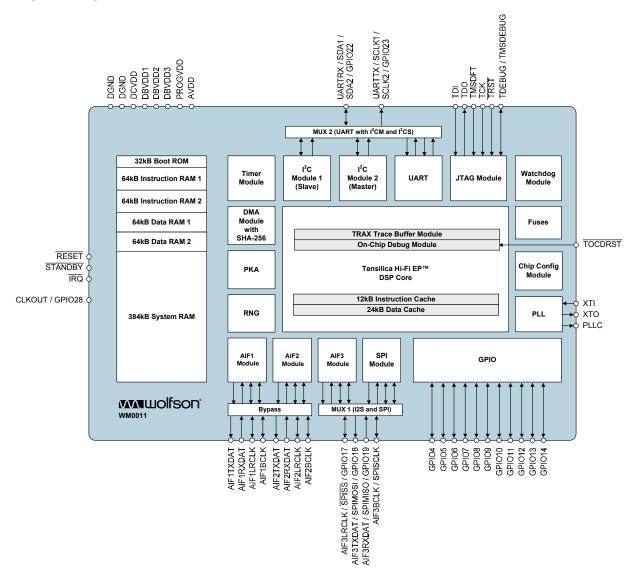

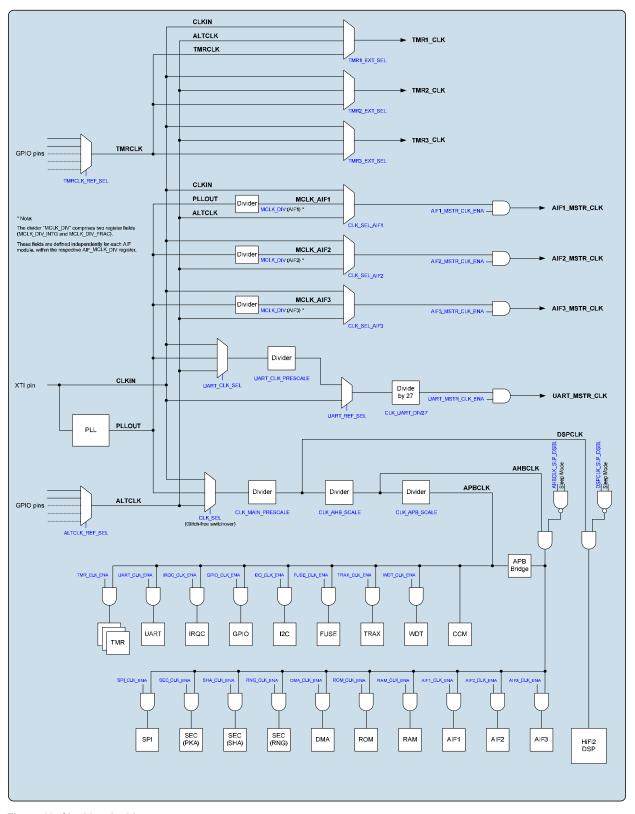

# **BLOCK DIAGRAM**

# **TABLE OF CONTENTS**

| DESCRIPTION                              | 1  |

|------------------------------------------|----|

| APPLICATIONS                             |    |

| FEATURES                                 |    |

| BLOCK DIAGRAM                            |    |

| TABLE OF CONTENTS                        |    |

| PIN CONFIGURATION                        |    |

|                                          |    |

| ORDERING INFORMATION                     |    |

| PIN DESCRIPTION                          |    |

| ABSOLUTE MAXIMUM RATINGS                 |    |

| RECOMMENDED OPERATING CONDITIONS         | 13 |

| THERMAL PERFORMANCE                      | 14 |

| ELECTRICAL CHARACTERISTICS               | 15 |

| TYPICAL POWER CONSUMPTION                | 16 |

| SIGNAL TIMING REQUIREMENTS               | 17 |

| SYSTEM CLOCK & PHASE LOCKED LOOP (PLL)   |    |

| AUDIO INTERFACE (AIF) TIMING             |    |

| DIGITAL AUDIO INTERFACE – MASTER MODE    |    |

| DIGITAL AUDIO INTERFACE – SLAVE MODE     |    |

| SPI INTERFACE TIMING                     | 20 |

| SPI INTERFACE - MASTER MODE              | 20 |

| SPI INTERFACE – SLAVE MODE               |    |

| CONTROL INTERFACE (I2C) TIMING           |    |

| DEVICE DESCRIPTION                       |    |

| INTRODUCTION                             |    |

| BLOCK DIAGRAM                            |    |

| DESCRIPTION OF MODULES                   |    |

| BOOT ROM                                 |    |

| TIGHTLY-COUPLED MEMORY (TCM) RAM         |    |

| MULTI-PURPOSE RAM                        |    |

| TENSILICA HIFI EP™ DSP CORE              |    |

| TIMER MODULE                             |    |

| WATCHDOG MODULE                          |    |

| IRQC MODULE                              |    |

| I <sup>2</sup> C MASTER AND SLAVE MODULE |    |

| PLL MODULE                               |    |

| AUDIO INTERFACE (AIF) MODULES            |    |

| SPI MODULE                               |    |

| FUSE MODULE                              |    |

| DMA MODULE                               | 27 |

| TRAX TRACE BUFFER MODULE                 | 27 |

| JTAG MODULE                              |    |

| ON-CHIP DEBUG MODULE                     | 28 |

| POWER-ON AND RESET CONTROL                           | 29 |

|------------------------------------------------------|----|

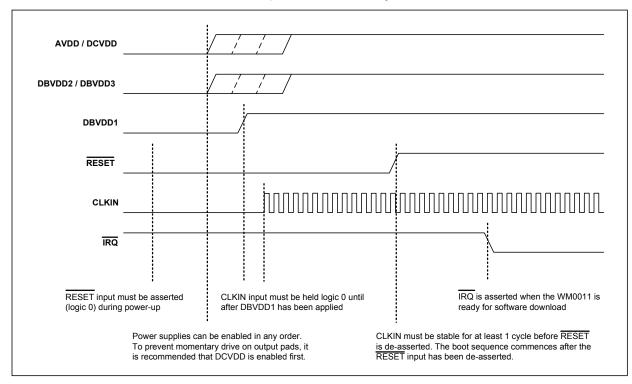

| POWER ON RESET                                       | 29 |

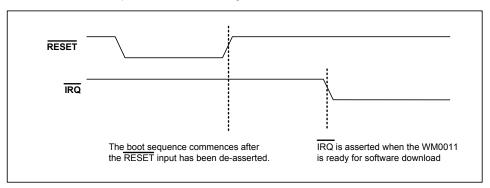

| HARDWARE RESET                                       | 30 |

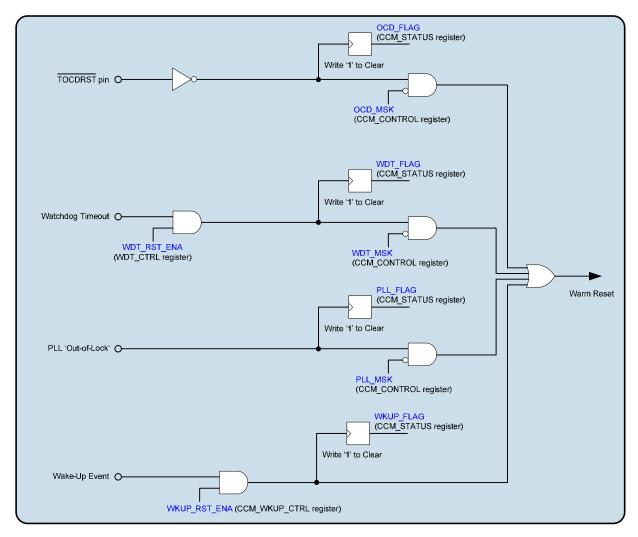

| WARM RESET                                           | 30 |

| SOFTWARE RESET                                       | 31 |

| JTAG RESET                                           |    |

| BOOT SEQUENCE CONTROL                                |    |

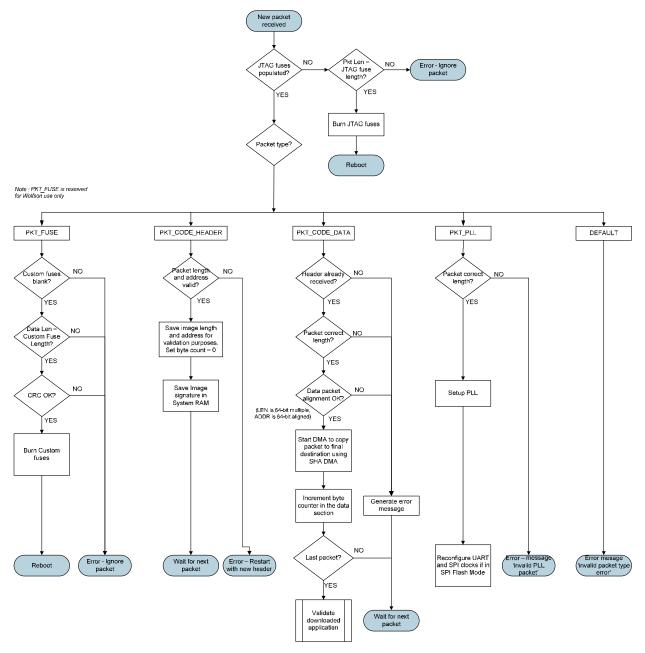

| SOFTWARE / CONFIGURATION DOWNLOAD                    |    |

| CODE PACKET FORMAT                                   |    |

| CODE HEADER DOWNLOAD                                 |    |

| CODE DATA DOWNLOAD                                   |    |

| PLL CONFIGURATION DOWNLOAD                           |    |

| BOOT STATUS AND ERROR REPORTING                      | 35 |

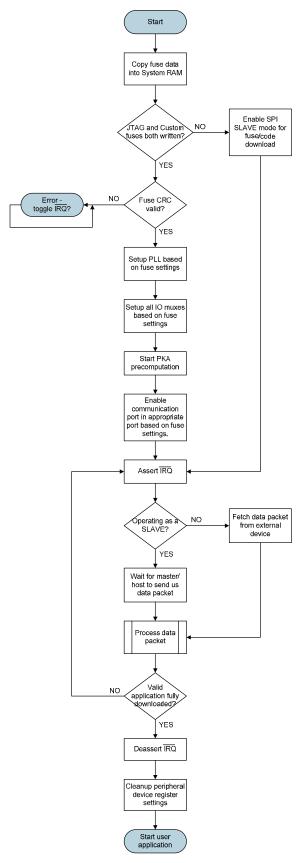

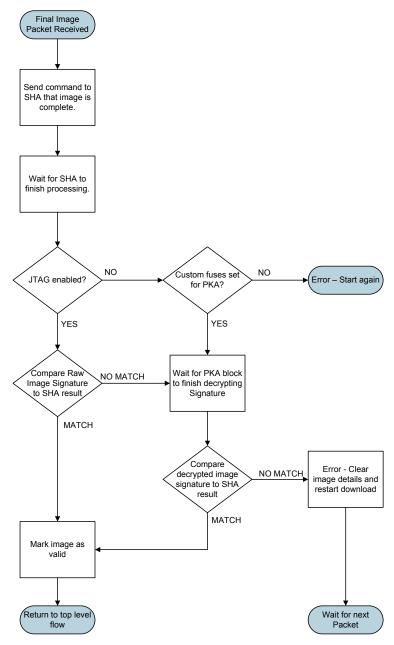

| BOOT SEQUENCE FLOW DIAGRAMS                          | 36 |

| INTERRUPTS                                           |    |

| MEMORY MAP                                           |    |

| CLOCKING                                             |    |

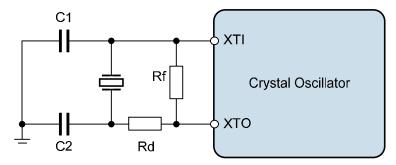

| CRYSTAL OSCILLATOR                                   |    |

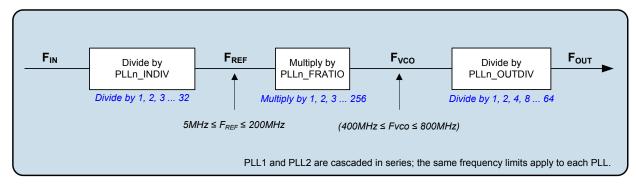

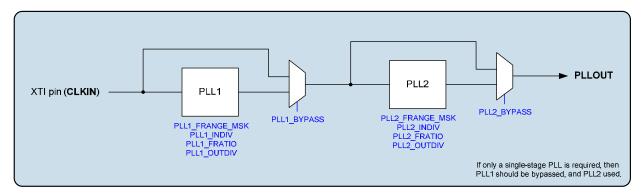

| PHASE LOCKED LOOP (PLL)                              |    |

|                                                      |    |

| CORE DEVICE PERIPHERALS                              |    |

| CCM - CHIP CONFIGURATION MODULE                      |    |

| CCM FEATURES                                         |    |

| CLOCKING CONTROL                                     |    |

| RESET CONTROLINTERFACE PORT SELECTION                |    |

| GPIO / STANDBY DE-BOUNCE                             |    |

| I/O BUFFER CONTROL                                   |    |

| SLEEP / WAKE-UP CONTROL                              |    |

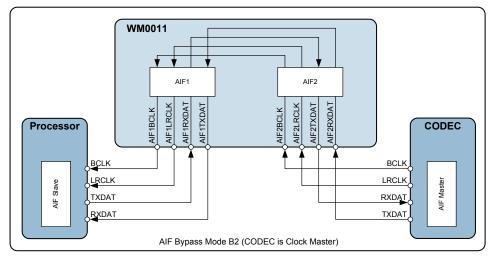

| AIF BYPASS MODE                                      |    |

| CCM REGISTER MAP                                     |    |

| CCM CONTROL – GENERAL CONTROL REGISTER               |    |

| CCM STATUS – GENERAL STATUS REGISTER                 |    |

| CCM GPIO SEL – PORT SELECT REGISTER                  |    |

| CCM CLK CTRL1 – CLOCK CONTROL 1 REGISTER             |    |

| CCM CLK CTRL2 – CLOCK CONTROL 2 REGISTER             |    |

| CCM CLK CTRL3 - CLOCK CONTROL 3 REGISTER             |    |

| CCM_PLL_LOCK_CTRL - PLL LOCK DETECT CONTROL REGISTER |    |

| CCM_CLK_ENA - CLOCK ENABLE REGISTER                  | 66 |

| CCM_SOFTRST – SOFTWARE RESET REGISTER                |    |

| CCM_WKUP_CTRL - CHIP WAKEUP CONTROL REGISTER         |    |

| CCM_DB_STBY - STANDBY DE-BOUNCE CONTROL REGISTER     |    |

| CCM_DB_GINT1 – GINT1 DE-BOUNCE CONTROL REGISTER      |    |

| CCM_DB_GINT2 - GINT2 DE-BOUNCE CONTROL REGISTER      |    |

| CCM_SCRATCH1 - SCRATCHPAD 1 REGISTER                 |    |

| CCM_SCRATCH2 - SCRATCHPAD 2 REGISTER                 |    |

| CCM_SCRATCH3 - SCRATCHPAD 3 REGISTER                 |    |

| CCM_SCRATCH4 – SCRATCHPAD 4 REGISTER                 |    |

| CCM_IOCTRL1 – I/O CONTROL 1 REGISTER                 |    |

| CCM_IOCTRL2 – I/O CONTROL 2 REGISTER                 |    |

| CCM_IOCTRL3 – I/O CONTROL 3 REGISTER                 |    |

| CCM_IOCTRL4 - I/O CONTROL 4 REGISTER                 |    |

| CCM_IOCTRL5 - I/O CONTROL 5 REGISTER                 |    |

| CCM_IOCTRL6 - I/O CONTROL 6 REGISTER                 | 81 |

| CCM IOCTRL7 - I/O CONTROL 7 REGISTER                                                   | 83  |

|----------------------------------------------------------------------------------------|-----|

| CCM_IOCTRL8 - I/O CONTROL 8 REGISTER                                                   |     |

| CCM_IOCTRL9 - I/O CONTROL 9 REGISTER                                                   |     |

| CCM_IOCTRL10 - I/O CONTROL 10 REGISTER                                                 |     |

| CCM IOCTRL11 – I/O CONTROL 11 REGISTER                                                 |     |

| TIMER (TMR) MODULES                                                                    |     |

| TIMER DESCRIPTION                                                                      |     |

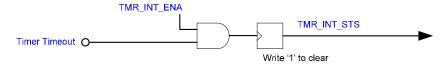

| TIMER INTERRUPTS                                                                       |     |

| TIMER REGISTER MAP                                                                     |     |

| TMR PRESCALE – TIMER PRESCALE REGISTER                                                 |     |

| TMR_MAX_CNT - TIMER MAXIMUM COUNT REGISTER                                             |     |

| TMR_CUR_CNT = TIMER MAXIMOM COUNT REGISTER  TMR_CUR_CNT = TIMER CURRENT COUNT REGISTER |     |

| TMR_CTRL - TIMER CONTROL REGISTER                                                      |     |

| TMR_INT_STATUS - TIMER INTERRUPT STATUS REGISTER                                       |     |

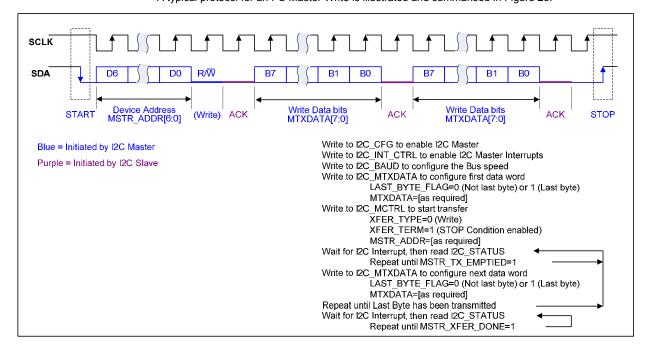

| I <sup>2</sup> C INTERFACE MODULE                                                      |     |

|                                                                                        |     |

| I2C FEATURES                                                                           |     |

| I2C TRANSFERS                                                                          |     |

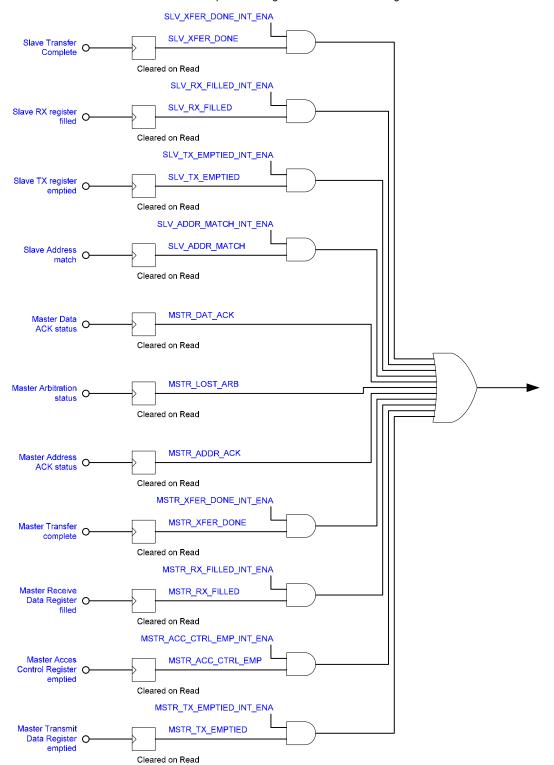

| I2C INTERRUPTS                                                                         |     |

| I2C REGISTER MAP<br>I2C CFG – I <sup>2</sup> C CONFIGURATION REGISTER                  |     |

|                                                                                        |     |

| I2C_STATUS – I2C STATUS REGISTER                                                       |     |

| 12C_INT_CTRL – I <sup>2</sup> C INTERRUPT CONTROL REGISTER                             |     |

| 12C_MCTRL - I <sup>2</sup> C MASTER ACCESS CONTROL REGISTER                            |     |

| I2C_MRXDATA – I <sup>2</sup> C MASTER RECEIVE DATA REGISTER                            |     |

| I2C_MTXDATA – I <sup>2</sup> C MASTER TRANSMIT DATA REGISTER                           |     |

| I2C_BAUD – I <sup>2</sup> C BAUD RATE REGISTER                                         |     |

| I2C_SRXDATA – I <sup>2</sup> C SLAVE RECEIVE DATA REGISTER                             |     |

| 12C_STXDATA – I <sup>2</sup> C SLAVE TRANSMIT DATA REGISTER                            |     |

| I2C_SLV_ADDR – I <sup>2</sup> C SLAVE ADDRESS REGISTER                                 |     |

| FUSE MEMORY                                                                            |     |

| FUSE MEMORY DEFINITION                                                                 |     |

| CYCLIC REDUNDANCY CHECK (CRC)                                                          |     |

| SOFTWARE AUTHENTICATION                                                                |     |

| GENERAL PURPOSE INPUT/OUTPUT (GPIO) MODULE                                             |     |

| GPIO FEATURES                                                                          |     |

| INPUT / OUTPUT CONTROL                                                                 |     |

| LEVEL/EDGE INTERRUPT CONTROL                                                           |     |

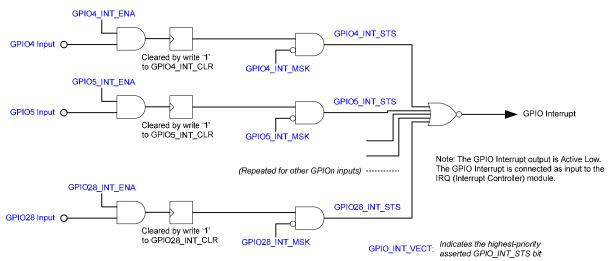

| GPIO INTERRUPTS                                                                        |     |

| GPIO REGISTER MAP                                                                      |     |

| GPIO_OUT – GPIO OUTPUT REGISTER                                                        |     |

| GPIO_IN - GPIO INPUT REGISTER                                                          |     |

| GPIO_DIR - GPIO DIRECTION REGISTER                                                     |     |

| GPIO_INV - GPIO INVERSION REGISTER                                                     |     |

| EDGE DETECTION                                                                         |     |

| GPIO_EDGE0 - GPIO EDGE DETECTION 0 REGISTER                                            |     |

| GPIO_EDGE1 – GPIO EDGE DETECTION 1 REGISTER                                            |     |

| GPIO_INT_CTRL - GPIO INTERRUPT CONTROL REGISTER                                        |     |

| GPIO_INT_CLR - GPIO INTERRUPT CLEAR REGISTER                                           |     |

| GPIO_INT_MSK - GPIO INTERRUPT MASK REGISTER                                            |     |

| GPIO_INT_VECT - GPIO INTERRUPT VECTOR REGISTER                                         |     |

| GPIO_INT_STS - GPIO INTERRUPT STATUS REGISTER                                          |     |

| INTERRUPT CONTROLLER (IRQC) MODULE                                                     |     |

| INTERRUPT CONTROLLER (IRQC) FEATURES                                                   |     |

| INPUT / OUTPUT CONTROL                                                                 | 125 |

| . = . = . = . = =                                      |     |

|--------------------------------------------------------|-----|

| LEVEL/EDGE INTERRUPT CONTROL                           |     |

| IRQC MODULE INTERRUPTS                                 |     |

| IRQC MODULE REGISTER MAP                               |     |

| IRQC_OUT – IRQ OUTPUT REGISTER                         |     |

| IRQC_IN - IRQ INPUT REGISTER                           |     |

| IRQC_DIR - IRQ DIRECTION REGISTER                      |     |

| IRQC_INV - IRQ INVERSION REGISTER                      |     |

| EDGE DETECTION                                         |     |

| IRQC_EDGE0 - IRQ EDGE DETECTION 0 REGISTER             |     |

| IRQC_EDGE1 – IRQ EDGE DETECTION 1 REGISTER             |     |

| IRQC_INT_CTRL - IRQ INTERRUPT CONTROL REGISTER         |     |

| IRQC_INT_CLR - IRQ INTERRUPT CLEAR REGISTER            |     |

| IRQC_IRQ_MSK - IRQ INTERRUPT MASK REGISTER             |     |

| IRQC_IRQ_VECT - IRQ INTERRUPT VECTOR REGISTER          |     |

| IRQC_IRQ_STS - IRQ INTERRUPT STATUS REGISTER           |     |

| IRQC_FIRQ_MSK - IRQ FAST INTERRUPT MASK REGISTER       |     |

| IRQC_FIRQ_VECT - IRQ FAST INTERRUPT VECTOR REGISTER    | 139 |

| IRQC_FIRQ_STS - IRQ FAST INTERRUPT STATUS REGISTER     |     |

| TRAX TRACE BUFFER MODULE                               | 141 |

| TRAX REGISTER MAP                                      | 141 |

| TRAX_CONFIG - TRAX TRACE BUFFER CONFIGURATION REGISTER | 142 |

| TRAX_CTRL - TRAX CONTROL REGISTER                      | 142 |

| TRAX_STS - TRAX STATUS REGISTER                        | 144 |

| TRAX_DATA – TRAX DATA REGISTER                         | 145 |

| TRAX ADDR – TRAX ADDRESS REGISTER                      | 145 |

| TRAX_TRIG_PC - TRAX PC MATCH TRIGGER REGISTER          | 146 |

| TRAX PC MATCH - TRAX PC MATCH CONTROL REGISTER         |     |

| TRAX DLY CNT - TRAX POST-TRIGGER DELAY COUNT REGISTER  | 148 |

| WATCHDOG TIMER (WDT) MODULE                            |     |

| WATCHDOG DESCRIPTION                                   |     |

| WATCHDOG TIMER INTERRUPT                               |     |

| WATCHDOG REGISTER MAP                                  |     |

| WDT_CTRL - WATCHDOG CONTROL REGISTER                   |     |

| WDT_CNT_RESTART - WATCHDOG COUNTER RESTART REGISTER    |     |

| WDT MAX CNT - WATCHDOG MAXIMUM COUNT REGISTER          |     |

| WDT_CUR_CNT - WATCHDOG CURRENT COUNT REGISTER          |     |

| WDT RST LEN - WATCHDOG RESET PULSE LENGTH REGISTER     |     |

| UART MODULE                                            |     |

| UART FEATURES                                          |     |

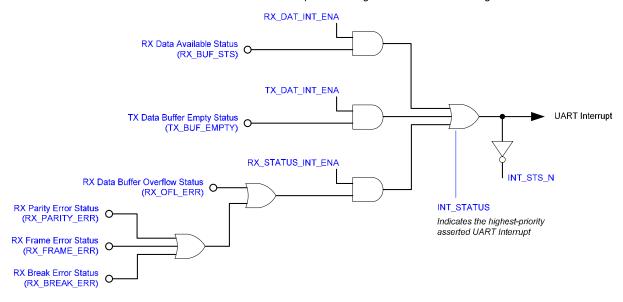

| UART INTERRUPTS                                        |     |

| UART REGISTER MAP                                      |     |

| UART DAT - UART DATA REGISTER                          |     |

| UART INT CTRL - UART INTERRUPT CONTROL REGISTER        |     |

| UART FIFO CTRL - UART FIFO CONTROL REGISTER            |     |

| UART_INT_STATUS - UART INTERRUPT STATUS REGISTER       |     |

| UART LINE CTRL - UART LINE CONTROL REGISTER            |     |

| UART_LOOPBACK_CTRL - UART LOOPBACK CONTROL REGISTER    |     |

| UART LINE STS - UART LINE STATUS REGISTER              |     |

| UART BAUD LSW - UART BAUD LSW REGISTER                 |     |

| UART_BAUD_MSW - UART BAUD MSW REGISTER                 |     |

| SERIAL PERIPHERAL INTERFACE (SPI) MODULE               |     |

| SPI FEATURESSPI FEATURES                               |     |

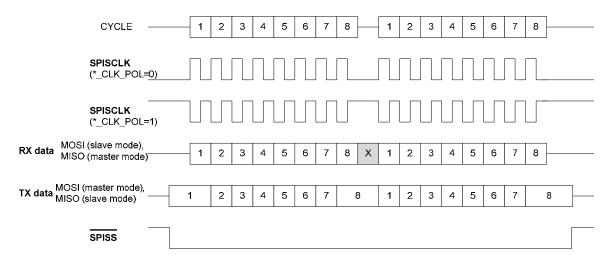

| SPI MASTER MODE                                        |     |

| SPI SLAVE MODE                                         |     |

| 01 1 0L (V L 1910 DL                                   | 108 |

| SPISCLK (CLOCK) CONFIGURATION                          | 159 |

|--------------------------------------------------------|-----|

| MISO/MOSI (DATA) CONFIGURATION                         | 161 |

| SPISS (SLAVE SELECT) PROTOCOL                          |     |

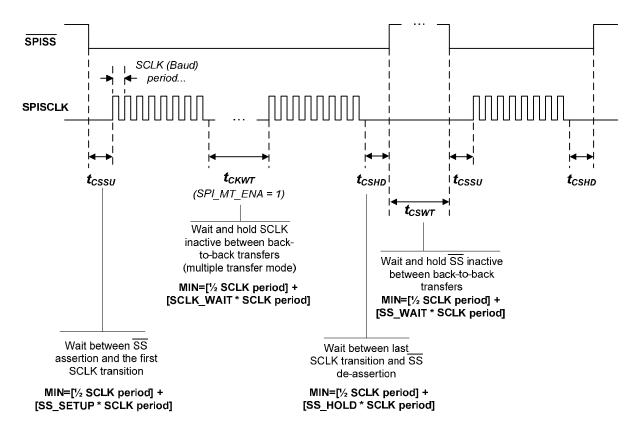

| SPISS (SLAVE SELECT) CONFIGURATION AND TIMING CONTROL  | 162 |

| EARLY TRANSMIT DATA PHASE                              | 163 |

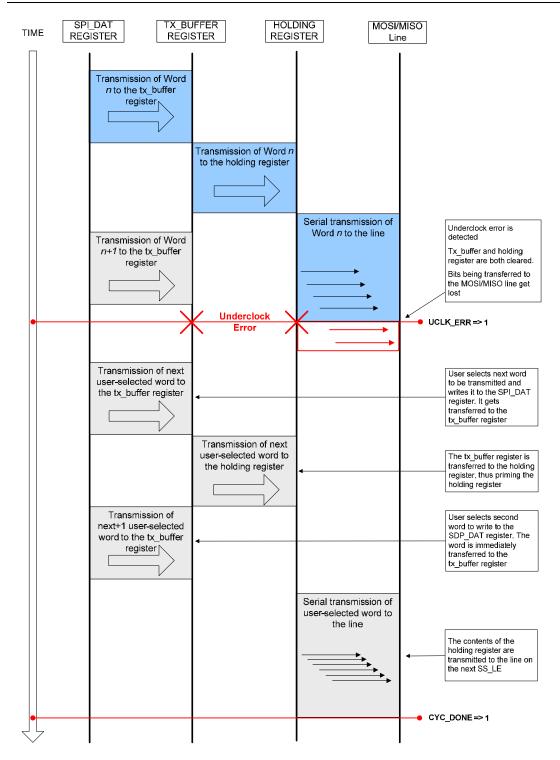

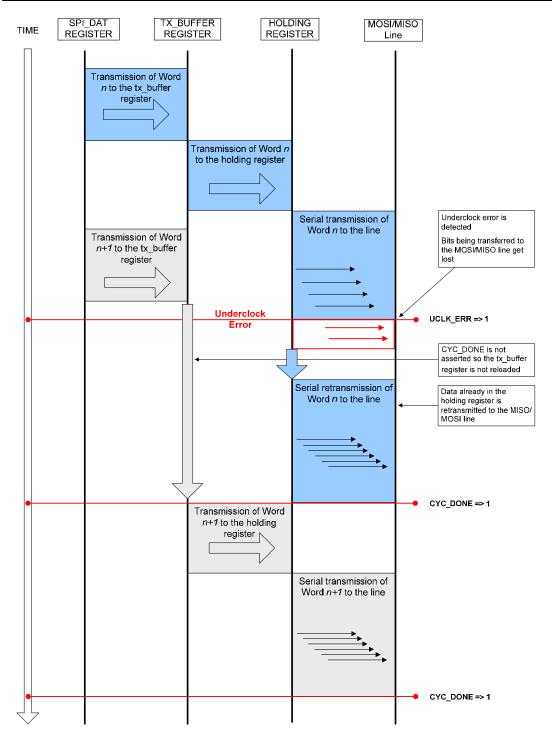

| AUTOMATED RE-TRANSMISSION OF DATA WORD                 | 164 |

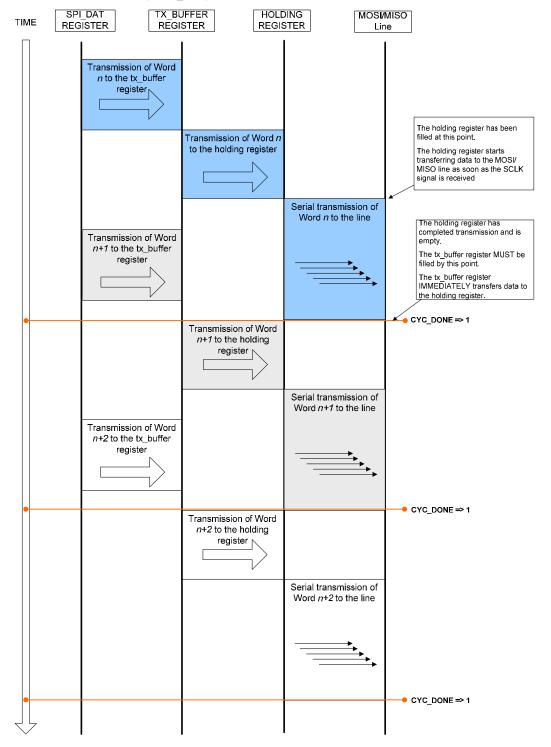

| DOUBLE-BUFFERED TRANSMIT                               | 164 |

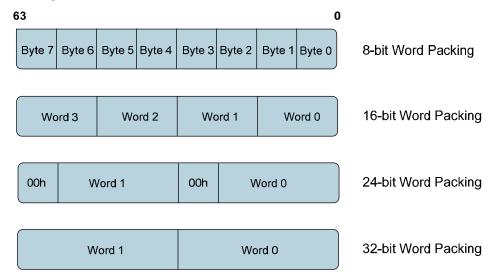

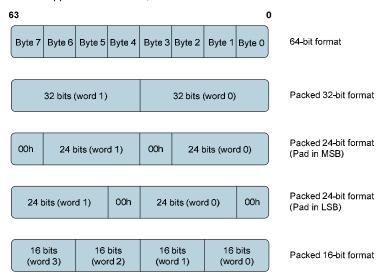

| SPI BYTE-PACKING                                       |     |

| SPI DMA OPERATIONS                                     |     |

| SPI CONTROL SEQUENCES                                  |     |

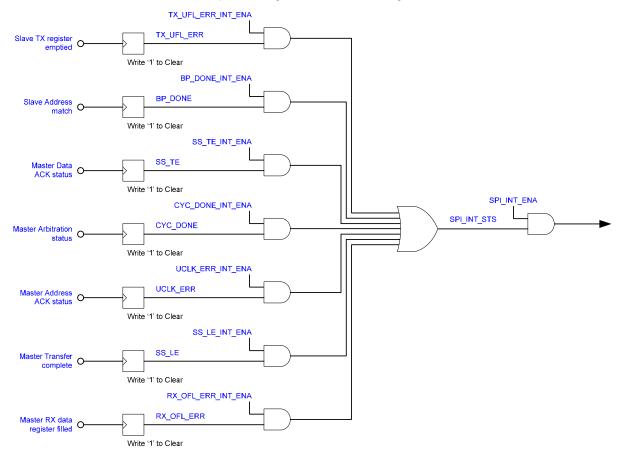

| SPI INTERRUPTS                                         |     |

| SPI REGISTER MAP                                       |     |

| SPI CTRL – SPI CONTROL REGISTER                        |     |

| SPI CFG – SPI CONFIGURATION REGISTER                   |     |

| SPI SCLKDIV – SPI CLOCK DIVISION REGISTER              |     |

| SPI STATUS – SPI STATUS REGISTER                       |     |

| SPI SS CFG- SPI SLAVE SELECT CONFIGURATION REGISTER    |     |

| SPI DAT- SPI DATA REGISTER                             |     |

| SPI INT CTRL – SPI INTERRUPT CONTROL REGISTER          |     |

| SPI DMA CTRL- SPI DMA CONTROL REGISTER                 |     |

| SPI BP CNT – SPI BYTE PACK WORD COUNT REGISTER         |     |

| SPI BP CNT RAW – SPI BYTE PACK RAW WORD COUNT REGISTER |     |

| DMA CONTROLLER MODULE                                  |     |

| DMA FEATURES                                           |     |

| DMA CHANNEL CONTROL                                    |     |

|                                                        |     |

| DMA CHANNEL ARBITRATION                                |     |

| NORMAL DMA OPERATION                                   |     |

| SHA MODULE DATA INPUT                                  |     |

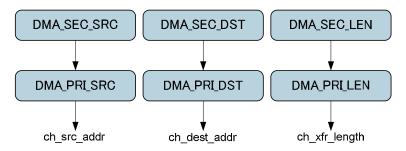

| DOUBLE-BUFFER DMA OPERATION                            |     |

| LINKED LIST DMA CHAINING                               |     |

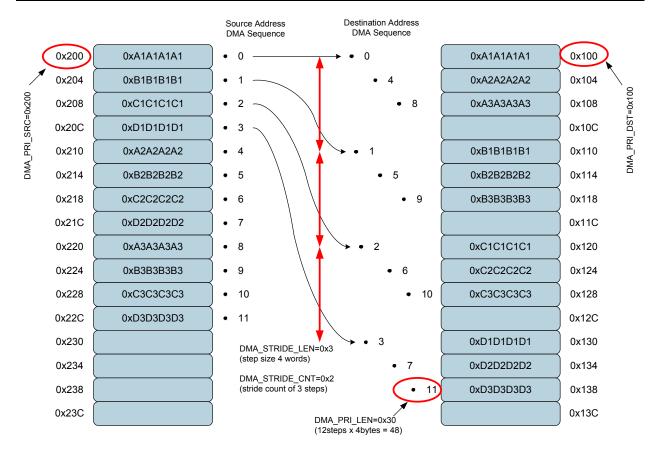

| DMA STRIDING                                           |     |

| BURST DATA TRANSFERS                                   |     |

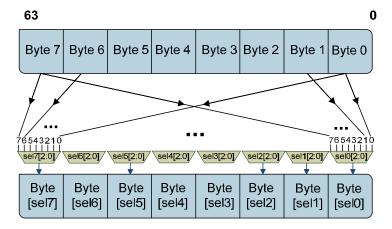

| DMA BYTE SWAP                                          |     |

| ENDIAN BYTE SWAP                                       |     |

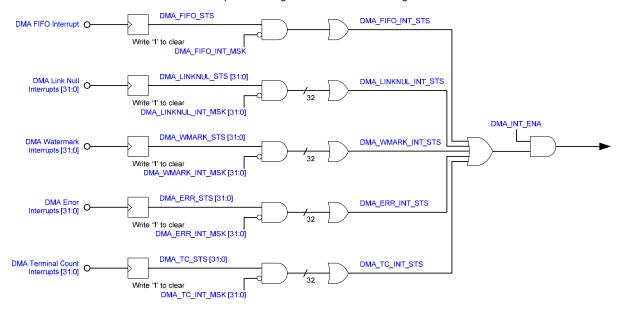

| DMA INTERRUPTS                                         |     |

| DMA REGISTER MAP                                       |     |

| DMA_GLB_CTRL REGISTER                                  |     |

| DMA_INT_STS REGISTER                                   |     |

| DMA_TC_INT_MSK REGISTER                                |     |

| DMA_ERR_INT_MSK REGISTER                               |     |

| DMA_WMARK_INT_MSK REGISTER                             |     |

| DMA_LINKNUL_INT_MSK REGISTER                           |     |

| DMA_TC_STS REGISTER                                    |     |

| DMA_ERR_STS REGISTER                                   |     |

| DMA_WMARK_STS REGISTER                                 |     |

| DMA_LINKNUL_STS REGISTER                               |     |

| DMA_FIFO_INT_MASK REGISTER                             |     |

| DMA_FIFO_STATUS REGISTER                               |     |

| DMA_AHB_SLAVE_ADDR REGISTER                            |     |

| DMA_PRI_SRC REGISTER                                   |     |

| DMA_PRI_DST REGISTER                                   |     |

| DMA_PRI_LEN REGISTER                                   |     |

| DMA_LINK_ADDR REGISTER                                 |     |

| DMA_SEC_SRC REGISTER                                   | 200 |

|                                                        |     |

| DMA OFO DOT DECICIED                                     | 004 |

|----------------------------------------------------------|-----|

| DMA_SEC_DST REGISTER                                     |     |

| DMA_SEC_LEN REGISTER                                     |     |

| DMA_COUNT REGISTER                                       |     |

| DMA_WMARK_CNT REGISTER                                   |     |

| DMA_CTRL1 REGISTER  DMA CTRL2 REGISTER                   |     |

| DMA_CTRL2 REGISTERDMA SOFT ABORT REGISTER                |     |

| DMA_STRIDE REGISTER                                      |     |

| DMA PROGRAM EXAMPLES                                     |     |

| EXAMPLE 1: PERIPHERAL TRANSFERS USING DMA                |     |

| EXAMPLE 2: MEMORY TO MEMORY TRANSFERS USING DMA          |     |

| EXAMPLE 3: LINKED LIST DMA OPERATION                     |     |

| AIF INTERFACE MODULES                                    |     |

| AIF FEATURES                                             |     |

| AIF INTERFACE FORMATS                                    |     |

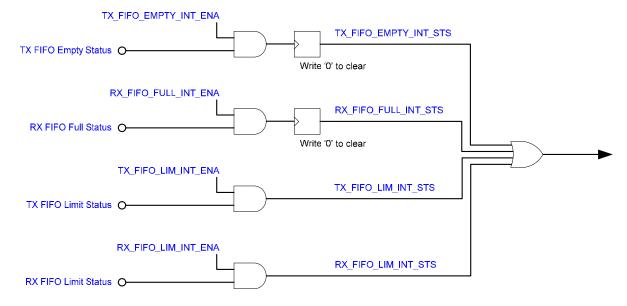

| AIF INTERRUPTS                                           |     |

| AIF REGISTER MAP                                         |     |

| AIF RX DAT – AIF RECEIVE DATA REGISTER                   |     |

| AIF RX CH ID – AIF RECEIVE CHANNEL ID REGISTER           |     |

| AIF RX STS – AIF RECEIVE FIFO STATUS REGISTER            |     |

| AIF_RX_LIMIT – AIF RECEIVE FIFO UPPER LIMIT REGISTER     |     |

| AIF TX DAT – AIF TRANSMIT DATA REGISTER                  |     |

| AIF TX CH ID – AIF TRANSMIT CHANNEL ID REGISTER          |     |

| AIF TX STS – AIF TRANSMIT FIFO STATUS REGISTER           |     |

| AIF TX LIMIT – AIF TRANSMIT FIFO LOWER LIMIT REGISTER    | 221 |

| AIF_DATA_CFG – AIF DATA CONFIGURATION REGISTER           | 221 |

| AIF_CLK_CFG - AIF SERIAL CLOCKING CONFIGURATION REGISTER | 224 |

| AIF_CTRL – AIF CONTROL REGISTER                          | 225 |

| AIF_INT_CTRL - AIF INTERRUPT CONTROL REGISTER            |     |

| AIF_MCLK_DIV – AIF MCLK DIVIDER REGISTER                 |     |

| JTAG (JTAG) MODULE                                       |     |

| CROSS-TRIGGER MODULE (CTM)                               | 228 |

| ON-CHIP DEBUG (OCD) MODULE                               |     |

| APPLICATIONS INFORMATION                                 | 229 |

| CONNECTIVITY DIAGRAM                                     |     |

| PACKAGE DIMENSIONS                                       |     |

| MPORTANT NOTICE                                          |     |

| ADDRESS:                                                 |     |

| PEVISION HISTORY                                         |     |

|                                                          |     |

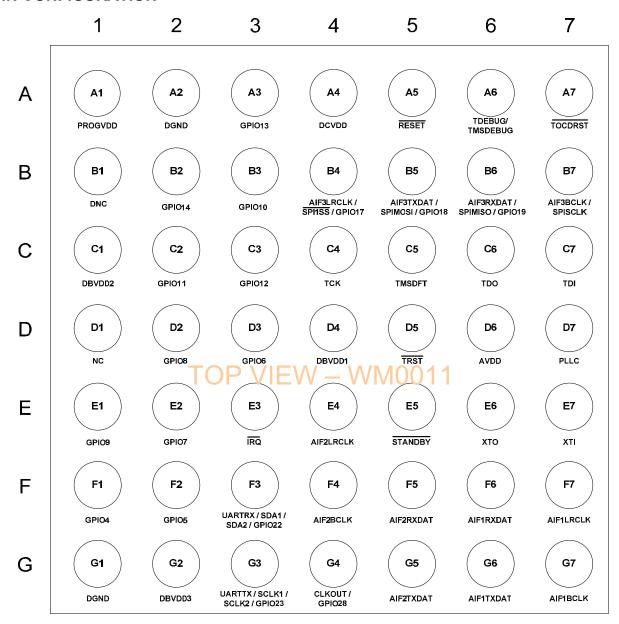

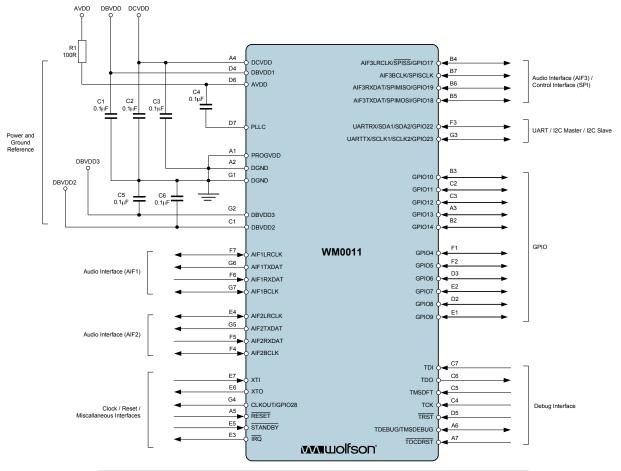

# **PIN CONFIGURATION**

# **ORDERING INFORMATION**

| DEVICE            | CUSTOM<br>FUSES | TEMPERATURE<br>RANGE | PACKAGE                  | MOISTURE<br>SENSITIVITY<br>LEVEL | PEAK<br>SOLDERING<br>TEMPERATURE |

|-------------------|-----------------|----------------------|--------------------------|----------------------------------|----------------------------------|

| WM0011ECS/R       | Un-programmed   | -40 to +85°C         | 49-ball W-CSP            | MSL1                             | 260°C                            |

|                   | 1 0             |                      | (Pb-free, Tape and reel) |                                  |                                  |

| WM0011xxxECS/R    | Custom-         | -40 to +85°C         | 49-ball W-CSP            | MSL1                             | 260°C                            |

| VVIVIOUTIXXXECS/R | Programmed      | -40 to +65 C         | (Pb-free, Tape and reel) | IVIOLI                           | 200 C                            |

#### Note:

Reel quantity = 5000

# **PIN DESCRIPTION**

| PIN<br>NO | NAME                                 | TYPE           | PULL<br>DEVICE | DESCRIPTION                                                    |  |

|-----------|--------------------------------------|----------------|----------------|----------------------------------------------------------------|--|

| Powe      | r and Ground Reference               |                |                |                                                                |  |

| D4        | DBVDD1                               | Supply         | -              | I/O supply (except GPIO pins 414)                              |  |

| A4        | DCVDD                                | Supply         | -              | Core supply                                                    |  |

| A1        | PROGVDD                              | Supply         | -              | Fuse programming supply. Connect to GND.                       |  |

| A2,<br>G1 | DGND                                 | Supply         | -              | Ground                                                         |  |

| D6        | AVDD                                 | Supply         | -              | Analogue supply                                                |  |

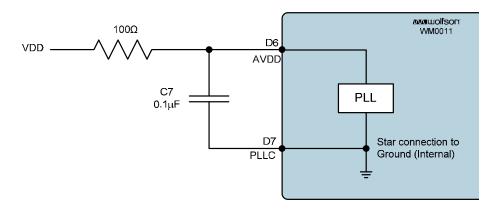

| D7        | PLLC                                 | Reference      | -              | PLL capacitor connection (0.1µF recommended)                   |  |

| C1        | DBVDD2                               | Supply         | -              | I/O supply (GPIO10, GPIO11, GPIO12, GPIO13, GPIO14 pins)       |  |

| G2        | DBVDD3                               | Supply         | -              | I/O supply (GPIO4, GPIO5, GPIO6, GPIO7, GPIO8, GPIO9 pins)     |  |

| Clock     | / Reset / Miscellaneous Interfaces   | }              |                |                                                                |  |

| E7        | XTI                                  | Input          | -              | Crystal connection or digital clock input                      |  |

| E6        | хто                                  | Output         | -              | Crystal connection                                             |  |

| A5        | RESET                                | Input          | Pull-Up        | Device reset                                                   |  |

| E5        | STANDBY                              | Input          | Pull-Up        | Standby input signal                                           |  |

| E3        | ĪRQ                                  | Output         | Pull-Up        | Interrupt output                                               |  |

| G4        | CLKOUT/GPIO28                        | Input / Output | Pull-Down      | Reference clock output / GPIO pin                              |  |

| Audio     | Interface 1 (AIF1)                   |                |                |                                                                |  |

| G6        | AIF1TXDAT                            | Output         | Pull-Down      | AIF1 data output                                               |  |

| F6        | AIF1RXDAT                            | Input          | Pull-Down      | AIF1 data input                                                |  |

| F7        | AIF1LRCLK                            | Input / Output | Pull-Down      | AIF1 frame clock                                               |  |

| G7        | AIF1BCLK                             | Input / Output | Pull-Down      | AIF1 bit clock                                                 |  |

| Audio     | Interface 2 (AIF2)                   |                |                |                                                                |  |

| G5        | AIF2TXDAT                            | Output         | Pull-Down      | AIF2 data output                                               |  |

| F5        | AIF2RXDAT                            | Input          | Pull-Down      | AIF2 data input                                                |  |

| E4        | AIF2LRCLK                            | Input / Output | Pull-Down      | AIF2 frame clock                                               |  |

| F4        | AIF2BCLK                             | Input / Output | Pull-Down      | AIF2 bit clock                                                 |  |

| Audio     | Interface 3 (AIF3) / Control Interfa | ice (SPI)      |                |                                                                |  |

| B5        | AIF3TXDAT/SPIMOSI/GPIO18             | Input / Output | Pull-Down      | AIF3 data output / SPI Master Out Slave In / GPIO <sup>1</sup> |  |

| В6        | AIF3RXDAT/SPIMISO/GPIO19             | Input / Output | Pull-Down      | AIF3 data input / SPI Master In Slave Out / GPIO1              |  |

| В4        | AIF3LRCLK/SPISS/GPIO17               | Input / Output | Pull-Up        | AIF3 frame clock / SPI slave select / GPIO <sup>1</sup>        |  |

<sup>\*</sup> xxx = Unique Custom Fuse part number

<sup>\*\*</sup> Custom programmed minimum order quantity 50,000.

| PIN<br>NO | NAME                                         | TYPE           | PULL<br>DEVICE | DESCRIPTION                                                                    |  |

|-----------|----------------------------------------------|----------------|----------------|--------------------------------------------------------------------------------|--|

| В7        | AIF3BCLK/SPISCLK                             | Input / Output | Pull-Down      | AIF3 bit clock / SPI serial clock <sup>1</sup>                                 |  |

| UART      | / I <sup>2</sup> C Master & Slave Interfaces |                |                |                                                                                |  |

| F3        | UARTRX/SDA1/SDA2/GPIO22                      | Input / Output | Pull-Down      | UART RX / Serial data 1 (slave) / Serial data 2 (master) / GPIO <sup>2</sup>   |  |

| G3        | UARTTX/SCLK1/SCLK2/GPIO23                    | Input / Output | Pull-Down      | UART TX / Serial clock 1 (slave) / Serial clock 2 (master) / GPIO <sup>2</sup> |  |

| GPIO      |                                              |                |                |                                                                                |  |

| F1        | GPIO4                                        | Input / Output | Pull-Up/Down   | GPIO pin                                                                       |  |

| F2        | GPIO5                                        | Input / Output | Pull-Up/Down   | GPIO pin                                                                       |  |

| D3        | GPIO6                                        | Input / Output | Pull-Up/Down   | GPIO pin                                                                       |  |

| E2        | GPIO7                                        | Input / Output | Pull-Up/Down   | GPIO pin                                                                       |  |

| D2        | GPIO8                                        | Input / Output | Pull-Up/Down   | GPIO pin                                                                       |  |

| E1        | GPIO9                                        | Input / Output | Pull-Up/Down   | GPIO pin                                                                       |  |

| В3        | GPIO10                                       | Input / Output | Pull-Up/Down   | GPIO pin                                                                       |  |

| C2        | GPIO11                                       | Input / Output | Pull-Up/Down   | GPIO pin                                                                       |  |

| C3        | GPIO12                                       | Input / Output | Pull-Up/Down   | GPIO pin                                                                       |  |

| А3        | GPIO13                                       | Input / Output | Pull-Up/Down   | GPIO pin                                                                       |  |

| B2        | GPIO14                                       | Input / Output | Pull-Up/Down   | GPIO pin                                                                       |  |

| Debu      | g                                            |                |                |                                                                                |  |

| C4        | TCK                                          | Input          | Pull-Up        | JTAG clock                                                                     |  |

| A6        | TDEBUG/TMSDEBUG                              | Input / Output | Pull-Up        | Test Mode Debug output / Test Mode Select input                                |  |

| C7        | TDI                                          | Input          | Pull-Up        | JTAG data input                                                                |  |

| C6        | TDO                                          | Output         | Pull-Up        | JTAG data output                                                               |  |

| C5        | TMSDFT                                       | Input          | Pull-Up        | JTAG mode select input                                                         |  |

| A7        | TOCDRST                                      | Input          | Pull-Up        | Maskable chip reset from the debug tool                                        |  |

| D5        | TRST                                         | Input          | Pull-Down      | JTAG Test Access Port (TAP) block reset                                        |  |

| Other     |                                              |                |                |                                                                                |  |

| B1        | DNC                                          |                |                | Do Not Connect                                                                 |  |

| D1        | NC                                           |                |                | Not used - connect to GND.                                                     |  |

#### Notes:

- 1. The SPI interface I/O pads are multiplexed with AIF3

- 2. The UART, I2C master and I2C slave signals are multiplexed into two I/O pads.

- 3. The I/O pad multiplexers are configured during the boot-up sequence, as determined by the Custom Fuse settings.

Table 1 identifies the default power-up condition of each of the input / output pins, assuming that the Custom Fuses are not programmed.

Application-specific parameters for configuring the input / output pins, and many other parameters, may be selected using the integrated one-time-programmable fuses. See "Boot Sequence Control" for further details.

| PIN<br>NO | NAME          | DEFAULT FUNCTION / RESET CONDITION (FUSES NOT PROGRAMMED) |        |                   |  |

|-----------|---------------|-----------------------------------------------------------|--------|-------------------|--|

| E7        | XTI           | XTI                                                       | input  |                   |  |

| E6        | XTO           | XTO                                                       | output |                   |  |

| A5        | RESET         | RESET                                                     | input  | Pull-up enabled   |  |

| E5        | STANDBY       | STANDBY                                                   | input  | Pull-up enabled   |  |

| E3        | ĪRQ           | ĪRQ                                                       | output | Pull-up enabled   |  |

| G4        | CLKOUT/GPIO28 | CLKOUT                                                    | output | Pull-down enabled |  |

| G6        | AIF1TXDAT     | AIF1TXDAT                                                 | output | Pull-down enabled |  |

| F6        | AIF1RXDAT     | AIF1RXDAT                                                 | input  | Pull-down enabled |  |

| PIN<br>NO | NAME                      | DEFAULT FUNCTION / RESET CONDITION (FUSES NOT PROGRAMMED) |              |                                                                                                                            |  |

|-----------|---------------------------|-----------------------------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------|--|

| F7        | AIF1LRCLK                 | AIF1LRCLK                                                 | input        | Pull-down enabled                                                                                                          |  |

| G7        | AIF1BCLK                  | AIF1BCLK                                                  | input        | Pull-down enabled                                                                                                          |  |

| G5        | AIF2TXDAT                 | AIF2TXDAT                                                 | output       | Pull-down enabled                                                                                                          |  |

| F5        | AIF2RXDAT                 | AIF2RXDAT                                                 | input        | Pull-down enabled                                                                                                          |  |

| E4        | AIF2LRCLK                 | AIF2LRCLK                                                 | input        | Pull-down enabled                                                                                                          |  |

| F4        | AIF2BCLK                  | AIF2BCLK                                                  | input        | Pull-down enabled                                                                                                          |  |

| B5        | AIF3TXDAT/SPIMOSI/GPIO18  | SPIMOSI                                                   | output       | Pull-down enabled                                                                                                          |  |

| B6        | AIF3RXDAT/SPIMISO/GPIO19  | SPIMISO                                                   | input        | Pull-down enabled                                                                                                          |  |

| B4        | AIF3LRCLK/SPISS/GPIO17    | SPISS                                                     | output       | Pull-up enabled                                                                                                            |  |

| B7        | AIF3BCLK/SPISCLK          | SPISCLK                                                   | output       | Pull-down enabled                                                                                                          |  |

| F3        | UARTRX/SDA1/SDA2/GPIO22   | UARTRX                                                    | input        | Pull-down enabled                                                                                                          |  |

| G3        | UARTTX/SCLK1/SCLK2/GPIO23 | UARTTX                                                    | output       | Pull-down enabled whilst RESET is asserted. Pull-down is disabled after RESET is released. UARTTX is then actively driven. |  |

| F1        | GPIO4                     | [Disabled]                                                | input/output | Pull-down enabled                                                                                                          |  |

| F2        | GPIO5                     | [Disabled]                                                | input/output | Pull-down enabled                                                                                                          |  |

| D3        | GPIO6                     | [Disabled]                                                | input/output | Pull-down enabled                                                                                                          |  |

| E2        | GPIO7                     | [Disabled]                                                | input/output | Pull-down enabled                                                                                                          |  |

| D2        | GPIO8                     | [Disabled]                                                | input/output | Pull-down enabled                                                                                                          |  |

| E1        | GPIO9                     | [Disabled]                                                | input/output | Pull-down enabled                                                                                                          |  |

| В3        | GPIO10                    | [Disabled]                                                | input/output | Pull-down enabled whilst RESET is asserted. Pull-up is enabled after RESET is released.                                    |  |

| C2        | GPIO11                    | [Disabled]                                                | input/output | Pull-down enabled                                                                                                          |  |

| C3        | GPIO12                    | [Disabled]                                                | input/output | Pull-down enabled                                                                                                          |  |

| A3        | GPIO13                    | [Disabled]                                                | input/output | Pull-down enabled                                                                                                          |  |

| B2        | GPIO14                    | [Disabled]                                                | input/output | Pull-down enabled                                                                                                          |  |

| C4        | TCK                       | TCK                                                       | input        | Pull-up enabled                                                                                                            |  |

| A6        | TDEBUG/TMSDEBUG           | TDEBUG/TMSDEBUG                                           |              | Pull-up enabled                                                                                                            |  |

| C7        | TDI                       | TDI                                                       | input        | Pull-up enabled                                                                                                            |  |

| C6        | TDO                       | TDO                                                       | output       | Pull-down enabled                                                                                                          |  |

| C5        | TMSDFT                    | TMSDFT                                                    | input        | Pull-up enabled                                                                                                            |  |

| A7        | TOCDRST                   | TOCDRST                                                   | input        | Pull-up enabled                                                                                                            |  |

| D5        | TRST                      | TRST                                                      | input        | Pull-down enabled                                                                                                          |  |

Table 1 Default Pin Conditions (assuming Fuses are not programmed)

WM0011

# **ABSOLUTE MAXIMUM RATINGS**

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical Characteristics at the test conditions specified.

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage of this device.

Wolfson tests its package types according to IPC/JEDEC J-STD-020 for Moisture Sensitivity to determine acceptable storage conditions prior to surface mount assembly. These levels are:

MSL1 = unlimited floor life at <30°C / 85% Relative Humidity. Not normally stored in moisture barrier bag.

MSL2 = out of bag storage for 1 year at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

MSL3 = out of bag storage for 168 hours at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

The Moisture Sensitivity Level for each package type is specified in Ordering Information.

| CONDITION                                              | MIN         | MAX           |

|--------------------------------------------------------|-------------|---------------|

| Supply voltage (DCVDD)                                 | DGND - 0.3V | 1.6V          |

| Supply voltage (DBVDD1, DBVDD2, DBVDD3, AVDD, PROGVDD) | DGND - 0.3V | 5.0V          |

| Voltage range digital inputs (DBVDD1 domain)           | DGND - 0.3V | DBVDD1 + 0.3V |

| Voltage range digital inputs (DBVDD2 domain)           | DGND - 0.3V | DBVDD2 + 0.3V |

| Voltage range digital inputs (DBVDD3 domain)           | DGND - 0.3V | DBVDD3 + 0.3V |

| Operating temperature range, T <sub>A</sub>            | -40°C       | +85°C         |

| Junction temperature, T <sub>J</sub>                   | -40°C       | +125°C        |

| Storage temperature after soldering                    | -65°C       | +150°C        |

#### RECOMMENDED OPERATING CONDITIONS

| PARAMETER                                                           | SYMBOL         | MIN  | TYP | MAX  | UNIT |

|---------------------------------------------------------------------|----------------|------|-----|------|------|

| Digital core supply range                                           | DCVDD          | 1.14 | 1.2 | 1.32 | V    |

| Digital I/O supply range                                            | DBVDD1         | 1.62 | 1.8 | 1.98 | V    |

| Digital I/O supply range (GPIO10, GPIO11, GPIO12, GPIO13, GPIO14)   | DBVDD2         | 1.62 |     | 3.63 | V    |

| Digital I/O supply range (GPIO4, GPIO5, GPIO6, GPIO7, GPIO8, GPIO9) | DBVDD2         | 1.62 |     | 3.63 | V    |

| PLL supply range                                                    | AVDD           | 1.14 | 1.2 | 1.32 | V    |

| Fuse programming supply                                             | PROGVDD        |      | 0   |      | V    |

| Ground                                                              | DGND           |      | 0   |      | V    |

| Operating temperature range                                         | T <sub>A</sub> | -40  |     | +85  | °C   |

#### Notes:

- 1. All supplies are independent of each other (i.e. not internally connected)

- 2. PROGVDD must be tied to 0V during normal operation

- 3. The WM0011 can operate with DBVDD2 tied to 0V, but GPIO10, GPIO11, GPIO12, GPIO13, GPIO14 functionality is not supported in this case

- 4. The WM0011 can operate with DBVDD3 tied to 0V, but GPIO4, GPIO5, GPIO6, GPIO7, GPIO8, GPIO9 functionality is not supported in this case

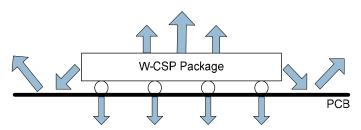

# THERMAL PERFORMANCE

Thermal analysis should be performed in the intended application to prevent the WM0011 from exceeding maximum junction temperature. Several contributing factors affect thermal performance most notably the physical properties of the mechanical enclosure, location of the device on the PCB in relation to surrounding components and the number of PCB layers. Connecting the GND pin through thermal vias and into a large ground plane will aid heat extraction.

Three main heat transfer paths exist to surrounding air as illustrated below in:

- Package top to air (radiation)

- Package bottom to PCB (radiation)

- Package pins to PCB (conduction)

Figure 1 Heat Transfer Paths

The temperature rise  $T_R$  is given by  $T_R = P_D * \Theta_{JA}$

- P<sub>D</sub> is the power dissipated in the device.

- Θ<sub>JA</sub> is the thermal resistance from the junction of the die to the ambient temperature and is therefore a measure of heat transfer from the die to surrounding air. Θ<sub>JA</sub> is determined with reference to JEDEC standard JESD51-9.

The junction temperature  $T_J$  is given by  $T_J = T_A + T_R$ , where  $T_A$  is the ambient temperature.

| PARAMETER            | SYMBOL         | MIN | TYP | MAX  | UNIT |

|----------------------|----------------|-----|-----|------|------|

| Ambient Temperature  | T <sub>A</sub> | -40 |     | +85  | °C   |

| Junction Temperature | $T_J$          | -40 |     | +125 | Ĵ    |

| Thermal Resistance   | ӨЈА            |     | 58  |      | °C/W |

#### Note:

- 1. Junction temperature is a function of ambient temperature and of the device operating conditions. The ambient temperature limits and junction temperature limits must both be observed.

- 2. Thermal resistance  $(\Theta_{JA})$  is measured using JESD51-2 methodology

# **ELECTRICAL CHARACTERISTICS**

#### **Test Conditions**

DCVDD=AVDD=1.2V, DBVDD1=DBVDD2=DBVDD3=1.8V,  $T_A$  = +25°C

| PARAMETER                                       | SYMBOL          | TEST CONDITIONS                                                 | MIN                           | TYP | MAX                           | UNIT |

|-------------------------------------------------|-----------------|-----------------------------------------------------------------|-------------------------------|-----|-------------------------------|------|

| Digital Input / Output                          |                 |                                                                 |                               |     | •                             | •    |

| Input HIGH Level,<br>GPIO[49] pads              | V <sub>IH</sub> |                                                                 | 0.65 x<br>V <sub>DBVDD3</sub> |     |                               | V    |

| Input LOW Level,<br>GPIO[49] pads               | V <sub>IL</sub> |                                                                 |                               |     | 0.35 x<br>V <sub>DBVDD3</sub> | V    |

| Input HIGH Level,<br>GPIO[1014] pads            | V <sub>IH</sub> |                                                                 | 0.65 x<br>V <sub>DBVDD2</sub> |     |                               | ٧    |

| Input LOW Level,<br>GPIO[1014] pads             | V <sub>IL</sub> |                                                                 |                               |     | 0.35 x<br>V <sub>DBVDD2</sub> | ٧    |

| Input HIGH Level,<br>All other digital pads     | V <sub>IH</sub> |                                                                 | 0.65 x<br>V <sub>DBVDD1</sub> |     |                               | ٧    |

| Input LOW Level,<br>All other digital pads      | V <sub>IL</sub> |                                                                 |                               |     | 0.35 x<br>V <sub>DBVDD1</sub> | V    |

| Output HIGH Level,<br>GPIO[49] pads             | V <sub>OH</sub> | I <sub>OH</sub> = 5mA<br>Full strength output drive (*_DS = 1)  | 0.75 x<br>V <sub>DBVDD3</sub> |     |                               | V    |

| Output LOW Level,<br>GPIO[49] pads              | V <sub>OL</sub> | I <sub>OL</sub> = -5mA<br>Full strength output drive (*_DS = 1) |                               |     | 0.25 x<br>V <sub>DBVDD3</sub> | V    |

| Output HIGH Level,<br>GPIO[1014] pads           | V <sub>OH</sub> | I <sub>OH</sub> = 5mA<br>Full strength output drive (*_DS = 1)  | 0.75 x<br>V <sub>DBVDD2</sub> |     |                               | ٧    |

| Output LOW Level,<br>GPIO[1014] pads            | V <sub>OL</sub> | $I_{OL} = -5mA$<br>Full strength output drive (*_DS = 1)        |                               |     | 0.25 x<br>V <sub>DBVDD2</sub> | V    |

| Output HIGH Level,<br>All other digital pads    | V <sub>OH</sub> | I <sub>OH</sub> = 1mA<br>Full strength output drive (*_DS = 1)  | 0.75 x<br>V <sub>DBVDD1</sub> |     |                               | V    |

| Output LOW Level,<br>All other digital pads     | V <sub>OL</sub> | I <sub>OL</sub> = -1mA<br>Full strength output drive (*_DS = 1) |                               |     | 0.25 x<br>V <sub>DBVDD1</sub> | V    |

| Input Capacitance                               | C <sub>IN</sub> |                                                                 |                               |     | 2.8                           | pF   |

| Input Leakage                                   |                 |                                                                 | -10                           |     | +10                           | μA   |

| Pull-up resistance,<br>GPIO[414] pads           |                 | Pull-Up enabled for the respective pad (*_PU = 1)               |                               | 61  |                               | kΩ   |

| Pull-down resistance,<br>GPIO[414] pads         |                 | Pull-Down enabled for the respective pad (*_PD = 1)             |                               | 61  |                               | kΩ   |

| Pull-up resistance,<br>All other digital pads   |                 | Pull-Up enabled for the respective pad (*_PU = 1)               |                               | 38  |                               | kΩ   |

| Pull-down resistance,<br>All other digital pads |                 | Pull-Down enabled for the respective pad (*_PD = 1)             |                               | 40  |                               | kΩ   |

Selectable output drive strength control is provided on the digital output pads, using the \*\_DS register bits. The reduced drive strength option may be used at lower clock speeds, if preferred. Specific characteristic data for reduced drive strength is not available.

# TYPICAL POWER CONSUMPTION

Typical power consumption data is provided below for a number of different operating conditions.

#### **Test Conditions:**

DCVDD = AVDD = 1.2V, DBVDD1 = 1.8V, DBVDD2 = DBVDD3 = 0V,  $T_A$  = +25°C

| OPERATING MODE                    | TEST CONDITIONS                                                                                                                              | I <sub>DCVDD</sub> | I <sub>DBVDD1</sub> | I <sub>AVDD</sub> | TOTAL   |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------|-------------------|---------|

| Reset                             | RESET asserted CLKIN = 0MHz                                                                                                                  | 0.2mA              | 0.03mA              | 0.05mA            | 0.35mW  |

| BootROM (awaiting code download)  | RESET de-asserted<br>CLKIN = 24.576MHz                                                                                                       | 8.78mA             | 0.48mA              | 0.05mA            | 11.46mW |

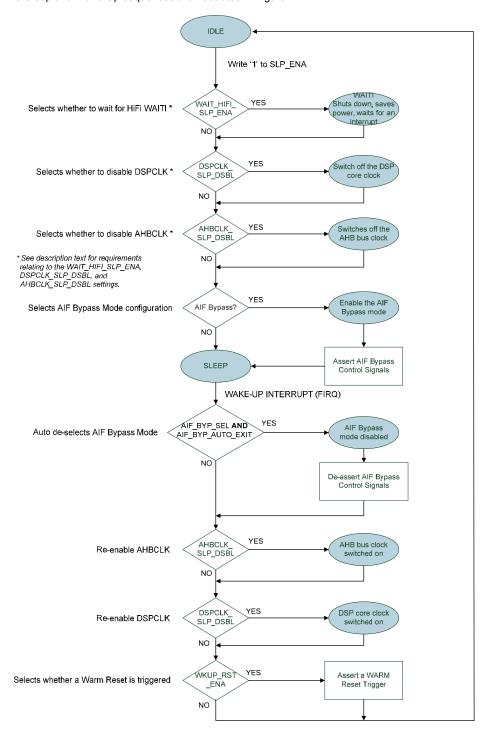

| Sleep Mode                        | RESET de-asserted  SLP_ENA=1 (CCM_WKUP_CTRL register)  CLKIN = 0MHz  DSPCLK disabled, AHBCLK disabled                                        | 0.25mA             | 0.02mA              | 0.05mA            | 0.40mW  |

|                                   | RESET de-asserted  SLP_ENA=1 (CCM_WKUP_CTRL register)  CLKIN = 24.576MHz  DSPCLK disabled, AHBCLK disabled  RAM & IRQC modules enabled       | 0.91mA             | 0.47mA              | 0.05mA            | 2.00mW  |

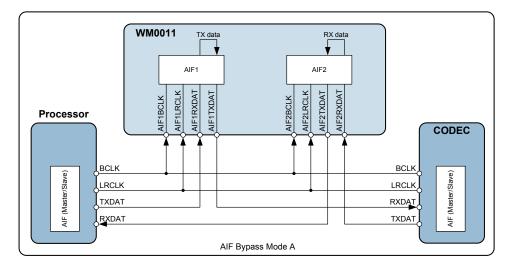

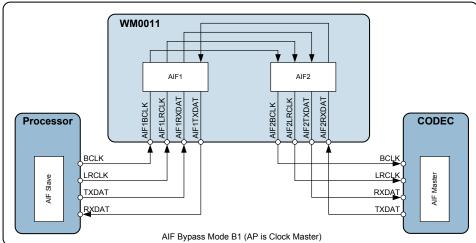

| Sleep Mode<br>AIF Bypass enabled  | RESET de-asserted  SLP_ENA=1 (CCM_WKUP_CTRL register)  CLKIN = 0MHz  DSPCLK disabled, AHBCLK disabled  AIF Bypass Mode A enabled             | 0.27mA             | 0.16mA              | 0.05mA            | 0.67mW  |

|                                   | RESET de-asserted SLP_ENA=1 (CCM_WKUP_CTRL register) CLKIN = 24.576MHz DSPCLK disabled, AHBCLK disabled AIF Bypass Mode A enabled            | 0.95mA             | 0.60mA              | 0.05mA            | 2.28mW  |

| Run Mode<br>(full processor load) | RESET de-asserted  SLP_ENA=0 (CCM_WKUP_CTRL register)  CLKIN = 24.576MHz  PLLOUT = 259.2MHz  All peripherals enabled  Processor fully loaded | 90mA               | 0.60mA              | 0.10mA            | 109.2mW |

The WM0011 supports a low-power Sleep mode, as referenced above. Note that, when the WM0011 is not in use, the Sleep mode (not the Reset mode) is recommended for typical applications. The Sleep mode allows the full processor functionality to be resumed at any time, without needing to re-load the software code. The Sleep mode also enables AIF Bypass modes to be selected.

# SIGNAL TIMING REQUIREMENTS SYSTEM CLOCK & PHASE LOCKED LOOP (PLL)

#### **Test Conditions**

DCVDD=AVDD=1.2V, DBVDD1=DBVDD2=DBVDD3=1.8V,  $T_A = +25^{\circ}C$

| PARAMETER               | SYMBOL | MIN  | TYP | MAX | UNIT |

|-------------------------|--------|------|-----|-----|------|

| External Clock Timing   |        |      |     |     |      |

| Chip Clock Input        | CLKIN  |      |     | 26  | MHz  |

| Alternate Clock Input   | ALTCLK |      |     | 26  | MHz  |

| Timer Clock Trigger     | TMRCLK |      |     | 26  | MHz  |

| Input Clock duty cycle  |        | 40   |     | 60  | %    |

| Phase Locked Loop (PLL) |        |      |     |     |      |

| PLL input frequency     | CLKIN  | 5    |     | 26  | MHz  |

| PLL input duty cycle    |        | 40   |     | 60  | %    |

| PLL output frequency    | PLLOUT | 6.25 |     | 260 | MHz  |

| PLL lock time           |        |      |     | 2   | ms   |

| Internal Clock Timing   |        |      |     |     |      |

| DSP Core Clock          | DSPCLK |      |     | 260 | MHz  |

| AHB Bus Clock           | AHBCLK |      |     | 130 | MHz  |

| APB Bus Clock           | APBCLK |      |     | 130 | MHz  |

Table 2 System Clock and Phase Locked Loop (PLL)

The WM0011 incorporates a 2-stage cascaded PLL circuit; the PLL timing parameters above refer to the 2-stage circuit in its entirety. Note that the specified frequency limits are not applicable to the internal reference points within the cascaded PLL circuits.

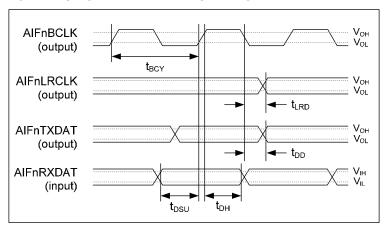

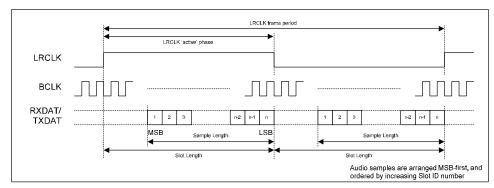

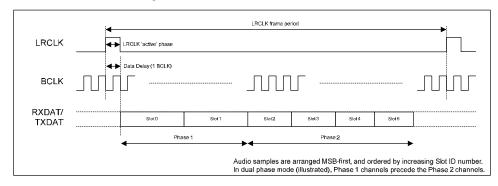

# **AUDIO INTERFACE (AIF) TIMING**

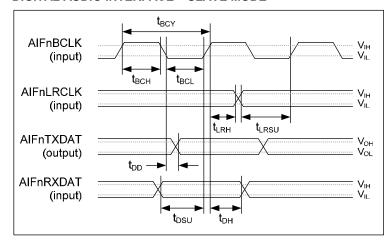

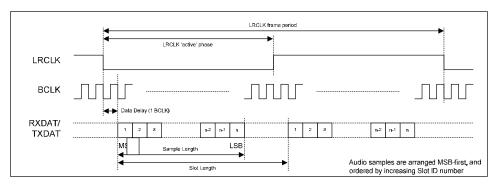

# **DIGITAL AUDIO INTERFACE - MASTER MODE**

Figure 2 AIF Interface Timing - Master Mode

#### **Test Conditions**

DCVDD=AVDD=1.2V, DBVDD1=DBVDD2=DBVDD3=1.8V,  $T_A = +25$ °C,  $C_{LOAD}$ =5pF (output pins)

| PARAMETER                                              | SYMBOL           | MIN  | TYP | MAX | UNIT |

|--------------------------------------------------------|------------------|------|-----|-----|------|

| Audio Interface Timing - Master Mode                   |                  |      |     |     |      |

| AIFnBCLK cycle time                                    | t <sub>BCY</sub> | 80   |     |     | ns   |

| AIFnBCLK duty cycle                                    |                  | 40   |     | 60  | %    |

| AIFnLRCLK propagation delay from AIFnBCLK falling edge | t <sub>LRD</sub> | 0    |     | 15  | ns   |

| AIFnTXDAT propagation delay from AIFnBCLK falling edge | t <sub>DD</sub>  | 0    |     | 15  | ns   |

| AIFnRXDAT setup time to AIFnBCLK rising edge           | t <sub>DSU</sub> | 16.3 |     |     | ns   |

| AIFnRXDAT hold time from AIFnBCLK rising edge          | t <sub>DH</sub>  | 16.3 |     |     | ns   |

**Table 3 AIF Master Mode Timing Values**

Note the timing figures quoted in the table above are for full drive strength outputs; these timings are not guaranteed for reduced drive strength.

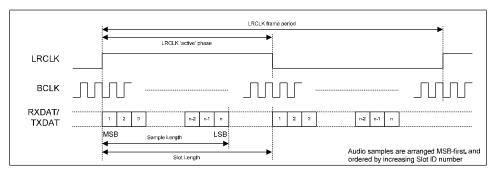

# **DIGITAL AUDIO INTERFACE - SLAVE MODE**

Figure 3 AIF Interface Timing - Slave Mode

# **Test Conditions**

DCVDD=AVDD=1.2V, DBVDD1=DBVDD2=DBVDD3=1.8V,  $T_A$  = +25°C,  $C_{LOAD}$ =5pF (output pins)

| PARAMETER                                              | SYMBOL            | MIN  | TYP | MAX | UNIT |

|--------------------------------------------------------|-------------------|------|-----|-----|------|

| Audio Interface Timing - Slave Mode                    |                   |      |     |     |      |

| AIFnBCLK cycle time                                    | t <sub>BCY</sub>  | 80   |     |     | ns   |

| AIFnBCLK duty cycle                                    |                   | 35   |     | 65  | %    |

| AIFnLRCLK set-up time to AIFnBCLK rising edge          | t <sub>LRSU</sub> | 16.3 |     |     | ns   |

| AIFnLRCLK hold time from AIFnBCLK rising edge          | t <sub>LRH</sub>  | 7.5  |     |     | ns   |

| AIFnRXDAT hold time from AIFnBCLK rising edge          | t <sub>DH</sub>   | 10   |     |     | ns   |

| AIFnTXDAT propagation delay from AIFnBCLK falling edge | t <sub>DD</sub>   | 0    |     | 12  | ns   |

| AIFnRXDAT set-up time to AIFnBCLK rising edge          | t <sub>DSU</sub>  | 16.3 |     |     | ns   |

Table 4 AIF Slave Mode Timing Values

Note the timing figures quoted in the table above are for full drive strength outputs; these timings are not guaranteed for reduced drive strength.

# **SPI INTERFACE TIMING**

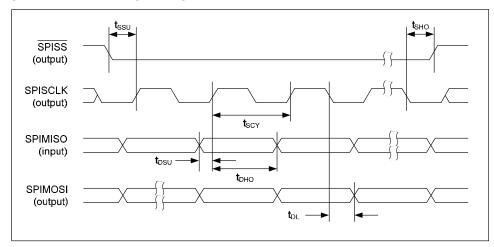

# SPI INTERFACE - MASTER MODE

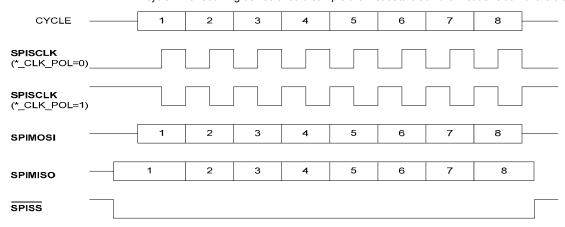

Figure 4 SPI Master Mode Timing

Note this diagram shows the mode where incoming data (SPIMISO) is sampled on the rising edge of SPISCLK, and outgoing data (SPIMOSI) transitions on the falling edge of SPISCLK.

Test Conditions AVDD=DCVDD=1.2V, DBVDD1=DBVDD2=DBVDD3=1.8V,  $T_A = +25^{\circ}C$ ,  $C_{LOAD}$ =5pF (output pins), unless otherwise stated.

| PAF                        | SYMBOL                       | MIN              | TYP           | MAX      | UNIT |    |

|----------------------------|------------------------------|------------------|---------------|----------|------|----|

| SPI Interface Timing - Mas | ter Mode                     |                  |               |          |      |    |

| SPISS set-up time to SPISC | LK rising edge               | t <sub>ssu</sub> | 25            |          |      | ns |

| SPISS hold time from SPISO | CLK falling edge             | t <sub>sho</sub> | 25            |          |      | ns |

| SPISCLK pulse cycle time   |                              | t <sub>SCY</sub> | 61.6          |          |      | ns |

| In SPI Master mode, the ma | MHz. It is also re           | quired that F    | SPISCLK ≤ FAI | HBCLK/8. |      |    |

| SPISCLK duty cycle         |                              |                  | 40            |          | 60   | %  |

| SPIMISO set-up time to SPI | SCLK rising edge             | t <sub>DSU</sub> | 10.5          |          |      | ns |

| SPIMISO hold time from SP  | ISCLK rising edge            | t <sub>DHO</sub> | 2.0           |          |      | ns |

| SPIMOSI propagation        | 5pF, reduced drive strength  | t <sub>DL</sub>  |               |          | 5.1  | ns |

| delay from SPISCLK         | 5pF, full drive strength     |                  |               |          | 4.7  |    |

| falling edge               | 25pF, reduced drive strength |                  |               |          | 6.3  |    |

|                            | 25pF, full drive strength    |                  |               |          | 8.7  |    |

Table 5 SPI Master Mode Timing Values

Note the timing figures quoted in the table above are for full drive strength outputs (except where otherwise stated); these timings are not guaranteed for reduced drive strength.

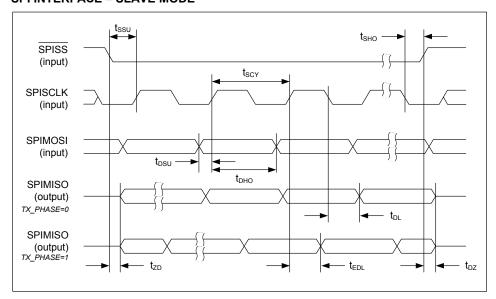

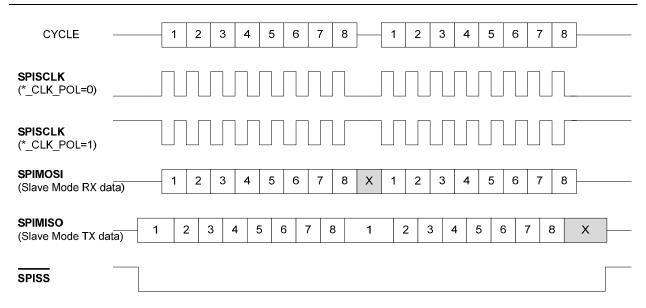

# SPI INTERFACE - SLAVE MODE

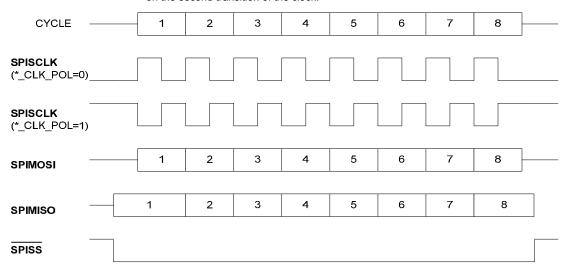

Figure 5 SPI Slave Mode Timing

Note this diagram shows the mode where incoming data (SPIMOSI) is sampled on the rising edge of SPISCLK. By default, the outgoing data (SPIMISO) transitions on the falling edge of SPISCLK. When 'Early Transmit Data Phase' mode is selected (TX\_PHASE=1), the outgoing data (SPIMISO) transitions on the rising edge of SPISCLK.

# **Test Conditions**

$AVDD=DCVDD=1.2V,\ DBVDD1=DBVDD2=DBVDD3=1.8V,\ T_A=+25^{\circ}C,\ C_{LOAD}=5pF\ (output\ pins),\ unless\ otherwise\ stated.$

| PARAMETER                                                       |                         | SYMBOL                | MIN                       | TYP                        | MAX  | UNIT |

|-----------------------------------------------------------------|-------------------------|-----------------------|---------------------------|----------------------------|------|------|

| SPI Interface Timing - Slave Mode                               |                         |                       |                           |                            |      |      |

| SPISS set-up time to SPISCLK rising edge                        |                         | t <sub>ssu</sub>      | t <sub>AHBCLK</sub> + 1.0 |                            |      | ns   |

| SPISS hold time from SPISCLK falling edge                       |                         | t <sub>SHO</sub>      | 2.0                       |                            |      | ns   |

| SPISCLK pulse cycle time                                        |                         | t <sub>scy</sub>      | 38.5                      |                            |      | ns   |

| In SPI Slave mode, the maximum SPISCLK f                        | requency is 26MH:       | z. It is also require | d that F <sub>SPISC</sub> | LK < F <sub>AHBCLK</sub> . |      |      |

| SPISCLK duty cycle                                              |                         |                       | 40                        |                            | 60   | %    |

| SPIMOSI set-up time to SPISCLK rising edge                      | )                       | t <sub>DSU</sub>      | 2.0                       |                            |      | ns   |

| SPIMOSI hold time from SPISCLK rising edge                      | е                       | t <sub>DHO</sub>      | 2.0                       |                            |      | ns   |

| SPIMISO propagation delay from                                  | C <sub>LOAD</sub> =25pF | t <sub>DL</sub>       |                           |                            | 12.1 | ns   |

| SPISCLK falling edge                                            | C <sub>LOAD</sub> =5pF  |                       |                           |                            | 9.3  |      |

| SPIMISO propagation delay from C <sub>LOAD</sub> =25pF          |                         | $t_{\sf EDL}$         |                           |                            | 14.1 | ns   |

| SPISCLK rising edge (early TX data mode) C <sub>LOAD</sub> =5pF |                         |                       |                           |                            | 11.3 |      |

| SPIMISO enable from SPISS falling edge                          |                         | t <sub>ZD</sub>       |                           |                            | 13.6 | ns   |

| SPIMISO disable from SPISS rising edge                          |                         | t <sub>DZ</sub>       |                           |                            | 7.8  | ns   |

Table 6 SPI Slave Mode Timing Values

Note the timing figures quoted in the table above are for full drive strength outputs; these timings are not guaranteed for reduced drive strength.

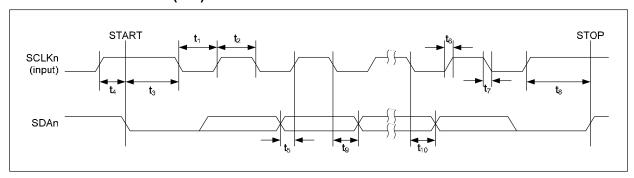

# **CONTROL INTERFACE (12C) TIMING**

Figure 6 I<sup>2</sup>C Control Interface Timing

#### **Test Conditions**

AVDD= DCVDD=1.2V, DBVDD1=DBVDD2=DBVDD3=1.8V,  $T_A$  = +25°C, unless otherwise stated.

| PARAME                             | TER              | SYMBOL          | MIN | TYP | MAX  | UNIT |

|------------------------------------|------------------|-----------------|-----|-----|------|------|

| SCLKn Frequency                    |                  |                 |     |     | 1000 | kHz  |

| SCLKn Low Pulse-Width              |                  | t <sub>1</sub>  | 500 |     |      | ns   |

| SCLKn High Pulse-Width             |                  | t <sub>2</sub>  | 260 |     |      | ns   |

| Hold Time (Start Condition)        | Pulse filter OFF | t <sub>3</sub>  | 260 |     |      | ns   |

|                                    | Pulse filter ON  |                 | 275 |     |      |      |

| Setup Time (Start Condition)       |                  | t <sub>4</sub>  | 260 |     |      | ns   |

| SDAn, SCLKn Rise Time              |                  | t <sub>6</sub>  |     |     | 120  | ns   |

| SDAn, SCLKn Fall Time              |                  | t <sub>7</sub>  |     |     | 120  | ns   |

| Setup Time (Stop Condition)        |                  | t <sub>8</sub>  | 260 |     |      | ns   |

| SDAn Setup Time (data/ACK input)   |                  | t <sub>5</sub>  | 50  |     |      | ns   |

| SDAn Hold Time (data/ACK input)    |                  | t <sub>9</sub>  | 0   |     |      | ns   |

| SDAn Valid Time (data/ACK output)  |                  | t <sub>10</sub> |     |     | 450  | ns   |

| Pulse width of spikes that will be | suppressed       | t <sub>ps</sub> | 0   |     | 50   | ns   |

Table 7 I<sup>2</sup>C Timing Values

# DEVICE DESCRIPTION INTRODUCTION

The WM0011 is an audio DSP designed for smartphones and other high performance audio applications. The architecture is optimised for multi-channel audio processing such as software CODECs, equalisation, compression and echo cancellation.

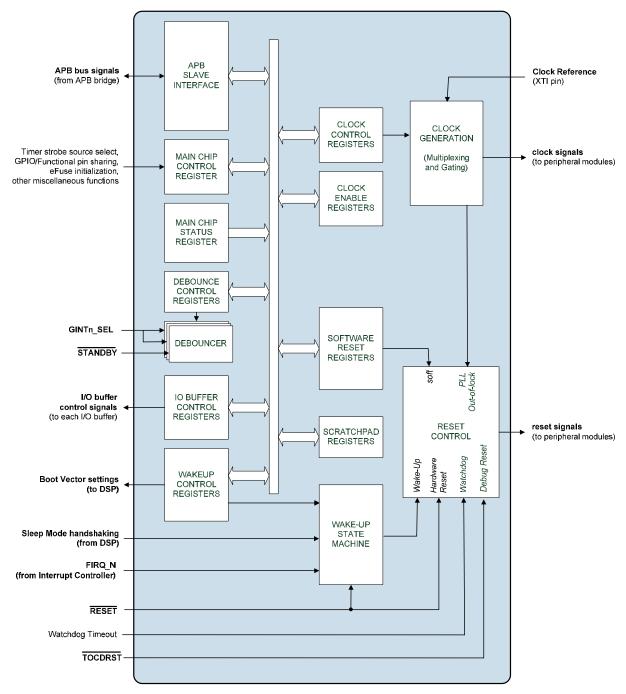

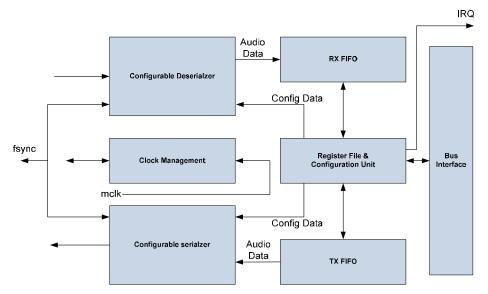

#### **BLOCK DIAGRAM**

Figure 7 WM0011 Block Diagram

# **DESCRIPTION OF MODULES**

#### **BOOT ROM**

The 32kB boot ROM allows the WM0011 to boot from a variety of sources. These are listed in the table below.

| MODULE BOOTABLE FROM |                             |

|----------------------|-----------------------------|

| SPI Slave            | External host processor     |

| SPI Master           | SST25WFxxx SPI Serial Flash |

#### **TIGHTLY-COUPLED MEMORY (TCM) RAM**

The DSP's primary memory comprises 64-bit wide, zero-latency tightly coupled memory.

- 128kB of instruction RAM

- 128kB of data RAM

#### **MULTI-PURPOSE RAM**

The 384kB system RAM is connected to the DSP via the system bus. This RAM can be used for storing either instructions or data. Both data and instructions can be transferred in and out of TCM by DMA.

# TENSILICA HIFI EP™ DSP CORE

The core combines a 24-bit audio DSP engine that has been optimised for highly efficient high-resolution audio processing, with a GCC-compatible (GNU Compiler Collection) general purpose RISC instruction set. It includes logic to interface with the AHB bus and the TRAX Trace Buffer, and to the JTAG TAP controller in order to provide support for On-Chip Debug (OCD). The HiFi  $EP^{TM}$  features:

- 7-stage instruction pipeline

- One load-store unit

- 12kB 3-way Instruction Cache (64-bit width), and corresponding TAG memory

- 24kB 3-way Data Cache (64-bit width), and corresponding TAG memory

- Pre-fetch buffering for slow external RAM support

- TCM Core Instruction RAM (64-bit width)

- PIF-to-AHB-Lite Bridge, Synchronous, 64-bit width

- Three general purpose timers

- Interrupt controller, with sixteen external and five internal interrupt inputs

- On-Chip Debug (OCD) support

- Trace port and corresponding 1kB TRAX trace RAM (32-bit width)

- Floating point accelerator

For more detailed information on the Tensilica HiFi EP™ core, refer to the 'HiFi EP Audio Engine Instruction Set Architecture Reference Manual' (HIFIEP-ISA-rm.pdf), available from Tensilica.

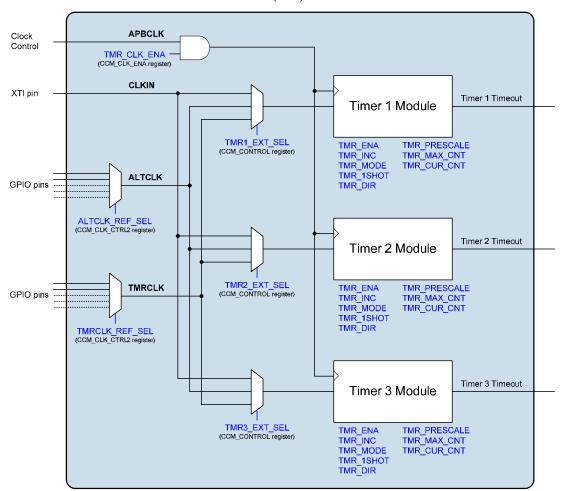

#### **TIMER MODULE**

Three 32-bit general-purpose timers are provided. The timers can be configured as up-counters or as down-counters. The Timer block features include:

- Free-running counter operation (triggered internally or externally)

- Event counter operation (externally triggered)

- One-shot operation from either an external or an internal trigger

# **WATCHDOG MODULE**

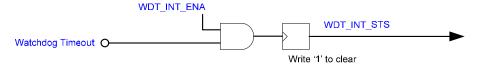

A watchdog timer block is provided as a means to reset the WM0011 chip in the case of a software failure. A timeout of the watchdog produces a Warm Reset (maskable) that includes a reset of most registers and state machines, and of the PLL.

# **GPIO MODULE**

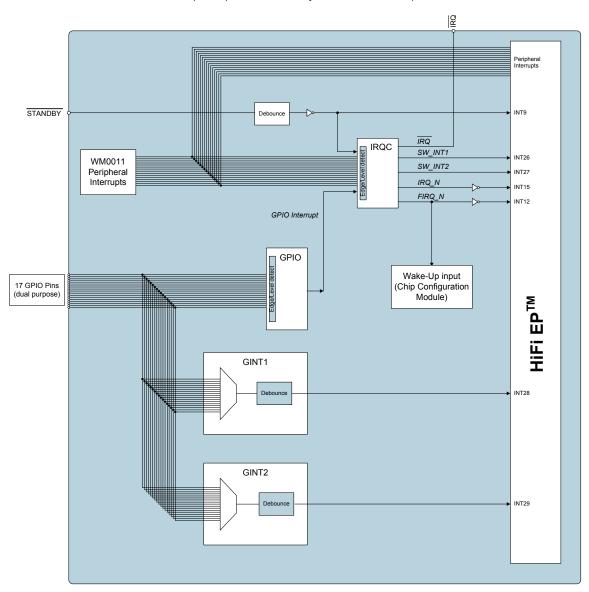

There is one GPIO controller controlling seventeen multiplexed GPIO inputs. Two of these inputs can be selected as an interrupt to HiFi EP<sup>TM</sup>, or one can be selected to be used as an input to the IRQC controller.

# **IRQC MODULE**

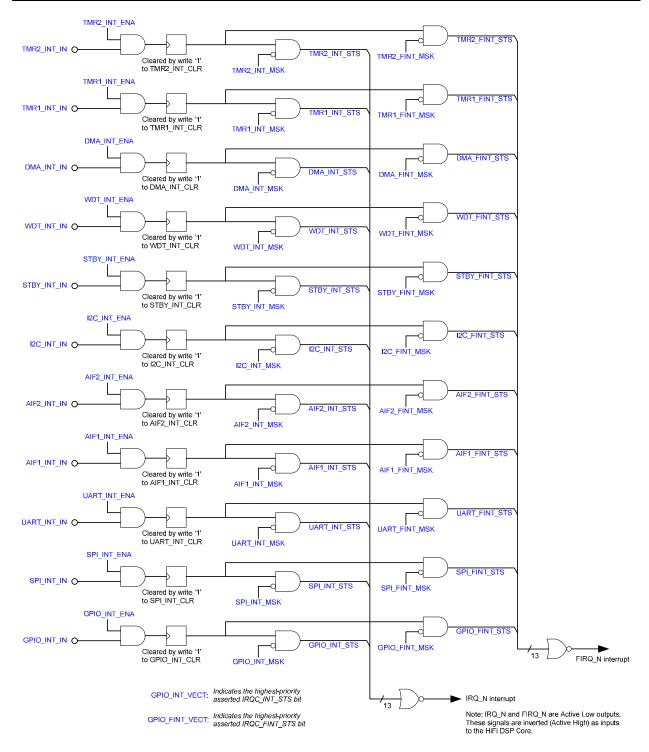

The IRQC controller provides fine control of interrupts (edge control, etc). It also enables wake-up, and controls the external IRQ output pin. Table 8 shows the IRQC assignments.

| IRQC BIT | DIRECTION | DESCRIPTION                                                                                           |

|----------|-----------|-------------------------------------------------------------------------------------------------------|

| 15       | Output    | Software interrupt – HiFi EP™ interrupt input                                                         |

| 14       | Output    | Software interrupt – HiFi EP™ interrupt input                                                         |

| 13       | Input     | Reserved                                                                                              |

| 12       | Input     | Reserved                                                                                              |

| 11       | Input     | Timer 2 interrupt                                                                                     |

| 10       | Input     | Timer 1 interrupt                                                                                     |

| 9        | Input     | DMA interrupt                                                                                         |

| 8        | Input     | Watchdog interrupt                                                                                    |

| 7        | Input     | STANDBY pin (Active Low)                                                                              |

|          |           | Note this input is inverted internally, and is therefore Active High at the input to the IRQC module. |

| 6        | Input     | I2C interrupt                                                                                         |

| 5        | Input     | AIF 2 interrupt                                                                                       |

| 4        | Input     | AIF 1 interrupt                                                                                       |

| 3        | Input     | UART interrupt                                                                                        |

| 2        | Input     | SPI interrupt                                                                                         |

| 1        | Input     | Cascaded interrupt input from the GPIO controller (Active Low)                                        |

| 0        | Output    | IRQ pin (Active Low)                                                                                  |

Table 8 IRQC Interrupt assignment

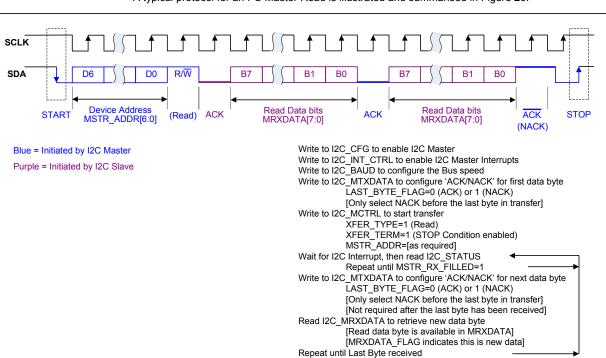

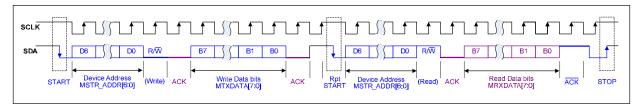

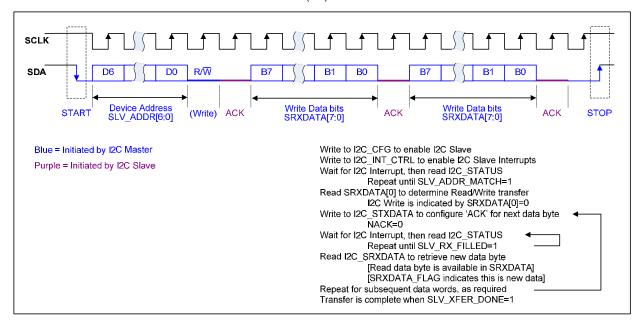

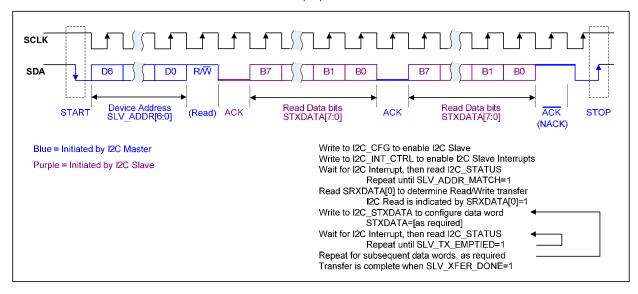

## I<sup>2</sup>C MASTER AND SLAVE MODULE

The  $I^2C$  module provides two independent  $I^2C$  buses. These are configured as one master and one slave. External pins are multiplexed such that only one of the  $I^2C$  Master, the  $I^2C$  slave, or the UART can be configured at any one time.