#### Click here to ask an associate for production status of specific part numbers.

### **General Description**

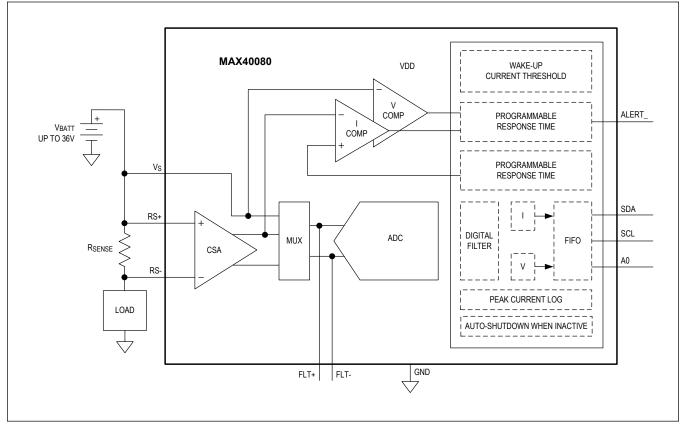

The MAX40080 is a high-precision, fast-response, bi-directional current-sense amplifier with digital output and a very wide input common-mode range from -0.1V (ground sensing) to 36V.

The device features an ultra-low  $5\mu$ V input offset voltage and a very low 0.2% gain error. The low input offset voltage is especially important because it allows using a small sense resistor, thus saving power dissipation, but at the same time not compromising the measurement accuracy. The device also features a programmable input sensing range between  $\pm 10$ mV and  $\pm 50$ mV (or programmable input gain between 125V/V and 25V/V) which is very useful to enhance accuracy at low current.

The device includes an analog-to-digital converter with a programmable sample rate and 12-bit resolution (13-bit including sign bit for current measurement) and features an  $I^2C$  compliant and SMBus compatible interface.

The device features a wake-up current threshold and auto-shutdown mode when the  $I^2C$  is inactive. Both these features are designed to minimize power consumption.

The device is available in a small 12-pin WLP (and also a 12-pin TDFN) and is specified over the -40°C to +125°C extended operating temperature range.

### **Applications**

- Server Backplanes

- Base-Station PA Control

- Telecom Equipment

- Battery Operated Devices

- Industrial Control and Automation

### Precision, Fast Sample-Rate, Digital Current-Sense Amplifier

### **Benefits and Features**

- Programmable Sample Rate up to 1Msps

- Wide Input Common-Mode range from -0.1V (ground sensing) to 36V

- Programmable Input Sense Range (±10mV and ±50mV)

- Very low 5µV Input Offset Voltage allows using a small sense resistor

- I<sup>2</sup>C compliant and SMBus compatible interface with smart modes to save power:

- Wake-up current threshold

- Low 4 measurements/s rate

- Auto-shutdown when I<sup>2</sup>C is inactive

- Bi-directional current sensing

- Common-Mode Voltage monitoring up to 36V

- Space-saving 12-bump WLP (0.4mm pitch) and 12-pin TDFN

- Peak current Log

- Programmable over-current/voltage thresholds and under-voltage threshold

- Alert output with programmable response time

- 64-cell deep FIFO

Ordering Information appears at end of data sheet.

© 2021 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners.

# Precision, Fast Sample-Rate, Digital Current-Sense Amplifier

### **Block Diagram**

Precision, Fast Sample-Rate, Digital Current-Sense Amplifier

### **TABLE OF CONTENTS**

| General Description.                                          | <br>. 1 |

|---------------------------------------------------------------|---------|

| Applications                                                  | <br>. 1 |

| Benefits and Features                                         | <br>. 1 |

| Block Diagram                                                 | <br>. 2 |

| Absolute Maximum Ratings                                      | <br>. 7 |

| Package Information                                           | <br>. 8 |

| WLP                                                           | <br>. 8 |

| TDFN*                                                         | <br>. 9 |

| Electrical Characteristics                                    | <br>11  |

| Typical Operating Characteristics                             | <br>15  |

| Pin Configurations                                            | <br>19  |

| WLP-12                                                        | <br>19  |

| TDFN                                                          | <br>19  |

| Pin Description                                               | <br>20  |

| Detailed Description                                          | <br>21  |

| I <sup>2</sup> C-Compliant and SMBus-Compatible Bus Interface | <br>21  |

| I <sup>2</sup> C Slave Address                                | <br>24  |

| I <sup>2</sup> C Communication Speed.                         | <br>25  |

| Engaging HS-Mode for Operation up to 3.4MHz.                  | <br>25  |

| Modes of Operation                                            | <br>26  |

| Alert Management                                              | <br>26  |

| Internal Registers                                            | <br>27  |

| Configuration Register.                                       | <br>28  |

| Operation Modes                                               | <br>28  |

| I <sup>2</sup> C Timeout                                      | <br>28  |

| Alert Response Time                                           | <br>28  |

| PEC                                                           | <br>28  |

| Input Range                                                   | <br>29  |

| Stay HS Mode                                                  | <br>29  |

| ADC Sample Rate                                               | <br>29  |

| Digital Filter                                                | <br>29  |

| Status Register                                               | <br>30  |

| Wake-Up Current                                               | <br>30  |

| Conversion Ready                                              | <br>31  |

| Overflow Current                                              | <br>31  |

| Overflow or Underflow Voltage                                 | <br>31  |

| I <sup>2</sup> C Timeout                                      |         |

| FIFO Alarm.                                                   | <br>31  |

| FIFO Overflow                                                 | <br>31  |

Precision, Fast Sample-Rate, Digital Current-Sense Amplifier

# TABLE OF CONTENTS (CONTINUED)

| FIFO Data Count                          | . 31 |

|------------------------------------------|------|

| Thresholds and Wake-Up Current registers | . 31 |

| MAX_Peak_Current                         | . 32 |

| FIFO Configuration                       | . 32 |

| Store IV                                 | . 32 |

| Overflow_Threshold                       | . 32 |

| R0                                       | . 32 |

| Flush                                    | . 33 |

| Read Current and Voltage from the FIFO   | . 33 |

| INT_EN                                   | . 33 |

| Applications Information                 | . 34 |

| Filter Selection                         | . 34 |

| FIFO Reading Data Rate                   | . 34 |

| Ordering Information                     | . 36 |

| Revision History                         | . 37 |

Precision, Fast Sample-Rate, Digital Current-Sense Amplifier

### LIST OF FIGURES

| Figure 1. I <sup>2</sup> C/SMBus Timing Diagram | 21 |

|-------------------------------------------------|----|

| Figure 2. 2-Byte Write (Write Word)             | 21 |

| Figure 3. 2-Byte Write with PEC Byte            | 22 |

| Figure 4. 2-Byte Read (Read Word)               | 22 |

| Figure 5. 2-Byte Read with PEC Byte             | 22 |

| Figure 6. One-Byte Read                         | 23 |

| Figure 7. One-Byte Read with PEC                | 23 |

| Figure 8. Read 32                               | 23 |

| Figure 9. Read 32 with PEC                      | 24 |

| Figure 10. Engaging HS Mode                     | 26 |

| Figure 11. Quick Command                        | 26 |

Precision, Fast Sample-Rate, Digital Current-Sense Amplifier

### LIST OF TABLES

| Table 1. I <sup>2</sup> C Slave Addresses                            | 24   |

|----------------------------------------------------------------------|------|

| Table 2. Register Functions and POR States                           | . 27 |

| Table 3. Operation Mode                                              | 28   |

| Table 4. Sample Rate Selection                                       | 29   |

| Table 5. Digital Filter Selection                                    | 30   |

| Table 6. Output Data Rate vs. Sample Rate                            | 30   |

| Table 7. Thresholds and Wake-Up Current registers                    | . 31 |

| Table 8. Filter Cap Selection                                        | 34   |

| Table 9. FIFO Reading Data Rate vs. I <sup>2</sup> C Interface Speed | 34   |

| Table 10. Read 2 Bytes                                               | 35   |

| Table 11. Read 4 Bytes                                               | 35   |

# Precision, Fast Sample-Rate, Digital Current-Sense Amplifier

### **Absolute Maximum Ratings**

| V <sub>DD</sub> to GND                 | 0.3V to +2V |

|----------------------------------------|-------------|

| RS+ to RS                              | ±2V         |

| V <sub>S</sub> , RS+, RS- to GND       |             |

| All other pins to GND                  |             |

| Continuous current into any input pin  |             |

| Continuous current into any input pirt |             |

| Continuous Power Dissipation (Multilayer | Board) ( $T_A = +70^{\circ}C$ , |

|------------------------------------------|---------------------------------|

| derate 13.73mW/°C above +70°C.)          |                                 |

| Operating Temperature Range              | 40°C to +125°C                  |

| Junction Temperature                     | +150°C                          |

| Storage Temperature Range                | 40°C to +150°C                  |

| Soldering Temperature (reflow)           | +260°C                          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### Package Information

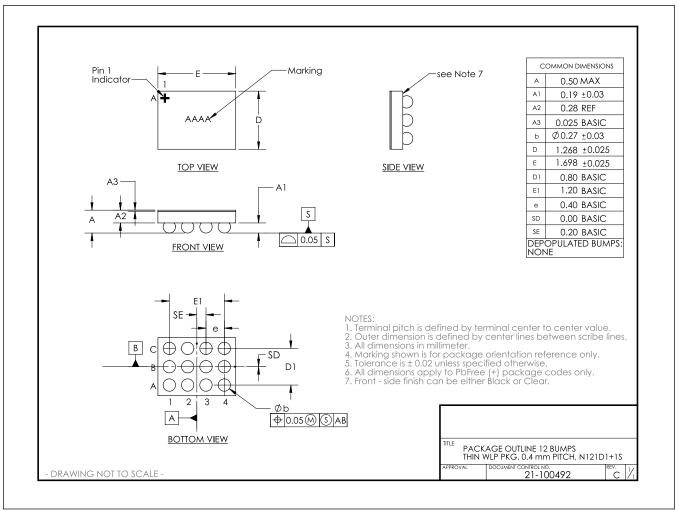

#### WLP

| Package Code                                                | N121D1+1S        |  |  |  |  |

|-------------------------------------------------------------|------------------|--|--|--|--|

| Outline Number                                              | <u>21-100492</u> |  |  |  |  |

| Land Pattern Number   Refer to <u>Application Note 1891</u> |                  |  |  |  |  |

| Thermal Resistance, Four-Layer Board:                       |                  |  |  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                      | 72.82°C/W        |  |  |  |  |

| Junction-to-Case Thermal Resistance $(\theta_{JC})$         | 17.90°C/W        |  |  |  |  |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/</u> <u>thermal-tutorial</u>.

# Precision, Fast Sample-Rate, Digital Current-Sense Amplifier

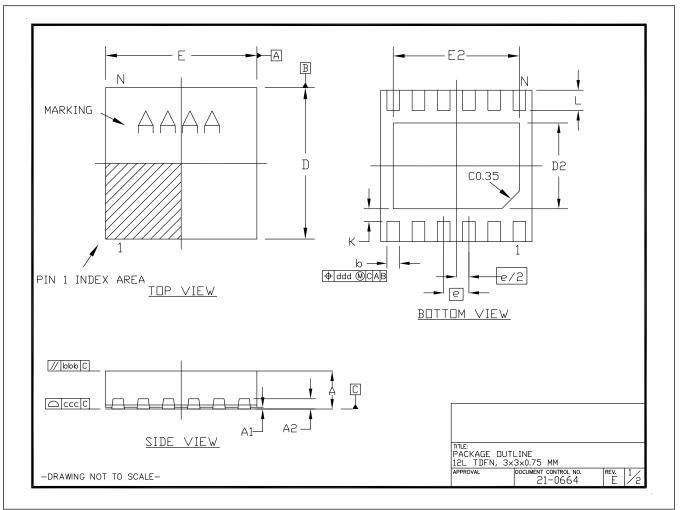

#### **TDFN\***

| Package Code                                          | TD1233+1C      |

|-------------------------------------------------------|----------------|

| Outline Number                                        | <u>21-0664</u> |

| Land Pattern Number                                   | <u>90-0397</u> |

| Thermal Resistance, Single-Layer Board:               |                |

| Junction-to-Ambient (θ <sub>JA</sub> )                | 63 °C/W        |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) | 8.5 °C/W       |

| Thermal Resistance, Four-Layer Board:                 |                |

| Junction-to-Ambient (θ <sub>JA</sub> )                | 41 °C/W        |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) | 8.5 °C/W       |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/</u> <u>thermal-tutorial</u>.

# Precision, Fast Sample-Rate, Digital Current-Sense Amplifier

|                                                                                                                                | ח                                          | IMENSION                                 | AL REFER                               | ENCES  |         |           |         |  |

|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------------------------------|----------------------------------------|--------|---------|-----------|---------|--|

|                                                                                                                                | SYMBOL                                     | MIN                                      | NDM                                    | MAX    | MIN     | NDM       | MAX     |  |

| TOTAL THICKNESS                                                                                                                | A                                          | 0.7                                      | 0.75                                   | 0.8    | 0.7     | 0.75      | 0.8     |  |

| STAND OFF                                                                                                                      | A1                                         | 0                                        | 0.035                                  | 0.05   | 0       | 0.035     | 0.05    |  |

| L/F THICKNESS                                                                                                                  | A2                                         |                                          | 0.203 REF                              |        |         | 0.203 REF |         |  |

| LEAD WIDTH                                                                                                                     | b                                          | 0.2                                      | 0.25                                   | 0.3    | 0.2     | 0.25      | 0.3     |  |

| BODY SIZE                                                                                                                      | D                                          | 2.9                                      | 3.0                                    | 3.1    | 2.95    | 3.00      | 3.05    |  |

| BUDI SIZE                                                                                                                      | E                                          | 2.9                                      | 3.0                                    | 3.1    | 2.95    | 3.00      | 3.05    |  |

| LEAD PITCH                                                                                                                     | e                                          |                                          | 0.5 BSC                                |        |         | 0.5 BSC   |         |  |

| EP SIZE                                                                                                                        | D2                                         | 1.6                                      | 1.7                                    | 1.8    | 1.45    | 1.55      | 1.65    |  |

| EF SIZE                                                                                                                        | E2                                         | 2.4                                      | 2.5                                    | 2.6    | 2.4     | 2.50      | 2.6     |  |

| LEAD LENGTH                                                                                                                    | L                                          | 0.35                                     | 0.4                                    | 0.45   | 0.30    | 0.4       | 0.50    |  |

| PACKAGE EDGE TOLERANCE                                                                                                         | ممم                                        |                                          | 0.1                                    |        |         | 0.1       |         |  |

| MOLD FLATNESS                                                                                                                  | bbb                                        |                                          | 0.1                                    |        |         | 0.1       |         |  |

| COPLANARITY                                                                                                                    | ссс                                        |                                          | 0.08                                   |        |         | 0.08      |         |  |

| LEAD DFFSET                                                                                                                    | ddd                                        |                                          | 0.1                                    |        |         | 0.1       |         |  |

| EXP PAD TO LEAD EDGE                                                                                                           | К                                          |                                          | 0.25 min                               |        |         | 0.25 min  |         |  |

| LEAD COUNT                                                                                                                     | N                                          |                                          | 12                                     |        |         | 12        |         |  |

| PKG CODE:                                                                                                                      |                                            | TD1233+                                  | TD1233+1, TD1233+1C                    |        | TD1233+ | 2, ТД1233 | +2C,    |  |

| AOTES:<br>. ALL DIMENSIONS AR<br>2. WARPAGE SHALL NO<br>5. COPLANARITY APPLIE<br>4. COPLANARITY SHALL<br>2. MARVING CULONNI IS | T EXCEED<br>S TO THE<br>NOT EXC<br>FOR PAC | ) 0.10<br>E EXPOS<br>CEED 0.0<br>CKAGE C | mm.<br>SED PAD<br>D8 mm.<br>iRIENTATII | ON REF |         | ONLY.     | /INALS. |  |

### **Electrical Characteristics**

$(V_{DD} = 1.8V, V_{RS+} = V_{RS-} = +12V, V_{SENSE} = (V_{RS+} - V_{RS-}) = 0V, V_S = +12V, T_A = +25^{\circ}C$ , minimum and maximum limits are from T<sub>A</sub> = -40^{\circ}C to +125^{\circ}C, unless otherwise noted. (Note 1))

| PARAMETER                                             | SYMBOL            | CONDITIONS                                                                                                                                          | MIN  | TYP                   | MAX  | UNITS  |

|-------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------|------|--------|

| CURRENT MEASUREME                                     | NT                |                                                                                                                                                     |      |                       |      |        |

| Input Common Mode<br>Range                            | V <sub>CM</sub>   |                                                                                                                                                     | -0.1 |                       | 36   | V      |

|                                                       | N                 | (RS+ - RS-), Option #1 programmable with I <sup>2</sup> C                                                                                           |      | ±50                   |      |        |

| Input Voltage Sense                                   | VSENSE            | (RS+ - RS-), Option #2 programmable with $I^2C$                                                                                                     |      | ±10                   |      | - mV   |

|                                                       | 6                 | V <sub>SENSE</sub> = ±10mV, Option #1<br>programmable with I <sup>2</sup> C                                                                         |      | 125                   |      | - V/V  |

| CSA Gain                                              | G                 | V <sub>SENSE</sub> = ±10mV, Option #1<br>programmable with I <sup>2</sup> C                                                                         |      | 25                    |      |        |

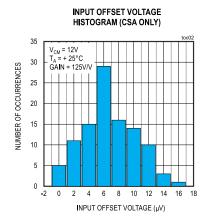

| Input Offset Voltage                                  | Vee               | T <sub>A</sub> = +25°C                                                                                                                              |      | 5                     | 20   |        |

| (CSA only)                                            | V <sub>OS</sub>   | $-40^{\circ}C \le T_A \le +125^{\circ}C$                                                                                                            |      | 5                     | 45   | - μV   |

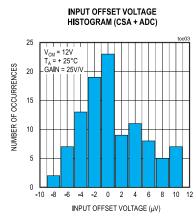

| Input Offset Voltage                                  | Vaa               | T <sub>A</sub> = +25°C                                                                                                                              |      | 5                     | 25   | μV     |

| (CSA + ADC)                                           | V <sub>OS</sub>   | $-40^{\circ}C \le T_A \le +125^{\circ}C$                                                                                                            |      | 5                     | 55   | μV     |

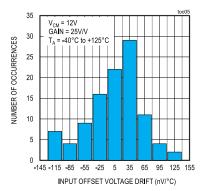

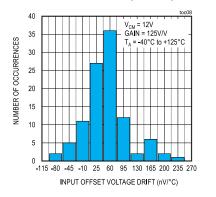

| Input Offset Drift                                    | TCV <sub>OS</sub> |                                                                                                                                                     |      | 50                    |      | nV/°C  |

| Input Bias Current                                    | Ι <sub>Β</sub>    | $-40^{\circ}C \le T_A \le +125^{\circ}C$                                                                                                            |      | 1                     | 20   | nA     |

| Gain Error (CSA only)                                 | GE                | T <sub>A</sub> = +25°C                                                                                                                              |      | 0.2                   | 0.55 | - %    |

|                                                       |                   | $-40^{\circ}C \le T_A \le +125^{\circ}C$                                                                                                            |      | 0.2                   | 0.75 | 70     |

| Gain Error (CSA + ADC)                                | GE                | T <sub>A</sub> = +25°C                                                                                                                              |      | 0.05                  | 0.5  | - %    |

|                                                       | GL                | $-40^{\circ}C \le T_A \le +125^{\circ}C$                                                                                                            |      | 0.05                  | 1.05 | 70     |

| Common Mode<br>Rejection Ratio (CSA<br>only)          | CMRR              |                                                                                                                                                     | 123  | 140                   |      | dB     |

| Common Mode<br>Rejection Ratio (CSA +<br>ADC)         | CMRR              |                                                                                                                                                     | 119  | 140                   |      | dB     |

| Power Supply Rejection<br>Ratio (CSA only)            | PSRR              |                                                                                                                                                     | 76   | 110                   |      | dB     |

| Power Supply Rejection<br>Ratio (CSA + ADC)           | PSRR              |                                                                                                                                                     | 76   | 110                   |      | dB     |

| Input Voltage-Noise<br>Density                        | V <sub>N</sub>    | $V_{\text{SENSE}} = (V_{\text{RS}^+} - V_{\text{RS}^-}) = 50 \text{mV}$ f = 1kHz                                                                    |      | 47                    |      | nV/√Hz |

| Cmall Cignal Dandwidth                                | BW                | $V_{SENSE} = (V_{RS+} - V_{RS-}) = \pm 50 \text{mV}$                                                                                                |      | 50                    |      | - kHz  |

| Small Signal Bandwidth                                | DVV               | $V_{SENSE} = (V_{RS+} - V_{RS-}) = \pm 10 \text{mV}$                                                                                                |      | 10                    |      | KI     |

| Wake-up and Over-<br>Current Thresholds<br>Resolution |                   | V <sub>SENSE</sub> = ±50mV                                                                                                                          |      | 0.78                  |      | mV     |

| Wake-up Response<br>Time                              |                   | Sampling Rate = 15ksps                                                                                                                              |      | 32.7                  |      | ms     |

| Over-Current Response<br>Time                         |                   | Unfiltered (D4 = 0)<br>Filtered (D4 = 1), Sample Rate = 15ksps<br>Filtered (D4 = 1), Sample Rate = 60ksps<br>Filtered (D4 = 1), Sample Rate = 1Msps |      | 31<br>294<br>88<br>35 |      | μs     |

# Precision, Fast Sample-Rate, Digital Current-Sense Amplifier

### **Electrical Characteristics (continued)**

$(V_{DD} = 1.8V, V_{RS+} = V_{RS-} = +12V, V_{SENSE} = (V_{RS+} - V_{RS-}) = 0V, V_S = +12V, T_A = +25^{\circ}C$ , minimum and maximum limits are from  $T_A = -40^{\circ}C$  to +125°C, unless otherwise noted. (Note 1))

| PARAMETER                                             | SYMBOL              | CONDITIONS                                                                                                                                          | MIN  | TYP                   | MAX   | UNITS |

|-------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------|-------|-------|

| INPUT VOLTAGE MEASU                                   | JREMENT             |                                                                                                                                                     |      |                       |       |       |

| Input Voltage Range                                   | VS                  |                                                                                                                                                     | 0    |                       | 36    | V     |

| Voltage Buffer Gain                                   | G                   |                                                                                                                                                     |      | 1/30                  |       | V/V   |

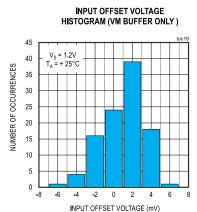

| Input Offset Voltage<br>(Voltage Buffer only)         | V <sub>OS</sub>     | Referred to $V_S$ , $V_S$ = 1.2V                                                                                                                    |      | 1.5                   | 21    | mV    |

| Input Offset Voltage<br>(Voltage Buffer + ADC)        | V <sub>OS</sub>     | Referred to $V_{S}$ , $V_{S}$ = 1.2V                                                                                                                |      | 1.5                   | 35    | mV    |

| Gain Error (Voltage<br>Buffer only)                   | GE                  |                                                                                                                                                     |      | 0.05                  | 0.4   | %     |

| Gain Error (Voltage<br>Buffer + ADC)                  | GE                  |                                                                                                                                                     |      | 0.2                   | 1.2   | %     |

| Input Voltage Signal<br>Bandwidth                     | BW                  |                                                                                                                                                     |      | 1                     |       | kHz   |

| Over/Under-Voltage<br>Thresholds Resolution           |                     | Referred to V <sub>S</sub>                                                                                                                          |      | 0.586                 |       | V     |

| Input Impedance                                       | Z <sub>IN</sub>     |                                                                                                                                                     |      | 6.5                   |       | MΩ    |

| Over/Under-Voltage<br>Response Time                   |                     | Unfiltered (D4 = 0)<br>Filtered (D4 = 1), Sample Rate = 15ksps<br>Filtered (D4 = 1), Sample Rate = 60ksps<br>Filtered (D4 = 1), Sample Rate = 1Msps |      | 31<br>294<br>88<br>35 |       | μs    |

| ADC CHARACTERISTIC                                    | S                   |                                                                                                                                                     |      |                       |       |       |

| Sample Frequency                                      | f <sub>S</sub>      | Programmable through I <sup>2</sup> C                                                                                                               | 15   |                       | 1,000 | Ksps  |

| Resolution                                            |                     | (Note 2)                                                                                                                                            |      | 12                    |       | bits  |

| Internal Reference<br>Voltage                         | V <sub>REF</sub>    |                                                                                                                                                     |      | 1.25                  |       | V     |

| Switching Time                                        | t <sub>S</sub>      | From current to voltage measurement or vice-versa                                                                                                   |      | 1                     |       | ms    |

| I <sup>2</sup> C TIMING (UP TO 1MHz                   | z) (Note 3)         |                                                                                                                                                     |      |                       |       |       |

| Serial Clock Frequency                                | fSCL                |                                                                                                                                                     |      |                       | 1     | MHz   |

| Bus Free Time Between<br>Start and Stop<br>Conditions | <sup>t</sup> BUF    |                                                                                                                                                     | 0.5  |                       |       | μs    |

| START Condition Hold<br>Time                          | <sup>t</sup> HD:STA |                                                                                                                                                     | 0.26 |                       |       | μs    |

| STOP Condition Setup<br>Time                          | <sup>t</sup> su:sto | 90% of SCL to 10% of SDA                                                                                                                            | 0.26 |                       |       | μs    |

| Clock Low Period                                      | t <sub>LOW</sub>    |                                                                                                                                                     | 0.5  |                       |       | μs    |

| Clock High Period                                     | thigh               |                                                                                                                                                     | 0.26 |                       |       | μs    |

| START Condition Setup<br>Time                         | <sup>t</sup> SU:STA | 90% of SCL to 90% of SDA                                                                                                                            | 0.26 |                       |       | μs    |

| Data Setup Time                                       | t <sub>SU:DAT</sub> | 10% of SDA to 10% of SCL                                                                                                                            | 50   |                       |       | ns    |

| Data In Hold Time                                     | thd:dat             | 10% of SCL to 10% of SDA                                                                                                                            | 0    |                       |       | μs    |

# Precision, Fast Sample-Rate, Digital Current-Sense Amplifier

### **Electrical Characteristics (continued)**

$(V_{DD} = 1.8V, V_{RS+} = V_{RS-} = +12V, V_{SENSE} = (V_{RS+} - V_{RS-}) = 0V, V_S = +12V, T_A = +25^{\circ}C$ , minimum and maximum limits are from  $T_A = -40^{\circ}C$  to +125°C, unless otherwise noted. (Note 1))

| PARAMETER                                                                          | SYMBOL              | CONDITIONS               | MIN TYP                   | MAX                      | UNITS |

|------------------------------------------------------------------------------------|---------------------|--------------------------|---------------------------|--------------------------|-------|

| Minimum Receive SCL/<br>SDA Rise Time                                              | t <sub>R</sub>      | (Note 3)                 | 20 +<br>0.1C <sub>B</sub> |                          | ns    |

| Maximum Receive SCL/<br>SDA Rise Time                                              | t <sub>R</sub>      | (Note 3)                 | 120                       |                          | ns    |

| Minimum Receive SCL/<br>SDA Fall Time                                              | t <sub>F</sub>      | (Note 3)                 | 20 +<br>0.1C <sub>B</sub> |                          | ns    |

| Maximum Receive SCL/<br>SDA Fall Time                                              | t <sub>F</sub>      | (Note 3)                 | 120                       |                          | ns    |

| Transmit SDA Fall Time                                                             | t <sub>F</sub>      | Bus capacitance = 550pF. |                           | 120                      | ns    |

| Maximum Pulse Width<br>of Spikes That Must Be<br>Suppressed by the Input<br>Filter |                     |                          | 50                        |                          | ns    |

| Capacitive Load for<br>Each Bus Line                                               | CB                  |                          | 550                       |                          | pF    |

| I <sup>2</sup> C TIMING (HS MODE U                                                 | P TO 3.4MHz) (      | Note 3)                  |                           |                          |       |

| Serial Clock Frequency                                                             | f <sub>SCL</sub>    |                          |                           | 3.4                      | MHz   |

| START Condition Hold<br>Time                                                       | <sup>t</sup> HD:STA |                          | 160                       |                          | ns    |

| START Condition Setup<br>Time                                                      | <sup>t</sup> SU:STA | 90% of SCL to 90% of SDA | 160                       |                          | ns    |

| Clock Low Period                                                                   | t <sub>LOW</sub>    |                          | 160                       |                          | ns    |

| Clock High Period                                                                  | tHIGH               |                          | 60                        |                          | ns    |

| Data Setup Time                                                                    | t <sub>SU:DAT</sub> | 10% of SDA to 10% of SCL | 10                        |                          | ns    |

| Data In Hold Time                                                                  | t <sub>HD:DAT</sub> | 10% of SCL to 10% of SDA | 35                        |                          | ns    |

| Minimum Receive SCL/<br>SDA Rise Time                                              | t <sub>R</sub>      | (Note 3)                 | 20 +<br>0.1C <sub>B</sub> |                          | ns    |

| Maximum Receive SCL/<br>SDA Rise Time                                              | t <sub>R</sub>      | (Note 3)                 | 120                       |                          | ns    |

| Minimum Receive SCL/<br>SDA Fall Time                                              | t <sub>F</sub>      | (Note 3)                 | 20 +<br>0.1C <sub>B</sub> |                          | ns    |

| Maximum Receive SCL/<br>SDA Fall Time                                              | t <sub>F</sub>      | (Note 3)                 | 120                       |                          | ns    |

| STOP Condition Setup<br>Time                                                       | tsu:sto             | 90% of SCL to 10% of SDA | 160                       |                          | ns    |

| Capacitive Load for<br>Each Bus Line                                               | CB                  |                          | 100                       |                          | pF    |

| Maximum Pulse Width<br>of Spikes That Must Be<br>Suppressed by the Input<br>Filter |                     |                          | 10                        |                          | ns    |

| LOGIC (SDA, SCL, A0, A                                                             | LERT_) DC CH        | ARACTERISTICS            |                           |                          |       |

| Input High Voltage                                                                 | V <sub>IH</sub>     |                          | 0.7 x<br>V <sub>DD</sub>  | V <sub>DD</sub> +<br>0.3 | V     |

# Precision, Fast Sample-Rate, Digital Current-Sense Amplifier

### **Electrical Characteristics (continued)**

$(V_{DD} = 1.8V, V_{RS+} = V_{RS-} = +12V, V_{SENSE} = (V_{RS+} - V_{RS-}) = 0V, V_S = +12V, T_A = +25^{\circ}C$ , minimum and maximum limits are from  $T_A = -40^{\circ}C$  to +125°C, unless otherwise noted. (Note 1))

| PARAMETER                                         | SYMBOL            | CONE                                                                                                      | DITIONS                                     | MIN  | TYP    | MAX                      | UNITS |

|---------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------|------|--------|--------------------------|-------|

| Input Low Voltage                                 | V <sub>IL</sub>   |                                                                                                           |                                             | -0.3 |        | 0.3 x<br>V <sub>DD</sub> | V     |

| Input High Leakage<br>Current                     | Чн                | Logic Input to DV <sub>DD</sub>                                                                           |                                             | -1   | ±0.005 | +1                       | μA    |

| Input Low Leakage<br>Current                      | IIL               | Logic Input to 0V                                                                                         |                                             | -1   | ±0.005 | +1                       | μA    |

| Input Capacitance                                 | C <sub>IN</sub>   |                                                                                                           |                                             |      | 5      |                          | pF    |

| Output Low Voltage                                | V <sub>OL</sub>   | I <sub>OL</sub> = 3mA                                                                                     |                                             | 0    |        | 0.3                      | V     |

| Output High Leakage<br>Current                    |                   | V <sub>OUT</sub> = V <sub>DD</sub>                                                                        |                                             |      | ±0.005 | 1                        | μA    |

| POWER SUPPLY                                      |                   |                                                                                                           |                                             |      |        |                          |       |

| Supply Voltage Range                              | V <sub>DD</sub>   | Guaranteed by PSR                                                                                         | R                                           | 1.71 |        | 1.98                     | V     |

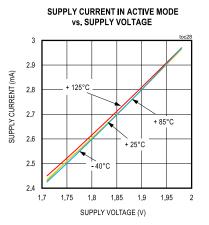

| Active Power Supply<br>Current                    | IACTIVE           | Active mode, I <sup>2</sup> C inactive                                                                    | -40°C ≤ T <sub>A</sub> ≤<br>+125°C          |      | 2700   | 3500                     | μA    |

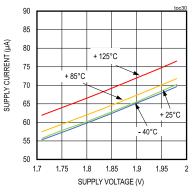

| Low-Power Mode<br>Supply Current                  | Ι <sub>LP</sub>   | I <sup>2</sup> C inactive, ADC<br>is shutdown,<br>current-sense<br>takes one<br>measurement<br>every 50ms | -40°C ≤ T <sub>A</sub> ≤<br>+125°C          |      | 52     | 85                       | μΑ    |

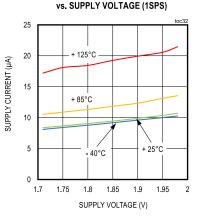

|                                                   |                   | I <sup>2</sup> C inactive, 4 conversions/s                                                                | -40°C ≤ T <sub>A</sub> ≤<br>+125°C          |      | 41     | 65                       |       |

| Average Supply Current                            |                   | I <sup>2</sup> C inactive, 1 conversions/s                                                                | -40°C ≤ T <sub>A</sub> ≤<br>+125°C (Note 3) |      | 18     | 38                       |       |

| Average Supply Current<br>in Selected Active Mode | IAVE              | I <sup>2</sup> C inactive, 0.25 conversions/s                                                             | -40°C ≤ T <sub>A</sub> ≤<br>+125°C (Note 3) |      | 14     | 27                       | μA    |

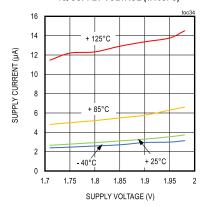

|                                                   |                   | I <sup>2</sup> C inactive,<br>0.0625<br>conversions/s                                                     | -40°C ≤ T <sub>A</sub> ≤<br>+125°C (Note 3) |      | 13     | 23                       |       |

| Standby Supply Current                            | I <sub>SDBY</sub> | In Standby and<br>between<br>conversions, I <sup>2</sup> C<br>bus inactive                                | -40°C ≤ T <sub>A</sub> ≤<br>+125°C          |      | 2.7    | 15                       | μΑ    |

| Ture Or Time                                      |                   | In Low-Power Mode<br>sense wakes up eve<br>current is below pro-<br>"Wakeup Current" re                   | grammed value in                            |      | 300    |                          |       |

| Turn-On Time                                      | t <sub>EN</sub>   | From Low-Power Mo<br>From Standby to eith<br>Selected Active Moo<br>Measurement Mode                      | her Active Mode or<br>le or Single          |      | 500    |                          | - µs  |

| Power-On Time                                     | t <sub>ON</sub>   | V <sub>DD</sub> = 0V to1.8V                                                                               |                                             |      | 100    |                          | ms    |

Note 1: All devices are 100% production tested at T<sub>A</sub> = +25°C. Specifications over temperature limits are guaranteed by design and characterization.

**Note 2:** 12 bit data + 1bit sign bit for current measurement.

Note 3: Guaranteed by design.

# Precision, Fast Sample-Rate, Digital Current-Sense Amplifier

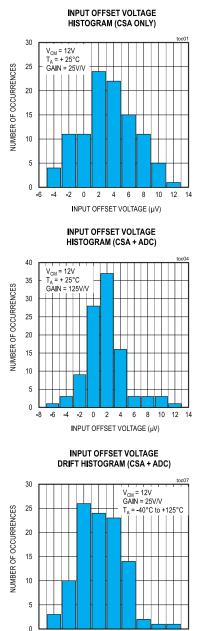

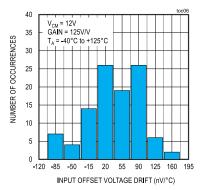

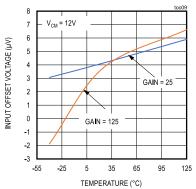

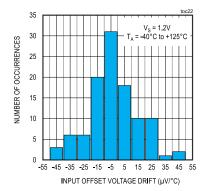

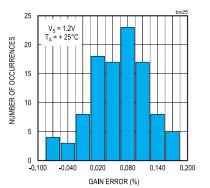

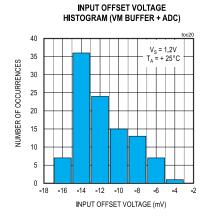

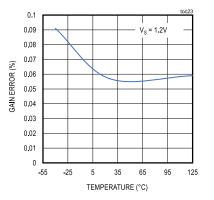

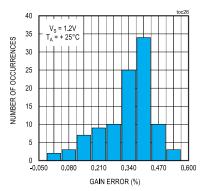

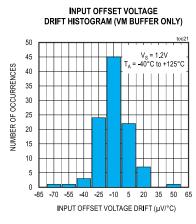

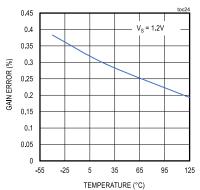

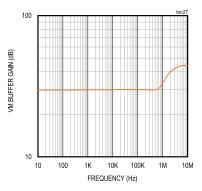

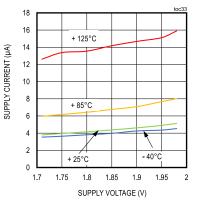

### **Typical Operating Characteristics**

$(V_{DD} = 1.8V, V_{RS+} = V_{RS-} = +12V, V_{SENSE} = (V_{RS+} - V_{RS-}) = 0V, V_S = +12V, T_A = +25^{\circ}C$ , minimum and maximum limits are from  $T_A = -40^{\circ}C$  to +125°C, unless otherwise noted.)

-115 -85 -55 -25 5 35 65 95 125 155 185

INPUT OFFSET VOLTAGE DRIFT (nV/°C)

INPUT OFFSET VOLTAGE DRIFT HISTOGRAM (CSA ONLY)

INPUT OFFSET VOLTAGE DRIFT HISTOGRAM (CSA + ADC)

INPUT OFFSET VOLTAGE DRIFT HISTOGRAM (CSA ONLY)

INPUT OFFSET VOLTAGE (CSA ONLY) vs. TEMPERATURE

# Precision, Fast Sample-Rate, Digital Current-Sense Amplifier

**Typical Operating Characteristics (continued)**

$(V_{DD} = 1.8V, V_{RS+} = V_{RS-} = +12V, V_{SENSE} = (V_{RS+} - V_{RS-}) = 0V, V_S = +12V, T_A = +25^{\circ}C$ , minimum and maximum limits are from T<sub>A</sub> = -40^{\circ}C to +125^{\circ}C, unless otherwise noted. )

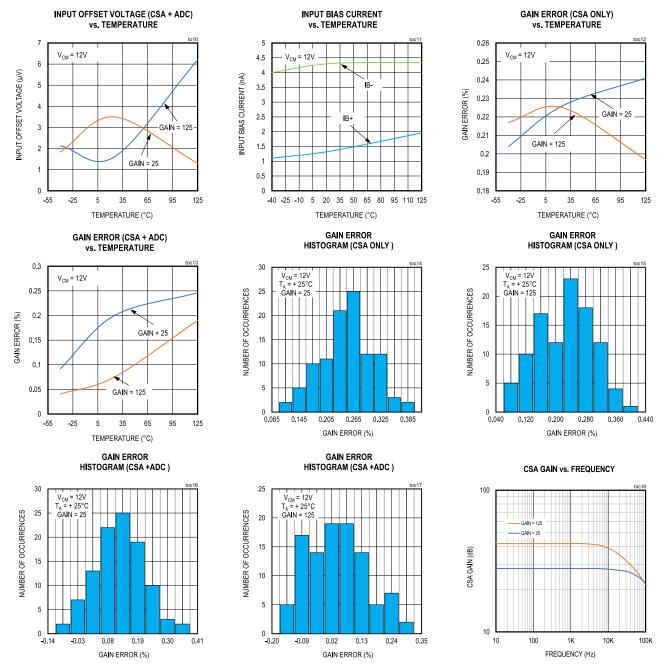

# Precision, Fast Sample-Rate, Digital Current-Sense Amplifier

**Typical Operating Characteristics (continued)**

$(V_{DD} = 1.8V, V_{RS+} = V_{RS-} = +12V, V_{SENSE} = (V_{RS+} - V_{RS-}) = 0V, V_S = +12V, T_A = +25^{\circ}C$ , minimum and maximum limits are from  $T_A = -40^{\circ}C$  to +125°C, unless otherwise noted. )

INPUT OFFSET VOLTAGE DRIFT HISTOGRAM (VM BUFFER + ADC)

GAIN ERROR HISTOGRAM (VM BUFFER ONLY )

GAIN ERROR (VM BUFFER ONLY) vs. TEMPERATURE

GAIN ERROR HISTOGRAM (VM BUFFER + ADC )

GAIN ERROR (VM BUFFER + ADC) vs. TEMPERATURE

VM BUFFER GAIN vs. FREQUENCY (ABS)

# Precision, Fast Sample-Rate, Digital Current-Sense Amplifier

**Typical Operating Characteristics (continued)**

$(V_{DD} = 1.8V, V_{RS+} = V_{RS-} = +12V, V_{SENSE} = (V_{RS+} - V_{RS-}) = 0V, V_S = +12V, T_A = +25^{\circ}C$ , minimum and maximum limits are from T<sub>A</sub> = -40^{\circ}C to +125^{\circ}C, unless otherwise noted.)

SUPPLY CURRENT IN STANDBY MODE

vs. SUPPLY VOLTAGE (4SPS)

+ 85°C

25°C

SUPPLY VOLTAGE (V)

+ 125°C

- 40°Ċ

50

45

40

35

30

25

20

1.7 1.75 1.8 1.85 1.9 1.95 2

SUPPLY CURRENT (µA)

vs. SUPPLY VOLTAGE 12 10 + 125°C SUPPLY CURRENT (µA) 8 + 85°C 6 25°C - 40°C 4 2 0 1.7 1.75 1.8 1.85 1.9 1.95 2 SUPPLY VOLTAGE (V)

SUPPLY CURRENT IN SELECTIVE ACTIVE MODE SUPPLY CURRENT IN SELECTIVE ACTIVE MODE

SUPPLY CURRENT IN SELECTIVE ACTIVE MODE vs. SUPPLY VOLTAGE (1/16SPS)

SUPPLY CURRENT IN LOW POWER MODE vs. SUPPLY VOLTAGE

SUPPLY CURRENT IN SELECTIVE ACTIVE MODE vs. SUPPLY VOLTAGE (0.25SPS)

# Precision, Fast Sample-Rate, Digital Current-Sense Amplifier

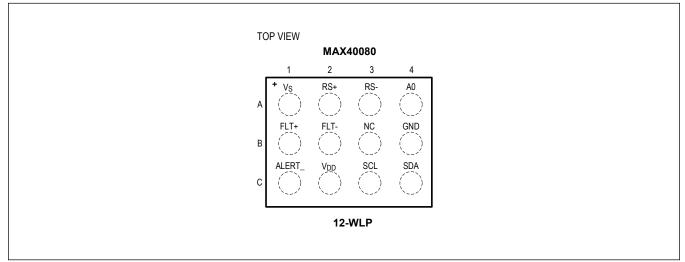

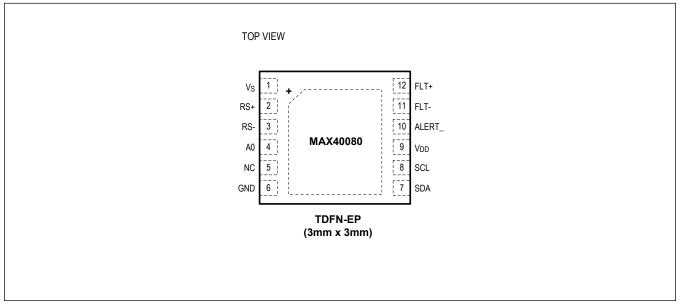

### **Pin Configurations**

### **WLP-12**

#### TDFN

# Precision, Fast Sample-Rate, Digital Current-Sense Amplifier

# **Pin Description**

| P      | IN   | NAME            | FUNCTION                                                                       |

|--------|------|-----------------|--------------------------------------------------------------------------------|

| WLP-12 | TDFN |                 | FUNCTION                                                                       |

| A1     | 1    | VS              | Input Voltage Sense                                                            |

| A2     | 2    | RS+             | Positive Current-Sensing Input                                                 |

| A3     | 3    | RS-             | Negative Current-Sensing Input                                                 |

| A4     | 4    | A0              | Address Input. Connect to the external resistor                                |

| B1     | 12   | FLT+            | Connect a capacitor between FLT+ and FLT- to limit the input signal bandwidth. |

| B2     | 11   | FLT-            | Connect a capacitor between FLT+ and FLT- to limit the input signal bandwidth  |

| B3     | 5    | NC              | Do Not Connect                                                                 |

| B4     | 6    | GND             | Ground                                                                         |

| C1     | 10   | ALERT_          | I <sup>2</sup> C Interrupt/Alert Output (active low)                           |

| C2     | 9    | V <sub>DD</sub> | Analog Positive Supply Voltage                                                 |

| C3     | 8    | SCL             | I <sup>2</sup> C Clock                                                         |

| C4     | 7    | SDA             | I <sup>2</sup> C Data                                                          |

### **Detailed Description**

The MAX40080 measures current and common-mode voltage and converts the data into digital form. It is an I<sup>2</sup>C-compatible two-wire serial interface that allows access to conversion results. Standard I<sup>2</sup>C commands allow reading the data and configuring other operating characteristics. While reading the current/voltage registers, any changes in measured current and voltage are ignored until the read is completed. The current/voltage register is updated for the new measurement upon completion of the read operation.

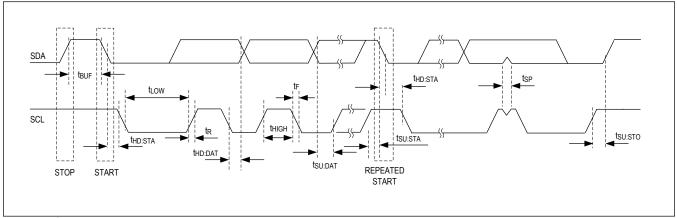

#### I<sup>2</sup>C-Compliant and SMBus-Compatible Bus Interface

A standard I<sup>2</sup>C-compliant 2-wire serial interface reads current/voltage data from the current and voltage registers. It also reads and writes control bits to/from the configuration registers. In addition, the interface supports useful SMBus functions, including selectable Packet Error Checking (PEC). SMBus timeout is not supported which makes this SMBus interface, compatible but not fully compliant.

Figure 1. I<sup>2</sup>C/SMBus Timing Diagram

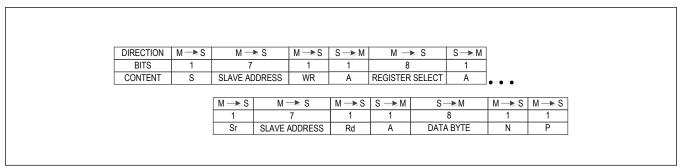

Normal transactions consist of 2-byte writes and reads. However, some registers are single-byte read and one register is 4-byte read. An additional byte will be appended when PEC is enabled. Attempting longer transactions is not recommended. A transaction always begins with a START (S) condition followed by the slave address and the Write/ Read bit.

A 2-byte write transaction (Write Word) begins with the master generating a START condition and then transmitting the MAX40080's slave address followed by the Write bit. The device acknowledges with an ACK (A) bit, and the master transmits the target register, followed by another ACK from the MAX40080. The master then writes the two data bytes, and the MAX40080 ACKs each. The master ends the transaction by generating a STOP (P) condition. Writing more bytes (not recommended) will simply overwrite the register (e.g., DATA LOW - DATA HIGH - DATA LOW - DATA HIGH for a 4-byte write).

| DIRECTION | M→S | M 🖚 S         | M→S | S 🔶 M | M → S           | S→ M | M→►S            | S 🅕 M | M→►S             | S → M | M 🔶 S |

|-----------|-----|---------------|-----|-------|-----------------|------|-----------------|-------|------------------|-------|-------|

| BITS      | 1   | 7             | 1   | 1     | 8               | 1    | 8               | 1     | 8                | 1     | 1     |

| CONTENT   | S   | SLAVE ADDRESS | WR  | A     | REGISTER SELECT | Α    | DATA BYTE [7:0] | A     | DATA BYTE [15:8] | A     | Р     |

Figure 2. 2-Byte Write (Write Word)

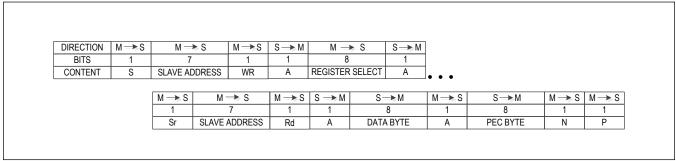

When Packet Error Checking (PEC) is enabled, the write transaction is similar, except that the PEC byte (calculated using SLAVE ADDRESS, REGISTER ADDRESS, DATA LOW, and DATA HIGH) is appended by the master after the

### Precision, Fast Sample-Rate, Digital Current-Sense Amplifier

ACK bit that follows the second data byte. Any attempted write that is not a multiple of three bytes will be ignored. If more than one set of three bytes is written, the PEC byte is calculated using the bytes listed above, plus the first PEC byte and the second DATA LOW and DATA HIGH bytes. Again, writing more than three bytes with PEC enabled is not recommended.

| DIRECTION | M→S | M \Rightarrow S | M→S | S → M | M → S           | S→ M | M→►S            | S → M | M→►S             | S → M | M→►S     | S 🔶 M | M 🔶 S |

|-----------|-----|-----------------|-----|-------|-----------------|------|-----------------|-------|------------------|-------|----------|-------|-------|

| BITS      | 1   | 7               | 1   | 1     | 8               | 1    | 8               | 1     | 8                | 1     | 8        | 1     | 1     |

| CONTENT   | S   | SLAVE ADDRESS   | WR  | A     | REGISTER SELECT | A    | DATA BYTE [7:0] | A     | DATA BYTE [15:8] | A     | PEC BYTE | A     | Р     |

Figure 3. 2-Byte Write with PEC Byte

A 2-byte read (Read Word) is slightly more complex than a write. After transmitting the register byte and receiving an ACK from the device, the master generates a REPEAT START (Sr) and writes the address and a Read bit. The device then ACKs the address/read a byte and transmits the two data bytes. The master ACKs the first and NACKs the second, signaling that the transaction is complete, and then generates the STOP condition.

| DIRECTION | M→S       | M →             |         | M→S       | S → M     | M →      |        | S→M       |                 |                  |         |        |

|-----------|-----------|-----------------|---------|-----------|-----------|----------|--------|-----------|-----------------|------------------|---------|--------|

|           | IVI — 🔊 S | IVI — 4         | 0       | IVI — 🔊 S | 3 - F IVI |          | 3      |           |                 |                  |         |        |

| BITS      | 1         | /               |         | 1         | 1         | 8        |        | 1         |                 |                  |         |        |

| CONTENT   | S         | SLAVE AD        | DRESS   | WR        | A         | REGISTER | SELECT | A         |                 |                  |         |        |

|           |           |                 |         |           |           |          |        |           |                 |                  |         |        |

|           |           | M \Rightarrow S | M       | → S       | M → S     | S ->> M  | S-     | ►M        | M \Rightarrow S | S→M              | M ->> S | M -> S |

|           |           | 1               |         | 7         | 1         | 1        |        | 8         | 1               | 8                | 1       | 1      |

|           |           | Sr              | SLAVE A | ADDRESS   | Rd        | A        | DATA B | YTE [7:0] | A               | DATA BYTE [15:8] | N       | Р      |

Figure 4. 2-Byte Read (Read Word)

When Packet Error Checking (PEC) is enabled, the read transaction is similar, except that the PEC byte is appended by the device after the ACK bit that follows the second data byte.

| DIRECTION | M→S | M —      | ► S   | M→S     | S → M | $M \rightarrow$ | s S    | S → M      |       |                  |                 |          |                 |                 |

|-----------|-----|----------|-------|---------|-------|-----------------|--------|------------|-------|------------------|-----------------|----------|-----------------|-----------------|

| BITS      | 1   | 7        |       | 1       | 1     | 8               |        | 1          |       |                  |                 |          |                 |                 |

| CONTENT   | S   | SLAVE AD | DRESS | WR      | A     | REGISTER        | SELECT | A          |       |                  |                 |          |                 |                 |

|           |     |          |       |         |       |                 |        |            |       |                  |                 |          |                 |                 |

|           |     | M ->> S  | M -   | → S     | M → S | S → M           | S-     | ►M         | M → S | S→M              | M \Rightarrow S | S→M      | M \Rightarrow S | M \Rightarrow S |

|           |     | 1        |       | 7       | 1     | 1               |        | 8          | 1     | 8                | 1               | 8        | 1               | 1               |

|           |     | Sr       | SLAVE | ADDRESS | Rd    | A               | DATA B | BYTE [7:0] | A     | DATA BYTE [15:8] | A               | PEC BYTE | N               | P               |

Figure 5. 2-Byte Read with PEC Byte

A one-byte read without and with PEC is similar to the Read Word above, but only one byte is read, as shown in Figure <u>6</u> and Figure <u>7</u>.

# Precision, Fast Sample-Rate, Digital Current-Sense Amplifier

Figure 6. One-Byte Read

Figure 7. One-Byte Read with PEC

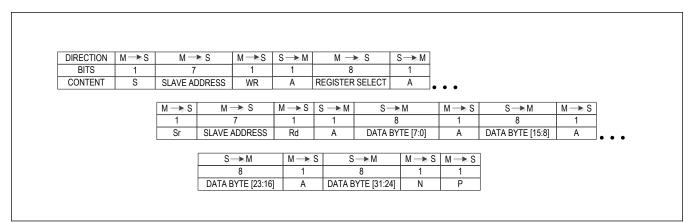

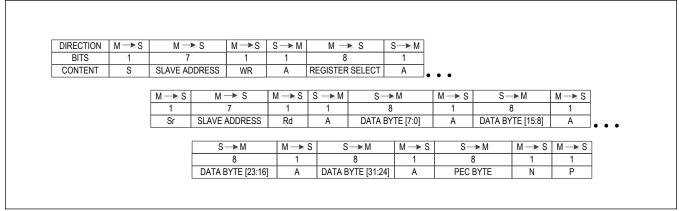

**Read 32 Protocol:** The Read 32 protocol is used with commands that require reading up to 32 bits (4 bytes) of data from a slave device. For MAX40080 this only applies to register Current\_Voltage\_Measurement.

This protocol can be used to read less than 32 bits, but the packet must be padded to fill 32 bits. Data or meaningful bits are packed into the lower order bits and unused higher-order bits are filled with zeros. For example, a 20-bit value is transmitted in bits [19:0] with the most significant bit in bit [19]. Bits [31:20] are all zeros.

Figure 8. Read 32

Figure 9. Read 32 with PEC

### I<sup>2</sup>C Slave Address

The MAX40080 has a unique  $I^2C$  slave address selection method based on a single resistor connected to the A0 input pin. Such a resistor-based method has many benefits, including lower cost and smaller size, as well as allowing the users to stock just one part in their inventory system and use it in multiple projects with different  $I^2C$  addresses just by changing a single standard 1% resistor. Select the resistor value by choosing the desired  $I^2C$  address. See <u>Table 1</u>.

32 different resistor values that correspond to 32 addresses, which are encoded by the 5 least significant bits. The two most significant bits of the address word ( $A_6$ ,  $A_5$ ) are fixed, two options A6 = 0, A5 = 1 or A6 = 1, A5 = 0 are available to be chosen at factory final test via OTP. Default value is  $A_6 = 0$ ,  $A_5 = 1$ . Note that the part will monitor the resistor value at A0 pin continuously, if the resistor value changes after the part are powered up, the I<sup>2</sup>C slave address will be changed.

#### **RESISTOR VALUE [Ω], 1%** SLAVE ADDRESS 115,000 A<sub>6</sub>, A<sub>5</sub>, 0\_0000 100,000 A<sub>6</sub>, A<sub>5</sub>, 0\_0001 86,600 A<sub>6</sub>, A<sub>5</sub>, 0\_0010 75.000 A<sub>6</sub>, A<sub>5</sub>, 0\_0011 64.900 A<sub>6</sub>, A<sub>5</sub>, 0\_0100 56,200 A<sub>6</sub>, A<sub>5</sub>, 0\_0101 48,700 A<sub>6</sub>, A<sub>5</sub>, 0\_0110 42,200 A<sub>6</sub>, A<sub>5</sub>, 0\_0111 36,500 A<sub>6</sub>, A<sub>5</sub>, 0\_1000 30,900 A<sub>6</sub>, A<sub>5</sub>, 0\_1001 26,100 A<sub>6</sub>, A<sub>5</sub>, 0\_1010 21,500 A<sub>6</sub>, A<sub>5</sub>, 0\_1011 16,900 A<sub>6</sub>, A<sub>5</sub>, 0 1100 12,400 A<sub>6</sub>, A<sub>5</sub>, 0\_1101 8,060 A<sub>6</sub>, A<sub>5</sub>, 0\_1110 3,740 A<sub>6</sub>, A<sub>5</sub>, 0\_1111 2,870 A<sub>6</sub>, A<sub>5</sub>, 1\_0000 2,490 A<sub>6</sub>, A<sub>5</sub>, 1\_0001 2,150 A<sub>6</sub>, A<sub>5</sub>, 1\_0010 1,870 A<sub>6</sub>, A<sub>5</sub>, 1\_0011

### Table 1. I<sup>2</sup>C Slave Addresses

### Table 1. I<sup>2</sup>C Slave Addresses (continued)

| 1,620 | A <sub>6</sub> , A <sub>5</sub> , 1_0100 |

|-------|------------------------------------------|

| 1,400 | A <sub>6</sub> , A <sub>5</sub> , 1_0101 |

| 1,210 | A <sub>6</sub> , A <sub>5</sub> , 1_0110 |

| 1,050 | A <sub>6</sub> , A <sub>5</sub> , 1_0111 |

| 909   | A <sub>6</sub> , A <sub>5</sub> , 1_1000 |

| 768   | A <sub>6</sub> , A <sub>5</sub> , 1_1001 |

| 649   | A <sub>6</sub> , A <sub>5</sub> , 1_1010 |

| 536   | A <sub>6</sub> , A <sub>5</sub> , 1_1011 |

| 422   | A <sub>6</sub> , A <sub>5</sub> , 1_1100 |

| 309   | A <sub>6</sub> , A <sub>5</sub> , 1_1101 |

| 200   | A <sub>6</sub> , A <sub>5</sub> , 1_1110 |

| 95.3  | A <sub>6</sub> , A <sub>5</sub> , 1_1111 |

### I<sup>2</sup>C Communication Speed

The MAX40080 provides a revision 3.0 I<sup>2</sup>C-compatible (3.4MHz) serial interface. Revision 3.0 I<sup>2</sup>C-compatible serial communications channel:

- 0Hz to 100kHz (standard mode)

- 0Hz to 400kHz (fast mode)

- 0Hz to 1MHz (fast mode plus)

- 0Hz to 3.4MHz (high-speed mode or HS mode)

- Does not utilize I<sup>2</sup>C clock stretching

Operating in standard mode, fast mode and fast mode plus do not require any special protocols. The main consideration when changing the bus speed through this range is the combination of the bus capacitance and pullup resistors. Higher time constants created by the bus capacitance and pullup resistance (C x R) slow the bus operation. Therefore, when increasing bus speeds the pullup resistance must be decreased to maintain a reasonable time constant. Refer to the *Pullup Resistor Sizing section of the I*<sup>2</sup>*C revision 3.0 specification* for detailed guidance on the pullup resistor selection. In general, for bus capacitance of 200pF, a 100kHz bus needs  $5.6k\Omega$  pullup resistors, a 400kHz bus needs about  $1.5k\Omega$  pullup resistors, and a 1MHz bus needs  $680\Omega$  pullup resistors. Note that the pullup resistor dissipates power when the open drain bus is low. The lower the value of the pullup resistor, the higher the power dissipation is (V<sup>2</sup>/R).

Operating high-speed mode requires some considerations. For the full list of considerations, refer to the I<sup>2</sup>C 3.0 specification. The major considerations with respect to MAX40080 are:

- The I<sup>2</sup>C bus master uses current source pull-ups to shorten the signal rise time.

- The I<sup>2</sup>C slave must use a different set of input filters on its SDA and SCL lines to accommodate for the higher bus speed.

- The communication protocols need to utilize the high speed master code.

At power-up and after each STOP condition, the MAX40080 input filters are set to standard mode, fast mode, or fast mode plus (i.e., 0Hz to 1MHz), unless bit 7 in the Configuration Register is set high. In that case, once entering the HS-mode, the device will stay into such a mode until this bit remains set, thus ignoring the STOP condition.

Once the bit is reset, at the next STOP condition the MAX40080 will exit from HS mode.

#### Engaging HS-Mode for Operation up to 3.4MHz

<u>Figure 10</u> shows the protocol for engaging HS mode operation. HS-mode operation allows for a bus operating speed up to 3.4MHz. The engaging HS-mode protocol is as follows:

- 1. Begin the protocol, while operating at a bus speed of 1MHz or lower.

- 2. The master sends a START command (S).

- 3. The master sends the 8-bit master code of 00001xxxb where xxxb are don't care bits.

- 4. The addressed slave issues a NOT ACKNOWLEDGE (NA).

### Precision, Fast Sample-Rate, Digital Current-Sense Amplifier

- 5. The master may now increase its bus speed up to 3.4MHz and issue any read/write operation.

- The master may continue to issue high-speed read/write operations until a STOP (P) is issued. Issuing a STOP (P) ensures that the bus input filters are set for 1MHz or slower operation. After a STOP has been issued, steps 1 to 6 in the above algorithm may be skipped.

| DIRECTION | M→S | M→S         | S→M     | M→ S | M → S                         | M→S | M→ S                          | M→S | M→ S           | M→S   |            |

|-----------|-----|-------------|---------|------|-------------------------------|-----|-------------------------------|-----|----------------|-------|------------|

| BITS      | 1   | 8           | 1       | 1    |                               | 1   |                               | 1   |                | 1     |            |

| CONTENT   | S   | MASTER CODE | NACK    | Sr   | ANY READ/WRITE FOLLOWED BY SR | Sr  | ANY READ/WRITE FOLLOWED BY SR | Sr  | ANY READ/WRITE | Р     | •••        |

|           |     | FAS         | ST MODE |      | → <                           |     | HS MODE                       |     |                | ▶ ◀── | -FAST MODE |

Figure 10. Engaging HS Mode

Note that the I<sup>2</sup>C HS Mode is only available when the device operates in Active Mode. See the <u>Configuration Register</u> section for more details about Active Mode and the other modes of operation.

#### Modes of Operation

The device operates in one of the following five modes that can be programmed through the "Configuration" register:

- 1. **Standby Mode:** The device is not active, except for the I<sup>2</sup>C interface which can receive commands.

- 2. Low-Power Mode: The ADC is disabled, but the current sense is partially active, taking one current measurement every 50ms. The measured current is below the threshold set in the "Wake\_Up\_Current" register. Once the measured current reaches the threshold the device will enter into "Active Mode". No voltage measurement is taken as long as the device stays in low-power mode. For this reason, it is recommended that only current is stored into the FIFO (See the *FIFO configuration register* to determine what to store into the FIFO). But once the device wakes up from low-power mode to active mode, it will take either current or voltage measurement according to the Store V\_I setting in the FIFO configuration register.

- 3. Single-Measurement Mode: The device is basically in Standby mode, but when it responds to the SM BUS "Quick Command", it wakes up and takes one current and voltage measurement, then it enters into Standby again until the next "Quick Command".

- 4. Active Mode: The device is active in all its functionality and measurement is continuously taken.

- 5. **Selected Active Mode:** The device automatically takes several measurements per second (according to the sample rate setting) and stays on standby in between each measurement.

When operating in either "Active Mode" or "Selected Active Mode" if the I<sup>2</sup>C bus is inactive for as long as 1 minute the device will automatically go in the Standby Mode.

#### **Quick Command:**

In the Quick Command, the R/W# bit of the slave address denotes the command. The R/W# bit is used only when in Single-Measurement Mode to make the measurement. There are no data sent or received.

| DIRECTION | M-►S | M-►S          | M-►S | S-►M | M-►S |

|-----------|------|---------------|------|------|------|

| BITS      | 1    | 7             | 1    | 1    | 1    |

| CONTENT   | S    | SLAVE ADDRESS | R/W# | A    | Р    |

Figure 11. Quick Command

#### Alert Management

The MAX40080 features an open-drain ALERT\_ output that reports when any of the following situations occur:

- Overcurrent

- Overvoltage

- Under voltage

- FIFO overflow warning (programmable threshold)

- FIFO full (64 data on it)

- Conversion ready (single-measurement mode only)

- Wake-up current threshold reached

- One minute timeout on the I<sup>2</sup>C bus (when inactive) expired

Any of the conditions above are also reported in the Status Register.

The ALERT\_ output is latched and is de-asserted only after the relevant flag has been cleared in the Status Register. Such a flag is cleared by writing into the Status Register. See the *Status Register description* for more details.

The ALERT\_ interrupt output (also called SMBALERT#) is a wired-AND signal that is used in conjunction with the SMBus Alert Response Address (ARA).

A slave-only device can signal the host through SMBALERT# that it wants to talk. The host processes the interrupt and simultaneously accesses all SMBALERT# devices through the Alert Response Address. Only the device(s) which pulled SMBALERT# low will acknowledge the Alert Response Address. The host performs a modified Receive Byte operation. The 7-bit device address provided by the slave transmits device is placed in the 7 most significant bits of the byte. The eighth bit can be a zero or one.

If more than one device pulls SMBALERT# low, the highest priority (lowest address) device will win communication rights via standard arbitration during the slave address transfer.

After receiving an acknowledge (ACK) from the master in response to its address, that device must stop pulling down on the SMBALERT# signal. If the host still sees SMBALERT# low when the message transfer is complete, it knows to read the ARA again.

#### **Internal Registers**

The pointer register selects between the registers as shown in <u>Table 2</u>. The pointer register must be written for each  $I^2C$  transaction.

Register addresses are not auto-incremented during reads and write. The max peak current register resets upon reading.

Write to the configuration register by writing the slave address byte, the pointer register byte to value 00h, and the data bytes. All other registers require the slave address byte, pointer register byte (04h or 05h, etc.), and 2 data bytes. If only 1 data byte is written, it is saved in bits D[15:8] of the respective register. If more than 2 data bytes are written, the additional data writes to the same register.

Perform a read operation by issuing the slave address byte (write), pointer byte, repeat START, another slave address byte (read), and then reading the data byte. If more than 2 data bytes are read, the additional reads are from the same register. See Figure 4.

| REGISTER NAME           | R/W | ADDRESS(HEX) | NUMBER OF BITS | POR STATE(HEX) | I2C READ TYPE |

|-------------------------|-----|--------------|----------------|----------------|---------------|

| Configuration           | R/W | 00h          | 16             | 0060h          | Read Word     |

| Status                  | R   | 02h          | 14             | 0000h          | Read Word     |

| Threshold_Over_Current  | R/W | 04h          | 7              | 30h            | Read Byte     |

| Threshold_Over_Voltage  | R/W | 05h          | 6              | 30h            | Read Byte     |

| Threshold_Under_Voltage | R/W | 06h          | 6              | 00h            | Read Byte     |

| Wake_Up_Current         | R/W | 07h          | 7              | 08h            | Read Byte     |

| Max_Peak_Current        | R   | 08h          | 14             | 0000h          | Read Word     |

| FIFO_Configuration      | R/W | 0Ah          | 16             | 3400h          | Read Word     |

| Current_Measurement     | R   | 0Ch          | 16             | 0000h          | Read Word     |

| Voltage_Measurement     | R   | 0Eh          | 16             | 0000h          | Read Word     |

### **Table 2. Register Functions and POR States**

### Precision, Fast Sample-Rate, Digital Current-Sense Amplifier

### Table 2. Register Functions and POR States (continued)

| Current_Voltage Measurement | R   | 10h | 32 | 0000 0000h | Read 32   |

|-----------------------------|-----|-----|----|------------|-----------|

| INT_EN                      | R/W | 14h | 8  | FFh        | Read Byte |

#### **Configuration Register**

The configuration register contains 16 bits of data:

| D15      | D14 D13 D12    | D11 D10 D9 D8   | D7           | D6          | D5  | D4    | D3          | D2 | D1    | D0 |

|----------|----------------|-----------------|--------------|-------------|-----|-------|-------------|----|-------|----|

| Reserved | Digital Filter | ADC Sample Rate | Stay HS Mode | Input Range | PEC | Alert | I2C Timeout | I  | Modes | 8  |

#### **Operation Modes**

Set bits D2, D1 and D0 to select one of the following device operation modes:

#### Table 3. Operation Mode

| OPERATION MODE         | D2 | D1 | D0 | COMMENT                         |

|------------------------|----|----|----|---------------------------------|

| Standby Mode           | 0  | 0  | 0  | Default mode at device power up |

| Low-Power Mode         | 0  | 0  | 1  |                                 |

| Single-Conversion Mode | 0  | 1  | 0  |                                 |

| Active Mode            | 0  | 1  | 1  | Continuous measurement          |

|                        | 1  | 0  | 0  | Fixed sample rate at 4sps       |

|                        | 1  | 0  | 1  | Fixed sample rate at 1sps       |

|                        | 1  | 1  | 0  | Fixed sample rate at 0.25sps    |

| Selected Active Mode   | 1  | 1  | 1  | Fixed sample rate at 0.0625sps  |

If a mode of operation is changed when a conversion is taking place, the conversion completes and then change occurs. While in standby, the I<sup>2</sup>C interface remains active and all registers remain accessible to the master.

When operating in either "Active Mode" or "Selected Active Mode" if the I<sup>2</sup>C bus is inactive for as long as 1 minute the device will automatically go into Standby Mode.

#### I<sup>2</sup>C Timeout

Write 1 to D3 to disable I<sup>2</sup>C timeout.

Write 0 to D3 to enable  $I^2C$  timeout (default condition at reset and power-up). When operating in either "Active Mode" or "Selected Active Mode" if the  $I^2C$  bus is inactive for as long as 1 minute the device will automatically go into Standby Mode. When such a condition happens the ALERT\_ is pulled low and a bit is set in the Status Register.

#### **Alert Response Time**

Bit D4 selects the alert interrupt response time:

- D4 = 0: Unfiltered. The alert is issued as soon as it is detected.

- D4 = 1: The alert is issued after being detected in four consecutive ADC clock samples (delay time varies from  $4\mu$ s to 266.4 $\mu$ s depending on the ADC sample frequency).

#### PEC

Write 1 to enable Packet Error Checking (Default).

Write 0 to disable Packet Error Checking.

Set PEC bit to enable Packet Error Checking (PEC). When enabled, a PEC byte is appended to the end of each message transfer. This is a CRC-8 byte that is calculated on all the message bytes (including the address/read/write byte). The last device to transmit a data byte, also transmits the PEC byte, so the master transmits the PEC byte after a Write transaction and the device transmits the PEC byte after a Read transaction.

#### Input Range

Write 0 to D6 to select a range of 50mV (default). Write 1 to D6 to select a range of 10mV.

#### Stay HS Mode

Set D7 to 1 to make the device stay in HS mode. Set D7 to 0 to exit from the HS mode (default). When this bit is set to 1, if device I<sup>2</sup>C speed is set to HS mode (up to 3.4MHz) the device will stay in HS mode, thus ignoring the STOP condition. Once the bit is reset to 0, at the next STOP condition the device will exit from HS mode.

#### ADC Sample Rate