#### **General Description**

The MAX6323/MAX6324 microprocessor (µP) supervisory circuits monitor power supplies and µP activity in digital systems. A watchdog timer looks for activity outside an expected window of operation. Six lasertrimmed reset thresholds are available with ±2.5% accuracy from +2.32V to +4.63V. Valid RESET output is guaranteed down to  $V_{CC} = +1.2V$ .

The RESET output is either push-pull (MAX6323) or open-drain (MAX6324). RESET is asserted low when V<sub>CC</sub> falls below the reset threshold, or when the manual reset input (MR) is asserted low. RESET remains asserted for at least 100ms after VCC rises above the reset threshold and MR is deasserted.

The watchdog pulse output (WDPO) utilizes an opendrain configuration. It can be triggered either by a fast timeout fault (watchdog input pulses are too close to each other) or a slow timeout fault (no watchdog input pulse is observed within the timeout period). The watchdog timeout is measured from the last falling edge of watchdog input (WDI) with a minimum pulse width of 300ns. WDPO is asserted for 1ms when a fault is observed. Eight laser-trimmed timeout periods are available.

The MAX6323/MAX6324 are offered in a 6-pin SOT23 package and operate over the extended temperature range ( $-40^{\circ}$ C to  $+125^{\circ}$ C).

#### **Applications**

Automotive

Industrial

Medical

**Embedded Control Systems**

#### Features

- ♦ Min/Max (Windowed) Watchdog, 8 Factory-Trimmed Timing Options

- ♦ Pulsed Open-Drain, Active-Low Watchdog Output

- **♦** Power-On Reset

- ◆ Precision Monitoring of +2.5V, +3.0V, +3.3V, and +5.0V Power Supplies

- ♦ Open-Drain or Push-Pull RESET Outputs

- ♦ Low-Power Operation (23µA typ)

- **♦ Debounced Manual Reset Input**

- ♦ Guaranteed Reset Valid to Vcc = +1.2V

#### **Ordering Information**

| PART        | TEMP            | PIN-    | RESET     |  |

|-------------|-----------------|---------|-----------|--|

|             | RANGE           | PACKAGE | OUTPUT    |  |

| MAX6323_UTT | -40°C to +125°C | 6 SOT23 | Push-Pull |  |

#### Ordering Information continued at end of data sheet.

\*These devices are factory trimmed to one of eight watchdogtimeout windows and one of six reset voltage thresholds. Insert the letter corresponding to the desired watchdog-timeout window (A, B, C, D, E, F, G, or H) into the blank following the number 6323 or 6324 (see Watchdog Timeout table). Insert the two-digit code (46, 44, 31, 29, 26, or 23) after the letters UT for the desired nominal reset threshold (see Reset Threshold Range table at end of data sheet).

/V denotes an automotive qualified part.

availability of nonstandard versions.

Devices are available in both leaded and lead-free packaging. Specify lead-free by replacing "-T" with "+T" when ordering. **Note:** There are eight standard versions of each device available (see Standard Versions table). Sample stock is generally held on standard versions only. Standard versions have an order increment requirement of 2500 pieces. Nonstandard versions have an order increment requirement of 10,000 pieces. Contact factory for

### Pin Configuration

| TOP VIEW | MR 1 6 RESET  MAXIM  MAX6323  MAX6324  WDD 3 4 Vcc |

|----------|----------------------------------------------------|

|          | SOT23                                              |

Typical Operating Circuit appears at end of data sheet.

### Watchdog Timeout

| WATCHDOG TIMEOUT* |     |       |      |       |  |

|-------------------|-----|-------|------|-------|--|

| SUFFIX            | FA  | ST    | SLOW |       |  |

| JUFFIX            | MAX | UNITS | MIN  | UNITS |  |

| А                 | 1.5 | ms    | 10   |       |  |

| В                 | 15  | ms    | 100  | ms    |  |

| С                 | 15  | ms    | 300  |       |  |

| D                 | 15  | ms    | 10   | S     |  |

| Е                 | 15  | ms    | 60   | 5     |  |

| F                 | 23  | ms    | 47   | ms    |  |

| G                 | 39  | ms    | 82   |       |  |

| Н                 | 719 | ms    | 1.3  | S     |  |

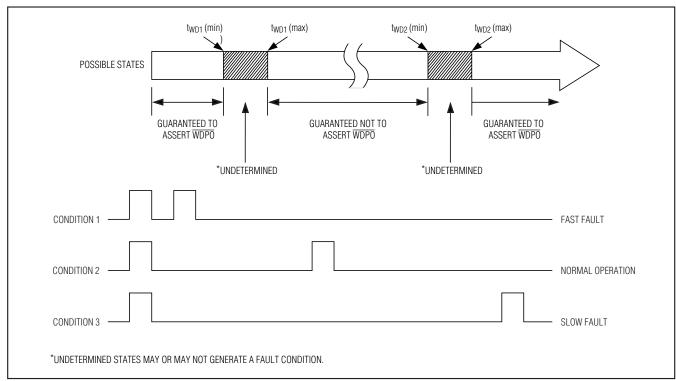

<sup>\*</sup>See Figure 1 for operation.

MIXIM

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| Terminal Voltage (with respect to GND)                |               |

|-------------------------------------------------------|---------------|

| V <sub>CC</sub>                                       |               |

| MR, RESET (MAX6323), WDI0.3V to                       |               |

| WDPO, RESET (MAX6324)                                 | 0.3V to +6.0V |

| Input Current, VCC, WDI, MR                           | 20mA          |

| Output Current, RESET, WDPO                           | 20mA          |

| Rate of Rise, Vcc                                     | 100V/µs       |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |               |

| 6-Pin SOT23 (derate 8 7mW/°C above +70°C)             | 696mW         |

| Operating Temperature Range       | 40°C to +125°C |

|-----------------------------------|----------------|

| Junction Temperature              | +150°C         |

| Storage Temperature Range         | 65°C to +150°C |

| Lead Temperature (soldering, 10s) | +300°C         |

| Soldering Temperature (reflow)    |                |

| Lead(Pb)-Free                     | +260°C         |

| Containing Lead                   |                |

| =                                 |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = \text{full range}, T_A = -40^{\circ}\text{C to} + 125^{\circ}\text{C}, \text{ unless otherwise noted}. \text{ Typical values are at } V_{CC} = 3V, T_A = +25^{\circ}\text{C.}) \text{ (Note 1)}$

| PARAMETER                      | SYMBOL                          | CONDITIONS                                                                       |                                                         | MIN                   | TYP  | MAX  | UNITS |  |

|--------------------------------|---------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------|------|------|-------|--|

| Operating Voltage Range        | Vcc                             |                                                                                  |                                                         | 1.2                   |      | 5.5  | V     |  |

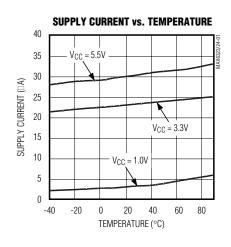

| Supply Current                 | lcc                             | No load, RESET                                                                   | $V_{CC} = 2.5V \text{ or } 3.3V$                        |                       | 23   | 45   | μΑ    |  |

| Supply Current                 | 100                             | deasserted                                                                       | V <sub>CC</sub> = 5.5V                                  |                       | 27   | 57   | μΑ    |  |

|                                |                                 | MAX632UT46                                                                       |                                                         | 4.50                  | 4.63 | 4.75 |       |  |

|                                |                                 | MAX632UT44                                                                       |                                                         | 4.25                  | 4.38 | 4.50 |       |  |

| Reset Threshold Voltage        | VTH                             | MAX632UT31                                                                       |                                                         | 3.00                  | 3.08 | 3.15 | V     |  |

| Treset Tilleshold Voltage      | VIH                             | MAX632UT29                                                                       |                                                         | 2.85                  | 2.93 | 3.00 | ď     |  |

|                                |                                 | MAX632UT26                                                                       |                                                         | 2.55                  | 2.63 | 2.70 |       |  |

|                                |                                 | MAX632UT23                                                                       |                                                         | 2.25                  | 2.32 | 2.38 |       |  |

| Reset Timeout Delay            | t <sub>RP</sub>                 | RESET deasserted                                                                 |                                                         | 100                   | 180  | 280  | ms    |  |

| V <sub>CC</sub> to RESET Delay |                                 | 10mV/ms, V <sub>TH</sub> +100mV to V <sub>TH</sub> - 100mV                       |                                                         |                       | 20   |      | μs    |  |

|                                | V <sub>OL</sub>                 | I <sub>SINK</sub> = 1.2mA, V <sub>CC</sub> = 2<br>MAX632UT26, MAX<br>MAX632UT31) | 2.25V (MAX632UT23,<br>632UT29,                          |                       |      | 0.4  |       |  |

| WDPO, RESET Output Voltage     |                                 | $I_{SINK} = 3.2$ mA, $V_{CC} = 4.25$ V (MAX632UT44, MAX632UT46)                  |                                                         |                       |      | 0.4  | V     |  |

|                                |                                 | I <sub>SINK</sub> = 100μA, V <sub>CC</sub> > 1.2V, RESET asserted                |                                                         |                       |      | 0.4  |       |  |

| RESET Output Voltage           | deas T Output Voltage  Vol. MAX |                                                                                  | = 3.15V, <u>RESET</u><br>_UT23, MAX632UT26,<br>632UT31) | 0.8 x V <sub>CC</sub> |      |      | V     |  |

| (MAX6323)                      |                                 | ISOURCE = 800µA, V <sub>CC</sub> deasserted, (MAX632_                            | = 4.75V, RESET<br>_UT44, MAX632UT46)                    | V <sub>CC</sub> - 1.5 |      |      |       |  |

| WDPO, RESET Output Leakage     | I <sub>LKG</sub>                | V <sub>RESET</sub> = V <sub>WDPO</sub> = +5.5V, RESET, WDPO deasserted           |                                                         |                       |      | 1    | μΑ    |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = \text{full range}, T_A = -40^{\circ}\text{C to} + 125^{\circ}\text{C}, \text{ unless otherwise noted}. \text{ Typical values are at } V_{CC} = 3\text{V}, T_A = +25^{\circ}\text{C}.) \text{ (Note 1)}$

| PARAMETER                             | SYMBOL           | CONDITIONS                                                        | MIN TYP                | MAX                   | UNITS    |

|---------------------------------------|------------------|-------------------------------------------------------------------|------------------------|-----------------------|----------|

| WATCHDOG INPUT AND OU                 | JTPUT            |                                                                   | ı                      |                       |          |

|                                       |                  | MAX632_AUT                                                        | 1                      | 1.5                   | - ms     |

|                                       |                  | MAX632_BUT                                                        | 10                     | 15                    |          |

|                                       |                  | MAX632_CUT                                                        | 10                     | 15                    |          |

| Watchdog Timeout (Fast)               |                  | MAX632_DUT                                                        | 10                     | 15                    |          |

| (Notes 2, 3)                          | t <sub>WD1</sub> | MAX632_EUT                                                        | 10                     | 15                    |          |

|                                       |                  | MAX632_FUT                                                        | 17                     | 23                    |          |

|                                       |                  | MAX632_GUT                                                        | 29                     | 39                    |          |

|                                       |                  | MAX632_HUT                                                        | 543                    | 719                   |          |

|                                       |                  | MAX632_AUT                                                        | 10                     | 15                    |          |

|                                       |                  | MAX632_BUT                                                        | 100                    | 150                   | ms       |

|                                       |                  | MAX632_CUT                                                        | 300                    | 450                   |          |

| Watchdog Timeout (Slow)               |                  | MAX632_DUT                                                        | 10                     | 15                    | - S      |

| (Note 4)                              | t <sub>WD2</sub> | MAX632_EUT                                                        | 60                     | 90                    |          |

|                                       |                  | MAX632_FUT                                                        | 47                     | 63                    | - ms     |

|                                       |                  | MAX632_GUT                                                        | 82                     | 108                   |          |

|                                       |                  | MAX632_HUT                                                        | 1.3                    | 1.8                   | S        |

| Minimum Watchdog Input<br>Pulse Width |                  |                                                                   | 300                    |                       | ns       |

| WDI Glitch Immunity                   |                  | V <sub>CC</sub> = 5.5V                                            | 100                    |                       | ns       |

| WDI I IV II                           | VIH              |                                                                   | 0.75 x V <sub>CC</sub> |                       |          |

| WDI Input Voltage                     | VIL              |                                                                   |                        | 0.8                   | V        |

| WDI In a st O support                 |                  | V <sub>WDI</sub> = 0V                                             | -1.5 -1                |                       | <u> </u> |

| WDI Input Current                     |                  | V <sub>WDI</sub> = V <sub>CC</sub>                                | 1                      | 1.5                   | μΑ       |

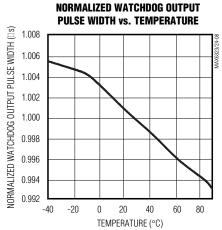

| WDPO Pulse Width                      |                  | V <sub>IL</sub> = 0.8V, V <sub>IH</sub> = 0.75V x V <sub>CC</sub> | 0.5 1                  | 3                     | ms       |

| MANUAL RESET INPUT                    | '                |                                                                   | '                      |                       |          |

| MR Input Voltage                      | V <sub>IH</sub>  |                                                                   | 0.7 x V <sub>CC</sub>  |                       | \/       |

|                                       | VIL              |                                                                   |                        | 0.3 x V <sub>CC</sub> | - V      |

| MR Minimum Pulse Width                |                  |                                                                   | 1                      |                       | μs       |

| MR Glitch Immunity                    |                  | V <sub>CC</sub> = 2.5V                                            | 100                    |                       | ns       |

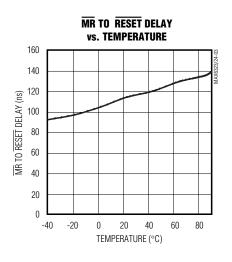

| MR to Reset Delay                     |                  | V <sub>CC</sub> = 2.5V                                            | 120                    |                       | ns       |

| MR Pullup Resistance                  |                  |                                                                   | 50 85                  |                       | kΩ       |

- **Note 1:** Devices are tested at  $T_A = +25$ °C and guaranteed by design for  $T_A = T_{MIN}$  to  $T_{MAX}$ , as specified.

- Note 2: WDPO will pulse low if a falling edge is detected on WDI before this timeout period expires.

- Note 3: To avoid a potential fake fault, the first WDI pulse after the rising edge of RESET or WDPO will not create a fast watchdog timeout fault.

- Note 4: WDPO will pulse low if no falling edge is detected on WDI after this timeout period expires.

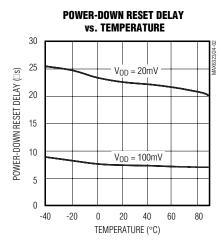

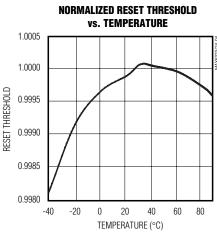

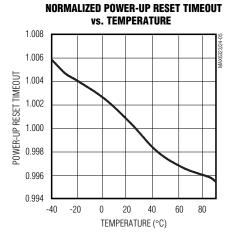

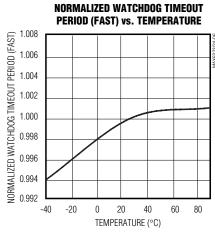

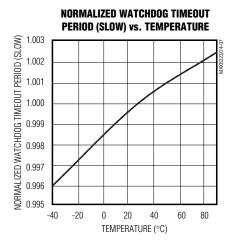

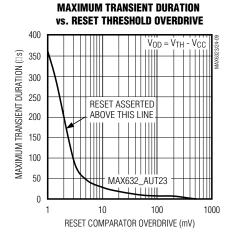

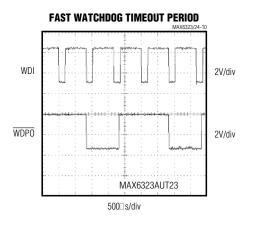

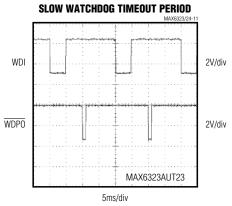

### **Typical Operating Characteristics**

(V<sub>CC</sub> = full range, T<sub>A</sub> = +25°C, unless otherwise noted.)

## Typical Operating Characteristics (continued)

$(V_{CC} = full range, T_A = +25^{\circ}C, unless otherwise noted.)$

## **Pin Description**

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | MR              | Active-Low, Manual Reset Input. When $\overline{\text{MR}}$ is asserted low, $\overline{\text{RESET}}$ is asserted low, the internal watchdog timer is reset to zero, and $\overline{\text{WDPO}}$ is reset to high impedance (open drain). After the rising edge of $\overline{\text{MR}}$ , $\overline{\text{RESET}}$ is asserted for at least 100ms. Leave $\overline{\text{MR}}$ unconnected or connect to $V_{CC}$ if unused. |

| 2   | GND             | Ground                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3   | WDI             | Watchdog Input. The internal watchdog timer clears to zero on the falling edge of WDI or when RESET goes high. If WDI sees another falling edge within the factory-trimmed watchdog window, WDPO will remain unasserted. Transitions outside this window, either faster or slower, will cause WDPO to pulse low for 1ms (typ).                                                                                                     |

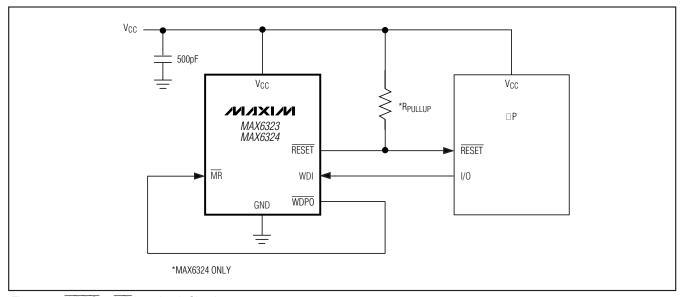

| 4   | V <sub>CC</sub> | Supply Voltage for the Device. Input for V <sub>CC</sub> reset monitor. For noisy systems, bypass V <sub>CC</sub> with a 500pF (min) capacitor.                                                                                                                                                                                                                                                                                    |

| 5   | WDPO            | Watchdog Pulse Output. The open-drain WDPO output is pulsed low for 1ms (typ) upon detection of a fast or slow watchdog fault. WDPO is only active when RESET is high.                                                                                                                                                                                                                                                             |

| 6   | RESET           | Active-Low. Reset is asserted when $V_{CC}$ drops below $V_{TH}$ and remains asserted until $V_{CC}$ rises above $V_{TH}$ for the duration of the reset timeout period. The MAX6323 has a push-pull output and the MAX6324 has an open-drain output. Connect a pullup resistor from $\overline{RESET}$ to any supply voltage up to +6V.                                                                                            |

Figure 1. Detailed Watchdog Input Timing Relationship

### Detailed Description

The MAX6323/MAX6324 uP supervisory circuits maintain system integrity by alerting the µP to fault conditions. In addition to a standard VCC monitor (for power-on reset, brownout detect, and power-down reset), the devices include a sophisticated watchdog timer that detects when the processor is running outside an expected window of operation for a specific application. The watchdog signals a fault when the input pulses arrive too early (faster than the selected twD1 timeout period) or too late (slower than the selected twp2 timeout period) (Figure 1). Incorrect timing can lead to poor or dangerous system performance in tightly controlled operating environments. Incorrect timing could be the result of improper µP clocking or code execution errors. If a timing error occurs, the MAX6323/MAX6324 issue a watchdog pulse output, independent from the reset output, indicating that system maintenance may be required.

#### **Watchdog Function**

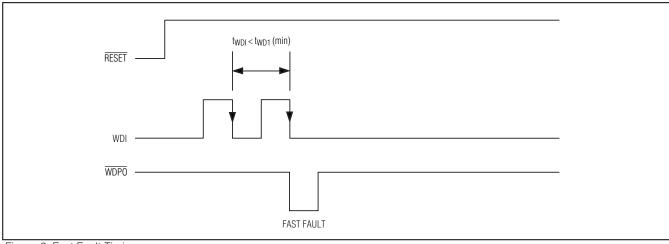

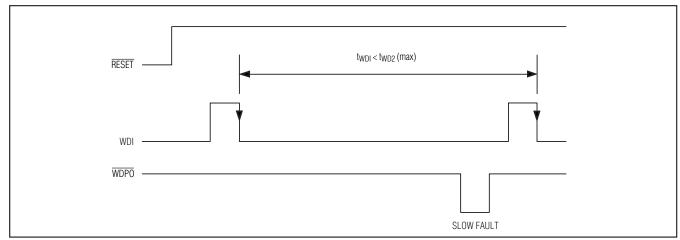

A pulse on the watchdog output WDPO can be triggered by a fast fault or a slow fault. If the watchdog input (WDI) has two falling edges too close to each

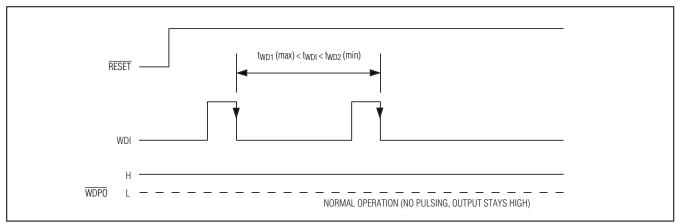

other (faster than twD1) (Figure 2) or falling edges that are too far apart (slower than twD2) (Figure 3), WDPO is pulsed low. Normal watchdog operation is displayed in Figure 4 (WDPO is not asserted). The internal watchdog timer is cleared when a WDI falling edge is detected within the valid watchdog window or when the device's RESET or WDPO outputs are deasserted. All WDI input pulses are ignored while either RESET or WDPO is asserted. Figure 1 identifies the input timing regions where WDPO fault outputs will be observed with respect to twD1 and twD2. After RESET or WDPO deasserts, the first WDI falling edge is ignored for the fast fault condition (Figure 2).

Upon detecting a watchdog fault, the WDPO output will pulse low for 1ms. WDPO is an open-drain output. Connect a pullup resistor on WDPO to any supply up to +6V.

#### Vcc Reset

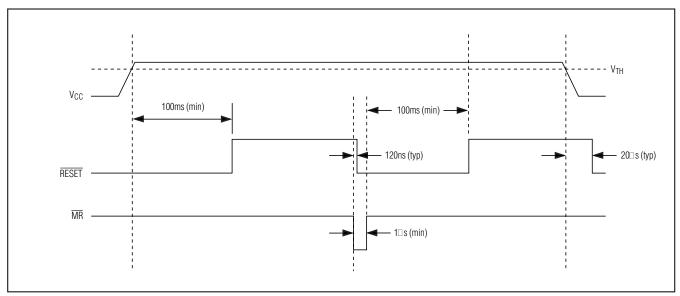

The MAX6323/MAX6324 also include a standard  $V_{CC}$  reset monitor to ensure that the  $\mu P$  is started in a known state and to prevent code execution errors during power-up, power-down, or brownout conditions. RESET is asserted whenever the  $V_{CC}$  supply voltage

6 \_\_\_\_\_\_ /N/XI/M

Figure 2. Fast Fault Timing

Figure 3. Slow Fault Timing

Figure 4. Normal Operation, WDPO Not Asserted

Figure 5. RESET Timing Relationship

falls below the preset threshold or when the manual reset input (MR) is asserted. The RESET output remains asserted for at least 100ms after VCC has risen above the reset threshold and MR is deasserted (Figure 5). For noisy environments, bybass VCC with a 500pF (min) capacitor to ensure correct operation.

The MAX6323 has a push-pull output stage, and the MAX6324 utilizes an open-drain output. Connect a pull-up resistor on the RESET output of the MAX6324 to any supply up to +6V. Select a resistor value large enough to register a logic low (see *Electrical Characteristics*) and small enough to register a logic high while supplying all input leakage currents and leakage paths connected to the RESET line. A  $10k\Omega$  pullup is sufficient in most applications.

#### Manual Reset Input

Many  $\mu P$ -based products require manual reset capability to allow an operator or external logic circuitry to initiate a reset. The manual reset input (MR) can connect directly to a switch without an external pullup resistor or debouncing network.  $\overline{MR}$  is internally pulled up to  $\underline{VCC}$  and, therefore, can be left unconnected if unused.  $\overline{MR}$  is designed to reject fast, negative-going transients (typically 100ns pulses), and it must be held low for a minimum of 1 $\mu$ s to assert the reset output (Figure 5). A 0.1 $\mu$ F capacitor from  $\overline{MR}$  to ground provides additional noise immunity. After  $\overline{MR}$  transitions from low to high, reset will remain asserted for the duration of the reset timeout period, at least 100ms.

### Applications Information

#### **Negative-Going Vcc Transients**

The MAX6323/MAX6324 are relatively immune to short-duration negative-going VCC transients (glitches), which usually do not require the entire system to shut down. Typically, 200ns large-amplitude pulses (from ground to VCC) on the supply will not cause a reset. Lower amplitude pulses result in greater immunity. Typically, a VCC transient that falls 100mV below the reset threshold and lasts less than 20 $\mu$ s will not trigger a reset (see *Typical Operating Characteristics*). An optional  $0.1\mu$ F bypass capacitor mounted close to VCC provides additional transient immunity.

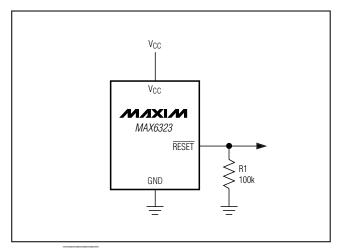

# Ensuring a Valid Reset Output Down to Vcc = 0V

When V<sub>CC</sub> falls below +1.2V, the MAX6323 RESET output no longer sinks current; it becomes an open circuit. Therefore, high-impedance CMOS logic inputs connected to RESET can drift to undetermined voltages. This does not present a problem in most applications, since most µPs and other circuitry are inoperative with V<sub>CC</sub> below +1.2V. However, in applications where RESET must be valid down to 0, adding a pulldown resistor to RESET causes any stray leakage currents to flow to ground, holding RESET low (Figure 6). R1's value is not critical;  $100\text{k}\Omega$  is large enough not to load RESET and small enough to pull RESET to ground. This scheme does not work with the open-drain output of the MAX6324.

8 \_\_\_\_\_\_ NIXI/N

Vcc

$\Box P$

GND

RESET

INPUT

## μP Supervisory Circuits with Windowed (Min/Max) Watchdog and Manual Reset

Vcc .

Figure 6.  $\overline{RESET}$  Valid to  $V_{CC}$  = Ground Circuit

# GND Figure 7. Interfacing to µPs with Bidirectional Reset Pins

$V_{CC}$

MIXIM

MAX6324

RESET

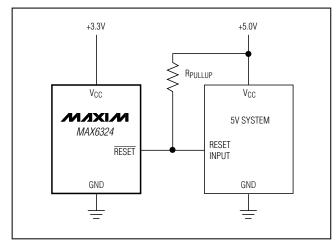

### Interfacing to uPs with **Bidirectional Reset Pins**

Since the RESET output on the MAX6324 is open-drain. this device easily interfaces with µPs that have bidirectional reset pins, such as the Motorola 68HC11. Connecting the uP supervisor's RESET output directly to the microcontroller's (µC's) RESET pin with a single pullup resistor allows either device to assert reset (Figure 7).

#### MAX6324 Open-Drain RESET Output **Allows Use with Multiple Supplies**

Generally, the pullup resistor connected to the MAX6324 will connect to the supply voltage that is being monitored at the IC's VCC pin. However, some systems may use the open-drain output to level-shift from the monitored supply to reset circuitry powered by some other supply (Figure 8). Keep in mind that as the MAX6324's V<sub>CC</sub> decreases below +1.2V, so does the IC's ability to sink current at RESET. Also, with any pullup resistor, RESET will be pulled high as VCC decays toward 0. The voltage where this occurs depends on the pullup resistor value and the voltage to which it is connected.

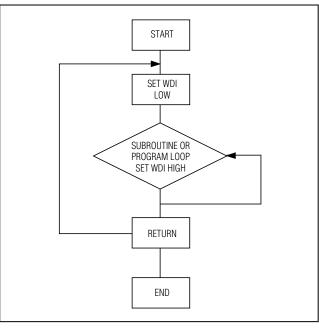

#### **Watchdog Software Considerations**

To help the watchdog timer monitor software execution more closely, set and reset the watchdog input at different points in the program, rather than "pulsing" the watchdog input high-low-high or low-high-low. This technique avoids a "stuck" loop in which the watchdog

Figure 8. MAX6324 Open-Drain RESET Output Allows Use with Multiple Supplies

time would continue to be reset within the loop, keeping the watchdog from timing out.

Figure 9 shows an example of a flow diagram where the I/O driving the watchdog input is set high at the beginning of the program, set low at the beginning of every subroutine or loop, then set high again when the program returns to the beginning. If the program should "hang" in any subroutine, the problem would be guickly corrected, since the I/O is continually set low and the watchdog time is allowed to time out, causing a reset or interrupt to be issued.

Figure 9. Watchdog Flow Diagram

#### WDPO to MR Loopback

An error detected by the watchdog often indicates that a problem has occurred in the  $\mu P$  code execution. This could be a stalled instruction or a loop from which the processor cannot free itself. If the  $\mu P$  will still respond to a nonmaskable input (NMI), the processor can be redirected to the proper code sequence by connecting the  $\overline{WDPO}$  output to an NMI input. Internal RAM data should not be lost, but it may have been contaminated by the same error that caused the watchdog to time out

If the processor will not recognize NMI inputs, or if the internal data is considered potentially corrupted when a watchdog error occurs, the processor should be restarted with a reset function. To obtain proper reset timing characteristics, the  $\overline{\text{WDPO}}$  output should be connected to the  $\overline{\text{MR}}$  input, and the  $\overline{\text{RESET}}$  output should drive the  $\mu P$   $\overline{\text{RESET}}$  input (Figure 10). The short 1ms  $\overline{\text{WDPO}}$  pulse output will assert the manual reset input and force the  $\overline{\text{RESET}}$  output to assert for the full reset timeout period (100ms min). All internal RAM data is lost during the reset period, but the processor is quaranteed to begin in the proper operating state.

Figure 10. WDPO to MR Loopback Circuit

#### Standard Versions

| MAX6323AUT29 | MAX6324AUT29 |

|--------------|--------------|

| MAX6323AUT46 | MAX6324AUT46 |

| MAX6323CUT29 | MAX6324BUT29 |

| MAX6323CUT46 | MAX6324BUT46 |

| MAX6323DUT29 | MAX6324EUT29 |

| MAX6323DUT46 | MAX6324EUT46 |

| MAX6323HUT29 | MAX6324HUT29 |

| MAX6323HUT46 | MAX6324HUT46 |

# Reset Threshold Range \_\_\_\_\_(-40°C to +125°C)

| SUFFIX | MIN  | TYP  | MAX  | UNITS |

|--------|------|------|------|-------|

| 46     | 4.50 | 4.63 | 4.75 |       |

| 44     | 4.25 | 4.38 | 4.50 |       |

| 31     | 3.00 | 3.08 | 3.15 | \/    |

| 29     | 2.85 | 2.93 | 3.00 | v     |

| 26     | 2.55 | 2.63 | 2.70 |       |

| 23     | 2.25 | 2.32 | 2.38 |       |

### Ordering Information (continued)

| PART           | TEMP<br>RANGE   | PIN-<br>PACKAGE | RESET<br>OUTPUT |  |

|----------------|-----------------|-----------------|-----------------|--|

| MAX6324_UTT    | -40°C to +125°C | 6 SOT23         | Open<br>Drain   |  |

| MAX6324_UT/V-T | -40°C to +125°C | 6 SOT23         | Open<br>Drain   |  |

| MAX6324_UT/V+T | -40°C to +125°C | 6 SOT23         | Open<br>Drain   |  |

<sup>\*</sup>These devices are factory trimmed to one of eight watchdogtimeout windows and one of six reset voltage thresholds. Insert the letter corresponding to the desired watchdog-timeout window (A, B, C, D, E, F, G, or H) into the blank following the number 6323 or 6324 (see Watchdog Timeout table). Insert the two-digit code (46, 44, 31, 29, 26, or 23) after the letters UT for the desired nominal reset threshold (see Reset Threshold Range table at end of data sheet).

N denotes an automotive qualified part.

Devices are available in both leaded and lead-free packaging. Specify lead-free by replacing "-T" with "+T" when ordering. **Note:** There are eight standard versions of each device available (see Standard Versions table). Sample stock is generally held on standard versions only. Standard versions have an order increment requirement of 2500 pieces. Nonstandard versions have an order increment requirement of 10,000 pieces. Contact factory for availability of nonstandard versions.

### **Chip Information**

TRANSISTOR COUNT: 1371

PROCESS: BiCMOS

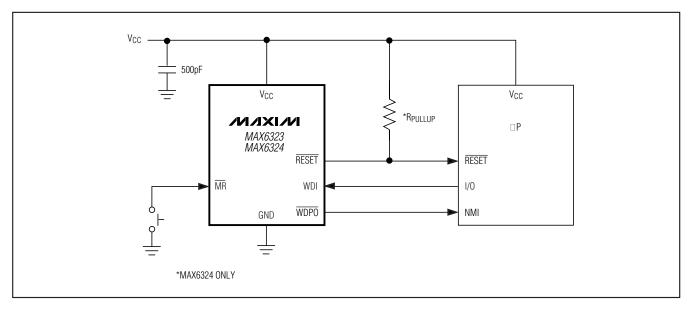

## **Typical Operating Circuit**

### **Package Information**

For the latest package outline information and land patterns, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | OUTLINE NO.    | LAND<br>PATTERN NO. |

|--------------|--------------|----------------|---------------------|

| 6 SOT23      | U6-1         | <u>21-0058</u> | <u>90-0175</u>      |

12 \_\_\_\_\_\_ **/\/**/**X//**/

### **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION                                                    | PAGES<br>CHANGED |

|--------------------|---------------|----------------------------------------------------------------|------------------|

| 0                  | 10/00         | Initial release                                                | _                |

| 5                  | 5/10          | Updated the Ordering Information and Absolute Maximum Ratings. | 1, 2, 10         |

| 6                  | 1/11          | Corrected placement of /V in the Ordering Information section  | 11               |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.