Data Sheet July 2003 FN4862.6

## 2.4GHz Power Amplifier and Detector

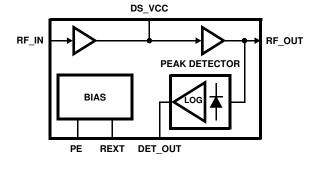

The ISL3984 is a 2.4GHz monolithic SiGe power amplifier designed to operate in the ISM band. It features two low-voltage single supply stages.

Cascaded, they deliver 18dBm (Typical) output power for the typical Direct Sequence Spread Spectrum (DSSS) signal (ACPR, 1st side lobe < -30dBc, 2nd side lobe < -50dBc).

In addition, the device includes a 2.4GHz detector which is accurate over a 15dB dynamic range within  $(\pm)1dB$ . Therefore, an accurate ALC function can be implemented.

The ISL3984 is housed in a 16 lead QFN package well-suited for PCMCIA board applications.

### **Ordering Information**

| PART NUMBER | TEMP<br>RANGE (°C) | PACKAGE       | PKG.<br>DWG.# |

|-------------|--------------------|---------------|---------------|

| ISL3984IR   | -40 to 85          | 16 Ld QFN     | L16.4x4       |

| ISL3984IR96 | -40 to 85          | Tape and Reel |               |

## Simplified Block Diagram

#### **Features**

| • | Single Supply 2.7V to 3.6V                                                                   |

|---|----------------------------------------------------------------------------------------------|

| • | Output Power . 18dBm (Typical) at ACPR, DSSS, 1st Side Lobe < -30dBc, 2nd Side Lobe < -50dBc |

| • | Power Gain                                                                                   |

| • | Detector Linear Input Power Range15dE                                                        |

| • | Detector Accuracy                                                                            |

### **Applications**

- IEEE802.11 1, 2 or 5.5Mbps Standard

- Systems Targeting IEEE802.11b, 11Mbps Standard

- · Wireless Local Area Networks (WLAN)

- PCMCIA Wireless Transceivers

- ISM Systems Including Automatic Level Control (ALC)

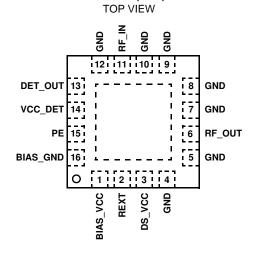

ISL3984 (QFN)

TDMA Packet Protocol Radios

#### **Pinouts**

### Pin Descriptions

| PIN NUMBER  | NAME     | DESCRIPTION                                                                                      |

|-------------|----------|--------------------------------------------------------------------------------------------------|

| 1           | BIAS_VCC | Power Supply                                                                                     |

| 2           | REXT     | Bias Resistor, biasing scheme independent of absolute temperature                                |

| 3           | DS_VCC   | Driver Stage Power Supply                                                                        |

| 4, 5        | GND      | DC and RF Ground                                                                                 |

| 6           | RF_OUT   | RF Output of the Power Amplifier                                                                 |

| 7, 8, 9, 10 | GND      | DC and RF Ground                                                                                 |

| 11          | RF_IN    | RF Input of the Power Amplifier                                                                  |

| 12          | GND      | DC and RF Ground                                                                                 |

| 13          | DET_OUT  | Detector Output                                                                                  |

| 14          | VCC_DET  | Detector Power Supply                                                                            |

| 15          | PE       | Digital Input Control Pin to enable operation of the Power Amplifier. Enable logic level is high |

| 16          | BIAS_GND | DC and RF Ground                                                                                 |

The ISL3984 works seamlessly with the PRISM II and PRISM 2.5 WLAN chip set components to give you a highly integrated, cost effective 11Mbps WLAN solution in the 2.4-2.5GHz ISM band. The ISL3984 is fabricated in the fastest SiGe BiCMOS process available allowing superior RF performance, normally found only in GaAs ICs. Cost-effective functions, normally requiring external components, are integrated into one IC. The ISL3984 integrates the following functions in one compact 16-pin QFN:

- Two Stage, 30dB Gain RFPA,

- Logarithmic power detect function (15dB Dynamic Range),

- CMOS level compatible Power Up/Down function,

- Single supply, 2.7V to 3.6V Operation.

The ISL3984 contains a highly linear RFPA designed to deliver 18dBm and meet an ACPR specification of -30dBc in the 2.4–2.5GHz ISM band. The performance of this two-stage RFPA can be optimized by adjusting the bias current with a dedicated resistor. No external positive or negative power supplies are required to set the bias currents. The on-chip bias network provides the optimum bias current temperature compensation when low Temperature Coefficient (TC) external resistors are used. To get the best performance from the ISL3984, the output stage matching network can be tailored using external components.

The ISL3984 power detect function provides a DC output voltage that is proportional to the logarithm of the output power. For an output power of 18dBm, the detector is accurate to within 0.5dB. The slope of the detector output voltage is 100mV/dB over a 15dB dynamic range. A simple application of the detector is to provide in-line monitoring of the output power using a DC voltmeter. No longer is a power meter or spectrum analyzer required. A more value-added application would use the HFA3861B/HFA3863 Baseband Processor to dynamically monitor the ISL3984 output power and control transmit power by adjusting the AGC of the HFA3783 IF Quadrature Modem to provide the best possible error-free data transfer rate for any given environment. Closed-loop power control is a very important feature which compensates for variability in the transmit chain (radio-to-radio, channel-to-channel, overtemperature, etc.).

The ISL3984 power up/down feature integrates the power-down capability onto the IC and requires no external components, thus freeing up board space and reducing external component count and cost. When the CMOS compatible Power Enable (PE) pin is driven low, the total supply current drops to under  $50\mu\text{A}$ , typically in 300ns. When the PE pin is driven high, the full ISL3984 output power is available in a few hundred nanoseconds.

In summary, the ISL3984 RFPA provides a highly cost- effective solution for the PA function by integrating many features that would require significant development time, drive up the total bill of materials cost and consume precious board space. It mates seamlessly with the other PRISM II ICs to provide a highly integrated, cost-effective 11Mbps WLAN solution in the 2.4–2.5GHz ISM band.

#### **Absolute Maximum Ratings**

| Supply Voltage                              |                               |

|---------------------------------------------|-------------------------------|

| Voltage on Any Other Pin                    | -0.3 to V <sub>CC</sub> +0.3V |

| V <sub>CC</sub> to V <sub>CC</sub> Decouple | 0.3 to +0.3V                  |

| Any GND to GND                              | 0.3 to +0.3V                  |

### **Operating Conditions**

| Temperature Range    | 40° to 85°C  |

|----------------------|--------------|

| Supply Voltage Range | 2.7V to 3.6V |

#### **Thermal Information**

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. θ<sub>JC</sub>, the

"case temp" is measured at the center of the exposed metal pad on the package underside. See Tech Brief TB379.

#### **General DC Electrical Specifications**

| PARAMETER                                                  | TEMP. (°C) | MIN                  | TYP                 | MAX                  | UNITS |

|------------------------------------------------------------|------------|----------------------|---------------------|----------------------|-------|

| Supply Voltage                                             | Full       | 2.7                  | -                   | 3.6                  | V     |

| Total Power Amplifier Supply Current at 3.3V, 18dBm Output | 25         | -                    | 137                 | -                    | mA    |

| RF Detector Supply Current                                 | 25         | -                    | -                   | 2                    | mA    |

| Power Down Supply Current                                  | Full       | -                    | 200                 | -                    | μА    |

| Power Up/ Down Speed                                       | Full       | -                    | 300                 | -                    | ns    |

| CMOS Low Level Input Voltage                               | Full       | -                    | -                   | 0.3*V <sub>DD</sub>  | V     |

| CMOS High Level Input Voltage (V <sub>DD</sub> = 3.6V)     | Full       | 0.7*V <sub>DD</sub>  | -                   | -                    | V     |

| CMOS Threshold Voltage                                     | Full       | >0.3*V <sub>DD</sub> | 0.5*V <sub>DD</sub> | <0.7*V <sub>DD</sub> | V     |

| CMOS High or Low Level Input Current                       | Full       | -10                  | -                   | +10                  | μА    |

# **Power Amplifier AC Electrical Specifications** V<sub>CC</sub> = 3.3V, f = 2.45GHz, Unless Otherwise Specified. Typical Application Circuit (external input and output matching networks) has been used.

| PARAMETER             | TEST CONDITIONS                                             | TEMP. (°C) | MIN  | TYP | MAX  | UNITS |

|-----------------------|-------------------------------------------------------------|------------|------|-----|------|-------|

| RF Frequency Range    |                                                             | Full       | 2400 | -   | 2500 | MHz   |

| Power/Voltage Gain    |                                                             | Full       | 27   | 30  | 35   | dB    |

| Input 50Ω VSWR        |                                                             | 25         | -    | -   | 2:1  | -     |

| Output 50Ω VSWR       |                                                             | 25         | -    | -   | 3:1  | -     |

| Output Power          | ACPR, DSSS, 1st Side Lobe <-30dBc, 2nd<br>Side Lobe <-50dBc | Full       | -    | 18  | -    | dBm   |

| Output Stability VSWR | Output Spurs Less than -60dBc                               | Full       | -    | -   | 10:1 | -     |

| Output Load Mismatch  | (Note 2)                                                    | Full       | -    | -   | 10:1 | -     |

#### NOTE:

2. Devices sustain no damage when subjected to a mismatch with a maximum of 10:1.

#### **Peak Detector AC Electrical Specifications**

| PARAMETER                        | TEST CONDITIONS             | TEMP (°C) | MIN  | TYP  | MAX | UNITS |

|----------------------------------|-----------------------------|-----------|------|------|-----|-------|

| RF Output Detector Response Time | External Capacitor, C = 5pF | Full      | -    | 0.15 | -   | μS    |

| RF Output Detector Voltage Range | Load > 1M                   | Full      | 0    | -    | 1.5 | V     |

| RF Output Detector Linearity     | Over Linear Range           | Full      | -0.5 | -    | 0.5 | dB/V  |

| RF Output Detector Accuracy      | 600mV <sub>DC</sub> Output  | Full      | -1   | -    | +1  | dB    |

| RF Output Detector Slope         | Over Linear Range           | Full      | -    | 10   | -   | dB/V  |

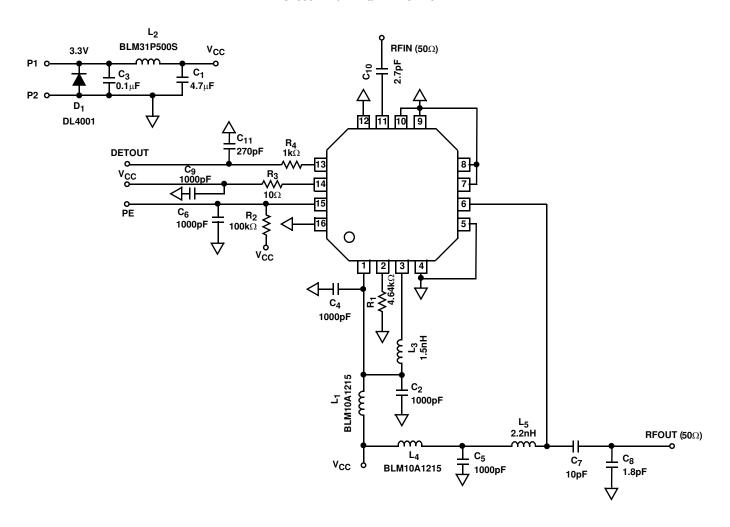

# Typical Application Example

ISL3984 - 16 PIN QFN PACKAGE

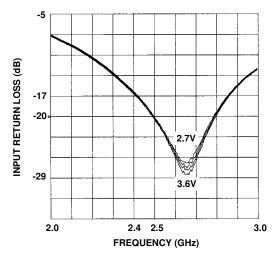

# **Typical Performance Curves**

FIGURE 1. INPUT RETURN LOSS OVERVOLTAGE

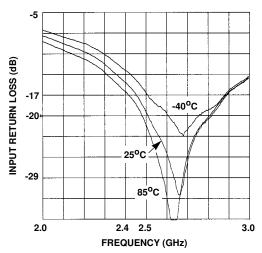

FIGURE 2. INPUT RETURN LOSS OVERTEMPERATURE

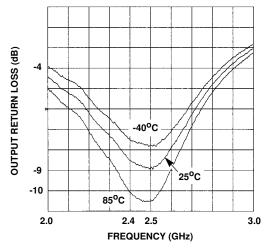

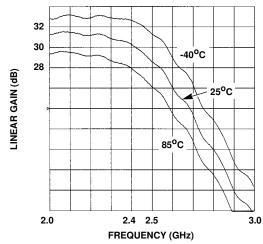

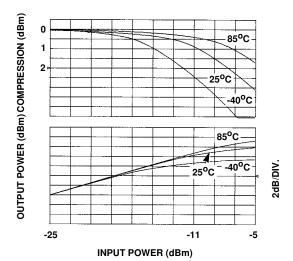

# Typical Performance Curves (Continued)

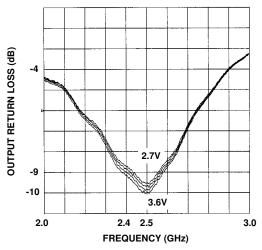

FIGURE 3. OUTPUT RETURN LOSS OVERVOLTAGE

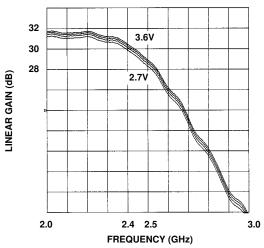

FIGURE 5. LINEAR GAIN OVERVOLTAGE

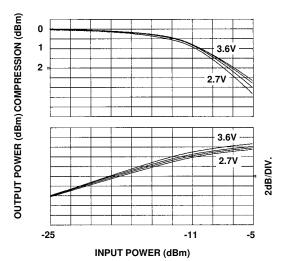

FIGURE 7. GAIN COMPRESSION OVERVOLTAGE

FIGURE 4. OUTPUT RETURN LOSS OVERTEMPERATURE

FIGURE 6. LINEAR GAIN OVERTEMPERATURE

FIGURE 8. GAIN COMPRESSION OVERTEMPERATURE

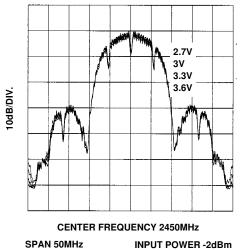

# Typical Performance Curves (Continued)

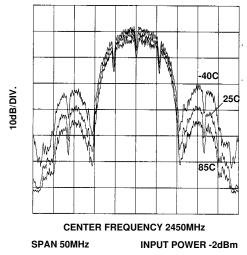

FIGURE 9. DSSS OUTPUT SIGNAL OVERVOLTAGE

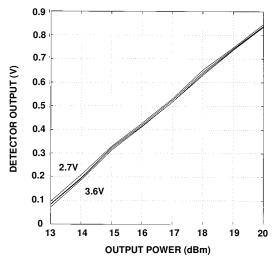

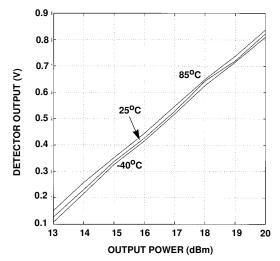

FIGURE 11. DETECTOR OUTPUT OVERVOLTAGE

FIGURE 10. DSSS OUTPUT SIGNAL OVERTEMPERATURE

FIGURE 12. DETECTOR OUTPUT OVERTEMPERATURE

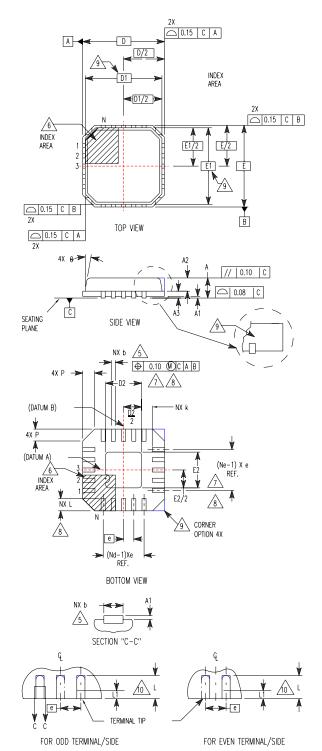

# Quad Flat No-Lead Plastic Package (QFN) Micro Lead Frame Plastic Package (MLFP)

L16.4x4

16 LEAD QUAD FLAT NO-LEAD PLASTIC PACKAGE

(COMPLIANT TO JEDEC MO-220-VGGC ISSUE C)

|        | MILLIMETERS |          |      |       |

|--------|-------------|----------|------|-------|

| SYMBOL | MIN         | NOMINAL  | MAX  | NOTES |

| Α      | 0.80        | 0.90     | 1.00 | -     |

| A1     | -           | -        | 0.05 | -     |

| A2     | -           | -        | 1.00 | 9     |

| А3     |             | 0.20 REF |      | 9     |

| b      | 0.23        | 0.28     | 0.38 | 5, 8  |

| D      |             | 4.00 BSC |      | -     |

| D1     |             | 3.75 BSC |      | 9     |

| D2     | 1.95        | 2.10     | 2.25 | 7, 8  |

| E      | 4.00 BSC    |          |      | -     |

| E1     |             | 3.75 BSC |      |       |

| E2     | 1.95        | 2.10     | 2.25 | 7, 8  |

| е      |             | 0.65 BSC |      | -     |

| k      | 0.25        | -        | -    | -     |

| L      | 0.35        | 0.60     | 0.75 | 8     |

| L1     | -           | -        | 0.15 | 10    |

| N      | 16          |          |      | 2     |

| Nd     | 4           |          |      | 3     |

| Ne     | 4           |          |      | 3     |

| Р      | -           | -        | 0.60 | 9     |

| θ      |             | -        | 12   | 9     |

Rev. 4 10/02

#### NOTES:

- 1. Dimensioning and tolerancing conform to ASME Y14.5-1994.

- 2. N is the number of terminals.

- 3. Nd and Ne refer to the number of terminals on each D and E.

- 4. All dimensions are in millimeters. Angles are in degrees.

- 5. Dimension b applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

- 7. Dimensions D2 and E2 are for the exposed pads which provide improved electrical and thermal performance.

- 8. Nominal dimensions are provided to assist with PCB Land Pattern Design efforts, see Intersil Technical Brief TB389.

- Features and dimensions A2, A3, D1, E1, P & θ are present when Anvil singulation method is used and not present for saw singulation.

- Depending on the method of lead termination at the edge of the package, a maximum 0.15mm pull back (L1) maybe present. L minus L1 to be equal to or greater than 0.3mm.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com