# M87C51

## CHMOS Single-Chip 8-Bit Microcontroller

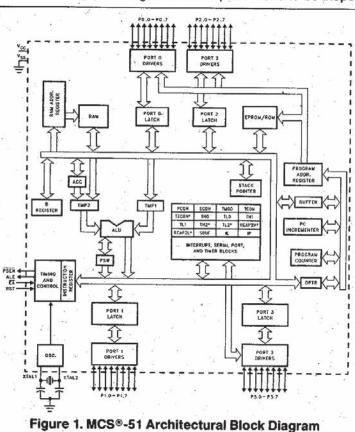

The M87C51 is the EPROM version of the M80C51BH. It is fabricated on Intel's CHMOS II-E process. It contains 4 Kbytes of on-chip program memory that can be electrically programmed, and can be erased by exposure to ultraviolet light.

The M87C51 EPROM array uses a modified Quick-Pulse Programming algorithm, by which the entire 4 Kbyte array can be programmed in about 12 seconds.

### Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

## 58E D 🖿 4826175 O124451 5TO 📰 ITL1

INTEL CORP (UP/PRPHLS)

### M87C51

## CHMOS SINGLE-CHIP 8-BIT MICROCONTROLLER WITH 4 KBYTES OF EPROM PROGRAM MEMORY

Military

- High Performance CHMOS EPROM

- Quick-Pulse Programming<sup>TM</sup> Algorithm

- 2-Level Program Memory Lock

- Boolean Processor

- 128-Byte Data RAM

- 32 Programmable I/O Lines

- Two 16-Bit Timer/Counters

- 5 Interrupt Sources

- Available in 40-Pin CERDIP, 44-Pin Leadless Chip Carrier, 44-Pin Gull-wing and 44-Pin J-Lead Packages

- Programmable Serial Channel

- TTL- and CMOS-Compatible Logic Levels

- 64K External Program Memory Space

T-49-19-63

4

- 64K External Data Memory Space

- IDLE and POWER DOWN Modes

- ONCETM Mode Facilitates System Testing

- Military Temperature Range: -55°C to + 125°C = (T<sub>C</sub>)

The M87C51 is the EPROM version of the M80C51BH. It is fabricated on Intel's CHMOS II-E process. It contains 4 Kbytes of on-chip program memory that can be electrically programmed, and can be erased by exposure to ultraviolet light.

The M87C51 EPROM array uses a modified Quick-Pulse Programming<sup>™</sup> algorithm, by which the entire 4 Kbyte array can be programmed in about 12 seconds.

The extremely low operating power, along with the two reduced power modes, Idle and Power Down, make this part very suitable for low power applications. The Idle mode freezes the CPU while allowing the RAM, timer/counters, serial port, and interrupt system to continue functioning. The Power Down mode saves the RAM contents but freezes the oscillator, causing all other chip functions to be inoperative.

### 58E D 4826175 0124452 437 MITLL M87C51

### INTEL CORP (UP/PRPHLS)

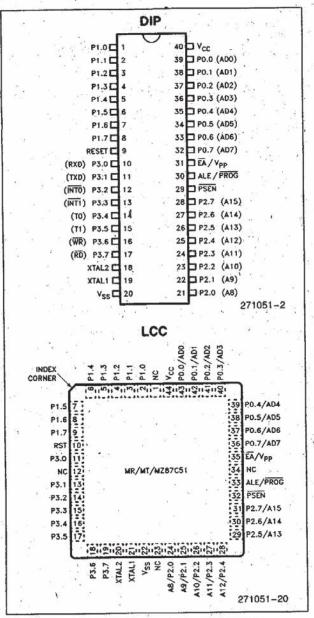

Figure 2. M87C51 Pin Connections

#### PIN DESCRIPTION

V<sub>CC</sub>: Supply voltage during normal, Idle, and Power Down operations.

Vss: Circuit ground.

**Port 0:** Port 0 is an 8-bit open drain bidirectional I/O port. As an output port each pin can sink 8 LS TTL inputs. Port 0 pins that have 1s written to them float, and in that state can be used as high-impedance inputs.

Port 0 is also the multiplexed low-order address and data bus during accesses to external memory. In this application it uses strong internal pullups when emitting 1s.

Port 0 also receives the code bytes during EPROM programming, and outputs the code bytes during program verification. External pullups are required during program verification.

**Port 1:** Port 1 is an 8-bit bidirectional I/O port with internal pullups. Port 1 pins that have 1s written to them are pulled high by the internal pullups, and in that state can be used as inputs. As inputs, Port 1 pins that are externally being pulled low will source current (IIL, on the data sheet) because of the internal pullups.

Port 1 also receives the low-order address bytes during EPROM programming and program verification.

**Port 2:** Port 2 is an 8-bit bidirectional I/O port with internal pullups. Port 2 pins that have 1s written to them are pulled high by the internal pullups, and in that state can be used as inputs. As inputs, Port 2 pins that are externally being pulled low will source current (IIL, on the data sheet) because of the internal pullups.

Port 2 emits the high-order address byte during fetches from external Program memory and during accesses to external Data Memory that use 16-bit addresses (MOVX @DPTR). In this application it uses strong internal pullups when emitting 1s.

During accesses to external Data Memory that use 8-bit addresses (MOVX @Ri), Port 2 emits the contents of the P2 Special Function Register.

Port 2 also receives some control signals and the high-order address bits during EPROM programming and program verification.

**Port 3:** Port 3 is an 8-bit bidirectional I/O port with internal pullups. Port 3 pins that have 1s written to them are pulled high by the internal pullups, and in that state can be used as inputs. As inputs, Port 3 pins that are externally being pulled low will source current (IIL, on the data sheet) because of the pullups.

Port 3 also serves the functions of various special features of the MCS®-51 Family, as listed below:

| Pin  | Name | Alternate Function                |

|------|------|-----------------------------------|

| P3.0 | RXD  | Serial input line                 |

| P3.1 | TXD  | Serial output line                |

| P3.2 | INTO | External Interrupt 0              |

| P3.3 | INT1 | External Interrupt 1              |

| P3.4 | TO   | Timer 0 external input            |

| P3.5 | T1   | Timer 1 external input            |

| P3.6 | WR   | External Data Memory Write strobe |

| P3.7 | RD   | External Data Memory Read strobe  |

### | 4826175 0124453 373 🎟 ITL1

M87C51

### INTEL CORP (UP/PRPHLS)

Port 3 also receives some control signals for EPROM programming and program verification.

58E

**RST:** Reset input. A logic high on this pin for two machine cycles while the oscillator is running resets the device. An internal pulldown resistor permits a power-on reset to be generated using only an external capacitor to  $V_{CC}$ .

ALE/PROG: Address Latch Enable output signal for latching the low byte of the address during accesses to external memory. This pin is also the program pulse input (PROG) during EPROM programming.

In normal operation ALE is emitted at a constant rate of 1/6 the oscillator frequency, and may be used for external timing or clocking purposes. Note, however, that one ALE pulse is skipped during each access to external Data Memory.

**PSEN:** Program Store Enable is the Read strobe to External Program Memory. When the M87C51 is executing from Internal Program Memory, <u>PSEN</u> is inactive (high). When the device is executing code from External Program Memory, <u>PSEN</u> is activated twice each machine cycle, except that two <u>PSEN</u> activations are skipped during each access to External Data Memory.

**EA/Vpp:** External Access enable. EA must be externally pulled low in order to enable the M87C51 to fetch code from External Program Memory locations 0000H to 0FFFH. Note, however, that if either of the Lock Bits is programmed, the logic level at EA is internally latched during reset.

$\overline{\text{EA}}$  must be strapped to  $V_{CC}$  for internal program execution.

This pin also receives the 12.75V programming supply voltage (Vpp) during EPROM programming.

XTAL1: Input to the inverting oscillator amplifier and input to the internal clock generating circuits.

XTAL2: Output from the inverting oscillator amplifier.

### **OSCILLATOR CHARACTERISTICS**

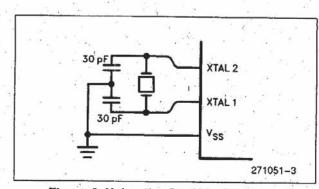

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier which can be configured for use as an on-chip oscillator, as shown in Figure 3.

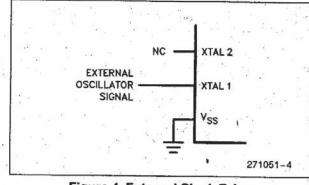

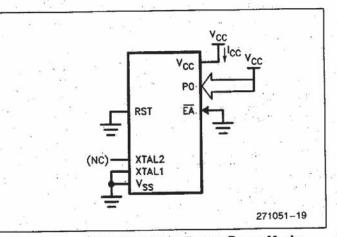

To drive the device from an external clock source, XTAL1 should be driven, while XTAL2 is left unconnected, as shown in Figure 4. There are no requirements on the duty cycle of the external clock signal, since the input to the internal clocking circuitry is

**Figure 4. External Clock Drive**

4

through a divide-by-two flip-flop, but minimum and maximum high and low times specified on the Data Sheet must be observed.

### **IDLE MODE**

In Idle Mode, the CPU puts itself to sleep while all the on-chip peripherals remain active. The mode is invoked by software. The content of the on-chip RAM and all the Special Functions Registers remain unchanged during this mode. The Idle Mode can be terminated by any enabled interrupt or by a hardware reset.

It should be noted that when Idle is terminated by a hardware reset, the device normally resumes program execution, from where it left off, up to two machine cycles before the internal reset algorithm takes control. On-chip hardware inhibits access to internal RAM in this event, but access to the port pins is not inhibited. To eliminate the possibility of an unexpected write to a port pin when Idle is terminated by reset, the instruction following the one that invokes Idle should not be one that writes to a port pin or to external data memory.

### POWER DOWN MODE

In the Power Down mode the oscillator is stopped, and the instruction that invokes Power Down is the last instruction executed. The on-chip RAM and

#### 4826175 0124454 20T MITL1 58E D

#### M87C51

### INTEL CORP (UP/PRPHLS)

Table 1. Status of the External Pins during Idle and Power Down

| Mode       | Program<br>Memory | ALE | PSEN | PORT0 | PORT1 | PORT2   | PORT3 |

|------------|-------------------|-----|------|-------|-------|---------|-------|

| Idle       | Internal          | 1 1 | . 1  | Data  | Data  | Data    | Data  |

| Idle       | External          | -1. | 1    | Float | Data  | Address | Data  |

| Power Down | Internal          | 0   | 0    | Data  | Data  | Data    | Data  |

| Power Down | External          | 0   | 0    | Float | Data  | Data    | Data  |

#### NOTE:

، لِمِ**ا** ال

For more detailed information on the reduced power modes refer to the current Intel Embedded Applications Handbook, and Application Note AP-252, "Designing with the 80C51BH."

Special Function Registers retain their values until the Power Down mode is terminated.

The only exit from Power Down is a hardware reset. Reset redefines the SFRs but does not change the on-chip RAM. The reset should not be activated before V<sub>CC</sub> is restored to its normal operating level and must be held active long enough to allow the oscillator to restart and stabilize.

### DESIGN CONSIDERATIONS

The M87C51 is available in a hermetically sealed, ceramic package which includes a window that allows for EPROM erasure when exposed to ultraviolet light (see Erasure Characteristics). During normal operation, ambient light may adversely affect the functionality of the chip. Therefore, applications which expose the M87C51 to ambient light may reguire an opaque label over the window.

If using the M87C51 to prototype for the M80C51BH, consult the Design Considerations section of the M80C51BH data sheet.

### PROGRAM MEMORY LOCK

The M87C51 contains two program memory lock schemes: Encrypted Verify and Lock Bits.

Encrypted Verify: The M87C51 implements a 32byte EPROM array that can be programmed by the customer, and which can then be used to encrypt the program code bytes during EPROM verification. The EPROM verification procedure is performed as usual, except that each code byte comes out logically X-NORed with one of the 32 key bytes. The key bytes are gone through in sequence. Therefore, to read the ROM code, one has to know the 32 key bytes in their proper sequence.

Lock Bits: Also on the chip are two Lock Bits which can be left unprogrammed (U) or can be programmed (P) to obtain the following additional features:

| Bit 1 | Bit 2 | Additional Features                                                                                                                                                       |

|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| . U   | U     | none                                                                                                                                                                      |

| Р     | U     | <ul> <li>Externally fetched code can not access internal Program Memory.</li> <li>Further programming disabled.</li> </ul>                                                |

| U.    | P     | (Reserved for Future definition.)                                                                                                                                         |

| P     | Р     | <ul> <li>Externally fetched code can not<br/>access internal Program Memory.</li> <li>Further programming disabled.</li> <li>Program verification is disabled.</li> </ul> |

When Lock Bit 1 is programmed, the logic level at the EA pin is sampled and latched during reset. If the device is powered up without a reset, the latch initializes to a random value, and holds that value until reset is activated. It is necessary that the latched value of EA be in agreement with the current logic level at that pin in order for the device to function properly.

#### ONCETM MODE

The ONCE ("on-circuit emulation") mode facilitates testing and debugging of systems using the M87C51 without the M87C51 having to be removed from the circuit. The ONCE mode is invoked by:

- 1. Pull ALE low while the device is in reset and PSEN is high;

- 2. Hold ALE low as RST is deactivated.

While the device is in ONCE mode, the Port 0 pins go into a float state, and the other port pins and ALE and PSEN are weakly pulled high. The oscillator circuit remains active. While the M87C51 is in this mode, an emulator or test CPU can be used to drive the circuit. Normal operation is restored when a normal reset is applied.

## 58E D 🗰 4826175 0124455 146 mittl

M87C51

# INTEL CORP (UP/PRPHLS)

### **ABSOLUTE MAXIMUM RATINGS\***

| Case Temperature Under Bias 55°C to + 125°C                    |

|----------------------------------------------------------------|

| Storage Temperature65°C to +150°C                              |

| Voltage on $\overline{EA}/V_{PP}$ Pin to $V_{SS}$ 0V to +13.0V |

| Voltage on Any Other Pin to V_{SS} $\dots -0.5V$ to $+6.5V$    |

| Power Dissipation                                              |

|                                                                |

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

### **Operating Conditions**

intel.

| Symbol          | Description                   | Min  | Max   | Units |

|-----------------|-------------------------------|------|-------|-------|

| TC              | Case Temperature (Instant On) | - 55 | + 125 | °C    |

| V <sub>CC</sub> | Digital Supply Voltage        | 4.50 | 5.50  | V     |

| fosc            | Oscillator Frequency          | 3.5  | 16    | MHz   |

### D.C. CHARACTERISTICS: (Over Specified Operating Conditions)

| Symbol           | Parameter                                                                                                               | Min                      | Typ(1)           | Max                                     | Unit           | Comments                                 |

|------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------|-----------------------------------------|----------------|------------------------------------------|

| VIL              | Input Low Voltage (Except EA)                                                                                           | -0.5                     |                  | 0.2 V <sub>CC</sub> -0.25               | V              |                                          |

| VIL1             | Input Low Voltage to EA                                                                                                 | 0                        |                  | 0.2 V <sub>CC</sub> -0.45               | ٧.             |                                          |

| VIH              | Input High Voltage (Except XTAL1, RST)                                                                                  | 0.2 V <sub>CC</sub> +1.1 |                  | V <sub>CC</sub> +0.5                    | V              |                                          |

| V <sub>IH1</sub> | Input High Voltage (XTAL1, RST)                                                                                         | 0.7 V <sub>CC</sub> +0.2 |                  | V <sub>CC</sub> +0.5                    | V              |                                          |

| VOL              | Output Low Voltage (Ports 1, 2, 3)                                                                                      |                          |                  | 0.45                                    | V.             | $I_{OL} = 1.6  \text{mA}$ (2)            |

| VOL1             | Output Low Voltage (Port 0, ALE, PSEN)                                                                                  |                          | 1. A. P.         | 0.45                                    | V              | $l_{OL} = 3.2 \text{ mA} (2)$            |

| VOH              | Output High Voltage (Ports 1, 2, 3)                                                                                     | 2.4                      |                  | · · · ·                                 | V              | $I_{OH} = -60 \mu A$                     |

|                  |                                                                                                                         | 0.75 V <sub>CC</sub>     |                  | 2 - 1 - 2 - 2 - 2 - 2 - 2 - 2 - 2 - 2 - | V              | $I_{OH} = -25 \mu A$                     |

|                  |                                                                                                                         | 0.9 V <sub>CC</sub>      |                  |                                         | ٧              | $I_{OH} = -10 \mu A$                     |

| VOH1             | Output High Voltage (Port 0 in                                                                                          | 2.4                      |                  |                                         | V              | I <sub>OH</sub> = -800 μA                |

|                  | External Bus Mode, ALE, PSEN)                                                                                           | 0.75 V <sub>CC</sub>     |                  |                                         | V              | $I_{OH} = -300 \mu A$                    |

| 19.2             |                                                                                                                         | 0.9V <sub>CC</sub>       |                  |                                         | V              | $I_{OH} = -80 \mu A$ (3)                 |

| IL               | Logical 0 Input Current (Ports 1, 2, 3)                                                                                 |                          |                  | -75                                     | μA             | $V_{IN} = 0.45 V$                        |

| TL               | Logical 1-to-0 transition current<br>(Ports 1, 2, 3)                                                                    |                          |                  | 750                                     | μΑ             | (4)                                      |

| LI               | Input Leakage Current (Port 0)                                                                                          |                          |                  | ±10                                     | μA             | 0.45 < V <sub>IN</sub> < V <sub>CC</sub> |

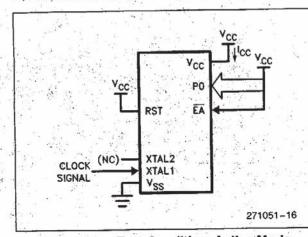

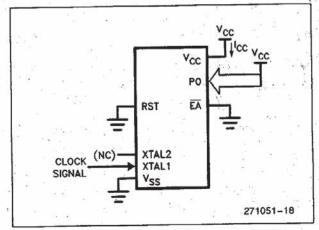

| lcc              | Power Supply Current:<br>Active Mode @ 12 MHz (Figure 5)<br>Idle Mode @ 12 MHz (Figure 6)<br>Power Down Mode (Figure 7) |                          | 11.5<br>1.3<br>3 | 35<br>6<br>75                           | mA<br>mA<br>μA | (5)                                      |

| RST              | Internal Reset Pulldown Resistor                                                                                        | 50                       |                  | 300                                     | KΩ             |                                          |

|                  | Pin Capacitance                                                                                                         | . 1                      | 1. 2.            | 10                                      | pF             |                                          |

4

#### 4826175 O124456 O82 🎟 ITL1 D 58E

M87C51

### INTEL CORP (UP/PRPHLS)

### D.C. CHARACTERISTICS: (Over Specified Operating Conditions) (Continued)

int\_.

1. "Typicals" are based on a limited number of samples taken from early manufacturing lots. The values listed are at room temp, 5V.

2. Capacitive loading on Ports 0 and 2 may cause spurious noise pulses to be superimposed on the VOLs of ALE and Ports 1 and 3. The noise is due to external bus capacitance discharging into the Port 0 and Port 2 pins when these pins make 1to-0 transitions during bus operations. In the worst cases (capacitive loading > 100pF), the noise pulse on the ALE pin may exceed 0.8V. In such cases it may be desirable to qualify ALE with a Schmitt Trigger, or use an address latch with a Schmitt Trigger STROBE input.

3. Capacitive loading on Ports 0 and 2 may cause the VOH on ALE and PSEN to momentarily fall below the 0.9 VCC specification when the address bits are stabilizing.

4. Pins of Ports 1, 2, and 3 source a transition current when they are being externally driven from 1 to 0. The transition current reaches its maximum value when VIN is approximately 2V.

5. I<sub>CC</sub> is measured with all output pins disconnected; XTAL1 driven with TCLCH, TCHCL = 5ns,  $V_{IL} = V_{SS} + .5V$ ,  $V_{IH} = V_{CC} - 0.5V$  measured with EA and RST connected to  $V_{CC}$ . "Idle" current is measured with EA and RST connected to  $V_{SS}$ . "Power Down" current is measured with XTAL1, EA and RST connected to  $V_{SS}$ . (See Figures 5 through 8 for a graphic representation of the ICC test conditions.

Figure 5. ICC Test Condition, Active Mode. All other pins are disconnected.

Figure 7. ICC Test Condition, Power Down Mode. All other pins are disconnected, V<sub>CC</sub> = 2V to 5.5V.

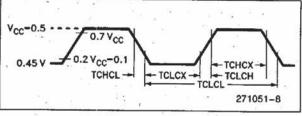

Figure 8. Clock Signal Waveform for  $I_{CC}$  Tests in Active and Idle Modes. TCLCH = TCHCL = 5 ns.

| 4826175 0124457 T19 🔳 ITL1

M87C51

## INTEL CORP (UP/PRPHLS)

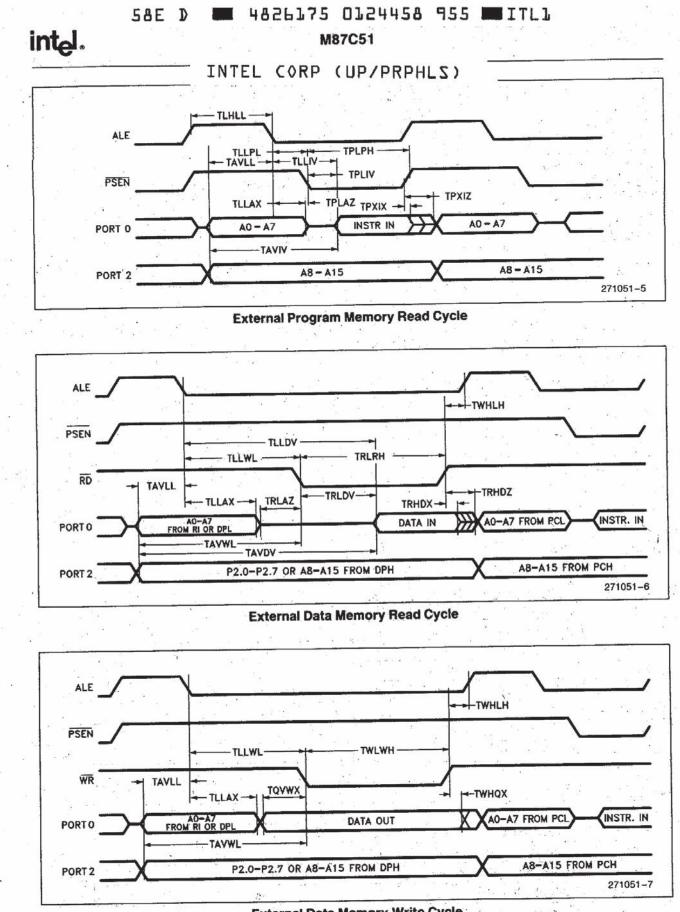

### **EXPLANATION OF THE AC SYMBOLS**

58E D

int\_l.

Each timing symbol has 5 characters. The first character is always a 'T' (stands for time). The other characters, depending on their positions, stand for the name of a signal or the logical status of that signal. The following is a list of all the characters and what they stand for.

A:Address. C:Clock. D:Input data. H:Logic level HIGH. I:Instruction (program memory contents). L:Logic level LOW, or ALE. P:PSEN. Q:Output data. R:READ signal. T:Time. V:Valid. W:WRITE signal. X:No longer a valid logic level. Z:Float.

For example,

TAVLL = Time from Address Valid to ALE Low. TLLPL = Time from ALE Low to PSEN Low.

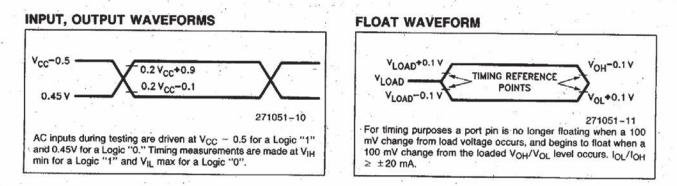

AC CHARACTERISTICS: (Over Specified Operating Conditions) Load Capacitance for Port 0, ALE, and PSEN = 100 pF; Load Capacitance for All Other Outputs = 80 pF

| Symbol  | Parameter                    | 12 MH            | Iz Osc | Variable   | Units      |       |

|---------|------------------------------|------------------|--------|------------|------------|-------|

|         |                              | Min              | Max    | Min        | Max        | Units |

| 1/TCLCL | Oscillator Frequency         | •                |        | 3.5        | 12         | MHz   |

| TLHLL   | ALE Pulse Width              | 127              |        | 2TCLCL-40  | · · ·      | ns    |

| TAVLL   | Address Valid to ALE Low     | 28               |        | TCLCL-55   |            | ns    |

| TLLAX   | Address Hold After ALE Low   | 48               |        | TCLCL-35   |            | ns    |

| TLLIV . | ALE Low to Valid Instr In    |                  | 223    |            | 4TCLCL-110 | ns    |

| TLLPL   | ALE Low to PSEN Low          | 43               |        | TCLCL-40   |            | ns    |

| TPLPH   | PSEN Pulse Width             | 205              |        | 3TCLCL-45  |            | ns    |

| TPLIV   | PSEN Low to Valid Instr In   | 3                | 135    |            | 3TCLCL-115 | ns    |

| TPXIX   | Input Instr Hold After PSEN  | 0                |        | 0          |            | ns    |

| TPXIZ   | Input Instr Float After PSEN | ÷                | 58     |            | TCLCL-25   | ns    |

| TAVIV   | Address to Valid Instr In    |                  | 302    |            | 5TCLCL-115 | ns    |

| TPLAZ   | PSEN Low to Address Float    |                  | 10     | -          | 10         | ns    |

| TRLRH   | RD Pulse Width               | 400              |        | 6TCLCL-100 |            | ns    |

| TWLWH   | WR Pulse Width               | 400              |        | 6TCLCL-100 |            | ns    |

| TRLDV   | RD Low to Valid Data In      |                  | 242    |            | 5TCLCL-175 | ns    |

| TRHDX   | Data Hold After RD           | 0                |        | 0          |            | ns    |

| TRHDZ   | Data Float After RD          | 4                | 97     |            | 2TCLCL-70  | ns    |

| TLLDV   | ALE Low to Valid Data In     | e to te t        | 507    |            | 8TCLCL-160 | ns    |

| TAVDV   | Address to Valid Data In     |                  | 575    |            | 9TCLCL-175 | ns    |

| TLLWL   | ALE Low to RD or WR Low      | 200              | 300    | 3TCLCL-50  | 3TCLCL+50  | ns    |

| TAVWL   | Address to RD or WR Low      | 203              | -<br>  | 4TCLCL-130 | 1.         | ns.   |

| TQVWX   | Data Valid to WR Transition  | 23               |        | TCLCL-60   |            | ns    |

| TWHQX   | Data Hold After WR           | 33               |        | TCLCL-50   |            | ns    |

| TRLAZ   | RD Low to Address Float      | - 1 - <u>1</u> - | 0      | eni a      | 0 .        | ns    |

| TWHLH   | RD or WR High to ALE High    | 43               | 123    | TCLCL-40   | TCLCL+40   | ns    |

### EXTERNAL PROGRAM AND DATA MEMORY CHARACTERISTICS

External Data Memory Write Cycle

### 4826175 O124459 891 MITL1

M87C51

# INTEL CORP (UP/PRPHLS)

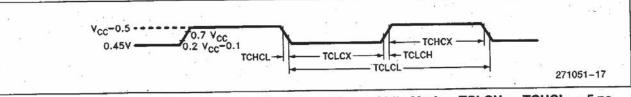

### EXTERNAL CLOCK DRIVE

intel.

58E D

| Symbol  | Parameter                                 | Min        | Max      | Units |

|---------|-------------------------------------------|------------|----------|-------|

| 1/TCLCL | Oscillator Frequency<br>87C51<br>87C51-16 | 3.5<br>3.5 | 12<br>16 | MHz   |

| TCHCX   | High Time                                 | 20         |          | ns    |

| TCLCX   | Low Time                                  | 20         |          | ns    |

| TCLCH   | Rise Time                                 |            | 20       | ns    |

| TCHCL   | Fall Time                                 |            | 20       | ns    |

4

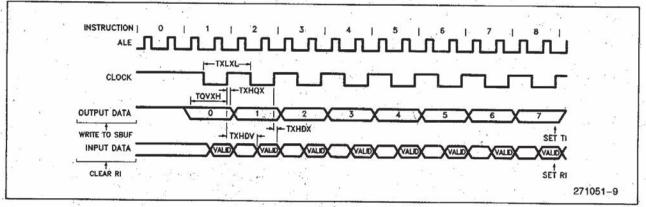

### SERIAL PORT TIMING-SHIFT REGISTER MODE (Over Specified Operating Conditions)

| Symbol | Parameter                                | 12 MH | iz Osc | Variable    | Oscillator    | Units |

|--------|------------------------------------------|-------|--------|-------------|---------------|-------|

|        |                                          | Min   | Max    | Min         | Max           | Units |

| TXLXL  | Serial Port Clock Cycle Time             | 1     | .0     | 12T0        | CLCL          | μs    |

| TQVXH  | Output Data Setup to Clock Rising Edge   | 700   | · · ·  | 10TCLCL-133 |               | ns    |

| TXHQX  | Output Data Hold After Clock Rising Edge | 50    |        | 2TCLCL-117  |               | ns    |

| TXHDX  | Input Data Hold After Clock Rising Edge  | 0     |        | 0           |               | ns    |

| TXHDV  | Clock Rising Edge to Input Data Valid    | 2     | 700    |             | 10TCLCL - 133 | ns    |

### SHIFT REGISTER MODE TIMING WAVEFORMS

#### A.C. TESTING:

#### 4826175 Ol24460 503 🎟 ITL1 D

#### M87C51

### INTEL CORP (UP/PRPHLS)

### EPROM CHARACTERISTICS

58E

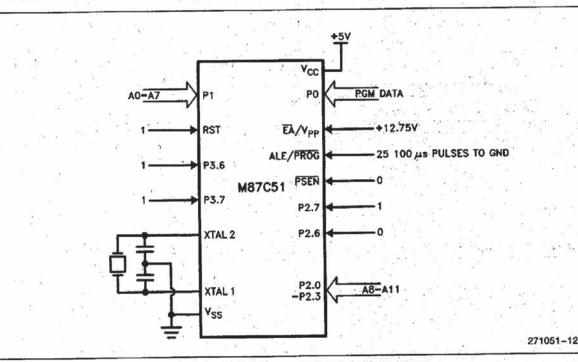

The M87C51 is programmed by a modified Quick-Pulse Programming<sup>™</sup> algorithm. It differs from older methods in the value used for Vpp (Programming Supply Voltage) and in the width and number of the ALE/PROG pulses.

The M87C51 contains two signature bytes that can be read and used by an EPROM programming system to identify the device. The signature bytes identify the device as an M87C51 manufactured by Intel.

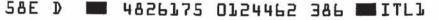

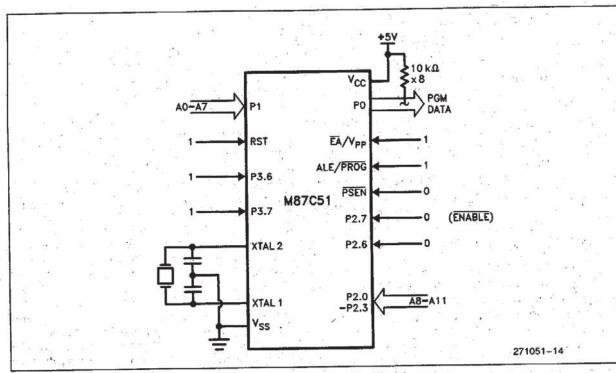

Table 2 shows the logic levels for reading the signature byte, and for programming the Program Memory, the Encryption Table, and the Lock Bits. The circuit configuration and waveforms for Quick-Pulse Programming are shown in Figures 9 and 10. Figure 11 shows the circuit configuration for normal Program Memory verification.

|                      |     |      |              |            | 1            |                 |                | · · · · |

|----------------------|-----|------|--------------|------------|--------------|-----------------|----------------|---------|

| MODE                 | RST | PSEN | ALE/<br>PROG | EA/<br>Vpp | P2.7         | P2.6            | P3.7           | P3.6    |

| Read Signature       | 1   | 0    | 1            | 1          | 0            | 0               | 0              | 0       |

| Program Code Data    | 1   | 0    | 0*           | VPP        | <b>1</b>     | 0               | . 1 :          | 1.      |

| Verify Code Data     | 1   | 0.   | 1            | 1          | 0            | 0               | 1              | 1       |

| Pgm Encryption Table | 1   | 0    | 0*           | Vpp        | 1            | 0               | 1 <b>1</b> - 2 | 0       |

| Pgm Lock Bit 1       | 1   | 0    | - 0*         | VPP        | 1 . <b>1</b> | ana <b>t</b> 2* | 1              | 1       |

| Pgm Lock Bit 2       | 1   | 0    | 0*           | VPP        | 1.1          | 2.1 %           | 0              | 0       |

#### manufactor Mode

#### NOTES:

intel.

"1" = Valid high for that pin

"0" = Valid low for that pin

$V_{PP} = 12.75V \pm 0.25V$

$V_{CC} = 5V \pm 10\%$  during programming and verification

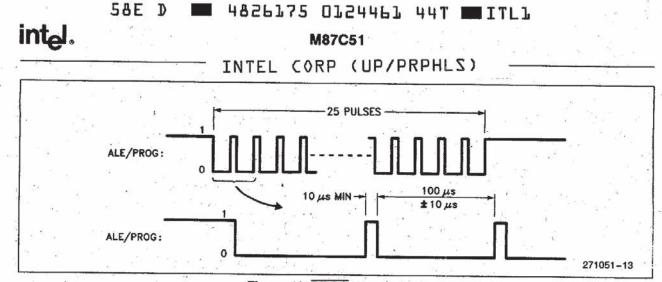

\*ALE/PROG receives 25 programming pulses while Vpp is held at 12.75V. Each programming pulse is low for 100 µs  $(\pm 10 \ \mu s)$  and high for a minimum of 10  $\mu s$ .

#### Figure 9. Programming Configuration

Figure 10. PROG Waveforms

### Quick-Pulse Programming™

The setup for Microcontroller Quick-Pulse Programming is shown in Figure 9. Note that the M87C51 is running with a 4 to 6 MHz oscillator. The reason the oscillator needs to be running is that the device is executing internal address and program data transfers.

The address of the EPROM location to be programmed is applied to Ports 1 and 2, as shown in Figure 9. The code byte to be programmed into that location is applied to Port 0. RST, PSEN, and pins of Ports 2 and 3 specified in Table 2 are held at the "Program Code Data" levels indicated in Table 2. Then ALE/PROG is pulsed low 25 times as shown in Figure 10.

To program the Encryption Table, repeat the 25pulse programming sequence for addresses 0 through 1FH, using the "Pgm Encryption Table" levels. Don't forget that after the Encryption Table is programmed, verify cycles will produce only encrypted data.

To program the Lock Bits, repeat the 25-pulse programming sequence using the "Pgm Lock Bit" levels. After one Lock Bit is programmed, further programming of the Code Memory and Encryption Table is disabled. However, the other Lock Bit can still be programmed.

Note that the  $\overline{EA}/V_{PP}$  pin must not be allowed to go above the maximum specified  $V_{PP}$  level for any amount of time. Even a narrow glitch above that voltage level can cause permanent damage to the device. The  $V_{PP}$  source should be well regulated and free of glitches and overshoot.

M87C51

INTEL CORP (UP/PRPHLS)

Figure 11. Program Verification

### **Program Verification**

intel.

If Lock Bit 2 has not been programmed, the on-chip Program Memory can be read out for program verification. The address of the Program Memory location to be read is applied to Ports 1 and 2 as shown in Figure 11. The other pins are held at the "Verify Code Data" levels indicated in Table 2. The contents of the addressed location will be emitted on Port 0. External pullups are required on Port 0 for this operation. Detailed timing specifications are shown in later sections of this data sheet.

If the Encryption Table has been programmed, the data presented at Port 0 will be the Exclusive NOR of the program byte with one of the encryption bytes. The user will have to know the Encryption Table contents in order to correctly decode the verification data. The Encryption Table itself can not be read out.

### **Reading the Signature Bytes**

The signature bytes are read by the same procedure as a normal verification of locations 030H and 031H, except that P3.6 and P3.7 need to be pulled to a logic low. The values returned are:

(030H) = 89H indicates manufactured by Intel

(031H) = 57H indicates M87C51

#### **Program/Verify Algorithms**

Any algorithm in agreement with the conditions listed in Table 2, and which satisfies the timing specifications, is suitable.

### **Erasure Characteristics**

Erasure of the EPROM begins to occur when the chip is exposed to light with wavelengths shorter than approximately 4,000 Angstroms. Since sunlight and fluorescent lighting have wavelengths in this range, exposure to these light sources over an extended time (about 1 week in sunlight, or 3 years in room level fluorescent lighting) could cause inadvertent erasure. If an application subjects the device to this type of exposure, it is suggested that an opaque label be placed over the window.

The recommended erasure procedure is exposure to ultraviolet light (at 2537 Angstroms) to an integrated dose of at least 15 W-sec/cm<sup>2</sup>. Exposing the EPROM to an ultraviolet lamp of 12,000  $\mu$ W/cm<sup>2</sup> rating for 30 minutes, at a distance of about 1 inch, should be sufficient.

Erasure leaves the array in an all 1s state.

# intel.

### 🗰 4826175 0124463 212 🗰 ITL1

M87C51

### INTEL CORP (UP/PRPHLS)

### EPROM PROGRAMMING AND VERIFICATION CHARACTERISTICS:

$T_A = 21^{\circ}C$  to 27°C,  $V_{CC} = 5V \pm 10\%$ ,  $V_{SS} = 0V$

58E D

| Symbol  | Parameter                  | Min      | Max                                           | Units   |

|---------|----------------------------|----------|-----------------------------------------------|---------|

| VPP     | Programming Supply Voltage | 12.5     | 13.0                                          | v       |

| Ipp     | Programming Supply Current |          | 50                                            | · mA    |

| 1/TCLCL | Oscillator Frequency       | 4        | 6                                             | MHz     |

| TAVGL   | Address Setup to PROG Low  | 48TCLCL  |                                               |         |

| TGHAX   | Address Hold After PROG    | 48TCLCL  |                                               |         |

| TDVGL   | Data Setup to PROG Low     | 48TCLCL  |                                               | 12 A 40 |

| TGHDX   | Data Hold After PROG       | 48TCLCL  |                                               |         |

| TEHSH   | P2.7 (ENABLE) High to VPP  | 48TCLCL  | e pri a la l | 1       |

| TSHGL   | Vpp Setup to PROG Low      | 10 .     |                                               | μs      |

| TGHSL   | VPP Hold After PROG        | 10       |                                               | μs      |

| TGLGH   | PROG Width                 | 90       | 110                                           | μs      |

| TAVQV   | Address to Data Valid      | 12<br>14 | 48TCLCL                                       |         |

| TELQV   | ENABLE Low to Data Valid   |          | 48TCLCL                                       | ÷ .     |

| TEHQZ   | Data Float After ENABLE    | 0        | 48TCLCL                                       | · · ·   |

| TGHGL   | PROG High to PROG Low      | 10       |                                               | μs      |

### **EPROM Programming and Verification Waveforms**

4