# MPC8272ADS User Guide

MPC8272ADSUG 3/2004 Rev. 0.1

Home Page: www.freescale.com email: support@freescale.com **USA/Europe or Locations Not Listed:** Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 (800) 521-6274 480-768-2130 support@freescale.com Europe, Middle East, and Africa: Freescale Halbleiter Deutschland GmbH **Technical Information Center** Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com Japan: Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064, Japan 0120 191014 +81 2666 8080 support.japan@freescale.com Asia/Pacific: Freescale Semiconductor Hong Kong Ltd. **Technical Information Center** 2 Dai King Street Tai Po Industrial Estate, Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com For Literature Requests Only: Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 (800) 441-2447 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all leaves and supersonal expension and supersonal the provided the supersonal sector of the sector of th claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Paragraph Number

Title

Page Number

#### About This Book

#### Chapter 1 Overview

| 1.1 | MPC8272ADS Specifications | 1-1 |

|-----|---------------------------|-----|

| 1.2 | MPC8272ADS Features       | 1-2 |

#### Chapter 2 Hardware Preparation and Installation

| 2.1    | Unpacking Instructions                                        | 2-1 |

|--------|---------------------------------------------------------------|-----|

| 2.2    | Hardware Preparation                                          | 2-1 |

| 2.2.1  | Setting the VDDL Supply Voltage Level                         | 2-3 |

| 2.2.2  | Setting MODCK(1:3) for PLLs Multiplication Factor—SW5 (#6-#8) | 2-3 |

| 2.2.3  | Setting Hard Reset Configuration Source—JP9                   | 2-4 |

| 2.2.4  | Setting Boot Source                                           | 2-5 |

| 2.2.5  | Setting MODCKH(0:3) for PLL Multiplication Factors            | 2-6 |

| 2.2.6  | Setting PCI_ARBITER for PCI Mode-Enabled                      | 2-6 |

| 2.2.7  | Setting PCI_DLL for PCI Mode-Enabled                          | 2-6 |

| 2.2.8  | Clock-In Source Selection                                     | 2-7 |

| 2.2.9  | FCC1 Ethernet Port Mode—MII/RMII                              | 2-7 |

| 2.2.10 | FCC2 Ethernet Port Mode—MII/RMII                              | 2-8 |

| 2.2.11 | USB Speed Selection                                           | 2-8 |

| 2.2.12 | USB Mode Selection                                            | 2-8 |

| 2.2.13 | COP/JTAG Connection                                           | 2-9 |

| 2.2.14 | Forced Parallel Port Connection                               | 2-9 |

| 2.2.15 | Power On/Off Switch                                           | 2-9 |

|        |                                                               |     |

#### Chapter 3 Installation Instructions

| Paragraph<br>Number | Title                                    | Page<br>Number |

|---------------------|------------------------------------------|----------------|

| 3.1                 | Installation Instructions                |                |

| 3.1.1               | Host-Controlled Operation                |                |

| 3.1.2               | Stand Alone Operation                    |                |

| 3.1.3               | COP/JTAG Connector—P21                   |                |

| 3.1.4               | Terminal to MPC8272ADS RS-232 Connection |                |

| 3.1.5               | 10/100-Base-T Ethernet Ports Connection  |                |

| 3.1.6               | Memory Installation                      |                |

| 3.1.6.1             | Flash Memory SIMM Installation           |                |

### Chapter 4 Operating Instructions

| 4.1    | Controls and Indicators 4-1                       |

|--------|---------------------------------------------------|

| 4.1.1  | Power-On RESET Switch—SW3                         |

| 4.1.2  | ABORT Switch—SW6                                  |

| 4.1.3  | Soft Reset Switch—SW7                             |

| 4.1.4  | Hard Reset Switches—SW6 & SW7                     |

| 4.1.5  | Reset Configuration Switch—SW2                    |

| 4.1.6  | Software Options Switch—SW1                       |

| 4.1.7  | 3IDDL Measurement—JP1                             |

| 4.1.8  | Thermal Sense Connector—JP7                       |

| 4.1.9  | IDDH Measurement—JP14                             |

| 4.1.10 | V <sub>PP</sub> Source Selector—JP4               |

| 4.1.11 | GND Bridges                                       |

| 4.1.12 | Power O.K. Indicator—LD13                         |

| 4.1.13 | 12V Indicator—LD14                                |

| 4.1.14 | UTOPIA Multi PHY Indicator—LD28 4-4               |

| 4.1.15 | 5-V Indicator—LD15                                |

| 4.1.16 | 3.3-V Indicator—LD16                              |

| 4.1.17 | USB Power Indicator—LD5                           |

| 4.1.18 | -12V Indicator—LD17                               |

| 4.1.19 | RUN Indicator—LD18                                |

| 4.1.20 | ATM ON Indicator—LD19 4-5                         |

| 4.1.21 | Fast Ethernet Port 1 Enabled—LD20                 |

| 4.1.22 | Fast Ethernet Port 2 Enabled—LD22 4-5             |

| 4.1.23 | RS232 Port 1 ON—LD23                              |

| 4.1.24 | Fast Ethernet Port 1 Full Duplex Indicator—LD14-5 |

| 4.1.25 | RS232 Port 2 ON—LD24                              |

| 4.1.26 | Fast Ethernet Port 1 100Base-Tx Indicator—LD2     |

| 4.1.27 | Ethernet Port 1 Tx/Rx Indicator—LD3 4-6           |

| 4.1.28 | General Purpose Led 2 Indicator—LD26              |

| 4.1.29 | Ethernet Port 1 LINK Indicator—LD4                |

| Paragraph<br>Number | Title                                          | Page<br>Number |

|---------------------|------------------------------------------------|----------------|

| 4.1.30              | Fast Ethernet Port 2 Full Duplex Indicator—LD6 |                |

| 4.1.31              | General Purpose Led 1 Indicator—LD25           |                |

| 4.1.32              | Fast Ethernet Port 2 100Base-Tx Indicator—LD7  |                |

| 4.1.33              | USB Enabled Indicator—LD21                     |                |

| 4.1.34              | Ethernet Port 2 LINK Indicator—LD9             |                |

| 4.1.35              | Ethernet Port 2 Tx/Rx Indicator—LD8            |                |

| 4.1.36              | V <sub>DDL</sub> Indication—LD27               |                |

| 4.1.37              | Parallel Port connection—LD10                  |                |

| 4.1.38              | External Debugger Connection Indicator—LD11    |                |

#### Chapter 5 Module Design

| 5.1     | Reset and Reset Configuration |

|---------|-------------------------------|

| 5.1.1   | Power-On Reset                |

| 5.1.2   | Power-On Reset Configuration  |

| 5.1.3   | Hard Reset                    |

| 5.1.3.1 | COP/JTAG Port Hard Reset      |

| 5.1.3.2 | Manual Hard Reset             |

| 5.1.3.3 | Internal Sources Hard Reset   |

| 5.1.3.4 | Hard Reset Configuration      |

| 5.1.4   | Soft Reset                    |

| 5.1.4.1 | COP/JTAG Port Soft Reset      |

| 5.1.4.2 | Manual Soft Reset             |

| 5.1.4.3 | Internal Sources Soft Reset   |

| 5.1.5   | PCI Bus Reset                 |

| 5.1.6   | Local Interrupter             |

| 5.1.6.1 | ABORT Interrupt               |

| 5.1.6.2 | ATM UNI Interrupt             |

| 5.1.7   | Fast Ethernet PHY Interrupt   |

| 5.1.8   | PCI Interrupt                 |

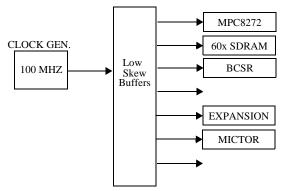

| 5.2     | Clock Generator               |

| 5.2.1   | MPC8272 Clock                 |

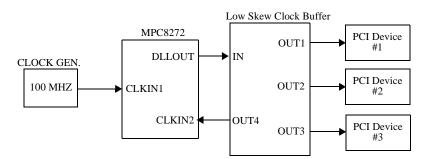

| 5.2.2   | PCI Clock                     |

| 5.3     | Bus Configuration             |

| 5.3.1   | Single PowerQUICC II Mode5-14 |

| 5.4     | Buffering                     |

| 5.5     | Chip-Select Generator         |

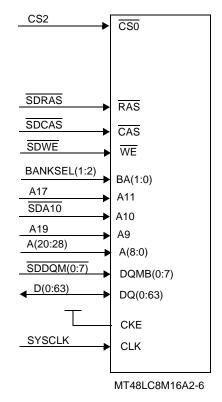

| 5.6     | Synchronous DRAM (60X Bus)    |

| 5.6.1   | SDRAM Programming             |

| 5.6.2   | SDRAM Refresh                 |

| 5.7     | Flash Memory SIMM 5-17        |

| 5.7.1    | Flash Programming Voltage                             |  |

|----------|-------------------------------------------------------|--|

| 5.8      | E2PROM Memory                                         |  |

| 5.9      | PCI Bus                                               |  |

| 5.10     | Communication Ports                                   |  |

| 5.10.1   | ATM Port                                              |  |

| 5.10.2   | 100/10 Base T Ports                                   |  |

| 5.10.2.1 | DM9161 Control                                        |  |

| 5.10.3   | RS232 Ports                                           |  |

| 5.10.3.1 | RS-232 Ports' Signal Description                      |  |

| 5.10.4   | USB Port                                              |  |

| 5.10.5   | PC Parallel Port                                      |  |

| 5.11     | Board Control and Status Register - BCSR              |  |

| 5.11.1   | BCSR0 Board Control—Status Register 0                 |  |

| 5.11.2   | BCSR1 Board Control—Status Register 1                 |  |

| 5.11.3   | BCSR2 Board Control—Status Register 2                 |  |

| 5.11.4   | BCSR3 Board Control - Status Register 3               |  |

| 5.11.5   | BCSR4 Board Control—Status Register 4                 |  |

| 5.11.6   | BCSR5 and BCSR7 Board Control—Status Register 3 and 5 |  |

| 5.12     | COP/JTAG Port                                         |  |

|          |                                                       |  |

### Chapter 6 Memory Map

| 6.1   | Overview                                  |

|-------|-------------------------------------------|

| 6.2   | PowerQUICC II Register Programming6-5     |

| 6.2.1 | System Initialization                     |

| 6.2.2 | Memory Controller Register Programming6-7 |

#### Chapter 7 Physical Properties

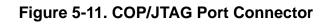

| 7.1     | Power Supply7-1               |

|---------|-------------------------------|

| 7.1.1   | 5-V Rail                      |

| 7.1.2   | 3.3-V Rail                    |

| 7.1.3   | 5-V Standby Rail              |

| 7.1.4   | V <sub>DDH</sub> Rail         |

| 7.1.4.1 | V <sub>DDI</sub> Bus          |

| 7.1.4.2 | 12-V Rail                     |

| 7.1.4.3 | -12-V Rail                    |

| 7.2     | Connectors                    |

| 7.2.1   | ATX Power Connector           |

| 7.2.2   | Fast Ethernet Port Connectors |

|         |                               |

| Paragraph<br>Number | Title                                        | Page<br>Number |

|---------------------|----------------------------------------------|----------------|

| 7.2.3               | ATM 155 Port Connection                      |                |

| 7.2.4               | RS232 Port Connector                         |                |

| 7.2.5               | CPM Expansion Connector                      |                |

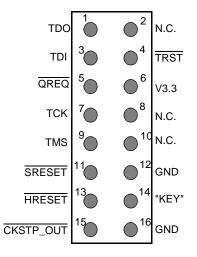

| 7.2.6               | COP/JTAG Port Connector                      |                |

| 7.2.7               | Logic Analyzer Connectors                    |                |

| 7.2.8               | Mach's In System Programming (ISP) Connector |                |

| 7.2.9               | PCI Connectors                               |                |

| 7.2.10              | System Expansion Connector                   |                |

| 7.2.11              | USB Connector                                |                |

| 7.2.12              | Parallel Port Connector                      |                |

| 7.3                 | PCB Layout                                   |                |

### Chapter 8 Support

| 8.1    | Interconnect Signals                               | 8-1    |

|--------|----------------------------------------------------|--------|

| 8.1.1  | P13—RS232 Ports 1 and 2 Connectors                 | 8-1    |

| 8.1.2  | P10 and P23 100/10 Base-T Ethernet Port Connector  | 8-2    |

| 8.1.3  | P21—COP/JTAG Connector                             | 8-2    |

| 8.1.4  | P1—CPM Expansion Connector                         | 8-4    |

| 8.1.5  | P9, P11, P14, P22, P17, P5, P20, P18, P15, P24,P12 |        |

|        | Logic Analyzer MICTOR Connectors                   |        |

| 8.1.6  | P26, P28, P29—PCI Connectors                       | 8-13   |

| 8.1.7  | P31 - ATX Power Supply Connector                   |        |

| 8.1.8  | P3,P4,P25—Mach/Lattice ISP Connector               | . 8-16 |

| 8.1.9  | P2—System Expansion Connector                      |        |

| 8.1.10 | P16, P19—USB Connectors                            | 8-22   |

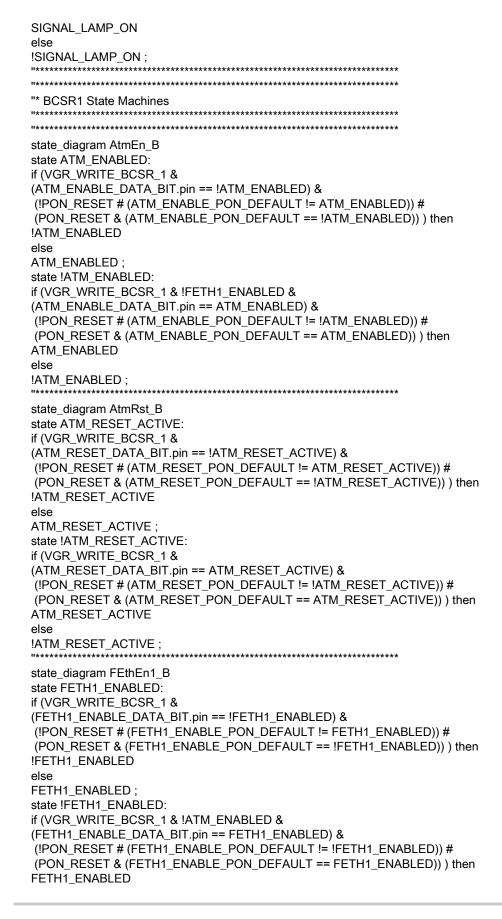

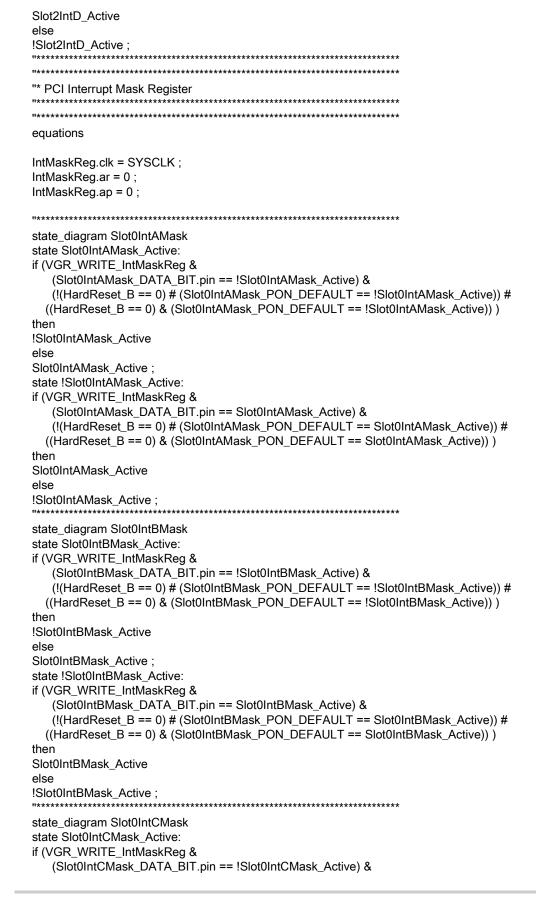

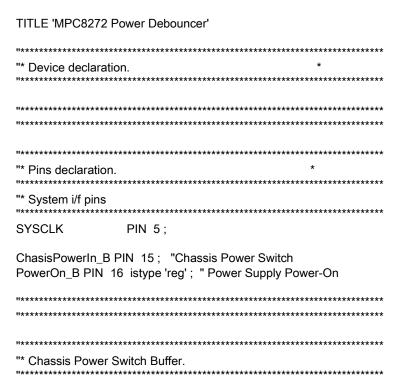

| 8.2    | Programmable Logic Equations                       | 8-23   |

| 8.2.1  | U3—BCSR Code                                       |        |

| 8.2.2  | U41—Power switch debounce                          | 8-53   |

### Appendix A Revision History

#### Index

Paragraph Number

Title

Page Number

# Figures

# Page Number

| Figure<br>Number | Title                                              | Page<br>Number |

|------------------|----------------------------------------------------|----------------|

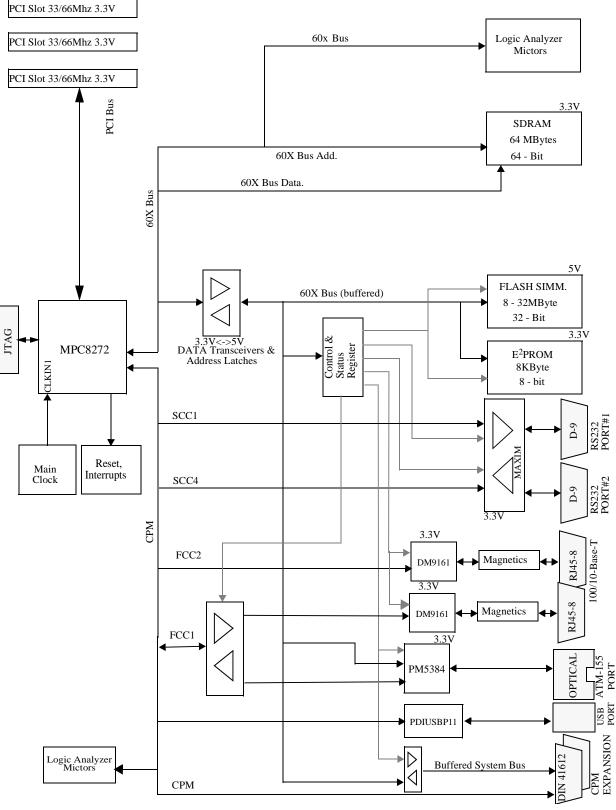

| 1-1              | MPC8272ADS Block Diagram                           |                |

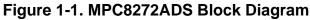

| 2-1              | MPC8272ADS Top Side Part Location Diagram          |                |

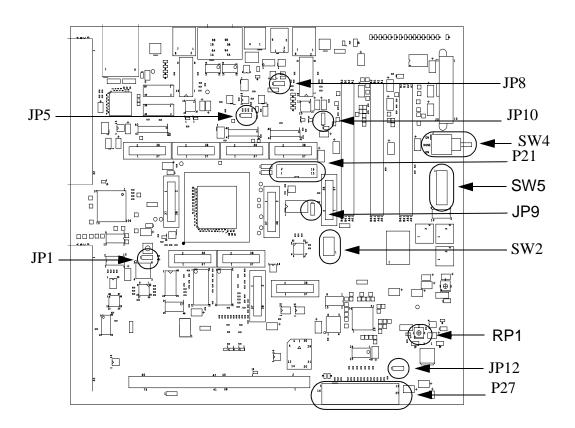

| 2-2              | V <sub>DDL</sub> Trimmer—RP1                       |                |

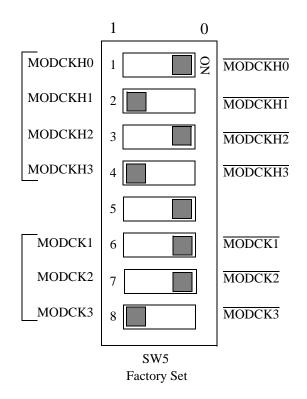

| 2-3              | SW5 Description                                    |                |

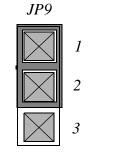

| 2-4              | Hard Reset Configuration Source Selection—JP9      |                |

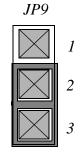

| 2-5              | SW2 Description                                    |                |

| 2-6              | Clock Source Selection                             |                |

| 2-7              | FCC1 Ethernet Mode Selection                       |                |

| 2-8              | FCC2 Ethernet Mode Selection                       |                |

| 2-9              | USB Mode Selection                                 |                |

| 2-10             | Forced Parallel Port Connection                    |                |

| 3-1              | Host-Controlled Operation Scheme—Command Converter |                |

| 3-2              | Host Controlled Operation Scheme—Parallel Port     |                |

| 3-3              | Stand Alone Configuration                          |                |

| 3-4              | P21—COP/JTAG Port Connector                        |                |

| 3-5              | P1A/P1B—RS232 Serial Port Connector                |                |

| 3-6              | Flash Memory SIMM Insertion                        |                |

| 4-1              | SW1 Description                                    |                |

| 4-2              | JP7 Therm Connector                                |                |

| 4-3              | JP13 V <sub>PP</sub> Source Selection              |                |

| 5-1              | PCI Host Configuration Registers                   |                |

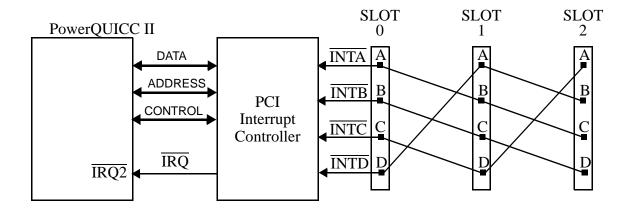

| 5-2              | PCI Interrupt Routing Scheme                       | 5-10           |

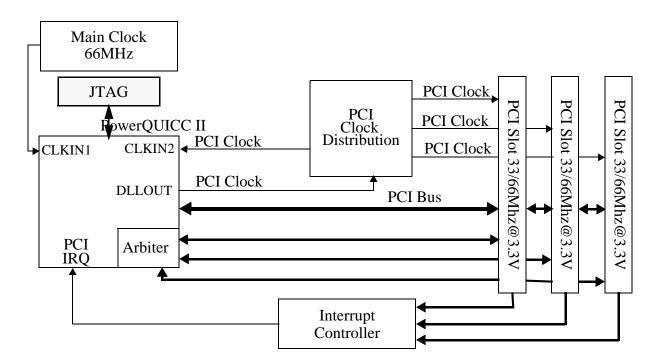

| 5-3              | Main Clock Generator Scheme                        |                |

| 5-4              | PCI Clock Generator Scheme                         | 5-14           |

| 5-5              | 60x SDRAM Connection Scheme                        | 5-16           |

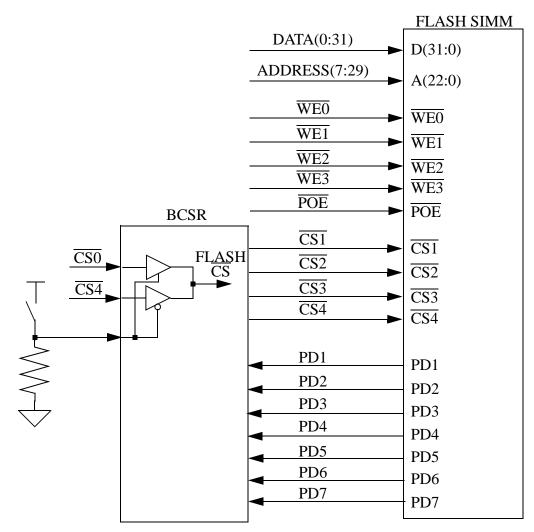

| 5-6              | FLASH SIMM Connection Scheme                       | 5-18           |

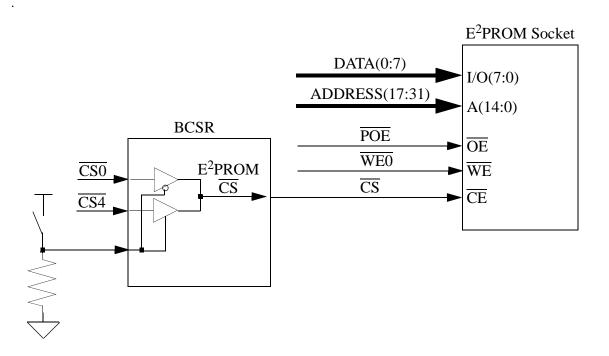

| 5-7              | E2PROM Connection Scheme                           | 5-20           |

| 5-8              | PCI Bus Scheme                                     |                |

| 5-9              | RS232 Serial Ports Connector                       |                |

| 5-10             | Debug Station Connection Schemes                   |                |

| 5-11             | COP/JTAG Port Connector                            |                |

| 7-1              | MPC8272ADS Power Scheme                            |                |

Figures

Table Number

# Tables

Title

#### Page Number

| i    | Acronyms and Abbreviated Terms xvii                               |

|------|-------------------------------------------------------------------|

| 1-1  | MPC8272ADS specifications 1-1                                     |

| 2-1  | MODCK(1:3) Encoding                                               |

| 5-1  | BCSR/FLASH Hard Reset Configuration Word                          |

| 5-2  | E2PROM Hard Reset Configuration Word                              |

| 5-3  | PCI Interrupt Register Description                                |

| 5-4  | PCI Interrupt Mask Register Description                           |

| 5-5  | MPC8272ADS Chip Select Assignments                                |

| 5-6  | 100 MHz SDRAM Mode Register Programming                           |

| 5-7  | BCSR0 Description                                                 |

| 5-8  | BCSR1 Description                                                 |

| 5-9  | BCSR2 Description                                                 |

| 5-10 | FLASH Presence Detect (7:5) Encoding                              |

| 5-11 | FLASH Presence Detect (4:1) Encoding                              |

| 5-12 | EXTOOLI(0:3) Assignment                                           |

| 5-13 | PowerQUICC II Board Version Encoding                              |

| 5-14 | PowerQUICC II Board Revision Encoding                             |

| 5-15 | External Tool Revision Encoding                                   |

| 5-16 | BCSR3 Description                                                 |

| 5-18 | PCI Board Present Signal Definitions                              |

| 5-17 | BCSR4 Description                                                 |

| 5-19 | BCSR5 to BCSR7 Description                                        |

| 5-20 | COP/JTAG Port Signals Description                                 |

| 6-1  | MPC8272ADS Memory Map—Flash (or BCSR) as Boot Device              |

| 6-2  | MPC8272ADS Memory Map—E2PROM as Boot Device                       |

| 6-3  | BCSR/Flash Power On Reset Configuration                           |

| 6-4  | E2PROM Power On Reset Configuration                               |

| 6-5  | SIU Register Programming                                          |

| 6-6  | Memory Controller Initialization For 100MHz—Flash as Boot Device  |

| 6-7  | Memory Controller Initialization For 100MHz—E2PROM as Boot Device |

| 6-8  | Memory Controller Initialization For 100MHz                       |

| 7-1  | Expansion Connectors Maximum Current Consumption                  |

| 7-2  | Maximum Power Consumption Per Add-In Card                         |

| 8-1  | P13 Connector                                                     |

| 8-2  | P10,P23 100/10 Base-T Ethernet Connector                          |

# Tables

| Table<br>Number | Title                          | Page<br>Number |

|-----------------|--------------------------------|----------------|

| 8-3             | P16—COP/JTAG Connector         |                |

| 8-4             | P1—CPM Expansion Connector     |                |

| 8-5             | P26, P28, P29—PCI Connectors   |                |

| 8-6             | P31—ATX Power Supply Connector |                |

| 8-7             | P3—Lattice ISP Connector       |                |

| 8-8             | P2—System Expansion Connector  |                |

| 8-9             | P16, P19—USB Connectors        |                |

# **About This Book**

The MPC8272 is a versatile communications processor that integrates on one chip a high-performance PowerPC<sup>TM</sup> RISC microprocessor, a very flexible system integration unit, encryption hardware, and many communications peripheral controllers that can be used in a variety of applications, particularly in communications and networking systems.

The primary objective of this manual is to describe the functionality of the MPC8272ADS board. It contains operational, functional and general information about the MPC8272ADS. This board is meant to serve as a platform for software and hardware development for the MPC8272 processor in a TEPBGA package (516 Pins in Hip7). The high-performance MPC8272 PowerQUICC II<sup>TM</sup> processor family contains a PowerPC<sup>TM</sup> core and addresses the needs of a wide variety of networking and communications applications.

Using its on-board resources and a debugger, a developer can download code, run it, set breakpoints, display memory and registers and connect proprietary hardware using the expansion connectors, to be incorporated into a desired system with the MPC8272 processor.

This board could also be used as a demonstration tool (for example, application software may be programmed either on or off-board into its Flash memory and run in exhibitions).

Although this book describes aspects regarding the PowerPC architecture that are critical for understanding the MPC8272 core, it does not contain a complete description of the architecture. Where additional information might help the reader, references are made to *Programming Environments Manual for 32-Bit Implementation of the PowerPC Architecture, REV 2.* Refer to "Architecture Documentation" for ordering information.

The information is subject to change without notice, as described in the disclaimers on the title page of this book. As with any technical documentation, it is the reader's responsibility to use the most recent version of the documentation. Before using this manual, determine whether it is the latest revision and the existence of errata or addenda. To locate any published errata or updates for this document, refer to the worldwide web at www.motorola.com/semiconductors.

# Audience

This manual is intended for system software and hardware developers and applications programmers who want to develop products using the MPC8272 integrated processor. Readers should understand the following topics:

- Computer networking

- Basic principles of RISC processing

- Details of the PowerPC architecture

# Organization

The following list describes the major sections of this manual:

- Chapter 1, "Overview," provides a high-level description of the MPC8272ADS, describing general operation, basic features, and a block diagram.

- Chapter 2, "Hardware Preparation and Installation," provides unpacking instructions and information about setting various modes, switches, and other configuration on the MPC8272ADS.

- Chapter 3, "Installation Instructions," provides information about host-controlled and stand alone operation, memory installation, and connection setup.

- Chapter 4, "Operating Instructions," provides information about controls and indicators for the MPC8272ADS.

- Chapter 5, "Module Design," provides information about MPC8272ADS reset and reset configuration, the clock generator, bus configuration, buffering, the chip-select generator, synchronous DRAM, Flash memory, and E<sup>2</sup>PROM memory.

- Chapter 6, "Memory Map," discusses PowerQUICC II register programming.

- Chapter 7, "Physical Properties," provides information about the power supply, connectors, and PCB layout.

- Chapter 8, "Support," provides information about interconnect signals and programmable logic equations.

- Appendix A, "Revision History," provides information about the revision history of this document.

The book also contains an index.

# **Suggested Reading**

This section lists additional reading that provides background for the information in this manual as well as general information about the PowerPC architecture.

### **MPC8272** Documentation

Supporting documentation for the MPC8272 can be accessed through the world-wide web at www.motorola.com/semiconductors. This documentation includes technical specifications, reference materials, and detailed applications notes.

# Architecture Documentation

Architecture documentation is organized in the following types of documents:

- Manuals—These books provide details about individual implementations of the PowerPC architecture and are intended to be used with the *Programming Environments Manual*. These include the *G2 Core Reference Manual* (Motorola order #: G2CORERM).

- Programming environments manuals—These books provide information about resources defined by the PowerPC architecture that are common to processors that implement the PowerPC architecture. The two versions include one that describes the functionality of the combined 32- and 64-bit architecture models and one that describes only the 32-bit model. The MPC8280 adheres to the 32-bit architecture definition.

- Programming Environments for 32-Bit Implementations of the PowerPC Architecture (Motorola order #: MPCFPE32B)

- *The Programmer's Pocket Reference Guide for the PowerPC Architecture*: MPCPRGREF/D—This guide provides an overview of registers, instructions, and exceptions for 32-bit implementations.

- Application notes—These short documents contain useful information about specific design issues useful to programmers and engineers working with Motorola's processors.

For a current list of documentation, refer to www.motorola.com/semiconductors.

# **Related Documentation**

Motorola documentation is available from the sources listed on the back cover of this manual. The document order numbers are included in parentheses for ease in ordering:

- *Programming Environments Manual for 32-Bit Implementations of the PowerPC Architecture*, which describes resources defined by the PowerPC architecture.

- The *G2 Core Reference Manual*, which describes features for the embedded G2 processor core, a derivative of the original MPC603e PowerPC microprocessor design.

- The *Tsi107<sup>TM</sup> PowerPC Host Bridge User Manual*, published by Tundra Semiconductor Corporation (Tundra). See the Tundra website at www.tundra.com for more information.

- User's manuals—These books provide details about individual implementations and are intended for use with the *Programming Environments Manual*.

- Addenda/errata to user's manuals—Because some processors have follow-on parts, an addendum describes the additional features and functionality changes. These addenda are intended for use with the corresponding user's manuals.

- Hardware specifications—Hardware specifications provide specific data about bus timing, signal behavior, and AC, DC, and thermal characteristics, as well as other design considerations. Separate hardware specifications are provided for each part described in this book.

- Technical summaries—Each device has a technical summary that provides an overview of its features. This document is roughly equivalent to the overview (Chapter 1) of a user's manual for implementation.

- *The Programmer's Reference Guide for the PowerPC Architecture*—This concise reference includes the register summary, memory control model, exception vectors, and the PowerPC instruction set.

- *The Programmer's Pocket Reference Guide for the PowerPC Architecture*—This foldout card provides an overview of PowerPC registers, instructions, and exceptions for 32-bit implementations.

- Application notes—These useful short documents address specific design issues for programmers and engineers who work with Motorola processors.

Additional literature is published as new processors become available. For a current list of documentation, refer to http://www.motorola.com/semiconductors.

# Conventions

This document uses the following notational conventions:

| cleared/set      | The words 'set' and 'cleared' are reserved for use with bits and fields, but not signals. A bit or field is <i>cleared</i> when it contains the value zero. A bit is <i>set</i> when it contains the value one. However, a field can be set to a value that contains zeros and ones. |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| asserted/negated | The words 'asserted' and 'negated' are reserved for use with signals and not bits.                                                                                                                                                                                                   |  |

| mnemonics        | Instruction mnemonics are shown in lowercase bold.                                                                                                                                                                                                                                   |  |

| italics          | Italics indicate variable command parameters, for example, <b>bcctr</b> <i>x</i> .                                                                                                                                                                                                   |  |

|                  | Book titles in text are set in italics.                                                                                                                                                                                                                                              |  |

|                  | Internal signals are set in italics, for example, $\overline{qual BG}$ .                                                                                                                                                                                                             |  |

| 0x0              | Prefix to denote hexadecimal number                                                                                                                                                                                                                                                  |  |

| 0b0              | Prefix to denote binary number                                                                                                                                                                                                                                                       |  |

| rA, rB        | Instruction syntax that identifies a source GPR                                                                                                                                                               |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rD            | Instruction syntax that identifies a destination GPR                                                                                                                                                          |

| frA, frB, frC | Instruction syntax that identifies a source FPR                                                                                                                                                               |

| frD           | Instruction syntax that identifies a destination FPR                                                                                                                                                          |

| REG[FIELD]    | Abbreviations for registers are shown in uppercase text. Specific bits, fields, or ranges appear in brackets. For example, MSR[LE] refers to the little-endian mode enable bit in the machine state register. |

| X             | In some contexts, such as signal encodings, an unitalicized x indicates a 'don't care' logic.                                                                                                                 |

| x             | An italicized x indicates an alphanumeric variable.                                                                                                                                                           |

| n             | An italicized <i>n</i> indicates an numeric variable.                                                                                                                                                         |

| -             | NOT logical operator                                                                                                                                                                                          |

| &             | AND logical operator                                                                                                                                                                                          |

|               | OR logical operator                                                                                                                                                                                           |

| 0000          | Indicates reserved bits or bit fields in a register. Although these bits can be written to as ones or zeros, they are always read as zeros.                                                                   |

# **Acronyms and Abbreviations**

Table i contains acronyms and abbreviations that appear in this document.

#### Table i. Acronyms and Abbreviated Terms

| MPC8272ADS | ADS board For MPC8272 processor          |

|------------|------------------------------------------|

| PQ2        | PowerQUICC II                            |

| MPC8275    | PowerQUICC II Hip7 in TEPBGA package     |

| VOYAGER    | MPC8260 - PowerQUICC 2                   |

| PPC        | PowerPC                                  |

| PCI        | Peripheral components interconnect       |

| USB        | Universal serial bus                     |

| СРМ        | Communication processor module           |

| SDRAM      | Synchronous dynamic random access memory |

| VADS       | Voyager application development system   |

| Kbyte      | 1024 bytes                               |

| LSB        | Least significant byte                   |

| lsb        | Least significant bit                    |

| Mbyte      | 1048576 bytes                            |

### Table i. Acronyms and Abbreviated Terms (continued)

| MPC8272ADS | ADS board For MPC8272 processor               |

|------------|-----------------------------------------------|

| DIMM       | Dual in-line memory module                    |

| SIMM       | Single in-line memory module                  |

| TBD        | To be defined                                 |

| UPM        | User programmable machine                     |

| EVB        | Evaluation board                              |

| GPCM       | General purpose chip-select machine           |

| GPL        | General purpose line                          |

| BCSR       | Board control and status register             |

| FLASH      | Non volatile reprogrammable memory.           |

| ZIF        | Zero input force                              |

| BGA        | Ball grid array                               |

| ADI        | Application development interface.            |

| COP        | Common on-chip processor                      |

| SAR        | Segmentation And reassembly                   |

| UTOPIA     | Universal test & operations interface for ATM |

# Chapter 1 Overview

The primary objective of this manual is to describe the functionality of the MPC8272ADS board. It contains operational, functional and general information about the MPC8272ADS. This board is meant to serve as a platform for software and hardware development for the MPC8272 processor in a TEPBGA package (516 Pins in Hip7). The high-performance MPC8272 PowerQUICC II<sup>TM</sup> processor family contains a PowerPC<sup>TM</sup> core and addresses the needs of a wide variety of networking and communications applications.

Using its on-board resources and a debugger, a developer can download code, run it, set breakpoints, display memory and registers and connect proprietary hardware using the expansion connectors, to be incorporated into a desired system with the MPC8272 processor.

This board could also be used as a demonstration tool (for example, application software may be programmed either on- or off-board into its Flash memory and run in exhibitions).

# 1.1 MPC8272ADS Specifications

Table 1-1 shows the MPC8272ADS specifications.

| CHARACTERISTICS                                                                    | SPECIFICATIONS                                                                                                                  |

|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Power requirements (no other boards attached)                                      | +5Vdc @ TBD A (Typ.), TBD A (Max.)<br>+3.3Vdc @ TBD A (Typ.), TBD A (Max.)<br>+12Vdc - @TBD A Max.<br>-12Vdc - @TBD A Max.      |

| Microprocessor                                                                     | MPC8272 running @ up to 100 MHz bus clock frequency.                                                                            |

| Addressing<br>Total address range on PPC bus:<br>Total address range on Local bus: | 4 GBytes (32 address lines)<br>256 KBytes External (18 address lines)<br>4 GBytes Internal (32 address lines internal decoding) |

| Flash Memory SIMM (PPC bus)<br>Synchronous Dynamic RAM DIMM (PPC bus)              | 8 MByte, 32 bits wide expandable to 32 MBytes 64 MByte, 64 bits wide                                                            |

Table 1-1. MPC8272ADS specifications

| CHARACTERISTICS                             | SPECIFICATIONS                                 |

|---------------------------------------------|------------------------------------------------|

| Operating temperature                       | 0°C - 70°C (room temperature)                  |

| Storage temperature                         | -25°C to 85°C                                  |

| Relative humidity                           | 5% to 90% (non-condensing)                     |

| Dimensions:<br>Length<br>Width<br>Thickness | 12" (305 mm)<br>9" (229 mm)<br>0.063" (1.6 mm) |

#### Table 1-1. MPC8272ADS specifications (continued)

# 1.2 MPC8272ADS Features

This section summarizes the features of the MPC8272ADS. Major features are the following:

- Supports MPC8272 (Hip7) processor

- 64-bit PowerQUICC II Communication Processor, running at up to 100MHz external bus frequency

- 64-MByte synchronous DRAM (soldered on-board), residing on 60X bus (PBI mode), controlled by SDRAM machine. Hard reset is applied by depressing BOTH Soft Reset & ABORT buttons.

- 8-MByte, 80-pin Flash SIMM, buffered from 60X bus. Supports up to 32 MBytes, controlled by GPCM, 5V/12V Programmable, with automatic Flash SIMM identification, using BCSR. Supports both On and OFF SIMM Flash reset.

- 5V/12V VPP (in-circuit programming voltage) for Flash SIMM—jumper selectable

- 64 KBytes  $E^2$ PROM, buffered from the 60x bus and controlled by the GPCM

- Board control and status register—BCSR, controlling boards' operation

- On-board COP/JTAG connector

- On-board logic to support direct connection to standard parallel port (EPP/SPP modes) in desktop PC for debug purposes using MetroWerks CodeWarrior tools

- Power-on reset option using JTAG

- Programmable power-on reset and hard-reset configuration using E<sup>2</sup>PROM or Flash memory for the PowerQUICC II core

- PCI local bus is PCI Standard 2.2-compliant

- 3 PCI slots are available to host up to three masters/targets cards at 3.3 V only. Arbitration is supported by the on-chip arbiter.

- PCI bus supports 25–66 MHz at 3.3 V devices (determined by the user).

- Simple generic interrupt controller to handle the PCI interrupts (4 in each PCI slot)

- Module enable indications for all on-board modules

- High-density (MICTOR) logic analyzer connectors, carrying all 60x, PCI, and CPM signals, for fast logic analyzer connection

- 155 Mbps ATM UNI on FCC1 with optical I/F, connected to the PowerQUICC II via UTOPIA Level 2 I/F supporting 8 bit in single/multi PHY, using the PMC-SIERA 5384

- Two 100/10-Base-T Ports on FCC1 and FCC2 with T.P. I/F, MII/RMII controlled, using Davicom DM9161

- USB Port, USB 1.1 Standard Compliant, using Philips PDIUSBP11 USB transceiver. USB Port is with shutdown option and speed selectable BCSR controlled. Host/slave selectable. Supports USB type-A and type-B connectors.

- Dual RS232 port residing on SCC1 & SCC4

- Module disable (that is, low-power mode) option for all communication transceivers —BCSR controlled, enabling use of communication ports, off-board by using the expansion connectors

- Dedicated PowerQUICC II communication ports expansion connectors for convenient tools' connection, carrying also necessary bus signals, for transceivers' M/P I/F connection. Use is done with 2 X 128 pin DIN 41612 receptacle connectors.

- External tools' identification & status read capability, via BCSR

- Separate power-on reset push button, soft / hard reset push button, and ABORT push button

- ATX power supply

- 1.3V to 1.7V (Hip7) internal logic operation voltage

- Software option switch provides 8 S/W options using BCSR.

Figure 1-1 shows the MPC8272ADS block diagram.

# Chapter 2 Hardware Preparation and Installation

This chapter provides unpacking instructions and hardware preparation for the MPC8272ADS.

# 2.1 Unpacking Instructions

If the shipping carton is damaged upon receipt, request that the carrier's agent is present during unpacking and inspection of equipment. Unpack the equipment from shipping carton. and refer to the packing list to verify that all items are included. Save the packing material for storing and reshipping the equipment.

#### NOTE

Avoid touching areas of integrated circuitry. Static discharge can damage the circuits of this product.

# 2.2 Hardware Preparation

To ensure that the desired configuration is selected to produce proper operation of the MPC8272ADS board, changes of the dip-switch settings may be required before installation. The location of the switches, indicators, dip-switches, and connectors is illustrated in Figure 2-1. Boards are factory-tested and shipped with dip-switch settings as described in the following tested graphs. Parameters can be changed for the following conditions:

The PowerQUICC II internal logic supply level within range  $(V_{DDL})$  using potentiometer RP1.

- PowerQUICC II's MODCK(1:3). Determining core's and CPM's PLLs multiplication factor using dip-switches SW5(#6 #8)

- PowerQUICC II's hard reset configuration word source BCSR or memory (FLASH/EEPROM) using jumper JP9

- PowerQUICC II's boot code source EEPROM/FLASH using dip-switch SW2(1)

- PowerQUICC II's MODCKH(0:3) using SW5(1-4)

- PowerQUICC II's PCI\_ARBITER using SW2(2)

- PowerQUICC II's PCI\_DLL using SW2(3)

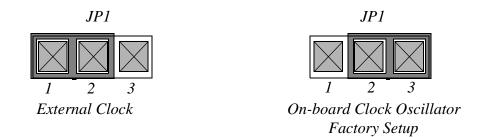

- Clock-in source—external or on-board clock oscillator—JP1

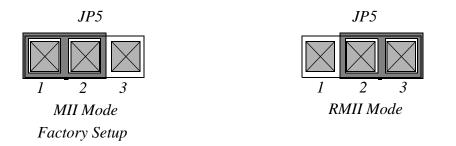

- FCC1 and FCC2 MII/RMII modes—using jumpers JP5 and JP10, respectively

- USB speed (12Mbits/s or 1.5Mbits/s) software controlled in BCSR

- USB host/slave mode—using jumper JP8

- PowerQUICC II's COP/JTAG connection—COP/JTAG connector (P21) or direct connection to PC parallel port (P27). Selected automatically by connecting parallel cable.

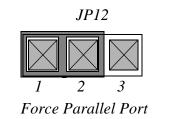

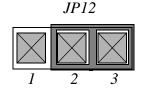

- Force PC parallel port (P27) connection using jumper JP12

- ATX power supply on/off switch using SW4

Figure 2-1. MPC8272ADS Top Side Part Location Diagram

# 2.2.1 Setting the VDDL Supply Voltage Level

The level of  $V_{DDL}$  is tuned using RP1 and is in the range of 1.3 V to 1.7 V.  $V_{DDL}$  may be measured upon JP13, using a DVM or any other high-input impedance voltage measuring device.

$V_{DDL}$  level is factory-set at the mid-range, but may be changed using RP1. Rotating RP1 CCW increases  $V_{DDL}$  voltage up to range-high. Rotating it clockwise decreases  $V_{DDL}$  down to range-low. LD27 provides visual indication for  $V_{DDL}$  level. It illuminates brighter with the rise of  $V_{DDL}$ .  $V_{DDL}$  changes Vs. RP1's rotation direction is shown in Figure 2-2.

Figure 2-2. V<sub>DDL</sub> Trimmer—RP1

### 2.2.2 Setting MODCK(1:3) for PLLs Multiplication Factor—SW5 (#6–#8)

After 1K cycles and negation of the power-on reset signal, the MPC8272 samples the seven MODCK lines—the lower 3 on MODCK(1-3) and the upper four—MODCKH(0:3) field to establish the multiplication factors of the CPM's and core's PLLs. The levels on MODCK(1:3) lines are set using SW5 (see Figure 2-3), switches #6–#8. When an individual switch is at the OFF position, its associated MODCK line is pulled-high ('1'). When at the ON position, the associated MODCK is pulled-down ('0'). SW5 is shown in Figure 2-3, while the various combinations for SW5 (#6 - #8) and their associated MODCK(1:3) values are shown in Table 2-1.

| MODCK(1:3) | Switch 6 | Switch 7 | Switch 8 |

|------------|----------|----------|----------|

| 0          | ON       | ON       | ON       |

| 1          | ON       | ON       | OFF      |

| 2          | ON       | OFF      | ON       |

| 3          | ON       | OFF      | OFF      |

| 4          | OFF      | ON       | ON       |

| 5          | OFF      | ON       | OFF      |

| 6          | OFF      | OFF      | ON       |

| 7          | OFF      | OFF      | OFF      |

| Table 2-1 | . MODCK(1:3) | Encoding |

|-----------|--------------|----------|

|-----------|--------------|----------|

### 2.2.3 Setting Hard Reset Configuration Source—JP9

The boot sequence that starts when  $\overline{\text{HRESET}}$  is asserted can be from two sources:

- BCSR (default hard-reset configuration word—<u>CS0</u> is assumed to be assigned to the FLASH)

- Memories (FLASH/EEPROM—user controlled hard-reset configuration word)

When a jumper is placed between positions 1–2 of JP9, the hard reset configuration source is a memory (FLASH/EEPROM) as configured by switch SW6-1. When a jumper is set between positions 2–3 of JP7, the hard reset configuration source is the BCSR. See Figure 2-4.

FLASH/EEPROM is hard reset configuration Source

BCSR is hard reset configuration Source

Factory Setup

Figure 2-4. Hard Reset Configuration Source Selection—JP9

## 2.2.4 Setting Boot Source

The hard-reset configuration word, read by the MPC8272 while HRESET is asserted, may be taken from the following sources:

- Flash memory SIMM

- EEPROM

- BCSR

(In fact, eight hard-reset configuration words are read by a configuration master; however, only the first is relevant for a single MPC8272.)

For additional information about the contents of the hard-reset configuration word, see Section 5.1, "Reset and Reset Configuration."

SW2#1 actually assigns  $\overline{CS0}$  to the FLASH (default when booting from the BCSR) or to the EEPROM. When SW2 #1 is OFF, the hard-reset configuration word is taken from EEPROM. When it is ON, the hard-reset configuration word is taken from the Flash SIMM (see Figure 2-5).

Figure 2-5. SW2 Description

# 2.2.5 Setting MODCKH(0:3) for PLL Multiplication Factors

Because the PCI mode in the PowerQUICC II (Hip4 and Hip7) is enabled, the MODCKH(0:3) lines are taken from SW5(#1 - #4) and the MODCKH(0:3) bits in the hard-reset configuration word are ignored. SW5(#1 - #4) set the upper 4 bits of the MODCK field during hard reset configuration acquisition. When an individual switch of SW4 #1 - #4 is at the OFF position, its corresponding MODCKH line is pulled-high ('1') during hard reset, while when at the ON position, pulled-down ('0') (see Figure 2-3).

# 2.2.6 Setting PCI\_ARBITER for PCI Mode-Enabled

The settings of this line determine the operation of the PCI arbiter (when the PowerQUICC II is in PCI mode). When PCI\_ARBITER is set low, the PCI arbiter in the PowerQUICC II is enabled. When set high, the PCI arbiter is disabled and an external arbiter can be used. When switch SW6 #2 is at the OFF position, its corresponding PCI\_ARBITER line is pulled-high ('1' - disabled), while when at the ON position, pulled-down ('0' - enabled) (see Figure 2-5).

### 2.2.7 Setting PCI\_DLL for PCI Mode-Enabled

The settings of this line determine the operation of the DLL for PCI mode-enabled. When PCI mode is enabled, the DLL must be enabled. When PCI\_DLL is set low, the DLL is disabled. When set high, the DLL is enabled. When switch SW6 #3 is at the OFF position, its corresponding PCI\_DLL line is pulled-high ('1' - enabled). When at the ON position, pulled-down ('0' - disabled) (see Figure 2-5).

### 2.2.8 Clock-In Source Selection

The main clock source can be selected between an external (off-board) source by connecting to P6 or an on-board clock oscillator. The selection is done by setting JP1. When a jumper is placed between positions 1-2 of JP1, the external clock source is enabled. When a jumper is placed between positions 2-3 of JP1, the on-board clock oscillator is enabled (see Figure 2-6).

Figure 2-6. Clock Source Selection

### 2.2.9 FCC1 Ethernet Port Mode—MII/RMII

The Ethernet PHY on FCC1 is set by default to 100Base-Tx full duplex and can be configured to operate in MII or RMII interface. The selection is done by setting JP5. When a jumper is placed between positions 1–2 of JP5, the MII interface is enabled. When a jumper is placed between positions 2–3 of JP5, the RMII interface is enabled (see Figure 2-7).

#### Figure 2-7. FCC1 Ethernet Mode Selection

#### NOTE

To cause a mode change, set JP5 while the board is powered-off.

### 2.2.10 FCC2 Ethernet Port Mode—MII/RMII

The Ethernet PHY on FCC2 is set by default to 100Base-Tx full duplex, and can be configured to operate in MII or RMII interface. The selection is done by setting JP10. When a jumper is placed between positions 1 - 2 of JP10, the MII interface is enabled. When a jumper is placed between positions 2–3 of JP10, the RMII interface is enabled (see Figure 2-8).

#### Figure 2-8. FCC2 Ethernet Mode Selection

#### NOTE

To cause the mode change, set JP10 while the board is powered-off.

### 2.2.11 USB Speed Selection

The USB port supports two speeds, 12 Mbits/s and 1.5 Mbits/s. The selection is softwarecontrolled in the BCSR. At power-on reset, the default selection is 12Mbits/s.

### 2.2.12 USB Mode Selection

The USB port supports two modes, host and slave. The selection is done by setting JP8. When a jumper is placed between positions 1-2 of JP8, the slave mode is enabled. When a jumper is placed between positions 2-3 of JP8, the host mode is enabled (see Figure 2-9).

#### Figure 2-9. USB Mode Selection

### 2.2.13 COP/JTAG Connection

Either of two options can establish connection to the COP port of the PowerQUICC II: COP/JTAG connector or a parallel port of a PC. The COP/JTAG connector requires a command converter, and the second option connects directly to the parallel port of a PC and eliminates the need for one. The selection is done automatically. If a cable is connected to the parallel port in a PC, this connection has priority over the COP/JTAG connector.

## 2.2.14 Forced Parallel Port Connection

In some computers, because the parallel port does not comply fully with the parallel port standard, the connection of a cable to the parallel port connector (P27) does not automatically switch the COP/JTAG connection to the PC. Jumper JP12 is used to force the parallel port connection in such cases. When a jumper is placed between positions 1–2 of JP12, the parallel port connection mode is forced. When a jumper is placed between positions 2–3 of JP12, the parallel port connection mode is not forced (see Figure 2-10).

Do Not Force Parallel Port Factory Setup

#### Figure 2-10. Forced Parallel Port Connection

### 2.2.15 Power On/Off Switch

Switching SW4 causes power-on reset or power-off.

# Chapter 3 Installation Instructions

This chapter provides installation instructions for the MPC8272ADS.

# 3.1 Installation Instructions

When the MPC8272ADS has been configured as desired by the user, it can be installed according to the required working environment as follows:

- Host-controlled operation

- Stand-alone

# 3.1.1 Host-Controlled Operation

In this configuration, the MPC8272ADS is controlled by a host computer using the COP port, which is a subset of the JTAG port. This configuration allows for extensive debugging using on-host debugger. There are two options to connect to the COP port:

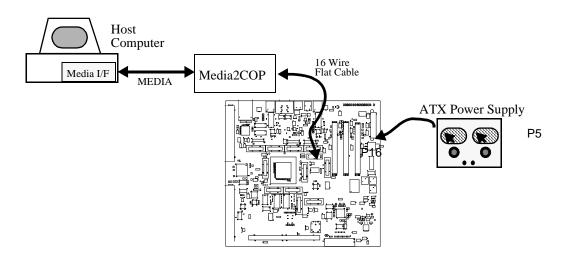

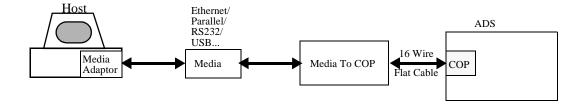

• The host is connected to the board by a COP controller (command converter) provided by a third party (see Figure 3-1).

Figure 3-1. Host-Controlled Operation Scheme—Command Converter

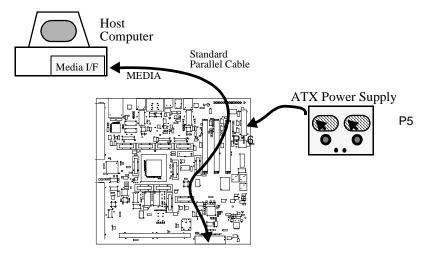

• The host is connected to the board directly from the host's parallel port (see Figure 3-2).

Figure 3-2. Host Controlled Operation Scheme—Parallel Port

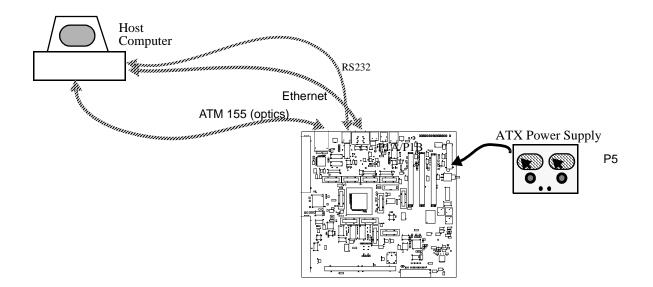

### 3.1.2 Stand Alone Operation

In this mode (see Figure 3-3), the board is not controlled by the host by using the COP port. It may connect to the host by using one of its other ports (for example, the RS232 port), Fast Ethernet port, ATM155 port, and so on. Operating in this mode requires programming an application program into the board's Flash memory.

Figure 3-3. Stand Alone Configuration

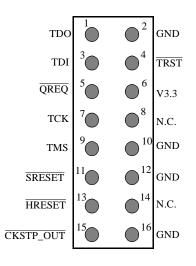

## 3.1.3 COP/JTAG Connector—P21

The MPC8272ADS COP interface connector P21 is a 16-pin, male header connector. The connection between the MPC8272ADS and the COP controller is by a 16-line flat cable supplied with the COP controller board obtained from a third party developer. Figure 3-4 shows the pin configuration of the connector.

Figure 3-4. P21—COP/JTAG Port Connector

## 3.1.4 Terminal to MPC8272ADS RS-232 Connection

A serial (RS232) terminal or any other RS232 equipment may be connected to the RS-232 connectors P1A and P1B. The RS-232 connectors are 9-pin female D-type connectors arranged in a stacked configuration. P1B connected to SCC2 of the PowerQUICC II is the lower and P1A, connected to SCC1 of the PowerQUICC II, is the upper in the stack.

The connectors are arranged in a manner that allows for 1:1 connection with the serial port of an IBM-AT or compatibles, that is, by using a flat cable. The pinout that is identical for both P1A and P1B is shown in Figure 3-5.

| CD  | 1             |   |       |

|-----|---------------|---|-------|

| ТХ  | $\frac{1}{2}$ | 6 | DSR   |

|     |               | 7 | N.C.  |

| RX  | 3             | 8 | CTS   |

| DTR | 4             | 9 | N.C.  |

| GND | 5             | - | 10.01 |

Figure 3-5. P1A/P1B—RS232 Serial Port Connector

### 3.1.5 10/100-Base-T Ethernet Ports Connection

The 10/100-Base-T port connectors P10 and P23 are an 8-pin, 90°, receptacle RJ45 connector. A standard cable that has two RJ45/8 jacks on its ends connects the 10/100-Base-T ports to the network. The pinout of P10 and P23 is described in Table 8-2.

### 3.1.6 Memory Installation

The MPC8272ADS is supplied with one type of memory module, the Flash memory SIMM.

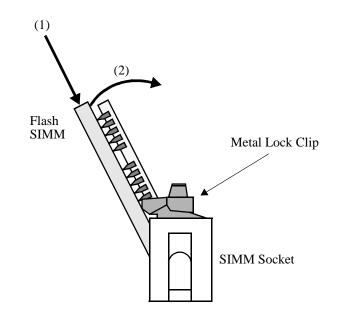

#### 3.1.6.1 Flash Memory SIMM Installation

To install a memory SIMM, remove it from its package, put it diagonally in its socket (U20), and raise it to a vertical position until the metal lock clips are locked (see Figure 3-6).

#### **CAUTION**

The memory SIMMs have alignment nibble near their # 1 pin. To avoid damage to both the memory SIMM and its socket, be sure to align the memory correctly before it is twisted.

Figure 3-6. Flash Memory SIMM Insertion

# Chapter 4 Operating Instructions

This chapter provides operating instructions for using the MPC8272ADS in host-controlled and stand-alone configurations. This information includes controls and indicators, memory map details, and software initialization of the board.

# 4.1 Controls and Indicators

The MPC8272ADS has the following switches and indicators.

# 4.1.1 Power-On RESET Switch—SW3

The power-on reset switch SW3 performs power-on reset to the MPC8272 as if the power was re-applied to the ADS. When the MPC8272 is reset that way, all configuration and all data residing in volatile memories is lost. After  $\overrightarrow{PORST}$  signal is negated, the MPC8272 re-acquires the power-on reset and hard-reset configuration data from the hard-reset configuration source. (Flash | EEPROM | BCSR).

# 4.1.2 ABORT Switch—SW6

The ABORT switch ends program execution by issuing a level 0 interrupt to the MPC8272. If the ADS is in standalone mode, the user must provide a means for handling the interrupt, because the MPC8272ADS does not have a resident debugger. The ABORT switch signal is debounced and may be disabled by software.

# 4.1.3 Soft Reset Switch—SW7

The soft reset switch SW3 performs soft reset to the MPC8272 internal modules, maintaining MPC8272's configuration (clocks and chip-selects) and SDRAMs' contents. The switch signal is debounced and software cannot disable it.

# 4.1.4 Hard Reset Switches—SW6 & SW7

When BOTH switches SW6 and SW7 are depressed simultaneously, hard reset is generated to the MPC8272. When the MPC8272 is hard reset, all its configuration is lost except for

the hard-reset configuration word, which is acquired only once after PON-Reset. The loss includes data stored in the SDRAMs, and the MPC8272 must be re-initialized.

# 4.1.5 Reset Configuration Switch—SW2

SW2 is a 4-switch dip-switch. For its function see Section 2.2, "Hardware Preparation."

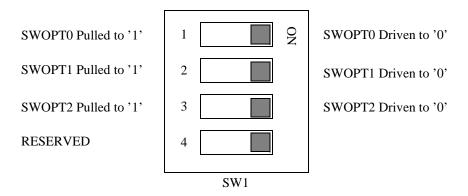

# 4.1.6 Software Options Switch—SW1

SW1 is a 4-switch dip-switch that is connected over SWOPT(0:2) lines that are available at BCSR2. S/W options may be manually selected, according to SW1 state. SW1 is factory set to all ON (see Figure 4-1).

Figure 4-1. SW1 Description

# 4.1.7 3IDDL Measurement—JP1

JP13 resides in the IDDL main current flow. To measure IDDL, JP13 should be removed using a solder tool. A current meter should be connected instead with wires that are as short and thick as possible.

#### <u>Warning</u>

The job of removing JP13 and soldering the current meter connections instead is very delicate and should be done by a skilled technician.

If this process is done by unskilled hands or repeated more than 3 times, the MPC8272ADS can be permanently damaged.

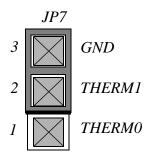

# 4.1.8 Thermal Sense Connector—JP7

Two dedicated pins THERM(0:1) provide a way to take internal temperature measurements of the MPC8272. These pins should be connected to GND for normal operation. JP7 is

factory-set with a jumper on its 2–3 positions so that THERM1 is connected to GND (see Figure 4-2).

Figure 4-2. JP7 Therm Connector

### 4.1.9 IDDH Measurement—JP14

JP14 resides in IDDH's main current flow. To measure IDDH, JP14 should be removed using a solder tool and a current meter should be connected with wires that are as short and thick as possible.

#### Warning

The job of removing JP14 and soldering current meter connections instead is very delicate, and should be done by a skilled technician.

If this process is done by unskilled hands or repeated more than 3 times, the MPC8272ADS can be permanently damaged.

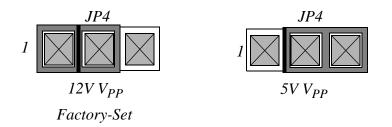

### 4.1.10 V<sub>PP</sub> Source Selector—JP4

JP4 selects the source for  $V_{PP}$  programming voltage for the Flash SIMM. When a jumper is located between pins 2 and 3 of JP4, the  $V_{PP}$  is connected to the VCC plane of the board, providing 5 V  $V_{PP}$  When a jumper is located between positions 1 and 2 of JP4,  $V_{PP}$  is drawn from the 12-V plane that provides 12V  $V_{PP}$  JP4 options are shown in Figure 4-3.

Figure 4-3. JP13 V<sub>PP</sub> Source Selection

# 4.1.11 GND Bridges

The MPC8272ADS has seven GND bridges that are meant to assist general measurements and the logic-analyzer connection.

#### <u>Warning</u>

When connecting to a GND bridge, use only insulated GND clips. Un-insulated clips may cause short-circuits that touch hot points around them. Failure to use insulated GND clips can permanently damage the MPC8272ADS.

### 4.1.12 Power O.K. Indicator—LD13

The green Power O.K. LED indicator lights if the ATX power supply is generating all the voltages.

### 4.1.13 12V Indicator—LD14

The green 12-V led LD14 indicates the presence of the +12-V supply on the board.

# 4.1.14 UTOPIA Multi PHY Indicator—LD28

The green multi PHY led LD28, indicates that the UTOPIA is in multiPHY mode. When this indicator is off, the UTOPIA is in single PHY mode.

# 4.1.15 5-V Indicator—LD15

The green 5V led LD15 indicates the presence of the +5 V supply on the board.

# 4.1.16 3.3-V Indicator—LD16

The green 3.3V led LD16 indicates the presence of the +3.3 V supply on the board.

# 4.1.17 USB Power Indicator—LD5

The green USB Power led LD5 indicates the presence of 5 V in the USB cable.

# 4.1.18 -12V Indicator—LD17

The green -12V led—LD17, indicates the presence of the -12V supply on the board.

### 4.1.19 RUN Indicator—LD18

When the green RUN led - LD18 is lit, it indicates that the MPC8272 is performing cycles on the PPC bus. When dark, the MPC8272 is either running internally or stuck.

### 4.1.20 ATM ON Indicator—LD19

When the yellow ATM ON led is lit, it indicates that the ATM-UNI transceiver PM5384 is enabled for communication. When it is dark, the ATM-UNI transceiver is disconnected from the MPC8272, enabling the use of its associated FCC1 pins off-board by using the expansion connectors or for Fast Ethernet.

ATM ON led is controlled by BCSR1.

# 4.1.21 Fast Ethernet Port 1 Enabled—LD20

When the yellow ETH1 ON led is lit, the fast Ethernet port 1 transceiver DM9161 is connected to FCC1. When it is dark, the DM9161 is in power-down mode and disconnected from FCC1, enabling the use of its associated FCC1 pins off-board by using the expansion connectors. BCSR1 controls the state of LD20.

### 4.1.22 Fast Ethernet Port 2 Enabled—LD22

When the yellow ETH2 ON led is lit, the fast Ethernet port 2 transceiver DM9161 is connected to FCC2. When it is dark, the DM9161 is in power-down mode and disconnected from FCC2, enabling the use of its associated FCC2 pins off-board by using the expansion connectors. BCSR1 controls the state of LD22.

# 4.1.23 RS232 Port 1 ON-LD23

When the yellow RS232 Port 1 ON led is lit, the RS232 transceiver is connected to P13A (upper DB9 connector), is active, and communication using that medium is allowed. When it is darkened, the transceiver is in shutdown mode and its associated SCC1 pins may be used off-board by using the expansion connectors.

# 4.1.24 Fast Ethernet Port 1 Full Duplex Indicator—LD1

When the Dm9161 on FCC1 is enabled and is in full duplex operation mode, the red led - LD1 lights.

# 4.1.25 RS232 Port 2 ON—LD24

When the yellow RS232 Port 2 ON led is lit, the RS232 transceiver is connected to P13B (lower DB9 connector), is active, and communication using that medium is allowed. When

darkened, it designates that the transceiver is in shutdown mode and its associated SCC4 pins may be used off-board by using the expansion connectors.

# 4.1.26 Fast Ethernet Port 1 100Base-Tx Indicator—LD2

When the DM9161 on FCC1 is enabled and is in 100 Mbps operation mode, the green led LD2 lights.

# 4.1.27 Ethernet Port 1 Tx/Rx Indicator—LD3

The green Ethernet transmit/receive LED indicator blinks whenever the Dm9161 on FCC1 is transmitting or receiving data by using the 10/100-Base-T port.

## 4.1.28 General Purpose Led 2 Indicator—LD26

This general-purpose red LED is user-controlled by BCSR0.

### 4.1.29 Ethernet Port 1 LINK Indicator—LD4

The yellow Ethernet twisted-pair link integrity LED indicator (LINK) lights to indicate good link integrity on the 10/100-Base-T port. When the link integrity fails, LD4 is off.

### 4.1.30 Fast Ethernet Port 2 Full Duplex Indicator—LD6

When the Dm9161 on FCC2 is enabled and is in full duplex operation mode, the red led LD6 lights.

### 4.1.31 General Purpose Led 1 Indicator—LD25

This general-purpose green LED is user-controlled by BCSR0.

### 4.1.32 Fast Ethernet Port 2 100Base-Tx Indicator—LD7

When the DM9161 on FCC2 is enabled and is in 100 Mbps operation mode, the green led LD7 lights.

### 4.1.33 USB Enabled Indicator—LD21

The yellow USB enable LED indicates that the USB transceiver is connected to the MPC8272.

### 4.1.34 Ethernet Port 2 LINK Indicator—LD9

The yellow Ethernet twisted pair link integrity LED indicator (LINK) lights to indicate good link integrity on the 10/100-Base-T port. When the link integrity fails, LD9 is off.

### 4.1.35 Ethernet Port 2 Tx/Rx Indicator—LD8

The green Ethernet transmit/receive LED indicator blinks whenever the Dm9161 on FCC2 is transmitting or receiving data using the 10/100-Base-T port.

# 4.1.36 V<sub>DDL</sub> Indication—LD27

The green  $V_{DDL}$  indicator led LD27 is lit to indicate a  $V_{DDL}$  power activity. Because  $V_{DDL}$  level may vary, the LD27 illumination level also varies accordingly.

### 4.1.37 Parallel Port connection—LD10

The green parallel port connection LED indicates that the board is connected directly to the PC parallel port and the COP/JTAG connector (P21) is irrelevant.

## 4.1.38 External Debugger Connection Indicator—LD11

The green external debugger connection LED indicates that a command converter can be connected to the COP/JTAG connector (P21).

# Chapter 5 Module Design

This chapter provides information about the functionality and design details of the various modules that constitute the MPC8272ADS.

# 5.1 Reset and Reset Configuration

The following are reset sources on the MPC8272ADS:

- Power-on reset

- Manual hard reset

- Manual soft reset

- PCI bus reset

- MPC8272 internal sources. For more information, see the *MPC8272 PowerQUICC II*<sup>TM</sup> *Family Reference Manual*.

# 5.1.1 Power-On Reset

The power-on reset to the MPC8272 initializes the processor state after power-on. A dedicated logic using Seiko S-80728AN-DR-T1, which is a voltage detector of 2.8V +/-2.4%, asserts PORESET input to the PowerQUICC II for a period of ~2.5sec. This time period is sufficient to cover the  $V_{DDL}$  stabilization also, powered by a different voltage regulator. It is assumed that the stabilization time for both linear regulators (see Section 7.1, "Power Supply") are about the same. Furthermore, power-on reset may be generated manually by an on-board dedicated push-button (SW1). Power-on reset can also be generated by the JTAG logic, which is integrated with BCSR.

# 5.1.2 **Power-On Reset Configuration**

At the end of Power - On reset sequence, MODCK(1:3) are sampled by the MPC8272 to configure the various clock modes of the MPC8272 (core, cpm, bus, PCI...). Selection between the MODCK(1:3) combination options is done by means of dip-switches on the mother board while PCI\_MODCKH(0:3) are obtained from the relevant dedicated dip-switches.

The configuration master is determined upon the rising edge of  $\overline{\text{PORST}}$ , according to the state of  $\overline{\text{RSTCONF}}$  signal, driven low on this board, to set the MPC8272 as a configuration master.

After power-on reset negates, the hard-reset sequence starts, during which many other different options are configured. Among these options are additional clock configuration bits PCI\_MODCKH(0:3), the most significant bits of the MODCK field, which determine additional options for the clock generator. Although these bits are sampled whenever the hard-reset sequence is entered, they are influential only once, after power-on reset. If a hard reset sequence is entered later, MODCKH(0:3), although sampled, are 'don't care'.

The PCI\_MODCK signal, which is sampled concurrently with the PCI\_MODCK(0:3) pins, determines the PCI bus clock frequency (see Section 5.2.2, "PCI Clock"). When set high, it divides the PCI bus frequency by two. When reset low, the PCI bus frequency is as determined by the MODCK(1:3) and PCI\_MODCKH(0:3) signals.

# 5.1.3 Hard Reset

Hard reset may be generated on the MPC8272ADS by the following sources:

- COP/JTAG port

- Manual hard reset

- MPC8272's internal sources

Hard-reset, when generated, causes the MPC8272 to reset all its internal hardware except for PLL logic, re-acquires the Hard-reset configuration from its current source, and jumps to the Reset vector in the exception table. Since hard-reset resets also the refresh logic for dynamic RAMs, their content is lost as well.

**HRESET** when asserted, is extended internally by the MPC8272 for additional 512 bus clock cycles at the end of which the MPC8272 waits for 16 bus clock cycles and then re-checks the state of the  $\overline{\text{HRESET}}$  line.

HRESET is an open-drain signal and must be driven with an open-drain gate by whichever external source is driving it. Otherwise, contention occurs over that line, which might cause permanent damage to either board logic or to the MPC8272 itself.

### 5.1.3.1 COP/JTAG Port Hard Reset

To provide convenient hard-reset capability for a COP/JTAG controller, HRESET line appears at the COP/JTAG port connector. The COP/JTAG controller may directly generate hard-reset by asserting (low) this line.

### 5.1.3.2 Manual Hard Reset

To allow runtime hard-reset, when the COP controller is disconnected from the MPC8272ADS, and to support resident debuggers, manual hard is facilitated. Depressing both soft reset (SW7) and ABORT (SW6) buttons asserts the HRESET pin of the MPC8272, generating a hard reset sequence.

Because the HRESET line may be driven internally by the MPC8272, it must be driven to the MPC8272 with an open-drain gate. If off-board hardware connected to the MPC8272ADS is to drive HRESET line, it should do so with an open-drain gate, to avoid contention over this line.

When hard reset is generated, the MPC8272 is reset in a destructive manner, that is, the hard reset configuration is re-sampled and all registers (except for the PLL's) are reset, including memory controller registers. This reset causes loss of dynamic memory contents.

To save on board's real-estate, this button is not a dedicated one, but is shared with the soft-reset button and the ABORT button. When both are depressed, hard reset is generated.

#### 5.1.3.3 Internal Sources Hard Reset

The MPC8272 has internal sources that generate hard reset. Among these sources are the following:

- Loss of lock reset. When one of the PLLs (core, CPM), is out of lock, hard-reset is generated.

- Check-stop reset. When the core enters a check-stop state from some reason, a hard reset may be generated, depending on the CSRE bit in the RMR.

- Bus monitor reset. When the bus monitor is enabled and a bus cycle is not terminated, hard-reset is generated.

- S/W Watch Dog Reset. When the S/W watch-dog is enabled, and application software fails to perform its reset routine, it generates hard reset.

- COP/JTAG Reset (Internal). Hard reset may be forced by driving the HRESET line using the external pin's scan chain. Not useful for run time.

The MPC8272 asserts a reset line HARD or SOFT for a period 512 clock cycles after a reset source is identified. A hard reset sequence is followed by a soft reset sequence.

### 5.1.3.4 Hard Reset Configuration

When hard reset is applied to the MPC8272 (externally as well as internally), it samples the hard reset configuration word. This configuration may be taken from an internal default, in case RSTCONF is negated during HRESET asserted or taken from the Flash /E2PROM/BCSR (MS 8 bits of the data bus) (in general, from any device residing on CS0) in case RSTCONF signal is asserted along with HRESET. The default configuration word

can be taken from the E2PROM/BCSR in case the Flash has been tampered with. The selection between the BCSR, FLASH and the E2PROM as the source of the default configuration word is determined by a dedicated dip-switch and a jumper.

During hard reset sequence, the configuration master<sup>1</sup> reads the Flash (or  $E^2PROM$  or BCSR) memory at addresses 0, 8, 0x18, 0x20,... a byte each time, to assemble the 32 bit configuration word. A total of 64 bytes of data is read from D(0:7) to acquire 8 full configuration words for system that may have up to 8 MPC8272 chips.

The configuration word for a single<sup>2</sup> MPC8272 is stored in the Flash memory SIMM, in the  $E^2$ PROM or as default in the BCSR, while the other seven words are not initialized, as there are no additional MPC8272 on the MPC8272ADS. The default configuration word is shown in Table 5-1 for the FLASH and in Table 5-2 for the  $E^2$ PROM. PCI module configuration is 256 Bytes long and should start at address 0x100.

The two possible configuration words are the following:

- FLASH/BCSR is the boot device.  $\overline{CS0}$  is assigned to the FLASH and  $\overline{CS4}$  is assigned to the E<sup>2</sup>PROM.

- $E^2PROM$  is the boot device.  $\overline{CS0}$  is assigned to the  $E^2PROM$  and  $\overline{CS4}$  is assigned to the FLASH.

| Field | Data<br>Bus<br>Bits | Prog<br>Value<br>[Bin] | Implication                                                                                                                                 | Offset In<br>Flash<br>[Hex] | Value<br>[Hex] |

|-------|---------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------------|

| ERB   | 0                   | '0'                    | Internal Arbitration Selected.                                                                                                              | 0                           | 0C             |

| EXMC  | 1                   | '0'                    | Internal Memory Controller. $\overline{CSO}$ active at system boot.                                                                         |                             |                |