# LS7290

LSI Computer Systems, Inc. 1235 Walt Whitman Road, Melville, NY 11747 (631) 271-0400 FAX (631) 271-0405

# STEPPER MOTOR CONTROLLER

#### FEATURES:

- Controls Bipolar and Unipolar motors

- Cost-effective replacement for L297

- Full, 1/2 step mode selected with mode input

- Direction control

- Reset input

- Step control input

- Enable input

- PWM chopper circuit for current control

- Two peak-current comparators with external reference input

- Step control frequency and duty cycle controlled by an external frequency source or by an internal crystal controlled oscillator (typically 8 MHz)

- All inputs and outputs TTL/CMOS compatible (TTL for 5V operation)

- 3V to 5.5V Operation ( $V_{DD} V_{SS}$ )

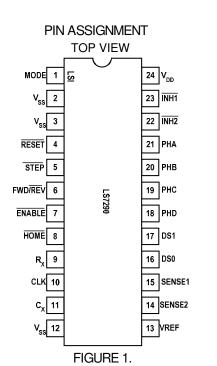

- LS7290 (DIP), LS7290-S (SOIC), LS7290-TS (TSSOP) See Figure 1.

#### DESCRIPTION:

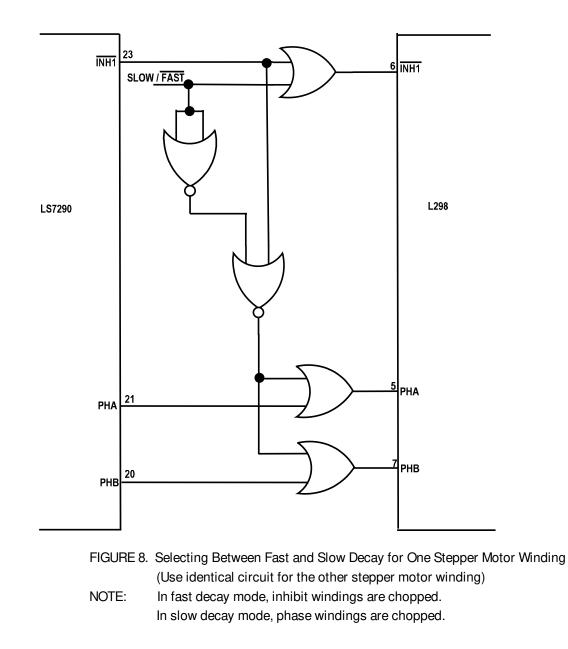

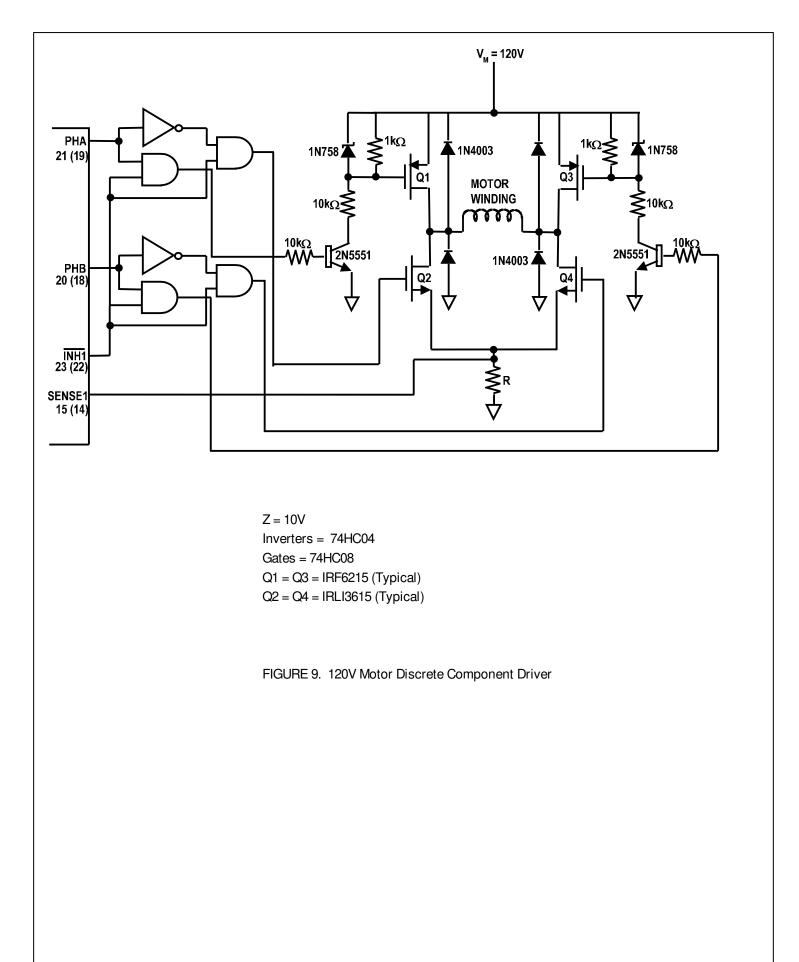

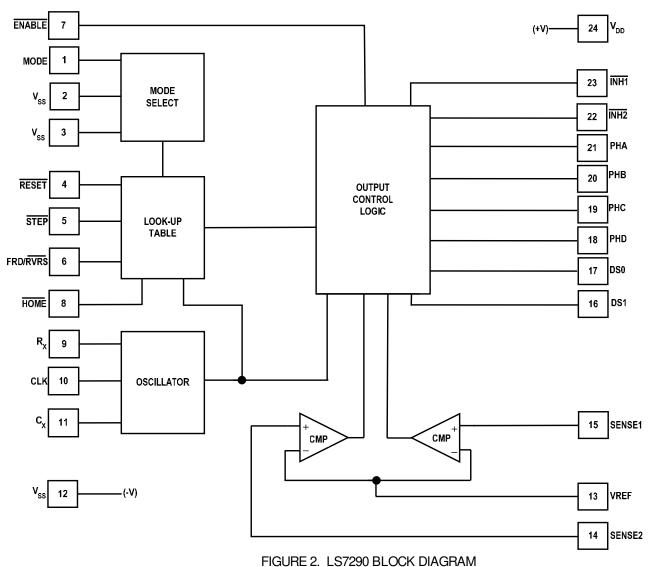

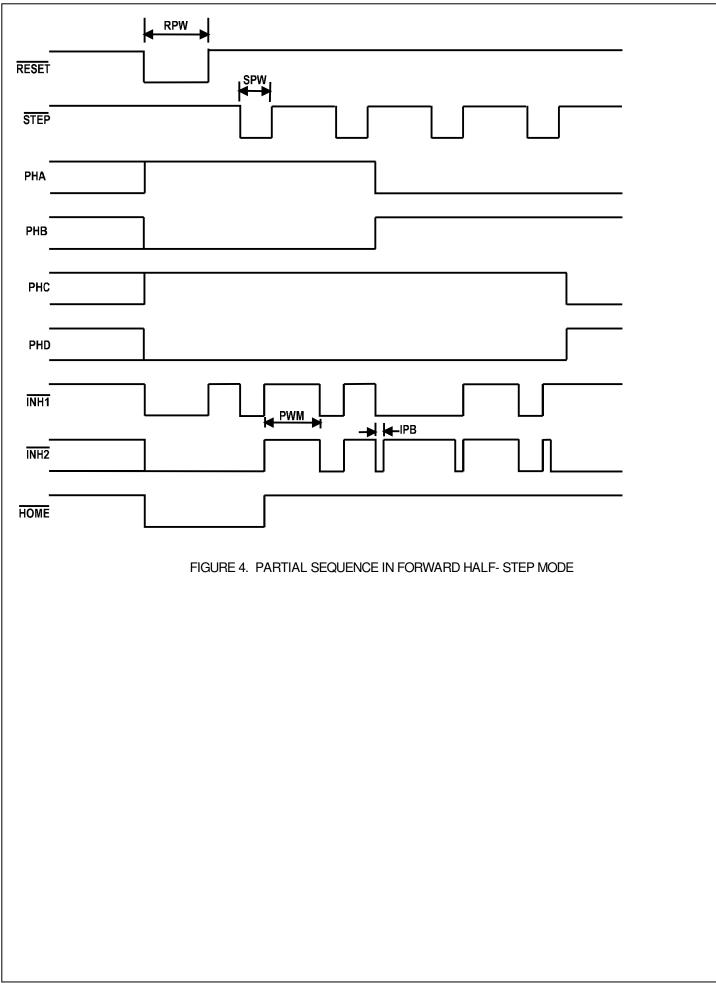

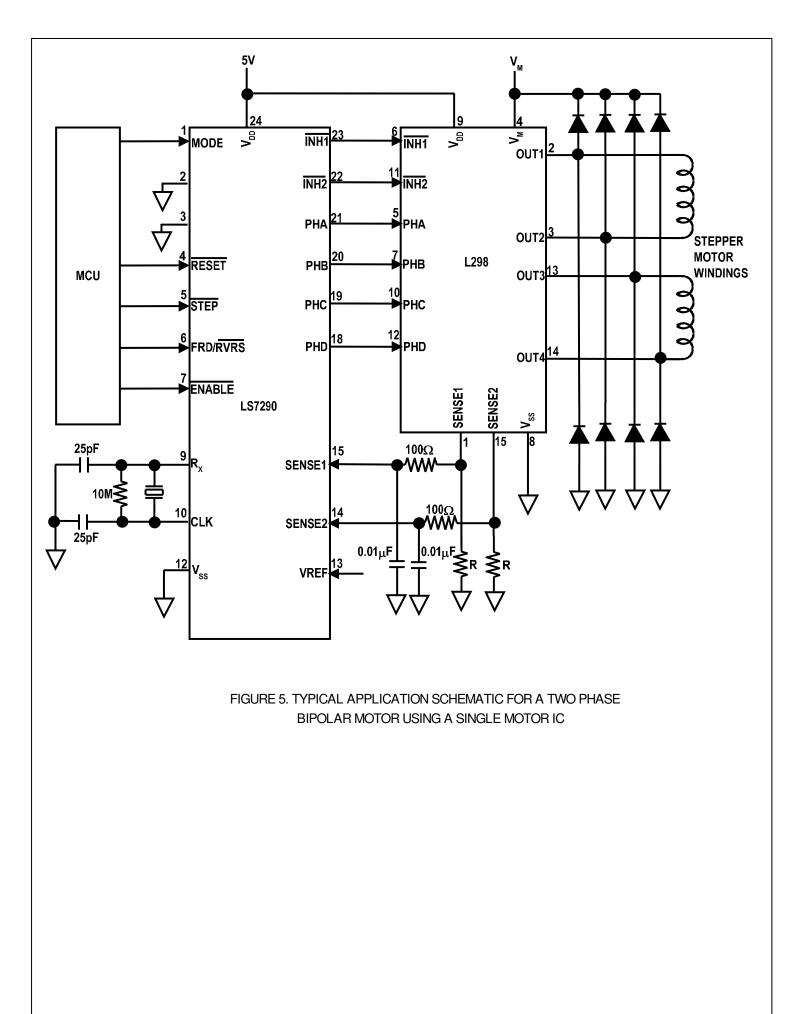

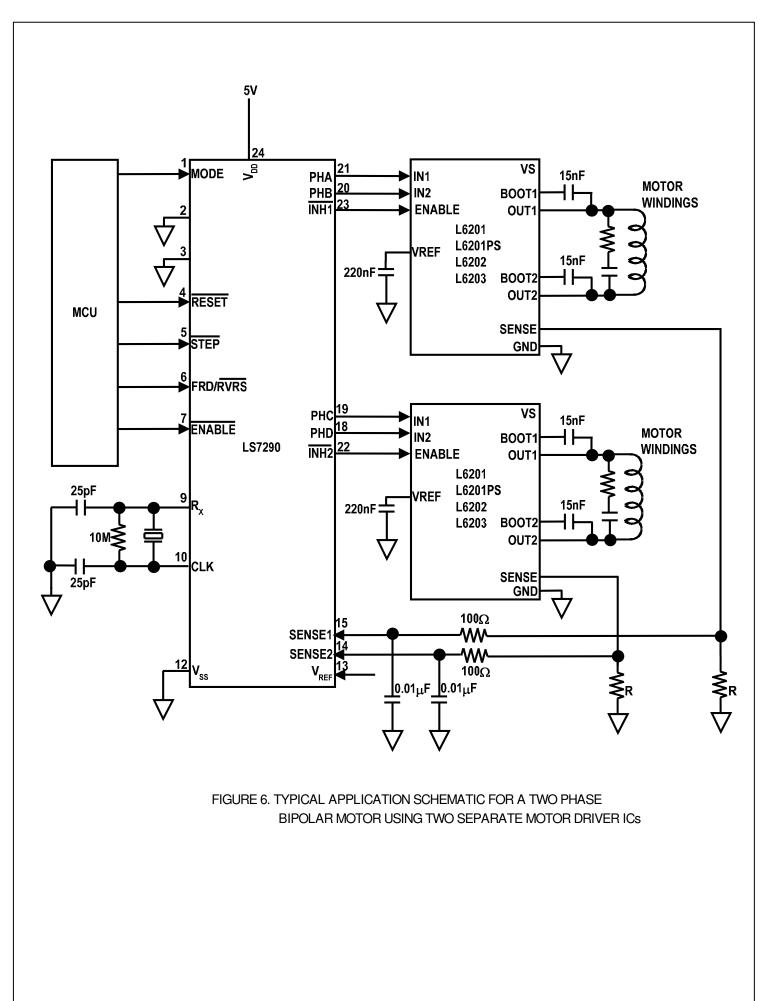

The LS7290 generates Phase Drive outputs and PWM outputs for controlling twophase Bipolar Motors or four-phase Unipolar Motors, respectively. The LS7290 contains a mode controlled look-up table for generating the motor duty cycle drive sequences. There are four outputs which are used to drive two H-Bridges for the two motor windings in the Bipolar motor or the four driver transistors for the two centertapped windings in the Unipolar motor (Refer to Table 2). The LS7290 can step a motor in full steps and half steps. The refresh rate is set using an internal oscillator controlled by a crystal or by use of an external input clock. Typical refresh rate is equal to 31.25kHz with the clock frequency set at 8MHz. Peak-current feedback control using pulse-width modulation is used in full-step or half-step modes. The chopper consists of a voltage comparator, flip-flop and external sense resistor. The internal oscillator sets the flip-flop and enables the INH1 and INH2 outputs at the beginning of each PWM cycle. Once the peak motor current causes the voltage across the sense resistors to reach the voltage set by VREF, the outputs are disabled until the next oscillator pulse. The VREF voltage sets the peak current in each motor winding.

# INPUT/OUTPUT DESCRIPTION

#### RESET Input

Active low. Resets the PWM table pointer to HOME position per Table 2 and brings INH1 and INH2 low. Upon power-up, a POR circuit also resets the PWM table pointer.

#### ENABLE Input

Active low. When high (inactive), brings PHA, PHB, PHC, PHD, INH1 and INH2 outputs low.

#### STEP Input

Active low. A low-going pulse on this input causes the motor to advance one step.

July 2011

NOTE: Pins 2 and 3 are used for factory test and must be tied to ground.

# FRD/RVRS Input

A low input causes the motor to move in incremental steps in reverse direction per Table 2. A high input causes the motor to move in incremental steps in forward direction per Table 2. Switching directions can occur at any time.

#### MODE Input

Defines the stepping modes as follows:

|                | MODE |  |  |  |  |

|----------------|------|--|--|--|--|

| full step mode | 0    |  |  |  |  |

| 1/2 step mode  | 1    |  |  |  |  |

Stepping mode can be changed at any time.

#### SENSE1 / SENSE2 Inputs

Inputs for motor winding current sense. A fractional-Ohm resistor connected in series with each of the H-Bridge drivers produce SENSE1 and SENSE2 voltages. These voltages are compared with VREF voltage input, for generating the PWM inhibit outputs.

#### **VREF** Input

External voltage reference for chopper circuit which determines the maximum motor winding current by regulating the PWM duty cycle. The SENSE resistors should satisfy the equations  $R_{S1}$  =  $R_{S2}$  =  $V_{\text{REF}}$  /  $I_{\text{MAX}}$  where  $I_{\text{MAX}}$  is the maximum motor winding current.

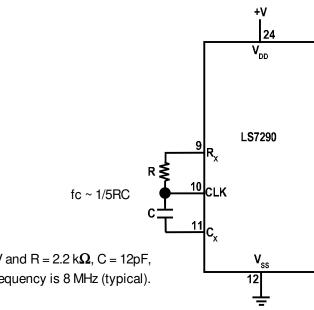

#### $R_X,\,C_X,\,CLK$

These three pins can be configured in one of three ways to obtain the primary clock. A crystal connected between RX and CLK pins or a resistor-capacitor pair connected among all three pins (see Figure 4) can make use of the internal oscillator. Alternatively, the CLK pin can be driven from an external clock source.

#### DS0/DS1 Inputs

The phase drive is blanked out between steps by switching outputs INH1 and  $\overline{\text{INH2}}$  low in order to reduce audible noise and power consumption. The duration of the blanking is selected by DS0 and DS1 according to Table 1.

8Mz

#### Table 1

| Blanking Time, IPB, at fc = | DS0 | DS1 |

|-----------------------------|-----|-----|

| 1.25µs                      | 0   | 0   |

| 2.50µs                      | 1   | 0   |

| 3.75µs                      | 0   | 1   |

| 5.00µs                      | 1   | 1   |

|                             |     |     |

#### PHA / PHB / PHC / PHD Outputs

The state of these phase outputs are determined by the look-up table and are used to control either the left or right half of each of the H-Bridge drivers. A low on a phase output enables the bottom driver while a high on the output enables the top driver.

### HOME Output

Indicates Step0 state per Table 2 with a logic low.

#### INH1 / INH2 Outputs

These outputs are used to provide PWM control to each of the two H-Bridge drivers.

The information included herein is believed to be accurate and reliable. However, LSI Computer Systems, Inc. assumes no responsibilities for inaccuracies, or for any infringements of patent rights of others which may result from its use.

| ABSOLUTE MAXIMUM RAT      | INGS:                             |                                  |     |     |      |                               |

|---------------------------|-----------------------------------|----------------------------------|-----|-----|------|-------------------------------|

| PARAMETER                 | SYMBOL                            | VALUE                            |     |     | UNIT |                               |

| DC Supply Voltage         | V <sub>DD</sub> - V <sub>SS</sub> | +7                               |     | V   |      |                               |

| Any Input Voltage         | VIN                               | $V_{SS} - 0.3$ to $V_{DD} + 0.3$ |     | V   |      |                               |

| Operating Temperature     | TA                                | -20 to +85                       |     | °C  |      |                               |

| Storage Temperature       | T <sub>STG</sub>                  | -85 to +150                      |     | °C  |      |                               |

| ELECTRICAL SPECIFICATIO   | ONS (-25°C < T                    | -<br>^ < +85                     | °C) |     |      |                               |

| PARAMETER                 | SYMBOL                            | MIN                              | TYP | MAX | UNIT | CONDITIONS                    |

| Supply Voltage            | VDD                               | 3.0                              | -   | 5.5 | V    | <u>-</u>                      |

| Supply Current            | IDD                               | -                                | -   | 2.0 | mA   | Outputs floating, Inputs high |

| CLK frequency             | fc                                |                                  | 8.0 | -   | MHz  | -                             |

| Enable Propagation Delay  | t <sub>epd</sub>                  | 100                              | -   | -   | ns   | -                             |

| FRD/RVRS Setup Time       |                                   | •                                |     |     |      |                               |

| (before step pulse)       | t <sub>ds</sub>                   | 0                                | -   | -   | μs   | -                             |

| Step Pulse Width          | SPW                               | 1.0                              | -   | -   | μs   | at $f_c = 8 MHz$              |

| Interstep Pulse Delay     | ISD                               | 32                               | -   | -   | μs   | at f <sub>c</sub> = 8 MHz     |

| Interstep Phase Blanking  | IPB                               | 1.25                             | -   | 5.0 | μs   | at f <sub>c</sub> = 8 MHz     |

| Reset Pulse Width         | R <sub>PW</sub>                   | 1.0                              | -   | -   | μs   | at f <sub>c</sub> = 8 MHz     |

| Reset to Step Pulse Delay | trs                               | 0                                | -   | -   | μs   | -                             |

| Hi-Level Input Voltage    | VIH                               | 2                                | -   | -   | v    | $V_{DD} = 5 \pm 0.25 V$       |

| Low-Level Input Voltage   | VIL                               | -                                | -   | 0.8 | V    | $V_{DD} = 5 \pm 0.25 V$       |

| High-Level Input Current  | Iн                                | -                                | -   | 50  | nA   | Leakage Current               |

| Low-Level Input Current   | ١L                                | -                                | -   | 50  | nA   | Leakage Current               |

| Output Sink Current       | lo                                | -10                              | -   | -   | mA   | $V_O = 0.4V$ , $V_{DD} = 5V$  |

|                           | lo                                | -5                               | -   | -   | mA   | $V_O = 0.4V, V_{DD} = 3.3V$   |

| Output Source Current     | lo                                | 5                                | -   | -   | mA   | $V_O = 4V, V_{DD} = 5V$       |

|                           | lo                                | 2.5                              | -   | -   | mA   | $V_{O} = 2.5V, V_{DD} = 3.3V$ |

| Comparator Offset Voltage | Vos                               | -                                | 5   | 15  | mV   | $V_{REF} = 1V$                |

| Input Reference Voltage   | V <sub>REF</sub>                  | 0.5                              | -   | 3.0 | V    | $V_{DD} = 5V$                 |

|                           | V <sub>REF</sub>                  | 0.5                              | -   | 1.5 | V    | $V_{DD} = 3.3V$               |

At VDD = 5V and R = 2.2 k $\Omega$ , C = 12pF, oscillator frequency is 8 MHz (typical).

FIGURE 3. RC OSCILLATOR FOR CLOCK GENERATOR

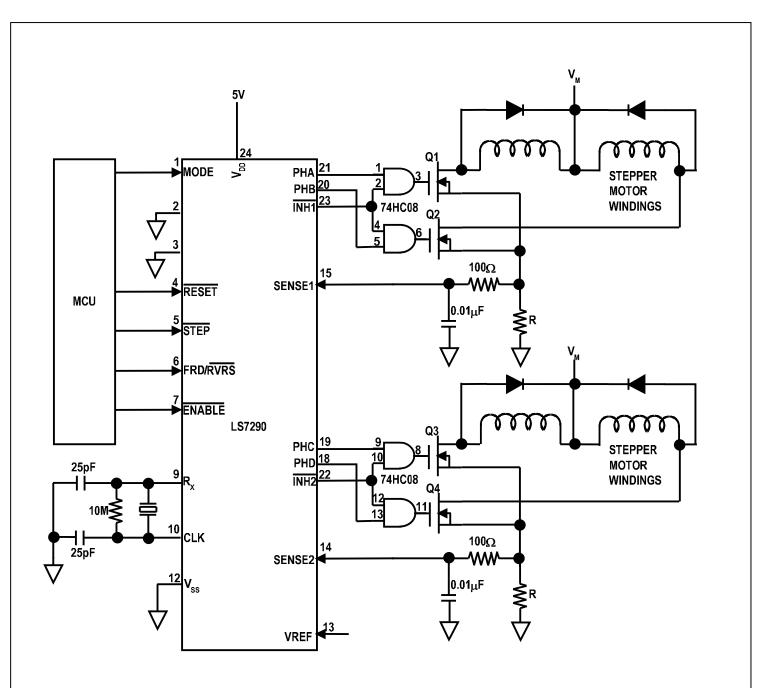

NOTE: Q1, Q2, Q3, Q4 are MOSFET Power Transistors suitable for 5V Gate Drive Typical P/Ns = IRLZ44N and IRF3708

FIGURE 7. TYPICAL APPLICATION SCHEMATIC FOR A FOUR PHASE UNIPOLAR MOTOR USING DISCRETE MOSFET TRANSISTORS

|        | TABLE 2 |       |       |        |     |     |     |            |  |

|--------|---------|-------|-------|--------|-----|-----|-----|------------|--|

| STEP N | IUMBER  |       |       | PHASES |     |     |     |            |  |

| FULL   | 1/2     | INH1  | INH2  | PHA    | PHB | PHC | PHD | STEP ANGLE |  |

| 0      | 0       | 100   | 0     | 1      | 0   | 1   | 0   | HOME       |  |

|        | 1       | 70.7  | 70.7  | 1      | 0   | 1   | 0   | 45         |  |

| 1      | 2       | 0     | 100   | 0      | 1   | 1   | 0   | 90         |  |

|        | 3       | -70.7 | 70.7  | 0      | 1   | 1   | 0   | 135        |  |

| 2      | 4       | -100  | 0     | 0      | 1   | 0   | 1   | 180        |  |

|        | 5       | -70.7 | -70.7 | 0      | 1   | 0   | 1   | 225        |  |

| 3      | 6       | 0     | -100  | 1      | 0   | 0   | 1   | 270        |  |

|        | 7       | 70.7  | -70.7 | 1      | 0   | 0   | 1   | 315        |  |

| 0      | 0       | 100   | 0     | 1      | 0   | 1   | 0   | HOME       |  |