# **High Speed Ultrasound Beamforming Source Driver**

#### **Features**

- ► Multiple-level ultrasound pulser

- ► Fast switching current source for push-pull topology

- ➤ 250MHz maximum frequency, 4.0ns input to output delay

- ▶ 15 independent programmable output level registers

- ▶ Pulse amplitude modulation (PAM) with 8-bit resolution

- ▶ 8-bit apodization DAC for peak output current via SPI

- Very low second order harmonic distortion

- Picoseconds time-jitter from input to output

- ► Fast SPI write and read-back of level & DAC registers

- ▶ +5.0V power supply, 2.5V CMOS logic interface

- Drives DN2625 MOSFETs output up to 230V<sub>P-P</sub>

- Programmable aperture windowing

## **Applications**

- Medical imaging ultrasound beamforming transmitter

- Dynamic focusing B-scan CW PW Doppler & FM chirp

- Ultrasonic phase array focusing transmitter

- Piezoelectric & MEMS transducer waveform drivers

- High speed arbitrary waveform generator

- High resolution NDT phase array ultrasound pulser

## **General Description**

The MD2134 is a high-speed source driver for use in a pulsed current waveform generator. This programmable, fast, arbitrary current level driver is designed for medical ultrasound imaging beamforming applications. It also can be used in HIFU, NDT ultrasound and other instrument applications.

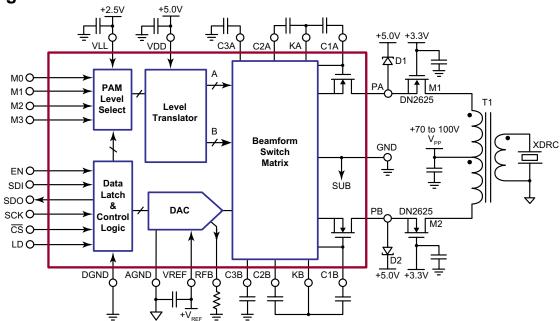

The MD2134 consists of CMOS digital logic input circuits, an eight-bit current DAC for aperture weighting amplitude control, and a programmable 15-level pulse amplitude modulation (PAM) current-source that does not include a zero level. The fast current sources are constructed with current-switch array, controlled by the LV0~LV15 level-register as the waveform data points. Four logic inputs M[3:0] are used for transmit data level selecting, as well as the transmitting timing control pins. Each level can be programmed to a resolution of +/-127 including zero (8-bit) in addition to an 8-bit SPI apodization DAC. The outputs PA and PB are controlled by M[3:0] pins directly, as well as the polarity-flip bit S1 in the SPI register. The high-speed SPI interface will achieve per-scan-line fast data updating for dynamically changing delay time, weighting and waveforms.

The MD2134 outputs are designed to drive two very low-threshold, high-voltage depletion N-MOSFETs, such as Supertex's DN2625s, as source drivers. The two DN2625 drains are connected to a center-tap RF pulse transformer. The transformer's secondary output connects to a cable and piezoelectric or capacitive transducer as a load with a good impedance match.

## **Block Diagram**

## **Ordering Information**

| Part Number | Package           | Packing   |

|-------------|-------------------|-----------|

| MD2134K7-G  | 40-Lead (5x5) QFN | 490/ Tray |

## **Absolute Maximum Ratings**

| Parameter                                        | Value           |

|--------------------------------------------------|-----------------|

| V <sub>LL</sub> , Logic supply                   | -0.5V to +3.5V  |

| V <sub>DD</sub> , Positive supply                | -0.5V to +6V    |

| V <sub>PA</sub> , V <sub>PB</sub> Driver outputs | -0.5V to +6V    |

| V <sub>SUB</sub> , Ground                        | 0V              |

| Operating temperature                            | 0°C to +70°C    |

| Storage temperature                              | -65°C to +150°C |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability. All voltages are referenced to device ground.

## **Pin Configuration**

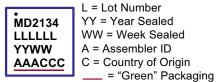

## **Package Marking**

Package may or may not include the following marks: Si or

40-Lead QFN (K7)

## **Typical Thermal Resistance**

| Package     | $oldsymbol{	heta}_{j_{oldsymbol{a}}}$ |

|-------------|---------------------------------------|

| 40-Lead QFN | 26°C/W                                |

**Operating Supply Voltages**

(Over operating conditions unless otherwise specified,  $V_{LL}$  = +2.5V,  $V_{DD}$  = +5V,  $V_{REF}$  = 2.5V,  $R_{FB}$  = 71.1k $\Omega$ ,  $T_A$  = 25°C, DAC = 0)

| Sym               | Parameter                             | Min  | Тур | Max  | Units | Conditions                                  |  |

|-------------------|---------------------------------------|------|-----|------|-------|---------------------------------------------|--|

| V <sub>LL</sub>   | Logic supply                          | 2.25 | -   | 2.75 | V     | T 04. 70%                                   |  |

| V <sub>DD</sub>   | Power supply                          | 4.75 | 5.0 | 5.25 | V     | $T_A = 0 \text{ to } 70^{\circ}\text{C}$    |  |

| I <sub>LLQ</sub>  | V <sub>LL</sub> supply current EN = 0 | -    | 0.1 | 1.0  |       | Standby condition                           |  |

| I <sub>DDQ</sub>  | V <sub>DD</sub> supply current EN = 0 | -    | 0.2 | 1.0  | μA    | Standby condition                           |  |

| I <sub>LLEN</sub> | V <sub>LL</sub> supply current EN = 1 | -    | 5.0 | 20   | μA    | f = 0 all logic input no transit            |  |

| I <sub>DDEN</sub> | V <sub>DD</sub> supply current EN = 1 | -    | 5.0 | 12   | mA    | $f_{SCK} = 0$ , all logic input, no transit |  |

| I <sub>LL50</sub> | V <sub>LL</sub> supply current EN = 1 | -    | 1.0 | 3.0  | mA    | f <sub>SCK</sub> = 50MHz, CW, M[0:3] = 0    |  |

| I <sub>DD50</sub> | V <sub>DD</sub> supply current EN = 1 | -    | 40  | 85   | mA    | f <sub>SCK</sub> = 0 , Input = 50MHz, CW    |  |

### **Output Characteristics**

(Over operating conditions unless otherwise specified,  $V_{LL}$  = +2.5V,  $V_{DD}$  = +5V,  $V_{REF}$  = 2.5V,  $R_{FB}$  = 71.1k $\Omega$ ,  $T_A$  = 25°C)

| Sym                  | Parameter                                          | Min  | Тур | Max  | Units | Conditions               |

|----------------------|----------------------------------------------------|------|-----|------|-------|--------------------------|

| I <sub>MAX-A/B</sub> | Full scale output peak current                     | 2.88 | _   | 3.52 | Α     | DAC = 255, Level = 127   |

| I <sub>OO-A/B</sub>  | Output current offset                              | _    | 0.5 | 2.0  | mA    | DAC = 0                  |

|                      | Output voltage range,<br>+10% of I <sub>PA/B</sub> | 5.3  | 5.8 | -    |       | I <sub>PA/B</sub> = 1.0A |

|                      |                                                    | 5.0  | 5.5 | -    |       | I <sub>PA/B</sub> = 1.5A |

| \ \/                 |                                                    | 4.5  | 5.0 | -    |       | I <sub>PA/B</sub> = 3.0A |

| V <sub>PA/B</sub>    | Output voltage range,<br>-10% of I <sub>PA/B</sub> | -    | 1.0 | 1.5  | V     | I <sub>PA/B</sub> = 1.0A |

|                      |                                                    | -    | 1.2 | 1.7  |       | I <sub>PA/B</sub> = 1.5A |

|                      |                                                    | -    | 1.8 | 2.3  |       | I <sub>PA/B</sub> = 3.0A |

## **Aperture DAC Characteristics**

(Over operating conditions unless otherwise specified,  $V_{LL}$  = +2.5V,  $V_{DD}$  = +5V,  $R_{FB}$  = 71.1k $\Omega$ ,  $T_{A}$  = 25°C)

| Sym                 | Parameter                       | Min  | Тур | Max | Units | Conditions |

|---------------------|---------------------------------|------|-----|-----|-------|------------|

| Reso                | Resolution                      | -    | 8   | 8   | Bits  |            |

| E <sub>LINEAR</sub> | Linearity error                 | -    | 1.0 | 3.0 | %     | ±% of FSR  |

| E <sub>DIFF</sub>   | Differential nonlinearity error | -    | 0.6 | 1.0 | %     | ±% of FSR  |

| MON                 | Monotonicity                    | -    | 8   | 8   | Bits  |            |

| V <sub>REF</sub>    | External reference voltage      | 1.25 | -   | 2.5 | V     |            |

Clock and Data Input/Output Characteristics (Over operating conditions unless otherwise specified,  $V_{LL}$  = +2.5V,  $V_{DD}$  = +5V,  $R_{FB}$  = 71.1k $\Omega$ ,  $T_A$  = 25°C)

| Sym             | Parameter                 | Min                | Тур | Max                | Units | Conditions               |

|-----------------|---------------------------|--------------------|-----|--------------------|-------|--------------------------|

| V <sub>IH</sub> | Input logic high voltage  | 0.8V <sub>LL</sub> | -   | V <sub>LL</sub>    | V     |                          |

| V <sub>IL</sub> | Input logic low voltage   | 0                  | -   | 0.2V <sub>LL</sub> | V     |                          |

| I <sub>IH</sub> | Input logic high current  | -                  | -   | 1.0                | μA    |                          |

| I               | Input logic low current   | -1.0               | -   | -                  | μA    |                          |

| C <sub>IN</sub> | Input capacitance         | -                  | 2.0 | -                  | pF    |                          |

| I <sub>OH</sub> | Output logic high current | -                  | -   | -5.0               | mA    |                          |

| I <sub>OL</sub> | Output logic low current  | -                  | -   | 5.0                | mA    |                          |

| V <sub>OH</sub> | Output logic high voltage | 1.95               | -   | -                  | V     | I <sub>OH</sub> = -5.0mA |

| V <sub>OL</sub> | Output logic low voltage  | -                  | -   | 0.35               | V     | I <sub>OL</sub> = 5.0mA  |

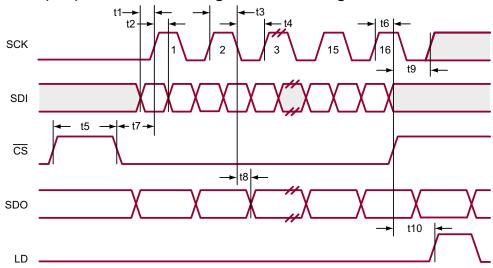

#### **AC Electrical Characteristics**

(Over operating conditions unless otherwise specified,  $V_{LL}$  = +2.5V,  $V_{DD}$  = +5V,  $R_{FB}$  = 71.1k $\Omega$ ,  $T_A$  = 25°C)

| Sym             | Parameter                                   | Min | Тур  | Max  | Units | Conditions                                     |

|-----------------|---------------------------------------------|-----|------|------|-------|------------------------------------------------|

| t <sub>st</sub> | DAC to output setup time                    | -   | -    | 10   | μs    | All caps 10nF, DAC = 0 to 255, settle to 1LSB, |

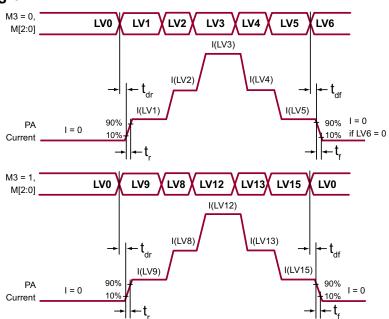

| t <sub>r</sub>  | Output current rise time                    | _   | 2.0  | 3.0  |       |                                                |

| t <sub>f</sub>  | Output current fall time                    | -   | 2.0  | 3.0  | ne    | With $1.0\Omega$ resistor load to $V_{DD}$ ,   |

| t <sub>dr</sub> | Input to output delay on rise               | _   | 4.0  | 5.0  | ns    | DAC = 85, V <sub>REF</sub> = 2.5V, LV=127      |

| t <sub>df</sub> | Input to output delay on fall               | -   | 4.0  | 5.0  |       |                                                |

| t <sub>M</sub>  | Delay time matching                         | -   | ±2.0 | ±3.0 | ns    | From PA to PB and device to device             |

| t               | Output jitter                               | _   | 50   | -    | ps    |                                                |

| t <sub>1</sub>  | SDI valid to SCK setup time                 | 0   | 2.0  | -    |       | See serial interface timing diagram            |

| t <sub>2</sub>  | SDI valid to SCK hold time                  | 4.0 | -    | -    | ns    |                                                |

| t <sub>3</sub>  | SCK high time % of 1/f <sub>CLK</sub>       | 45  | -    | 55   | %     | See sorial interfess timing diagram            |

| t <sub>4</sub>  | SCK low time % of 1/f <sub>CLK</sub>        | 45  | -    | 55   | 70    | See serial interface timing diagram            |

| t <sub>5</sub>  | CS pulse width                              | 4.0 | -    | -    |       |                                                |

| t <sub>6</sub>  | LSB SCK high to CS high                     | 7.0 | -    | -    |       |                                                |

| t <sub>7</sub>  | CS low to SCK high                          | 7.0 | -    | -    |       |                                                |

| t <sub>8</sub>  | SDO propagation delay from SCK failing edge |     |      | 10   | ns    | See serial interface timing diagram            |

| t <sub>9</sub>  | CS high to SCK rising edge                  | 7.0 | -    | -    |       |                                                |

| t <sub>10</sub> | CS high to LD rising edge                   | 10  | -    | -    |       |                                                |

## **AC Electrical Characteristics**

| Sym                 | Parameter                      | Min | Тур  | Max  | Units | Conditions |

|---------------------|--------------------------------|-----|------|------|-------|------------|

| f <sub>sck</sub>    | Serial clock maximum frequency | 40  | 50   | _    | MHz   |            |

| t <sub>CSR</sub>    | Clock input slew rate          | 1.0 | _    | _    | V/ns  |            |

| t <sub>DSR</sub>    | Control / data input slew rate | 1.0 | _    | _    | V/ns  |            |

| THD                 | Total harmonic distortion      | _   | -45  | -40  | dB    |            |

| t <sub>EN-Off</sub> | EN fall to PA/PB turn-off time | -   | 5.0  | 8.0  | ns    | 50% to 90% |

| t <sub>EN-On</sub>  | EN rise to PA/PB turn-on time  | -   | 13.5 | 20.0 | μs    | 50% to 10% |

## **DAC Input and Output Description**

| MSB | DAC Value Register |    |    |    | er |    | LSB | PA or PB Output Current                             |

|-----|--------------------|----|----|----|----|----|-----|-----------------------------------------------------|

| D7  | D6                 | D5 | D4 | D3 | D2 | D1 | D0  | 1 A of 1 B Output Ourrent                           |

| 0   | 0                  | 0  | 0  | 0  | 0  | 0  | 0   | (0/255)I <sub>MAX-A/B</sub> + I <sub>OO-A/B</sub>   |

| 0   | 0                  | 0  | 0  | 0  | 0  | 0  | 1   | (1/255)I <sub>MAX-A/B</sub> + I <sub>OO-A/B</sub>   |

| 0   | 1                  | 1  | 1  | 1  | 1  | 1  | 1   | (127/255)I <sub>MAX-A/B</sub> + I <sub>OO-A/B</sub> |

| 1   | 0                  | 0  | 0  | 0  | 0  | 0  | 0   | (128/255)I <sub>MAX-A/B</sub> + I <sub>OO-A/B</sub> |

| 1   | 1                  | 1  | 1  | 1  | 1  | 1  | 0   | (254/255)I <sub>MAX-A/B</sub> + I <sub>OO-A/B</sub> |

| 1   | 1                  | 1  | 1  | 1  | 1  | 1  | 1   | (255/255)I <sub>MAX-A/B</sub> + I <sub>OO-A/B</sub> |

## **Output Current Level Control Data Register LAx or LBx**

| MSB | Curren | t Level D | ata Regis | ster LAx | or LBx | LSB | Potio of full cools | Output Bolovity Control |

|-----|--------|-----------|-----------|----------|--------|-----|---------------------|-------------------------|

| D6  | D5     | D4        | D3        | D2       | D1     | D0  | Ratio of full scale | Output Polarity Control |

| 1   | 1      | 1         | 1         | 1        | 1      | 1   | 127/127             |                         |

| 1   | 1      | 1         | 1         | 1        | 1      | 0   | 126/127             | M3 = 0 output to PA     |

|     |        |           |           |          |        |     |                     | M3 = 1 output to PB     |

| 0   | 0      | 0         | 0         | 0        | 0      | 1   | 1/127               | - me reacparter B       |

| 0   | 0      | 0         | 0         | 0        | 0      | 0   | 0                   |                         |

## **Fast Output Current Level Control Pin Description**

| Input Control Pin Name |    |    |    | PAM           | Description                         |

|------------------------|----|----|----|---------------|-------------------------------------|

| M3                     | M2 | M1 | MO | Current Level | Description                         |

| 0                      | 0  | 0  | 0  | LV0           | PA & PB Both Off, Zero Current      |

| 0                      | 0  | 0  | 1  | LV1           | Select LV1 Current Magnitude to PA  |

| 0                      | 0  | 1  | 0  | LV2           | Select LV2 Current Magnitude to PA  |

| 0                      | 0  | 1  | 1  | LV3           | Select LV3 Current Magnitude to PA  |

| 0                      | 1  | 0  | 0  | LV4           | Select LV4 Current Magnitude to PA  |

| 0                      | 1  | 0  | 1  | LV5           | Select LV5 Current Magnitude to PA  |

| 0                      | 1  | 1  | 0  | LV6           | Select LV6 Current Magnitude to PA  |

| 0                      | 1  | 1  | 1  | LV7           | Select LV7 Current Magnitude to PA  |

| 1                      | 0  | 0  | 0  | LV8           | Select LV8 Current Magnitude to PB  |

| 1                      | 0  | 0  | 1  | LV9           | Select LV9 Current Magnitude to PB  |

| 1                      | 0  | 1  | 0  | LV10          | Select LV10 Current Magnitude to PB |

| 1                      | 0  | 1  | 1  | LV11          | Select LV11 Current Magnitude to PB |

| 1                      | 1  | 0  | 0  | LV12          | Select LV12 Current Magnitude to PB |

| 1                      | 1  | 0  | 1  | LV13          | Select LV13 Current Magnitude to PB |

| 1                      | 1  | 1  | 0  | LV14          | Select LV14 Current Magnitude to PB |

| 1                      | 1  | 1  | 1  | LV15          | Select LV15 Current Magnitude to PB |

#### Note:

Turning on PA & PB simultaneously can cause over-current and permanent damage to the IC, high voltage MOSFETs, or to the transformer.

## **SPI Control Registers Description**

| Data          | C1 | C0 | RA3 | RA2 | RA1 | RA0 | D9                          | D8 | D7 | D6 D5 D4 D3 D2 D1 D0                   |  |  |  |  |

|---------------|----|----|-----|-----|-----|-----|-----------------------------|----|----|----------------------------------------|--|--|--|--|

|               | 0  | 0  | 0   | 0   | 0   | 0   | Х                           | S1 |    | DAC[7:0] Data Write                    |  |  |  |  |

|               | 0  | 0  | 0   | 0   | 0   | 1   | Х                           | Х  | Х  | LV1[6:0] PAM current Level Data Write  |  |  |  |  |

|               | 0  | 0  | 0   | 0   | 1   | 0   | Х                           | Х  | Х  | LV2[6:0] PAM current Level Data Write  |  |  |  |  |

| Write<br>Data | 0  | 0  | 0   | 0   | 1   | 1   | Х                           | х  | х  | LV3[6:0] PAM current Level Data Write  |  |  |  |  |

|               | 0  | 0  | 0   | 1   | 0   | 0   | Х                           | Х  | Х  | LV4[6:0] PAM current Level Data Write  |  |  |  |  |

|               | 0  | 0  | 0   | 1   | 0   | 1   | Х                           | Х  | Х  | LV5[6:0] PAM current Level Data Write  |  |  |  |  |

|               | 0  | 0  | 0   | 1   | 1   | 0   | Х                           | Х  | Х  | LV6[6:0] PAM current Level Data Write  |  |  |  |  |

|               | 0  | 0  | 0   | 1   | 1   | 1   | Х                           | Х  | Х  | LV7[6:0] PAM current Level Data Write  |  |  |  |  |

|               | 0  | 0  | 1   | 0   | 0   | 0   | Х                           | Х  | Х  | LV8[6:0] PAM current Level Data Write  |  |  |  |  |

|               | 0  | 0  | 1   | 0   | 0   | 1   | Х                           | х  | Х  | LV9[6:0] PAM current Level Data Write  |  |  |  |  |

|               | 0  | 0  | 1   | 0   | 1   | 0   | Х                           | Х  | Х  | LV10[6:0] PAM current Level Data Write |  |  |  |  |

|               | 0  | 0  | 1   | 0   | 1   | 1   | Х                           | Х  | Х  | LV11[6:0] PAM current Level Data Write |  |  |  |  |

|               | 0  | 0  | 1   | 1   | 0   | 0   | Х                           | Х  | Х  | LV12[6:0] PAM current Level Data Write |  |  |  |  |

|               | 0  | 0  | 1   | 1   | 0   | 1   | Х                           | Х  | Х  | LV13[6:0] PAM current Level Data Write |  |  |  |  |

|               | 0  | 0  | 1   | 1   | 1   | 0   | Х                           | Х  | Х  | LV14[6:0] PAM current Level Data Write |  |  |  |  |

|               | 0  | 0  | 1   | 1   | 1   | 1   | Х                           | Х  | Х  | LV15[6:0] PAM current Level Data Write |  |  |  |  |

|               | 0  | 1  | 0   | 0   | 0   | 0   | Х                           | S1 |    | DAC[7:0] Data Read                     |  |  |  |  |

|               | 0  | 1  | 0   | 0   | 0   | 1   | Х                           | Х  | Х  | LV1[6:0] PAM current Level Data Read   |  |  |  |  |

|               | 0  | 1  | 0   | 0   | 1   | 0   | Х                           | Х  | Х  | LV2[6:0] PAM current Level Data Read   |  |  |  |  |

|               | 0  | 1  | 0   | 0   | 1   | 1   | Х                           | Х  | Х  | LV3[6:0] PAM current Level Data Read   |  |  |  |  |

|               | 0  | 1  | 0   | 1   | 0   | 0   | Х                           | Х  | Х  | LV4[6:0] PAM current Level Data Read   |  |  |  |  |

|               | 0  | 1  | 0   | 1   | 0   | 1   | Х                           | Х  | Х  | LV5[6:0] PAM current Level Data Read   |  |  |  |  |

| Read          | 0  | 1  | 0   | 1   | 1   | 0   | Х                           | Х  | Х  | LV6[6:0] PAM current Level Data Read   |  |  |  |  |

| Back          | 0  | 1  | 0   | 1   | 1   | 1   | Х                           | Х  | Х  | LV7[6:0] PAM current Level Data Read   |  |  |  |  |

| Data          | 0  | 1  | 1   | 0   | 0   | 0   | Х                           | Х  | Х  | LV8[6:0] PAM current Level Data Read   |  |  |  |  |

|               | 0  | 1  | 1   | 0   | 0   | 1   | Х                           | Х  | Х  | LV9[6:0] PAM current Level Data Read   |  |  |  |  |

|               | 0  | 1  | 1   | 0   | 1   | 0   | Х                           | Х  | Х  | LV10[6:0] PAM current Level Data Read  |  |  |  |  |

|               | 0  | 1  | 1   | 0   | 1   | 1   | Х                           | Х  | Х  | LV11[6:0] PAM current Level Data Read  |  |  |  |  |

|               | 0  | 1  | 1   | 1   | 0   | 0   | Х                           | Х  | Х  | LV12[6:0] PAM current Level Data Read  |  |  |  |  |

|               | 0  | 1  | 1   | 1   | 0   | 1   | Х                           | Х  | Х  | LV13[6:0] PAM current Level Data Read  |  |  |  |  |

|               | 0  | 1  | 1   | 1   | 1   | 0   | Х                           | Х  | Х  | LV14[6:0] PAM current Level Data Read  |  |  |  |  |

|               | 0  | 1  | 1   | 1   | 1   | 1   | Х                           | Х  | Х  | LV15[6:0] PAM current Level Data Read  |  |  |  |  |

| PWDN          | 1  | 0  | Х   | Х   | Х   | Х   | D[9:0] = X Power Down State |    |    |                                        |  |  |  |  |

| N.A.          | 1  | 1  | Х   | Х   | Х   | Х   | (Reserved, Do Not Use)      |    |    |                                        |  |  |  |  |

### Note:

S1 is Tx polarity swapping control bit. When S1 =  $0 LV1\sim7$  output to PA and  $LV8\sim15$  output to PB, when S1 =  $1 LV1\sim7$  output to PB and  $LV8\sim15$  output to PA.

### Serial Port Interface (SPI) Read Write Timing for Control Register

### **Tx Output Timing Diagram**

## PA and PB Output Current Equations

The in-phase PA and 180° PB output sinking current magnitudes  $\rm I_A$  and  $\rm I_B$  can be calculated by the following equations.

$$I_{A} = \frac{48 \cdot V_{REF} \cdot DAC \cdot (2^{6} - 1) \cdot \frac{LAx}{127}}{9 \cdot R_{FB}}$$

$$I_{B} = \frac{48 \cdot V_{REF} \cdot DAC \cdot (2^{6} - 1) \cdot \frac{LBx}{127}}{9 \cdot R_{FB}}$$

Where the  $V_{\rm REF}$  is the voltage reference, DAC is the decimal value of the data in the DAC register,  $R_{\rm FB}$  is the setting resistor value in ohms, LAx or LBx is the decimal value of the data in the level register.

The values of the results from the equations represent the magnitude of the output current. The current flow into the port PA or PB is controlled by M0, M1, M2 or M3 are turned on. Note that the maximum full scale peak current at PA or PB port only can be obtained at DAC = 255,  $V_{REF}$  = 2.5V,  $R_{FB}$  = 71.1k $\Omega$ , LAx[6:0] = 127 for PA or LBx[6:0] = 127 for PR

## **Pin Description**

| Pin | Name | Description                                                                                               |

|-----|------|-----------------------------------------------------------------------------------------------------------|

| 1   | KA   | Kelvin connection A                                                                                       |

| 2   | GND  | High current output ground                                                                                |

| 3   | C1A  | Bypass cap to KA, 10nF low ESR X7R ceramic cap.                                                           |

| 4   | GND  | High current output ground                                                                                |

| 5   | VDD  | Supplies voltage of the gate driver and internal analog circuit.                                          |

| 6   | C3A  | Bypass cap to GND of Pin #7, 10nF low ESR X7R ceramic cap.                                                |

| 7   | GND  | High current output ground                                                                                |

| 8   | VLL  | Supply voltage of logic circuit.                                                                          |

| 9   | DGND | Digital logic ground.                                                                                     |

| 10  | SCK  | Serial clock input.                                                                                       |

| 11  | SDI  | Serial data input.                                                                                        |

| 12  | M3   | Control logic for selecting output current level. See "Fast Output Current Level Control Pin Description" |

| 13  | M2   | Control logic for selecting output current level. See "Fast Output Current Level Control Pin Description" |

| 14  | M1   | Control logic for selecting output current level. See "Fast Output Current Level Control Pin Description" |

| 15  | MO   | Control logic for selecting output current level. See "Fast Output Current Level Control Pin Description" |

| 16  | VDD  | Supplies voltage of the gate driver and internal analog circuit.                                          |

| 17  | AGND | Analog reference ground.                                                                                  |

| 18  | SDO  | Serial data output.                                                                                       |

| 19  | CS   | Serial chip select, active low, and buffer register loading clock on rising edge.                         |

| 20  | LD   | DAC data register loading clock on rising edge.                                                           |

| 21  | EN   | Enable, EN = Low, PA = PB = Hi-Z and all internal registers freeze until next clock rising edge.          |

| 22  | VREF | External reference voltage input.                                                                         |

| 23  | RFB  | Resistor to GND, 71.1kΩ 0.1% for the best accuracy.                                                       |

| 24  | GND  | High current output ground.                                                                               |

| 25  | C3B  | Bypass cap to GND of Pin #24, 10nF low ESR X7R ceramic cap.                                               |

| 26  | VDD  | Supplies voltage of the gate driver and internal analog circuit.                                          |

| 27  | GND  | High current output ground.                                                                               |

| 28  | C1B  | Bypass cap to KB, 10nF low ESR X7R ceramic cap.                                                           |

| 29  | GND  | High current output ground.                                                                               |

| 30  | KB   | Kelvin connection B.                                                                                      |

| 31  | C2B  | Bypass cap to KB, 10nF low ESR X7R ceramic cap.                                                           |

| 32  | PB   | Current sinking source driver output B, external Schottky diode to VDD.                                   |

| 33  | PB   | Current sinking source driver output B, external Schottky diode to VDD.                                   |

| 34  | PB   | Current sinking source driver output B, external Schottky diode to VDD.                                   |

| 35  | VSUB | Substrate voltage must connect to the lowest potential of the IC, the ground.                             |

| 36  | VSUB | Substrate voltage must connect to the lowest potential of the IC, the ground.                             |

| 37  | PA   | Current sinking source driver output A, external Schottky diode to VDD.                                   |

| 38  | PA   | Current sinking source driver output A, external Schottky diode to VDD.                                   |

| 39  | PA   | Current sinking source driver output A, external Schottky diode to VDD.                                   |

| 40  | C2A  | Bypass cap to KA, 10nF low ESR X7R ceramic cap.                                                           |

## Notes:

- Pin # 35 & #36 are V<sub>SUB</sub> connected to the center thermal pad internally in the package.

All bypass capacitors need be very close to the pins

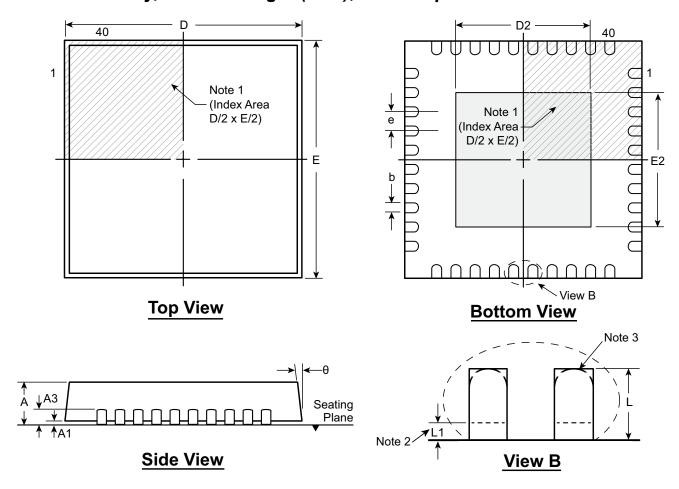

## 40-Lead QFN Package Outline (K7)

## 5.00x5.00mm body, 0.80mm height (max), 0.40mm pitch

#### Notes:

- A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

- 2. Depending on the method of manufacturing, a maximum of 0.15mm pullback (L1) may be present.

- 3. The inner tip of the lead may be either rounded or square.

| Symbol         |     | Α    | A1   | А3          | b    | D     | D2                | E     | E2                | е           | L                 | L1   | θ          |

|----------------|-----|------|------|-------------|------|-------|-------------------|-------|-------------------|-------------|-------------------|------|------------|

| Dimension (mm) | MIN | 0.70 | 0.00 | 0.20<br>REF | 0.15 | 4.85* | 3.45              | 4.85* | 3.45              | 0.40<br>BSC | 0.25 <sup>†</sup> | 0.00 | <b>0</b> ° |

|                | NOM | 0.75 | 0.02 |             | 0.20 | 5.00  | 3.60              | 5.00  | 3.60              |             | 0.35 <sup>†</sup> | -    | -          |

|                | MAX | 0.80 | 0.05 |             | 0.25 | 5.15* | 3.70 <sup>†</sup> | 5.15* | 3.70 <sup>†</sup> |             | 0.45 <sup>†</sup> | 0.15 | 14º        |

JEDEC Registration MO-220, Variation WHHE-1, Issue K, June 2006

Drawings not to scale.

Supertex Doc. #: DSPD-40QFNK75X5P040, Version C041009.

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="http://www.supertex.com/packaging.html">http://www.supertex.com/packaging.html</a>.)

**Supertex inc.** does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate "product liability indemnification insurance agreement." **Supertex inc.** does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the **Supertex inc.** (website: http://www.supertex.com)

©2012 **Supertex inc.** All rights reserved. Unauthorized use or reproduction is prohibited.

<sup>\*</sup> This dimension is not specified in the JEDEC drawing.

<sup>†</sup> This dimension differs from the JEDEC drawing.