The Future of Analog IC Technology

# DESCRIPTION

The MP6519 is a monolithic, step-down, current-source driver for applications that require accurate and fast current-response control. The MP6519 achieves up to 5A of output current with excellent load and line regulation over a wide input supply range.

The four integrated MOSFET H-bridge control provide a fast dynamic load response and an ultra-high efficiency solution. For ease of use, the output polarity can be controlled by pulling MODE high or low.

By setting the full-scale output current through an external resistor, the output current can be dimmed by the PWM input signal from 0 - 100% of the full-scale current range.

Full protection features include load open, loadshort protection, over-current protection (OCP), over-temperature protection (OTP), and input over-voltage protection (OVP). The MP6519 is available in a QFN-19 (3mmx3mm) package.

# *MP6519* 2.5V - 28V, 5A, H-Bridge Current Regulator

## **FEATURES**

- Wide 2.5V to 28V Operating Input Range

- Up to 5A Output Load Current

- ± 2% Accuracy at Full-Scale Reference

- $65m\Omega$  R<sub>DS(ON)</sub> for Each MOSFET of H-Bridge

- 100% Duty Cycle Operation of H-Bridge

- 30kHz to 300kHz Programmable Switching Frequency

- 20kHz 100kHz PWM Input for Current Regulation

- Programmable Full-Scale Current

- Up to 94% Efficiency

- Selectable Current Polarity Mode

- Switching Auto-Disabled by PWM Input Detection

- 1µA Shutdown Mode

- Inherent Open-Load Protection

- Cycle-by-Cycle Over-Current Protection (OCP)

- Output Short-Circuit Protection (SCP)

- Input Over-Voltage Protection (OVP)

- Over-Temperature Shutdown

- Available in a QFN-19 (3mmx3mm) Package

# **APPLICATIONS**

- Current Regulators

- DC Motors

- Solenoid/Actuators

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

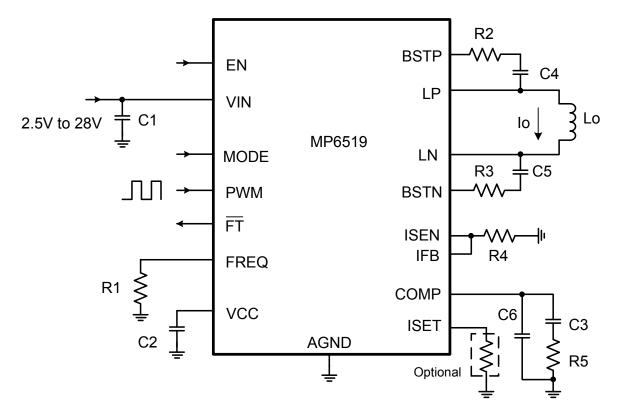

# **TYPICAL APPLICATION**

## **ORDERING INFORMATION**

| Part Number* | Package          | Top Marking |

|--------------|------------------|-------------|

| MP6519GQ     | QFN-19 (3mmx3mm) | See Below   |

\* For Tape & Reel, add suffix –Z (e.g. MP6519GQ–Z)

## **TOP MARKING**

# ARUY LLL

ARU: Product code of MP6519GQ Y: Year code LLL: Lot number

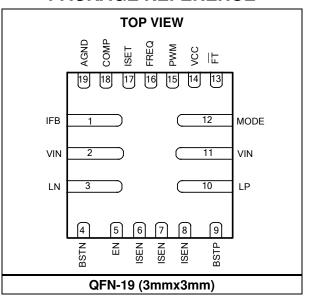

### PACKAGE REFERENCE

## ABSOLUTE MAXIMUM RATINGS (1)

| Supply voltage (V <sub>IN</sub> ) | 35V                                       |

|-----------------------------------|-------------------------------------------|

| V <sub>LP</sub> , V <sub>LN</sub> |                                           |

| V <sub>BSTP</sub>                 | V <sub>LP</sub> + 6V                      |

| V <sub>BSTN</sub>                 | V <sub>LN</sub> + 6V                      |

| All other pins                    |                                           |

| Continuous power dissipation      | ו (T <sub>A</sub> = +25°C) <sup>(2)</sup> |

| QFN-19 (3mmx3mm)                  | 2.5W                                      |

| Junction temperature              | 150°C                                     |

| Lead temperature                  |                                           |

| Storage temperature               | 65°C to +150°C                            |

#### **Recommended Operating Conditions** <sup>(3)</sup>

Supply voltage ( $V_{IN}$ ) ...... 2.5V to 28V Operating junction temp ( $T_J$ ).....-40°C to +125°C

### Thermal Resistance <sup>(4)</sup> $\theta_{JA}$ $\theta_{JC}$

QFN-19 (3mmx3mm)...... 50 ...... 8 ....°C/W

#### NOTES:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub>(MAX), the junction-to-ambient thermal resistance θ<sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub>(MAX)=(T<sub>J</sub>(MAX)-T<sub>A</sub>)/ θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operation conditions.

- 4) Measured on JESD51-7 4-layer board.

# **ELECTRICAL CHARACTERISTICS**

VIN = 12V,  $T_A = +25^{\circ}C$ , unless otherwise noted.

| Parameters                        | Symbol                        | Condition                   | Min | Тур  | Max  | Units |

|-----------------------------------|-------------------------------|-----------------------------|-----|------|------|-------|

| Supply Voltage                    | •                             |                             |     |      |      |       |

| VIN operating range               | VIN                           |                             | 2.5 |      | 28   | V     |

| Turn-on threshold                 | Vin_on                        | VIN rising edge             |     | 2.3  | 2.45 | V     |

| Turn-on hysteretic voltage        | V <sub>IN_HY</sub>            |                             |     | 0.15 |      | V     |

| IC Supply                         |                               |                             |     |      |      |       |

| Shutdown current                  | IIN_SD                        | EN = low                    |     |      | 1    | μA    |

| Quiescent current                 | I <sub>IN_SBY</sub>           | Standby mode                |     | 370  | 450  | μA    |

| VCC regulator voltage             | Vvcc                          | VIN > 5.2V                  | 4.5 | 5    | 5.5  | V     |

| VCC regulator drop output voltage |                               | VIN < 5V, 20mA load         |     | 100  |      | mV    |

| Logic                             |                               |                             |     |      |      |       |

| EN high threshold                 | $V_{\text{EN}_{\text{High}}}$ |                             |     |      | 1.5  | V     |

| EN low threshold                  | V <sub>EN_Low</sub>           |                             | 0.4 |      |      | V     |

| MODE input high threshold         | $V_{\text{EN}_{\text{High}}}$ |                             |     |      | 1.5  | V     |

| MODE input low threshold          | V <sub>EN_Low</sub>           |                             | 0.4 |      |      | V     |

| PWM high threshold                | $V_{PWM_{High}}$              |                             |     |      | 1.5  | V     |

| PWM low threshold                 | $V_{PWM\_Low}$                |                             | 0.4 |      |      | V     |

| IC start-up delay                 | T <sub>delay</sub>            | EN active to switching      |     | 230  | 350  | μs    |

| Switching Frequency               |                               |                             |     |      |      |       |

| Switching frogueney               | fs                            | $R_{FREQ} = 75k\Omega$      | 255 | 300  | 345  | kHz   |

| Switching frequency               |                               | $R_{FREQ} = 750 k\Omega$    | 22  | 30   | 38   | kHz   |

| Current Reference                 |                               |                             |     |      |      |       |

| Current reference coources/       | V <sub>REF_FB</sub>           | V <sub>REF_FB</sub> = 200mV | 196 | 200  | 204  | mV    |

| Current reference accuracy        |                               | V <sub>REF_FB</sub> = 50mV  | 47  | 50   | 53   | mV    |

| Loop Compensation                 |                               |                             |     |      |      |       |

| Transconductance                  | Gea                           |                             |     | 270  |      | μA/V  |

| Max source current                |                               |                             |     | 50   |      | μA    |

| Max sink current                  |                               |                             |     | 50   |      | μA    |

| Power MOSFET                      |                               |                             |     |      |      |       |

| High-side MOSFET on resistance    |                               |                             | 42  | 65   | 93   | mΩ    |

| Low-side MOSFET on resistance     |                               |                             | 42  | 65   | 93   | mΩ    |

| Minimum on time                   |                               |                             |     | 200  |      | ns    |

| Bootstrap for High-Side Driver    |                               |                             |     |      |      |       |

| Forward voltage for BST charge    |                               |                             |     | 0.5  |      | V     |

| BST UVLO                          |                               | Rising edge                 |     | 2    |      | V     |

|                                   |                               |                             |     |      |      |       |

# ELECTRICAL CHARACTERISTICS (continued)

VIN = 12V,  $T_A = +25^{\circ}$ C, unless otherwise noted.

| Parameters                       | Symbol | Condition                       | Min  | Тур | Max | Units |

|----------------------------------|--------|---------------------------------|------|-----|-----|-------|

| Protection                       | -      |                                 |      |     |     |       |

| Hiccup over-current threshold    |        | RISET float                     | 255  | 300 | 345 | mV    |

| Load short hiccup recovery timer |        |                                 |      | 1   |     | ms    |

| Latch-off over-current threshold |        | RISET float, RSEN = $40m\Omega$ |      | 13  |     | Α     |

| Input over-voltage threshold     | VINOVP |                                 | 28.2 | 30  | 31  | V     |

| Thermal shutdown (5)             |        |                                 |      | 150 |     | °C    |

| Thermal shutdown hysteresis      |        |                                 |      | 20  |     | °C    |

NOTE:

5) Guaranteed by design.

# **TYPICAL PERFORMANCE CHARACTERISTICS**

### MP6519 - 2.5V TO 28V, 5A, H-BRIDGE CURRENT REGULATOR

## **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

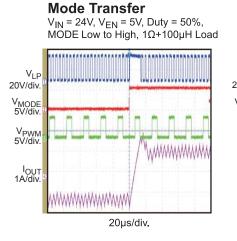

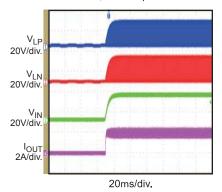

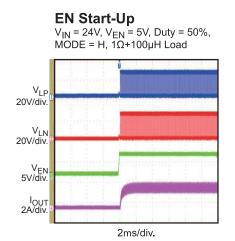

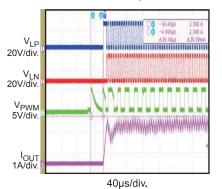

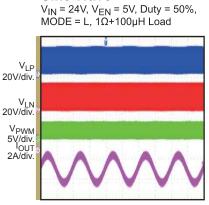

$V_{IN} = 24V, V_{EN} = 5V, Duty = 50\%, MODE High to Low, 1\Omega+100\muH Load V_{LP}$

**Mode Transfer**

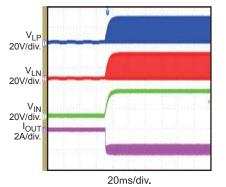

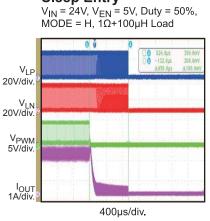

### VIN Start-Up

$V_{IN}$  = 24V,  $V_{EN}$  = 5V, Duty = 50%, MODE = H, 1 $\Omega$ +100µH Load

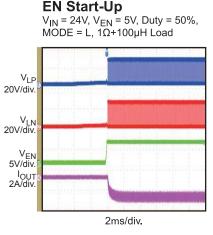

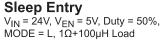

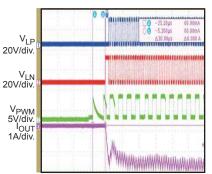

$$\label{eq:VIN_start-Up} \begin{split} & \text{VIN Start-Up} \\ & \text{V}_{\text{IN}} = 24\text{V}, \, \text{V}_{\text{EN}} = 5\text{V}, \, \text{Duty} = 50\%, \\ & \text{MODE} = \text{L}, \, 1\Omega\text{+}100\mu\text{H Load} \end{split}$$

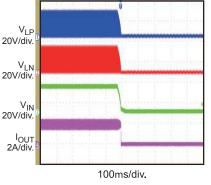

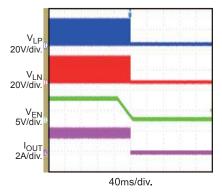

VIN Shutdown  $V_{IN} = 24V, V_{EN} = 5V, Duty = 50\%,$ MODE = H, 1 $\Omega$ +100 $\mu$ H Load

VIN Shutdown  $V_{IN}$  = 24V,  $V_{EN}$  = 5V, Duty = 50%, MODE = L, 1 $\Omega$ +100 $\mu$ H Load

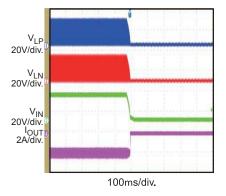

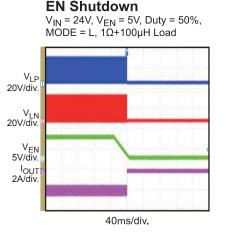

**EN Shutdown**

$V_{IN}$  = 24V,  $V_{EN}$  = 5V, Duty = 50%, MODE = H, 1 $\Omega$ +100 $\mu$ H Load

MP6519 Rev.1.01 3/10/2020 www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2020 MPS. All Rights Reserved.

### MP6519 – 2.5V TO 28V, 5A, H-BRIDGE CURRENT REGULATOR

## **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

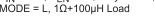

Sleep Entry

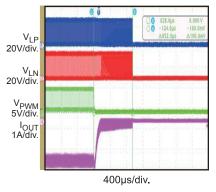

Sleep Recovery  $V_{IN} = 24V, V_{EN} = 5V, Duty = 50\%,$ MODE = H,  $1\Omega$ +100µH Load

Sleep Recovery

$V_{IN}$  = 24V,  $V_{EN}$  = 5V, Duty = 50%, MODE = L, 1 $\Omega$ +100µH Load

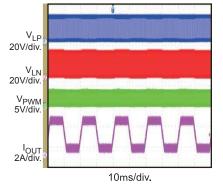

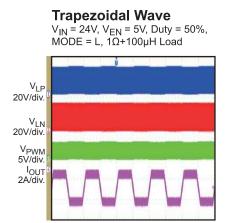

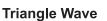

**Trapezoidal Wave**

$V_{IN}$  = 24V,  $V_{EN}$  = 5V, Duty = 50%, MODE = H, 1 $\Omega$ +100 $\mu$ H Load

10ms/div.

V<sub>PWM</sub> 5V/div.

IOUT 2A/div

$V_{IN} = 24V$ ,  $V_{EN} = 5V$ , Duty = 50%, MODE = L, 1 $\Omega$ +100 $\mu$ H Load

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2020 MPS. All Rights Reserved.

10ms/div.

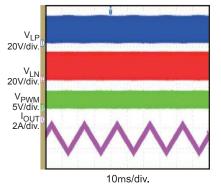

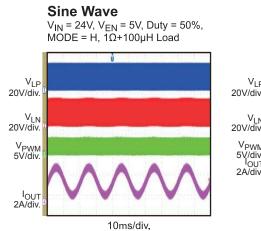

Sine Wave

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

10ms/div.

# **PIN FUNCTIONS**

| Pin #   | Name | Description                                                                                                                                                                                           |  |  |

|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1       | IFB  | Current sense signal feedback. Connect IFB and ISEN together.                                                                                                                                         |  |  |

| 2, 11   | VIN  | Input supply.                                                                                                                                                                                         |  |  |

| 3       | LN   | Negative switching node of H-bridge.                                                                                                                                                                  |  |  |

| 4       | BSTN | Bootstrap pin for LN high-side MOSFET gate driver. Connect a capacitor between BSTN and LN.                                                                                                           |  |  |

| 5       | EN   | IC enable.                                                                                                                                                                                            |  |  |

| 6, 7, 8 | ISEN | Current sense. Connect a current sensing resistor between ISEN and power ground.                                                                                                                      |  |  |

| 9       | BSTP | Bootstrap pin for LP high-side MOSFET gate driver. Connect a capacitor between BSTP and LP.                                                                                                           |  |  |

| 10      | LP   | Positive switching node of H-bridge.                                                                                                                                                                  |  |  |

| 12      | MODE | <b>Current polarity setting.</b> Assuming the current direction flowing from LP to LN is positive, drive MODE high to run the current from LP to LN; drive MODE low to run the current from LN to LP. |  |  |

| 13      | FT   | Fault indication output. FT is active low for fault conditions.                                                                                                                                       |  |  |

| 14      | VCC  | 5V LDO output for internal driver and logic.                                                                                                                                                          |  |  |

| 15      | PWM  | <b>PWM signal input for current dimming.</b> Apply a >20kHz PWM signal to PWM when used.                                                                                                              |  |  |

| 16      | FREQ | Switching frequency setting. Connect a resistor from FREQ to GND.                                                                                                                                     |  |  |

| 17      | ISET | Full-scale current reference setting. Connect a resistor to GND from ISET.                                                                                                                            |  |  |

| 18      | COMP | Loop compensation setting.                                                                                                                                                                            |  |  |

| 19      | AGND | Ground for internal logic.                                                                                                                                                                            |  |  |

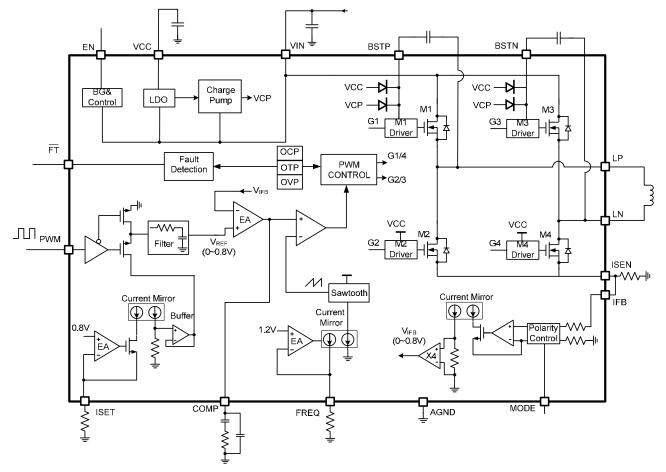

# **BLOCK DIAGRAM**

Figure 1: Functional Block Diagram

## **OPERATION**

The MP6519 is a current driver for applications that need to control the accurate load current and fast dynamic current response. The MP6519 works in step-down mode with four fully integrated MOSFET H-bridges to provide small size and high efficiency. The full-scale output current can be set by the external resistor, and the current polarity can be controlled by MODE to achieve a bidirectional current setting.

### **H-Bridge General Operation**

The MP6519 works in a four-MOSFET H-bridge topology and uses pulse-width-modulation (PWM) with average current control to achieve a bidirectional current output and fast dynamic current response. The switching frequency is programmable from 30kHz to 300kHz.

In normal operation when enabled, the MOSFETs M1 and M4 turn on and off in the same sequence, and M2 and M3 turn on and off in the same sequence. M1/M4 and M2/M3 turn on an off in complementary operation with around 25ns of dead time to avoid device damage caused by a shoot-through. There is about 200ns of minimum on-time for all of the MOSFET switches (M1/M4 and M2/M3). Assuming the output current direction is set positive by pulling MODE high, the output current sensed by M2 and M4 is sent to the error amplifier negative input. By comparing the output current feedback signal with the current reference signal at the error amplifier positive node, the error amplifier outputs an appropriate voltage value which is compared with a sawtooth signal to provide a driver signal for M1/M4 and M2/M3. The device can enter four different modes described in the following sections to control the working sequence.

#### Shutdown Mode

The MP6519 goes into shutdown mode when pulling the EN signal low. In shutdown mode, all circuits and blocks are disabled, and the MP6519 consumes less than  $1\mu$ A of shutdown current. There is about 150ns of deglitch time on EN to avoid a mistrigger.

#### Standby Mode

The MP6519 enters standby mode if either of following conditions are met:

- During start-up, the PWM signal on PWM is low while EN is high.

- After start-up in normal switching operation, the PWM signal keeps low for >1ms if EN is high.

In standby mode, the bandgap block and other control blocks begin working except for the gate drive block for the internal switching MOSFETs. This way, the device stops switching to reduce the quiescent current at no load. Meanwhile, standby mode can minimize the time that the output current tracks the reference signal of the PWM input, which comes after the EN signal. Since the MP6519 needs some time to establish the bandgap signal and other necessary control blocks, it is recommended that the PWM signal comes at least 300µs after the EN signal switches high.

#### Normal Switching Mode

If both the PWM and EN signals keep high, the MP6519 enters normal switching mode immediately. In this mode, the output feedback current closely follows the reference signal, which is received from the PWM input signal through an R-C filter (see the Current Feedback section on page 15 and the PWM Input Current Dimming section on page 14).

The H-bridge MOSFETs work in a fixed switching frequency (see the Switching Frequency Setting section on page 14). The output current polarity can be changed easily by pulling MODE high or low (see the following Current Polarity Mode section).

#### **Current Polarity Mode**

The current polarity is set by MODE. By pulling MODE high, the current is positive, and the current direction is from LP to LN. By pulling MODE low, the current is negative, and the current direction is from LN to LP. There is about 150ns of deglitch on MODE to avoid a mistrigger.

#### **Full-Scale Current Setting**

The full-scale current reference value is set by connecting a resistor between ISET and GND. When  $I_{SET}$  is floating, the full-scale current reference voltage is set to the default 200mV. If a resistor is connected between  $I_{SET}$  and GND, the full-scale current reference voltage can be reduced below 200mV to reduce power loss on the feedback resistor. The IC needs about 0.3ms to detect whether a resistor is available or not on ISET when the IC starts up for the first time. During this time, the IC is not switching. The relation of the full-scale current reference voltage and  $R_{ISET}$  is shown in Equation (1):

$$V_{\text{REF}_FULL} = 0.2^{*} \frac{40}{R_{\text{ISET}}(k\Omega)}$$

(1)

For example, if  $R_{ISET}$  is  $80k\Omega$ , the reference voltage is 100mV. For better accuracy,  $40k\Omega$  to  $80k\Omega$  is recommended to achieve a 200mV to 100mV current reference voltage.

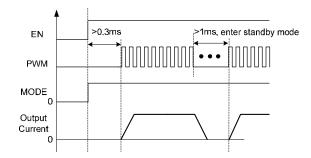

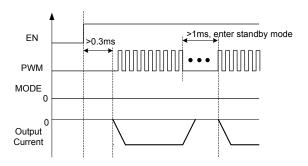

#### Start-Up Sequence

The IC needs about 0.3ms to detect whether a resistor is available or not on ISET when the IC starts up for the first time. During this time, the IC is not switching. It is recommended to apply a PWM signal at least 0.3ms after the EN signal (see Figure 2 and Figure 3).

Figure 2: Positive Output Current Mode

Figure 3: Negative Output Current Mode

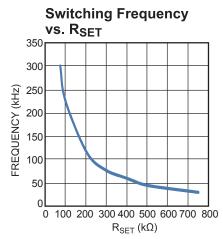

### Switching Frequency Setting

The H-bridge MOSFET switching frequency is set by FREQ by connecting a resistor between FREQ and GND. With a proper resistor value, the switching frequency can be set between 30kHz and 300kHz. A higher switching frequency leads to a smaller current ripple, but the MOSFET switching loss is larger. Therefore, a tradeoff is needed for the design. The switching frequency setting formula is shown in Equation (2):

$$f_{FREQ} = \frac{22500}{R_{FREQ}(k\Omega)}$$

(2)

#### **PWM Input Current Dimming**

If the full-scale output current reference is set, the actual output current reference sent to the error amplifier can be further controlled by applying a PWM input signal to PWM. This way, V<sub>REF FULL</sub> is chopped by the PWM input signal, and the current reference voltage is received from this chopped PWM voltage through the internal low-pass filter. For a smaller output current reference ripple, the input frequency of PWM is recommended to be 20kHz to 100kHz. Considering the full-scale reference, the relationship between the actual output current reference and duty cycle of the PWM input (D<sub>PWM</sub>) is shown in Equation (3):

$$V_{\text{REF}_{FB}} = 0.2^{*} \frac{40}{R_{\text{ISET}}(k\Omega)} * D_{\text{PWM}}$$

(3)

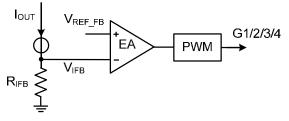

#### **Current Feedback**

The current flowing through the load is sensed through a resistor connected between IFB and GND. This sensing voltage on IFB is sent to the feedback block circuit and used to generate the average feedback voltage ( $V_{IFB}$ ), which is equal to the average output current multiplied by the sensing resistor value ( $R_{IFB}$ ).  $V_{IFB}$  is sent to the error amplifier negative node and compared with the output current reference voltage on the error amplifier jositive node. The output of the error amplifier is COMP. The COMP voltage ( $V_{COMP}$ ) is used to generate the internal MOSFET switch on and off times.

The simple block is shown in Figure 4.

#### Figure 4: Current Feedback Loop

#### VCC LDO Regulator

The IC employs an LDO regulator to provide a constant voltage (5V) at VCC. The VCC voltage is used for the internal power supply of the logic circuit and driver circuit. When the input voltage is high enough (larger than 5.2V), the VCC output is 5V. When the input voltage drops below 5V, the VCC voltage drops together with the input voltage. The dropout voltage is around 100mV. If the VCC voltage drops below 2.15V, the IC triggers a power reset sequence and shuts down. The IC resumes normal operation when VCC is higher than 2.3V.

#### High-Side MOSFET Driver

The high-side MOSFETs of M1 and M3 are Nchannel MOSFETs. When M1 and M3 turn on, a bootstrap supply voltage across BSTP and BSTN is needed. The bootstrap voltage is generated by a combination of the internal charge pump and a 5V VCC. This allows the IC to work in 100% duty cycle to provide enough driver voltage for the high-side MOSFETs (M1 and M3).

#### **Over-Current Protection (OCP)**

To provide robust protection during an overcurrent event, the IC uses a two-level protection mode.

If the current flowing through the MOSFETs is larger than 150% of the full-scale setting value during two consecutive switching cycles, the IC stops switching and triggers a power reset sequence to restart after 1ms.

If the current flowing through the MOSFETs is larger than 200% of the full-scale setting value, the IC will latch off. If the high-side MOSFET hits over-current, the high-side MOSFET is turned off immediately and the Fault pin is driven low. At the same time, the two low-side MOSFETs are turned on for several milliseconds and then the two low-side MOSFETs are turned off and IC latches off. The reverse will happen if the low-side MOSFET hits over-current where the low-side MOSFET is turned off immediately and the Fault pin is driven low. And at the same time the high-side MOSFETs turned on for are several milliseconds and then the high-side MOSFETs are turned off and IC latches off.

#### Input Over-Voltage Protection (OVP)

During operation, the energy stored in the load current is delivered to the input side during the free-wheeling time. If the input voltage and output current are high enough, the energy sent back to the input side causes the input voltage to rise up. To avoid IC damage due to a high voltage spike, the IC employs input voltage protection. If the input voltage is higher than the input over-voltage threshold for four consecutive switching cycles, the IC stops switching and latches off immediately.

#### Junction Over-Temperature Protection (OTP)

If the IC junction temperature  $(T_J)$  is higher than 150°C, the IC stops switching and resumes normal operation when  $T_J$  drops below 130°C.

### Fault Indication Output (FT)

In normal operation,  $\overline{FT}$  is a high-impedance open drain. If any fault occurs during operation,  $\overline{FT}$  is pulled low to indicate the fault condition for the external system. Recycle the input power or toggle the EN signal to remove the fault latch condition.

### Enable/Disable (EN)

To enable the IC, a logic-high signal needs to be applied to EN, and the high-level signal time needs to be higher than about  $10\mu s$ . To shut down the IC, pull EN to logic low, and the low-level signal needs to higher than 100ns.

### **APPLICATION INFORMATION**

#### **Selecting the Input Capacitor**

The input capacitor reduces the surge current drawn from the input supply and the switching noise from the device. The input capacitor impedance at the switching frequency should be less than the input source impedance to prevent the high-frequency switching current from passing through to the input. Ceramic capacitors with X5R or X7R dielectrics are recommended for their low ESR and small temperature coefficients. A higher value capacitor is helpful for reducing input voltage ripple and noise. For most applications, two  $22\mu$ F ceramic capacitors in parallel are sufficient. It is recommended to connect one capacitor on each VIN pin.

#### Setting the Full-Scale Output Current

If a resistor is connected between  $I_{SET}$  and GND, the full-scale output current reference ( $V_{REF_FULL}$ ) can be calculated with Equation (4):

$$I_{OUT} = 0.2^{*} \frac{40}{R_{ISET}(k\Omega)}^{*} \frac{1}{R_{IFB}(\Omega)}$$

(4)

If ISET is left floating, the current setting formula is as shown in Equation (5):

$$I_{OUT} = \frac{0.2}{R_{IFB}(\Omega)}$$

(5)

For example, if  $R_{ISET}$  is  $80k\Omega$ , then the reference voltage is 100mV. For better accuracy,  $40k\Omega$  to  $80k\Omega$  is recommended to achieve a 200mV to 100mV current reference voltage.

#### Setting the Feedback Resistor

The power loss of the sensing resistor can be calculated with Equation (6):

$$\mathsf{P}_{\mathsf{LOSS\_RIFB}} = \frac{\mathsf{V}_{\mathsf{REF\_FULL}}^{2}}{\mathsf{R}_{\mathsf{IFB}}(\Omega)}$$

(6)

To guarantee a current reference, the nominated power rating of the sensing resistor is recommended to be twice the calculated power loss with at least a 1% accuracy resistor.

#### Setting the Switching Frequency

A higher switching frequency leads to a smaller current ripple but a higher switching loss of the MOSFETs. Therefore, a trade-off is required for the design. The switching frequency setting can be calculated with Equation (7):

$$f_{FREQ} = \frac{22500}{R_{FREQ}(k\Omega)}$$

(7)

Since the power loss of this resistor is small, a resistor size 0603 or 0402 is sufficient.

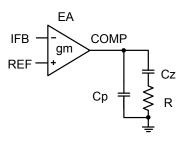

#### Selecting the Compensation Loop

The loop compensation components can be used to make the closed loop stable and achieve a better transient response (see Figure 5).

#### Figure 5: Compensation Loop

The transfer function of the loop compensation from the EA input to the EA output can be calculated with Equation (8):

$$G_{c}(s) = \frac{g_{m}}{(C_{z} + C_{p})s} \frac{(1 + sRC_{z})}{(1 + sR\frac{C_{z}C_{p}}{C_{z} + C_{p}})}$$

(8)

Where  $g_m$  is the EA transconductance value.

The transfer function zero point is made up from R and  $C_z$ . The pole point is made up from R and the value of  $C_z$  in parallel with  $C_p$ .

Usually, for an inductive load with resistance, the compensation zero can be set as the load pole made of the load inductance (L) and its resistance value. The compensation pole point is usually set around the switching frequency point to eliminate high-frequency noise. After the zero and pole point of the compensation is fixed, R can be used to increase the loop bandwidth. 1/10 to 1/5 of the switching frequency can be set as the close-loop bandwidth to achieve a good system response.

#### PCB Layout Guidelines

Efficient PCB layout is critical for stable operation. For best results, follow the guidelines below.

- 1. Place the input capacitor close to VIN.

- 2. Use a wider copper for input, output, and the GND connecting wire to improve thermal performance.

- 3. Place as many GND vias near the output and input capacitor as possible to improve thermal performance.

- 4. Keep the IFB feedback signal far away from noise sources.

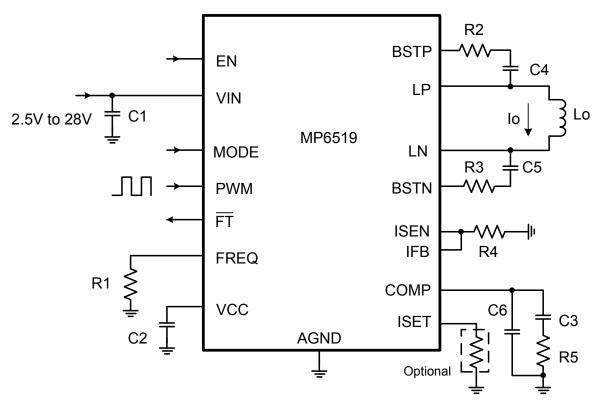

# **TYPICAL APPLICATION CIRCUIT**

**Figure 6: Typical Application**

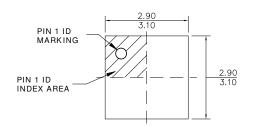

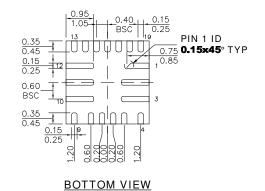

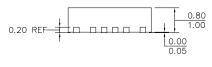

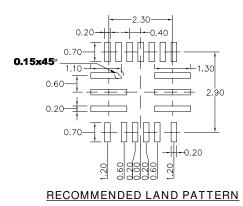

## **PACKAGE INFORMATION**

QFN-19 (3mmx3mm)

TOP VIEW

SIDE VIEW

NOTE:

LAND PATTERNS OF PIN2,3,10,11 AND 12 HAVE THE SAME SHAPE.

ALL DIMENSIONS ARE IN MILLIMETERS.

LEAD COPLANARITY SHALL BE 0.10 MILLIMETERS MAX.

JEDEC REFERENCE IS MO-220.

DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.