# High-Speed SERDES Briefcase Board

Evaluation Board for ORSO/ORT82G5, ispGDX2™ and ispPAC® Devices

User's Guide

#### Introduction

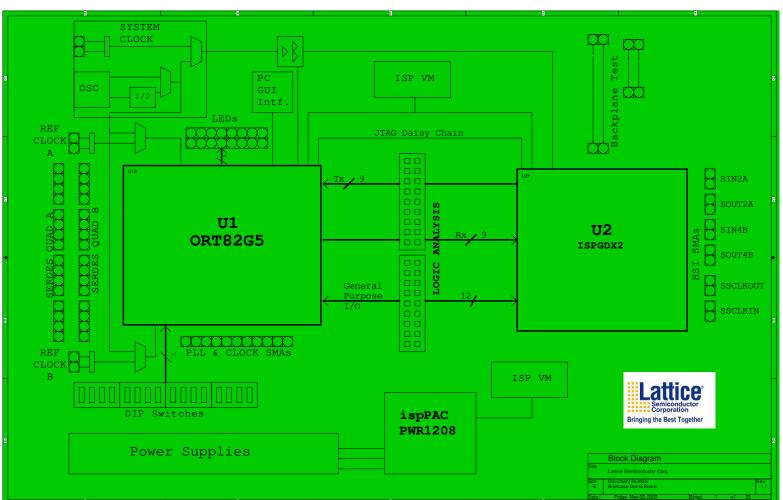

the Lattice ORSO82G5 and ORT82G5 Field Programmable grated power supply controller by the ispPAC-POWR1208. The board includes the following features: socket and test connections for evaluation of the ispGDX2-256 programmable digital crosspoint switch, and an inte-This user's guide describes the Lattice High-Speed SERDES Briefcase Board, a stand-alone evaluation board for System Chips (FPSCs). The board also contains a

- Stand-alone power source

- ispVM<sup>®</sup> programming support

- On-board reference clock sources (external clock source can be used)

- Discrete high speed interface SMA test points and clock connections

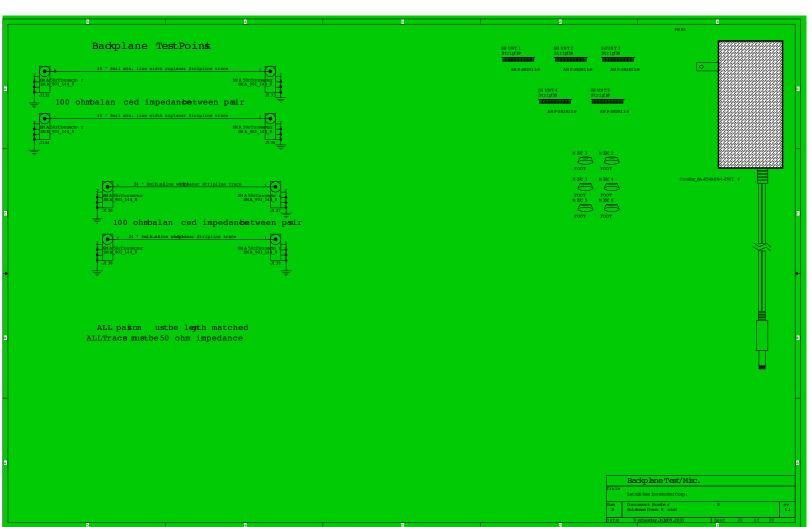

- Simulated matched backplane controlled impedance test runs

board. Figure 1 shows the functional partitioning of the board board, descriptions of all connectors, diodes and switches and a complete set of schematics for version 1.1 of the The contents of this user's guide include top level functional descriptions of the various portions of the evaluation

<u>a</u> SERDES I/O ORCAstra Inter Ē **-**0 Lattice Programming Interface Stripline

Figure 1. Lattice High-Speed SERDS Briefcase Board

user to configure bits on the control registers of the FPSC devices via a PC. For more information, refer to the ORCAstra Users Manual available on the Lattice web site at <a href="https://www.latticesemi.com">www.latticesemi.com</a>. The Lattice web site also con-The evaluation board is also supported by the ORCAstra™ graphical user interface (GUI). ORCAstra enables the tains further information about the Lattice devices used on this board, including device data sheets and application

# Electrical, Mechanical and Environmental Specifications

The nominal board dimensions are 12 inches by 12 inches. The environmental specifications are as follows:

- Operating temperature: 0°C to 55°C

- Storage temperature: -40°C to 75°C

- Humidity: < 95% without condensation</li>

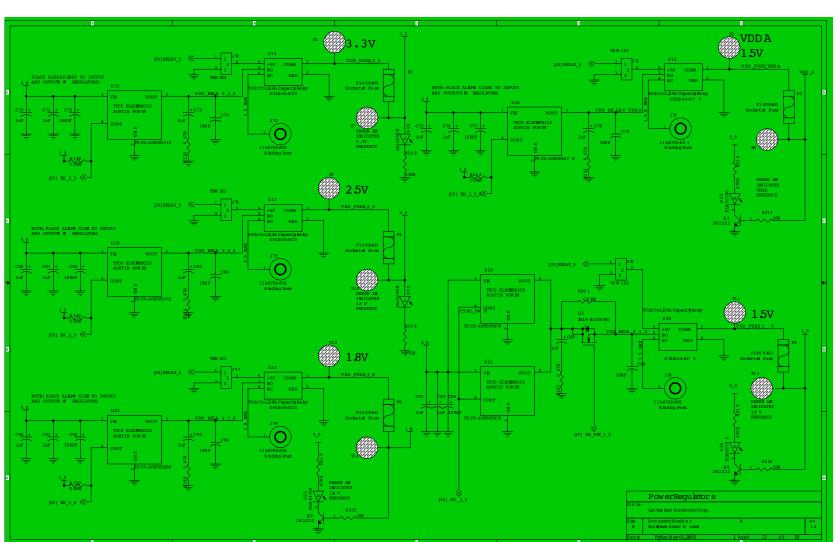

Regulated power is available from on-board supplies operated from a wall-type 5V supply. Alternately, power may be supplied from an external source. 3.3V, 2.5V, 1.8V and 1.5V power buses are supplied.

pendent differential clock sources. When the clock is sourced from the internal oscillator, a trigger output for test equipment is available. The devices may be driven by the on-board 156MHz oscillator or, to allow operation at different speeds, from inde-

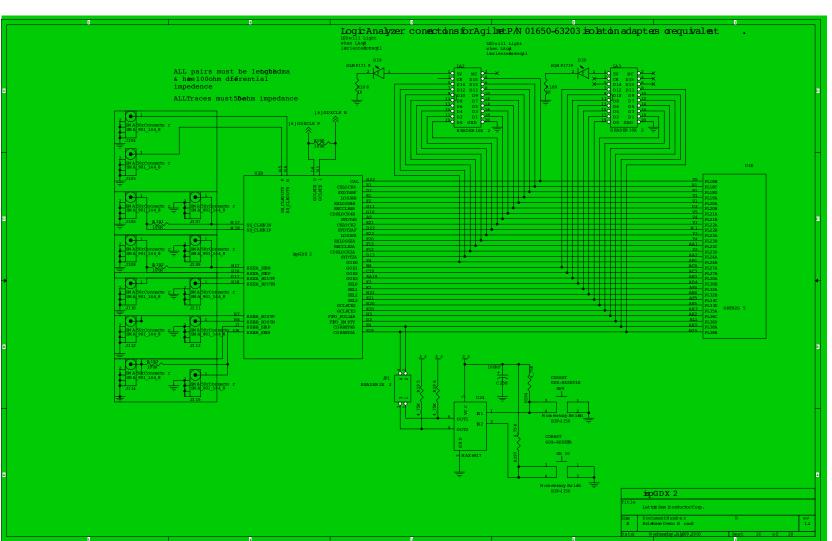

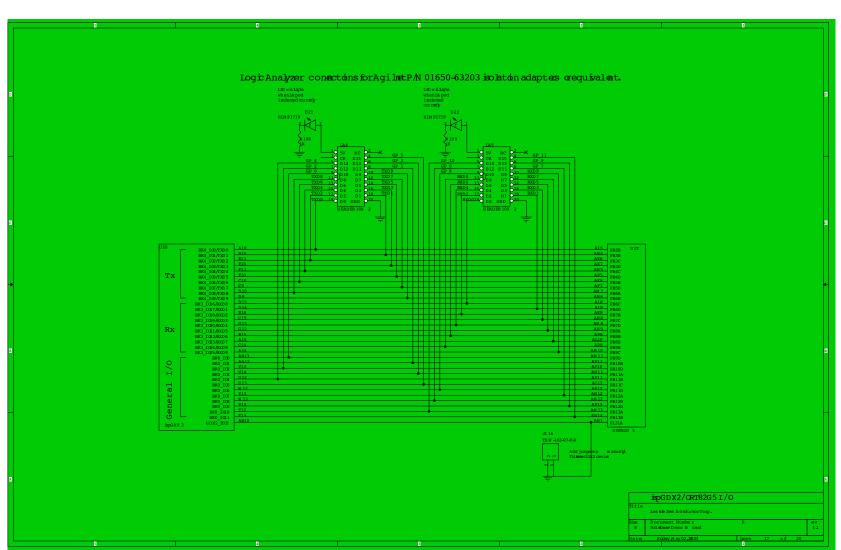

63203 isolation adapters or equivalents. Standard headers and DIP switches are provided for setup of the evaluation environment, and LEDs are provided to indicate current board and device status. Connections are provided both to device pins with dedicated functions, and to general purpose I/Os from the FPGA portion of the FPSC In addition to the high-speed SMA connectors, five logic analyzer connections are supplied for Agilent P/N 01650-

# Jacks, Connectors, Diodes and Switches

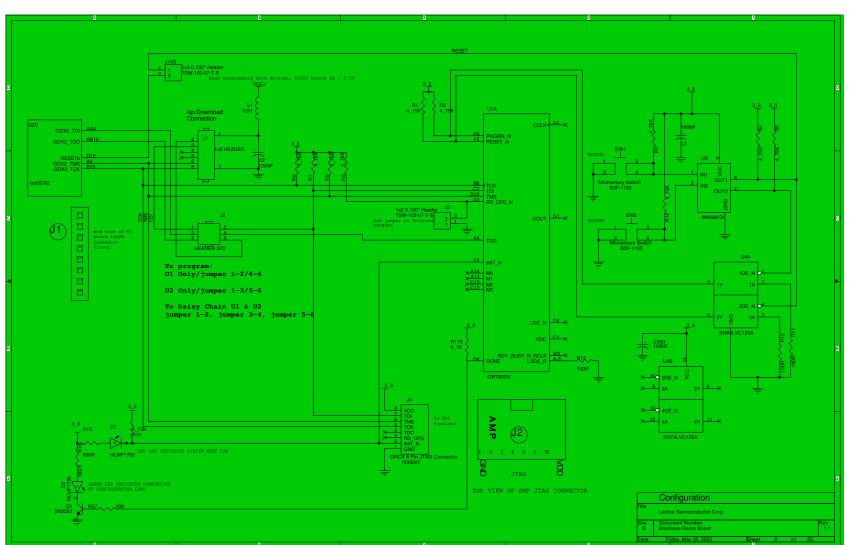

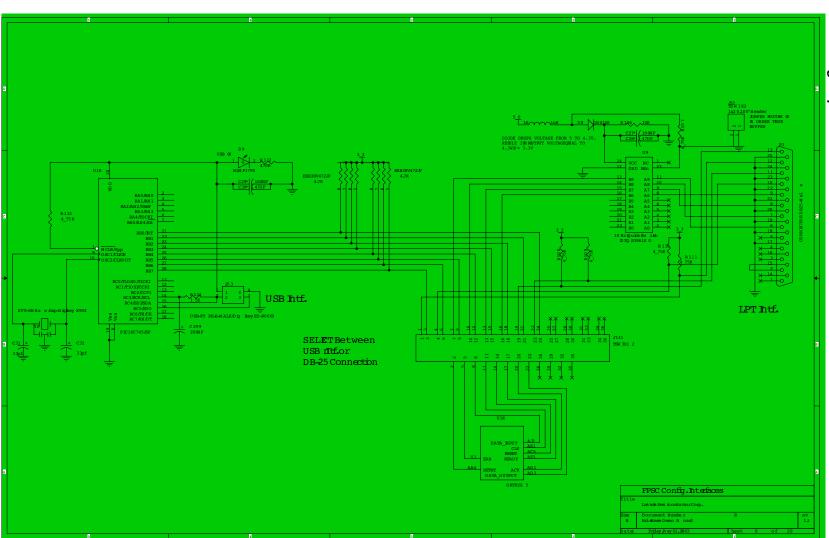

# **Bitstream Configuration Connectors**

The following connectors are used for configuration and programming

## Table 1. Programming Connections

| Jack Number | Size            | Function                           |

|-------------|-----------------|------------------------------------|

| J1          | 8 pins (6 used) | ispVM Download - FPSCs and ispGDX2 |

| J4          | 8 pins (6 used) | ORCA® Download (not populated)     |

| 09L         | 8 pins (6 used) | ispVM Download - ispPAC-POWR1208   |

| Ninter      |                 |                                    |

#### Notes:

- 1. LEDs are used to indicate the status of FPSC and ispGDX2 downloads.

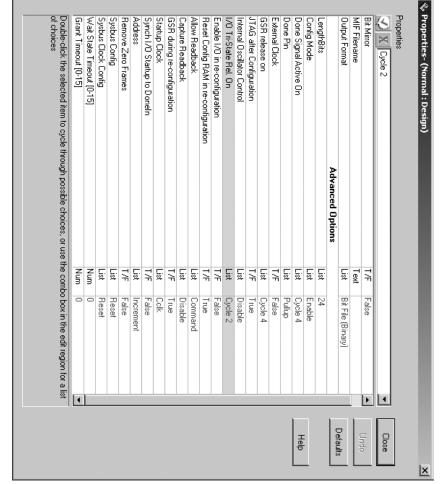

- ы The preference selections shown in Figure 2 are recommended for generating ORCA bit-streams. Note particularly the selections of the "Cycle 2" and "Cycle 4" options.

- ω Programming jacks J1 and J60 are intended for use with the Lattice ispDOWNLOAD® Cable, type pDS4102-DL2.

Figure 2. ispVM Preference Settings for ORCA Bitstreams

related to the USB when programming is first attempted. If this occurs, do the following: Note: With some operating system configurations, the ispVM software will generate failure and error messages

- Click on Options in the ispVM toolbar and select Cable and I/O Port Setup

- 2. Verify that "Cable Type" is "USB" and "Port Setting" is "Ezusb-0"

- 3. Unplug the USB cable from the system running ispVM

- 4. Replug the USB cable into the system running ispVM

- 5. Click OK

The device should now program successfully.

# **ORCAstra Interface Connectors**

The following connectors are used to interface with the ORCAstra GUI.

Table 2. ORCAstra GUI Connections

| J53                                           | ٩                                      | Jack Number |

|-----------------------------------------------|----------------------------------------|-------------|

| 3                                             | 1                                      | ımber       |

| 4 pin                                         | 24 pin                                 | Size        |

| Universal Serial Bus (USB) ORCAstra Interface | Parallel Port (LPT) ORCAstra Interface | Function    |

Note: The USB serial interface device and supporting EPROM are not specifically highlighted on the board photograph in Figure 1.

#### **Headers**

Standard 0.100 headers are provided for interconnecting points on the board. This can be accomplished with 0.100 IDC connectors and ribbon cable for bus connections or 0.025 pin socket patch cords (such as Pomona Electronics #5948. See www.pomonaelectronics.com for more information).

The following standard headers are used on the evaluation board. Boards are provided with default connections (ORSO/ORT82G5 listed here. Refer to the schematics in Appendix A for other configuration options).

Table 3. General Purpose Headers

| J92                                    | J90                                    | J86                                    | J84                                        | J81                                        | J77                                  | J76                                  | J74                                  | J71                                         | J70                                  | J69                             | J68                             | J67                             | J66                             | J65                             | J140                                                                                                                 | J64                                    | J63                                    | J62                                    | J61                                    | J141                                                       | J52                                                          | J51                         | J50                                                                       | J45                                                                      | J42                                              | J41                                                             | J39                                                                     | J37                                                  | J3                                                                     | J2                                                   | Jack<br>Number        |

|----------------------------------------|----------------------------------------|----------------------------------------|--------------------------------------------|--------------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|---------------------------------------------|--------------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|------------------------------------------------------------|--------------------------------------------------------------|-----------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------|-----------------------|

| Figure 17                              | Figure 17                              | Figure 17                              | Figure 17                                  | Figure 17                                  | Figure 16                            | Figure 16                            | Figure 16                            | Figure 16                                   | Figure 16                            | Figure 15                       | Figure 14                                                                                                            | Figure 14                              | Figure 14                              | Figure 14                              | Figure 14                              | Figure 12                                                  | Figure 12                                                    | Figure 11                   | Figure 10                                                                 | Figure 10                                                                | Figure 9                                         | Figure 9                                                        | Figure 9                                                                | Figure 8                                             | Figure 6                                                               | Figure 6                                             | Related<br>Schematic  |

| 4x2                                    | 4x2                                    | 4x2                                    | 4x2                                        | 4x2                                        | 2>1                                  | 2>1                                  | 2>1                                  | 2>1                                         | 2>1                                  | 4x2                             | 4x2                             | 4x2                             | 4x2                             | 4x2                             | 1x2                                                                                                                  | 1x2                                    | 1x2                                    | 1x2                                    | 1x2                                    | 3x12                                                       | 1x2                                                          | 4x2                         | 2>1                                                                       | 2>1                                                                      | 2>1                                              | 2>1                                                             | 2>1                                                                     | 1x2                                                  | 3x2                                                                    | 1x2                                                  | Size                  |

| Input Configure, ORCA PLL Clock 6 Test | Input Configure, ORCA PLL Clock 1 Test | Input Configure, ORCA PLL Clock 0 Test | Input Configure, ORCA Primary Clock 1 Test | Input Configure, ORCA Primary Clock 0 Test | External/Internal Power Select, 1.8V | External/Internal Power Select, 1.5V | External/Internal Power Select, 2.5V | External/Internal Power Select, analog 1.5V | External/Internal Power Select, 3.3V | VDDIO5 Select, ORSO/ORT82G5 I/O | VDDIO6 Select, ORSO/ORT82G5 I/O | VDDIO2 Select, ORSO/ORT82G5 I/O | VDDIO1 Select, ORSO/ORT82G5 I/O | VDDIO0 Select, ORSO/ORT82G5 I/O | 5V connection to evaluation board – remove jumper to configure isp-PAC (located to the right of J58 and left of SW8) | ispPAC Input (jumper shorts to ground) | Configures ORCAstra Parallel Port or USB Interface         | Enables ORCAstra Parallel Port Interface (located above J68) | VDD select for DIP Switches | ORSO/ORT82G5 REF_CLKB Select, for Quad B (located below the LEDs and J54) | ORSO/ORT82G5 REF_CLKA Select for Quad A (located below the LEDs and J54) | On-Board Clock2 (located below the LEDs and J54) | External/On-board Clock Select (located below the LEDs and J54) | On-Board Oscillator Power, +3.3 or GND (located below the LEDs and J54) | ORSO/ORT82G5 PTEMP pin (located to the right of J69) | Sets up configuration path, U1, U2 or daisy chain (located under J128) | Tristates ORSO/ORT82G5 (located between J55 and J56) | Function              |

| [1-2] [7-8]                            | [1-2] [7-8]                            | [1-2] [7-8]                            | [1-2] [7-8]                                | [1-2] [7-8]                                | [1-2]                                | [1-2]                                | [1-2]                                | [1-2]                                       | [1-2]                                | [1-5]                           | [1-5]                           | [1-5]                           | [1-8]                           | [1-8]                           | [1-2]                                                                                                                | None                                   | None                                   | None                                   | None                                   | [2,3][5-6][8-9]<br>[11-12][14-15]<br>[17-18][20-21][23-24] | None                                                         | [1-2]                       | [2-3]                                                                     | [1-2]                                                                    | [2-3]1                                           | [1-2]¹                                                          | [1-2]                                                                   | None                                                 | [1-2][3-4][5-6]                                                        | None                                                 | Default<br>Connection |

Table 3. General Purpose Headers (Continued)

| Jack<br>Number | Related<br>Schematic | Size | Function                                                               | Default<br>Connection |

|----------------|----------------------|------|------------------------------------------------------------------------|-----------------------|

| J96            | Figure 17            | 4x2  | Input Configure, ORCA PLL Clock 7 Test                                 | [1-2] [7-8]           |

| 398            | Figure 18            | 2>1  | External/Internal Power Select, VDD_OB (located left of J69)           | [1-2]                 |

| J100           | Figure 18            | 2>1  | External/Internal Power Select, VDD_IB (located left of J69)           | [1-2]                 |

| J102           | Figure 18            | 2>1  | External/Internal Power Select, VDDA (located left of J69)             | [1-2]                 |

| JP1            | Figure 20            | 2x2  | Pushbutton/FPGA GDXRESET Select                                        | None                  |

| J116           | Figure 21            | 1x2  | ispGDX2 Manual Tristate (jumper tristates ispGDX2), located above J124 | None                  |

| J117           | Figure 22            | 4x2  | VCC Select, ispGDX2                                                    | [2-4]                 |

| J118           | Figure 22            | 2>1  | External/Internal Power Select, ispGDX2 VCC                            | [1-2]                 |

| J120           | Figure 23            | 4x2  | VCCO0 Select, ispGDX2                                                  | [1-5]                 |

| J121           | Figure 23            | 4x2  | VCCO5 Select, ispGDX2                                                  | [1-5]                 |

| J122           | Figure 23            | 4x2  | VCCO6 Select, ispGDX2                                                  | [1-5]                 |

| J123           | Figure 23            | 4x2  | VCCO1 Select, ispGDX2                                                  | [1-5]                 |

| J124           | Figure 23            | 4x2  | VCCO2 Select, ispGDX2                                                  | [1-5]                 |

| J125           | Figure 23            | 4x2  | VCCO3 Select, ispGDX2                                                  | [1-5]                 |

| J126           | Figure 23            | 4x2  | VCCO4 Select, ispGDX2                                                  | [1-5]                 |

| J127           | Figure 23            | 4x2  | VCCJ Select (JTAG voltage)                                             | [1-5]                 |

| J128           | Figure 23            | 4x2  | VCCO7 Select, ispGDX2                                                  | [1-5]                 |

| J129           | Figure 23            | 2>1  | External/Internal Power Select, ispGDX2 VCCP (located above J131)      | [1-2] <sup>2</sup>    |

| J130           | Figure 23            | 4x2  | VCCA Select, ispGDX2 (located to the left of J131)                     | [2-6] <sup>2</sup>    |

Errata for Jacks J41 and J42 is as follows: To select an external clock source via SMA connections, remove default jumpers on J41 and J42 and add a connection between J42[1] to J41[2]. This can be accomplished using a 0.25 pin socket 6" patch cord(Pomona P/N 5948 or sim-

#### J54 and TP1

This evaluation board has wiring for a 12x3 header (J54) to support SERDES testing, and a test point (TP1) for observing the ATMOUT\_A signal (see Figure 13). Both are located next to the PASB RESET pushbutton. In general, this header location is not populated.

#### **TP2 through TP9**

The evaluation board has wiring for 8 test points (TP2 through TP9) for observing the operation of the ispPAC PWR1208 Power Sequencer (see Figure 14).

<sup>2.</sup> Lattice recommends VCCP0 and VCCP1 be connected to the appropriate voltage supply, even when the PLL and sysHSI circuits will not be

#### **SMA Connectors**

The following SMA connectors are used on the evaluation board (see Figure 1).

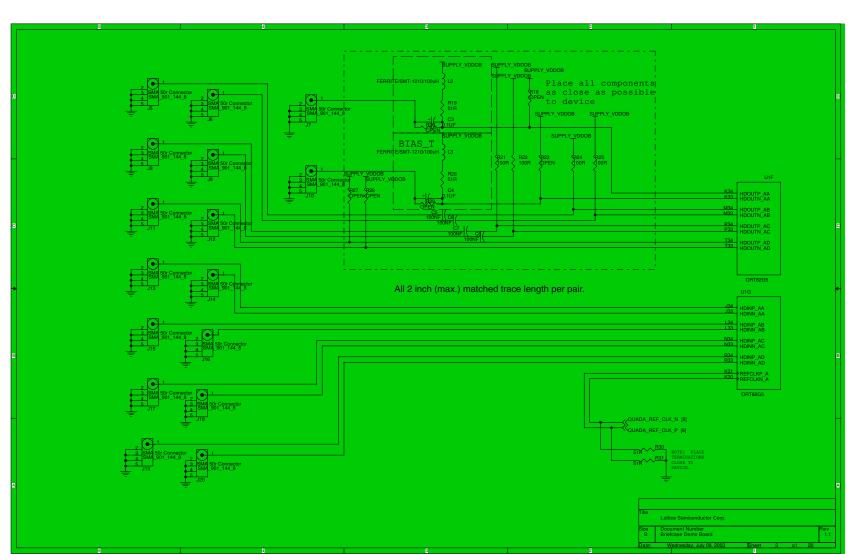

Table 4. ORSO/ORT82G5 Quad A Serial I/O (see Figure 7)

| Jack Number | I/O Name  |

|-------------|-----------|

| J14         | HDIN_AA   |

| J13         | HDIP_AA   |

| J16         | HDIN_AB   |

| J15         | HDIP_AB   |

| J18         | HDIN_AC   |

| J17         | HDIP_AC   |

| J20         | DA_NIDH   |

| J 19        | DP_ADH_   |

| J10         | HDOUTN_AA |

| J7          | HDOUTP_AA |

| 9F          | HDOUTN_AB |

| J5          | HDOUTP_AB |

| 6F          | ADOUTN_AC |

| 8           | HDOUTP_AC |

| J12         | DA_NTUODH |

| J11         | HDOUTP_AC |

|             |           |

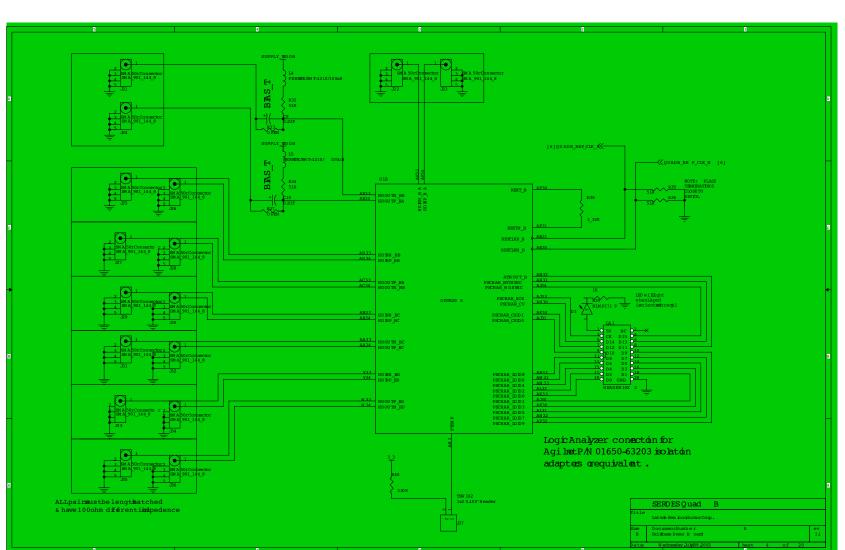

Table 5. ORSO/ORT82G5 Quad B Serial I/O (see Figure 8)

| J36      | HDOUTP_BB   |

|----------|-------------|

| J35      | HDOUTN_BB   |

| J32      | HDOUTP_BB   |

| J31      | HDOUTN_BB   |

| J28      | HDOUTP_BB   |

| J27      | HDOUTN_BB   |

| J24      | HDOUTP_BA   |

| J21      | HDOUTN_BA   |

| J34      | HDIP_BD     |

| J33      | HDIN_BD     |

| 08r      | HDIP_BC     |

| J29      | HDIN_BC     |

| J26      | HDIP_BB     |

| J25      | HDIN_BB     |

| J23      | HDIP_BA     |

| J22      | HDIN_BA     |

| I/O Name | Jack Number |

Note: Outputs for channels AA and BA have on-board bias\_T's to the VDD\_OB supply. Channels AB and AC are AC coupled with 100ohm pull-up resistors to VDD\_OB. The remaining output channels and all input channels are DC coupled.

Table 6. Clock SMA Connectors

| Figure 10 Trigger (Clock) Out_N               | Figure 10            | J49         |

|-----------------------------------------------|----------------------|-------------|

| Figure 10 Trigger (Clock) Out_P               | Figure 10            | J48         |

| Figure 10 ORSO/ORT External Ref Clk B_P Input | Figure 10            | J47         |

| Figure 10 ORSO/ORT External Ref Clk B_P Input | Figure 10            | J46         |

| Figure 10 ORSO/ORT External Ref Clk A_N Input | Figure 10            | J44         |

| Figure 10 ORSO/ORT External Ref Clk A_P Input | Figure 10            | J43         |

| External System Clock Input_N                 | Figure 9             | J40         |

| External System Clock Input_P                 | Figure 9             | J38         |

| Function                                      | Related<br>Schematic | Jack Number |

#### Notes:

- On-board header connections determine the clock source for the FPSC. The FPSC reference clocks may be provided by the onboard oscillator, a common external clock source, or multiple external clocks.

- 2. If an external clock source is used, it must be a differential clock.

- ω The trigger outputs are DC coupled in the default configuration. They can be converted to AC coupling by replacing resistors R204 and R215 with 0.01  $\mu F$  surface mount capacitors.

Table 7. OECA/PLL Clock Test SMA Connectors (see Figure 17)

|                                       | J95 TI                       | D 46r                                 | C 86r                                     | T 191                        | T 68L                            | O 88r                                 | O 28r                                     | T 58L                        | T 88L                            | J82 C                                 | 1 08r                        | Jack Number |  |

|---------------------------------------|------------------------------|---------------------------------------|-------------------------------------------|------------------------------|----------------------------------|---------------------------------------|-------------------------------------------|------------------------------|----------------------------------|---------------------------------------|------------------------------|-------------|--|

| Complementary Input, PLL Clock 7 Test | True Input, PLL Clock 7 Test | Complementary Input, PLL Clock 6 Test | Complementary Input, Primary Clock 1 Test | True Input, PLL Clock 6 Test | True Input, Primary Clock 1 Test | Complementary Input, PLL Clock 1 Test | Complementary Input, Primary Clock 0 Test | True Input, PLL Clock 1 Test | True Input, Primary Clock 0 Test | Complementary Input, PLL Clock 0 Test | True Input, PLL Clock 0 Test | Function    |  |

Table 8. ispGDX2 SMA Connectors (see Figure 20)

| Jack Number | Function                              |

|-------------|---------------------------------------|

| J104        | Negative Clock Out, SS_CLKOUT0N       |

| J105        | Positive Clock Out, SS_CLKOUT0P       |

| J106        | Positive Clock In, SS_CLKIN1P         |

| J107        | Negative Clock Out, SS_CLKIN1N        |

| J108        | Positive Serial Data In, HSI2A_SINP   |

| J109        | Negative Serial Data In, HSI2A_SINN   |

| 011L        | Positive Serial Data Out, HSI2A_SOUTP |

| 111L        | Negative Serial Data Out, HSI2A_SOUTN |

| J112        | Positive Serial Data Out, HSI4B_SOUTP |

| J113        | Negative Serial Data Out, HSI4B_SOUTN |

| J114        | Positive Serial Data In, HSI4B_SINP   |

| J115        | Negative Serial Data In, HSI4B_SINN   |

Table 9. Backplane Test SMA Connectors (see Figure 24 and areas marked "stripline" in Figure 1)

| Jack Number | umber | Connection                              |

|-------------|-------|-----------------------------------------|

| J132        | J133  | 40" backplane, 8 mil coplanar stripline |

| J134        | J135  | 40" backplane, 8 mil coplanar stripline |

| J136        | J137  | 24" backplane, 8 mil coplanar stripline |

| J138        | J139  | 24" backplane, 8 mil coplanar stripline |

All connections have 100Ω balanced impedance between pairs.

# **Logic Analyzer Connections**

The Logic Analyzer connections are connectors for Agilent P/N 01650-63203 isolation adapters or an equivalent. As shown in Figure 1, each connector has an associated LED that lights when a proper connection is made. See Figure 1 and Figure 8.

This 10x2 connector is used for ORSO/ORT82G5 Quad B SERDES testing (PSCHAR).

Table 10. Logic Analyzer Connectors

| 20  | Ground         | PSCHAR_LDIO0  | 19  |

|-----|----------------|---------------|-----|

| 18  | PSCHAR_LDIO1   | PSCHAR_LDIO2  | 17  |

| 16  | PSCHAR_LDIO3   | PSCHAR_LDIO4  | 15  |

| 14  | PSCHAR_LDIO5   | PSCHAR_LDIO6  | 13  |

| 12  | PSCHAR_LDIO7   | PSCHAR_LDIO8  | 11  |

| 10  | PSCHAR_LDIO9   | PSCHAR_CKIO0  | 6   |

| 8   | PSCHAR_WDSYNC  | PSCHAR_CKIO1  | 7   |

| 6   | PSCHAR_BYTSYNC | PSCHAR_CV     | 5   |

| 4   | ATM_OUT_B      | PSCHAR_XCK    | 3   |

| 2   | N/C            | Ground via D3 | 1   |

| Pin | Signal         | Signal        | Pin |

#### LA2 and LA3

These 10x2 ORCA to ispGDX2 bus analyzer connectors are used for clock, control, status and reset signals for the ispGDX2 device (see Figure 20). Each pin is also connected to a general purpose I/O pin in the ORSO/ORT82G5 FPGA logic.

Table 11. LA2 Signals

| 20     | 19      | 18     | 17      | 16        | 15     | 14       | 13       | 12       | 11       | 10     | 9         | 8       | 7      | 6       | 5    | 4   | 3   | 2   | 1              | Pin    |

|--------|---------|--------|---------|-----------|--------|----------|----------|----------|----------|--------|-----------|---------|--------|---------|------|-----|-----|-----|----------------|--------|

| Ground | CSLOCK2 | STDT4B | SYDT2AF | CDRLOCK4B | LOSS2A | RECCLK4B | EXLOSS2A | EXLOSS4B | RECCLK2A | LOSS4B | CDRLOCK2A | SYDT4BF | SYDT2A | CSLOCK4 | GOE0 | CAL | N/C | N/C | Ground via D19 | Signal |

Table 12. LA3 Signals

| 20     | 19   | 18      | 17   | 16      | 15   | 14          | 13   | 12         | 11   | 10       | 9    | 8        | 7    | 6   | 5   | 4   | 3   | 2   | 1              | Pin    |

|--------|------|---------|------|---------|------|-------------|------|------------|------|----------|------|----------|------|-----|-----|-----|-----|-----|----------------|--------|

| Ground | SEL3 | GCLKCE2 | SEL2 | GCLKCE3 | SEL1 | FIFO_FULL4B | SEL0 | FIFO_EMPTY | GOE3 | CDRRST4B | GOE2 | CDRRST2A | GOE1 | N/C | N/C | N/C | N/C | N/C | Ground via D20 | Signal |

#### LA4 and LA5

These 10x2 ORCA to ispGDX2 bus analyzer connectors are used for TX data, RX data and general purpose I/O signals for the ispGDX2 device (see Figure 21). Each pin is also connected to a general purpose I/O pin in the ORSO/ORT82G5 FPGA logic.

Table 13. LA4 Signals

| 20     | 19   | 18   | 17   | 16   | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3   | 2   | 1              | Pin    |

|--------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|----------------|--------|

| Ground | 0DXL | TXD1 | TXD2 | TXD3 | TXD4 | TXD5 | 9DXL | 7DXT | 8DXL | 6DXL | GP_0 | GP_1 | GP_2 | GP_3 | GP_4 | GP_5 | N/C | N/C | Ground via D21 | Signal |

Table 14. LA5 Signals

| 20     | 19   | 18   | 17   | 16   | 15   | 14   | 13   | 12   | 11   | 10   | 6    | 8    | 7    | 9    | 5     | 4     | 3   | 2   | 1              | Pin    |

|--------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-------|-------|-----|-----|----------------|--------|

| Ground | RXD0 | RXD1 | RXD2 | RXD3 | RXD4 | RXD5 | RXD6 | RXD7 | RXD8 | RXD9 | GP_6 | GP_7 | GP_8 | GP_9 | GP_10 | GP_11 | N/C | N/C | Ground via D22 | Signal |

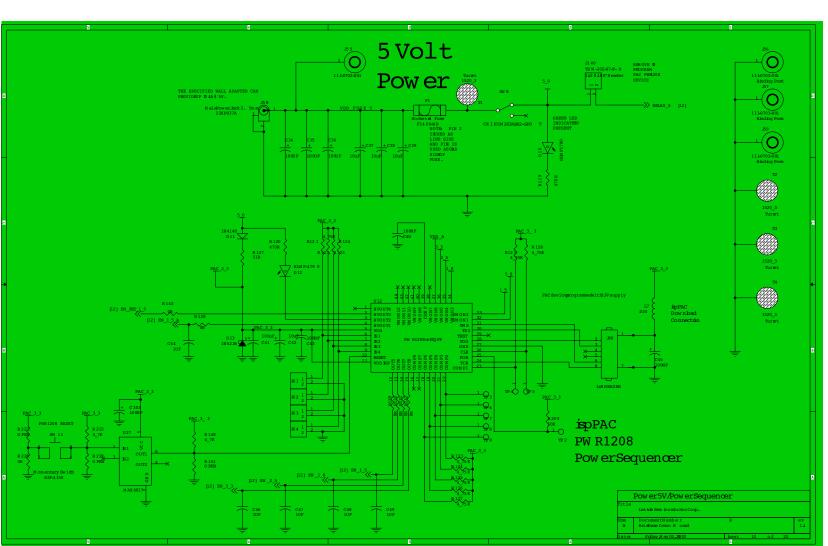

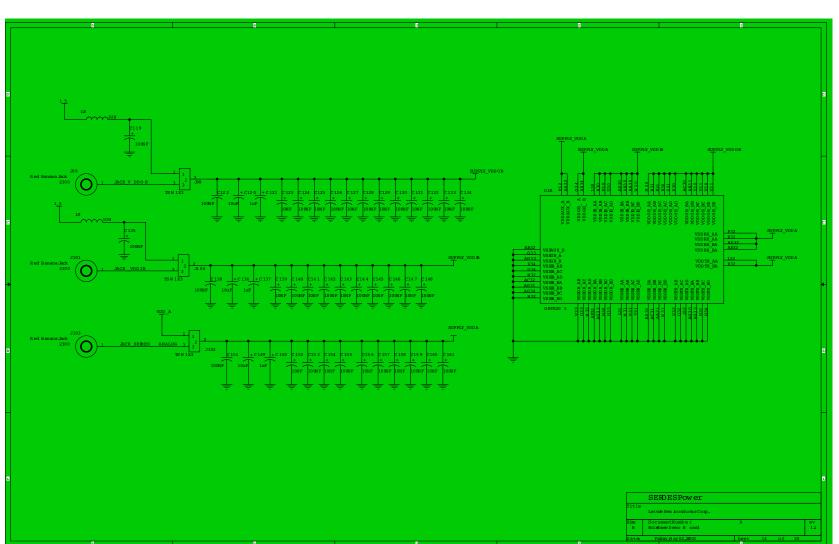

### **Power Supply Notes**

Headers are used to allow a choice of voltage for the on-board voltage buses, and to control the relays for either on-chip or off-chip power for each voltage level. Each supply is fused and has an associated LED indicating that the voltage is present (see Figure 1). The fuses are Littelfuse Alarm Indicating Fuses, 0481 Series (F1 is Digikey P/N F725 and the other four fuses are Digikey P/N F723). The evaluation board includes five on-board regulated power supplies that operate from an external 5V supply.

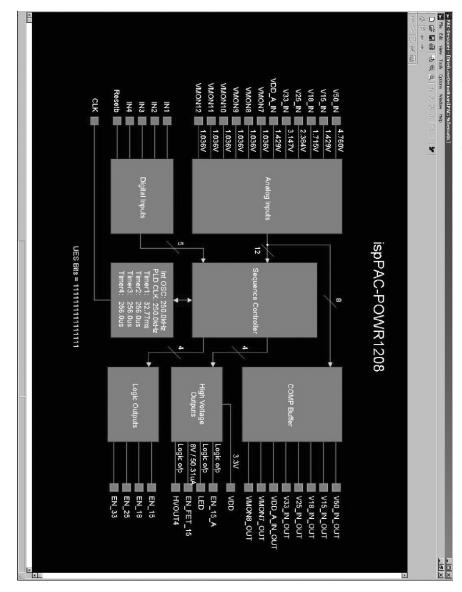

The evaluation board also includes an ispPAC-POWR1208 power control device. Programming files for this device can be developed using Lattice PAC-Designer® software. The top level PAC-Designer screen used for the default programming of the ispPAC-POWR1208 device is shown in Figure 3.

Figure 3. PAC-Designer Configuration Interface for ispPAC-POWR1208

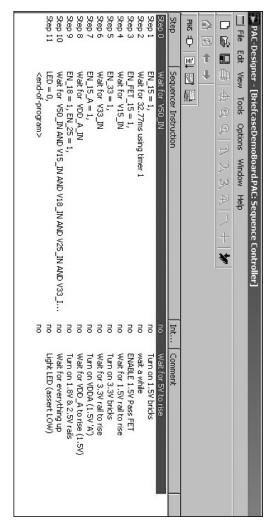

As provided, the device is programmed to provide power in the sequence shown in Figure 4.

Figure 4. Default Power Sequence for ispPAC-POWR1208 Used on the Evaluation Board

### **Turret Connectors**

The following turret connectors are available for monitoring the power buses on the evaluation board

Table 15. Turret Connectors

| Turret Number | Related<br>Schematic | Connected to – Power Bus        |

|---------------|----------------------|---------------------------------|

| T1            | Figure 14            | 5V                              |

| Т2            | Figure 14            | Ground                          |

| Т3            | Figure 14            | Ground                          |

| Т4            | Figure 14            | Ground                          |

| Т5            | Figure 16            | 3.3V, relay side of fuse        |

| Т6            | Figure 16            | Analog 1.5V, relay side of fuse |

| 77            | Figure 16            | 3.3V, LED side of fuse          |

| 18            | Figure 16            | Analog 1.5V, LED side of fuse   |

| T9            | Figure 16            | 2.5V, relay side of fuse        |

| T10           | Figure 16            | 2.5V, LED side of fuse          |

| T11           | Figure 16            | 1.5V, relay side of fuse        |

| T12           | Figure 16            | 1.8V, relay side of fuse        |

| Т13           | Figure 16            | 1.5V, LED side of fuse          |

| T14           | Figure 16            | 1.8V, LED side of fuse          |

## **Banana Jack Connectors**

The following banana jack connectors are available for supplying power to the evaluation board from an external

Table 16. Banana Jack Connectors

| Jack Number | Related<br>Schematic | Color | Function                                              |

|-------------|----------------------|-------|-------------------------------------------------------|

| J55         | Figure 14            | Red   | 5V external supply (VDD5)                             |

| J56         | Figure 14            | Black | Ground (GND)                                          |

| J57         | Figure 14            | Black | Ground (GND)                                          |

| J59         | Figure 14            | Black | Ground (GND)                                          |

| J72         | Figure 16            | Red   | Analog 1.5V external supply (VDDA)                    |

| J73         | Figure 16            | Red   | 3.3V external supply (VDD33)                          |

| J75         | Figure 16            | Red   | 2.5V external supply (VDD25)                          |

| J78         | Figure 16            | Red   | 1.5V external supply (VDD15)                          |

| J79         | Figure 16            | Red   | 1.8V external supply (VDD18)                          |

| 66F         | Figure 18            | Red   | VDD_OB external supply (located beneath DIP switches) |

| J101        | Figure 18            | Red   | VDD_IB external supply (located beneath DIP switches) |

| J103        | Figure 18            | Red   | VDDA external supply (located beneath DIP switches)   |

| J119        | Figure 22            | Red   | ispGDX2 VCC external supply                           |

| J131        | Figure 23            | Red   | ispGDX2 VCCP (analog) external supply                 |

#### **J**58

A 2.5 mm male power jack (J58) is provided for connection to the 5V wall power adapter (Condor SA-054A00-1-206IP or equivalent). See Figure 14.

#### Diodes

The following diodes are used on the evaluation board.

Table 17. Diodes

| ED ORCA to ispGDX2 Test LA Pod 5 OK               | Yellow LED   | Figure 21              | D22          |

|---------------------------------------------------|--------------|------------------------|--------------|

| ED ORCA to ispGDX2 Test LA Pod 4 OK               | Yellow LED   | Figure 21              | D21          |

| ED ORCA to ispGDX2 Test LA Pod 3 OK               | Yellow LED   | Figure 20              | D20          |

| ED ORCA to ispGDX2 Test LA Pod 2 OK               | Yellow LED   | Figure 20              | D19          |

| ED 1.8V (VDD18) present on evaluation board       | Green LED    | Figure 16              | D25          |

| ED 1.5V (VDD15) present on evaluation board       | Green LED    | Figure 16              | D24          |

| ED 2.5V (VDD25) present on evaluation board       | Green LED    | Figure 16              | D16          |

| ED Analog 1.5V (VDDA) present on evaluation board | Green LED    | Figure 16              | D23          |

| ED 3.3V (VDD33) present on evaluation board       | Green LED    | Figure 16              | D14          |

| 6 ispPAC VDD bias network, Zener                  | 1N5226       | Figure 14              | D13          |

| ED ispPAC Configuration Done                      | Green LED    | Figure 14              | D12          |

| 8 ispPAC VDD bias network                         | 1N4148       | Figure 14              | D11          |

| ED 5V (VDD5) present on evaluation board          | Green LED    | Figure 14              | D10          |

| ED USB Interface Active                           | Green LED    | Figure 12              | D9           |

| 8 Voltage dropping diode, parallel port input     | 1N4148       | Figure 12              | BG           |

| LED Outputs from ORSO/ORT82G5 FPGA Logic          | Quad Red LED | Figure 11 <sup>1</sup> | D7           |

| LED Outputs from ORSO/ORT82G5 FPGA Logic          | Quad Red LED | Figure 11 <sup>1</sup> | D6           |

| LED Outputs from ORSO/ORT82G5 FPGA Logic          | Quad Red LED | Figure 11 <sup>1</sup> | D5           |

| LED Outputs from ORSO/ORT82G5 FPGA Logic          | Quad Red LED | Figure 11 <sup>1</sup> | D4           |

| ED ORSO/ORT82G5 SERDES Test LA Pod OK             | Yellow LED   | Figure 8               | D3           |

| ED ORSO/ORT82G5 Configuration DONE                | Green LED    | Figure 6               | D2           |

| D ORSO/ORT82G5 Configuration INIT                 | Red LED      | Figure 6               | D1           |

| Function/Indication                               | Туре         | Related<br>Schematic   | Diode Number |

<sup>1.</sup> Also see LED and DIP table (Table 19).

#### **Switches**

The following switches are used on the evaluation board.

#### Table 18. Switches

|               | ,                        |              |                                            |

|---------------|--------------------------|--------------|--------------------------------------------|

| Switch Number | Related<br>Schematic     | Туре         | Function                                   |

| SW1           | Figure 6                 | Momentary PB | ORSO/ORT82G5 RESETN                        |

| SW2           | Figure 6                 | Momentary PB | ORSO/ORT82G5 PRGMN                         |

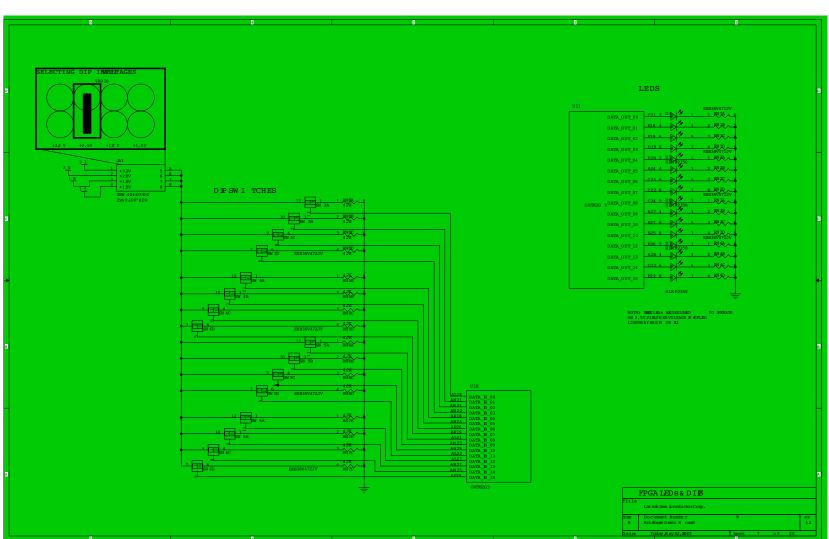

| SW3[A:D]      | Figure 11 <sup>1,2</sup> | Quad DIP     | Switch Inputs to ORSO/ORT82G5 FPGA Logic   |

| SW4[A:D]      | Figure 11 <sup>1,2</sup> | Quad DIP     | Switch Inputs to ORSO/ORT82G5 FPGA Logic   |

| SW5[A:D]      | Figure 11 <sup>1,2</sup> | Quad DIP     | Switch Inputs to ORSO/ORT82G5 FPGA Logic   |

| SW6[A:D]      | Figure 11 <sup>1,2</sup> | Quad DIP     | Switch Inputs to ORSO/ORT82G5 FPGA Logic   |

| SW7           | Figure 13                | Momentary PB | ORSO/ORT82G5 PASB_RESETN (SERDES Test)     |

| 8WS           | Figure 14                | SPDT         | Disconnects +5 volts from evaluation board |

| SW11          | Figure 14                | Momentary PB | PWR1208 RESET                              |

| 6MS           | Figure 20                | Momentary PB | GDX-RESET4B                                |

| SW10          |                          | Momentary PB | GDX-RESET2A                                |

|               |                          |              |                                            |

# **LED and DIP Connections to ORSO/ORT82G5**

Table 19. LED and DIP Connectors

| FPGA Logic Options | FPGA Logic Options from ORSO/ORT82G5 | FPGA Logic Inputs | FPGA Logic Inputs to ORSO/ORT82G5 |

|--------------------|--------------------------------------|-------------------|-----------------------------------|

| FPSC Pin           | LED                                  | DIP Switch        | FPSC Pin                          |

| C21                | D4 - Pin 2                           | SW3A              | AL18                              |

| E18                | D4 - Pin 4                           | SW3B              | AN21                              |

| E19                | D4 - Pin 6                           | SW3C              | AM21                              |

| D19                | D4 - Pin 8                           | SW3D              | AN22                              |

| D20                | D5 - Pin 2                           | SW4A              | AK18                              |

| B24                | D5 - Pin 4                           | SW4B              | AN23                              |

| C23                | D5 - Pin 6                           | SW4C              | AP26                              |

| C22                | D5 - Pin 8                           | SW4D              | 9K19                              |

| C24                | D6 - Pin 2                           | SW5A              | AL21                              |

| A27                | D6 - Pin 4                           | SW5B              | AM23                              |

| B27                | D6 - Pin 6                           | SW5C              | AN25                              |

| B25                | D6 - Pin 8                           | SW5D              | AL22                              |

| B26                | D7 - Pin 2                           | SW6A              | AL23                              |

| A28                | D7 - Pin 4                           | SW6B              | AN27                              |

| D22                | D7 - Pin 6                           | SW6C              | AM25                              |

| E22                | D7 - Pin 8                           | SW6D              | AP29                              |

|                    |                                      |                   |                                   |

Also see the LED and DIP table (Table 19).

For the Quad DIP switches, "off" is toward the banana jacks.

### Ordering Information

| Description                                                          | Ordering Part Number | China RoHS Environment-Friendly<br>Use Period (EFUP) |

|----------------------------------------------------------------------|----------------------|------------------------------------------------------|

| ORT82G5, ispGDX256, and ispPAC Power Manager 1208<br>Briefcase Board | ORT82G5-G2-PAC-EV    |                                                      |

| ORSO82G5 Evaluation Board                                            | ORSO82G5-G2-PAC-EV   | Č                                                    |

# **Technical Support Assistance**

Hotline: 1-800-LATTICE (North America)

+1-503-268-8001 (Outside North America)

e-mail: techsupport@latticesemi.com

Internet: www.latticesemi.com

### **Revision History**

| _                                   |                  |                |

|-------------------------------------|------------------|----------------|

| March 2007                          | March 2003       | Date           |

| 01.1                                | 01.0             | Version        |

| Added Ordering Information section. | Initial release. | Change Summary |

© 2007 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at <a href="https://www.latticesemi.com/legal">www.latticesemi.com/legal</a>. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

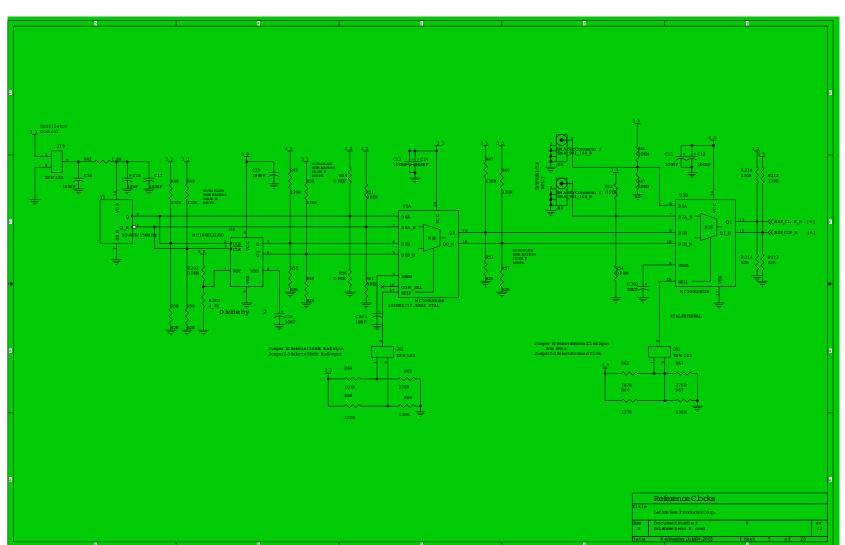

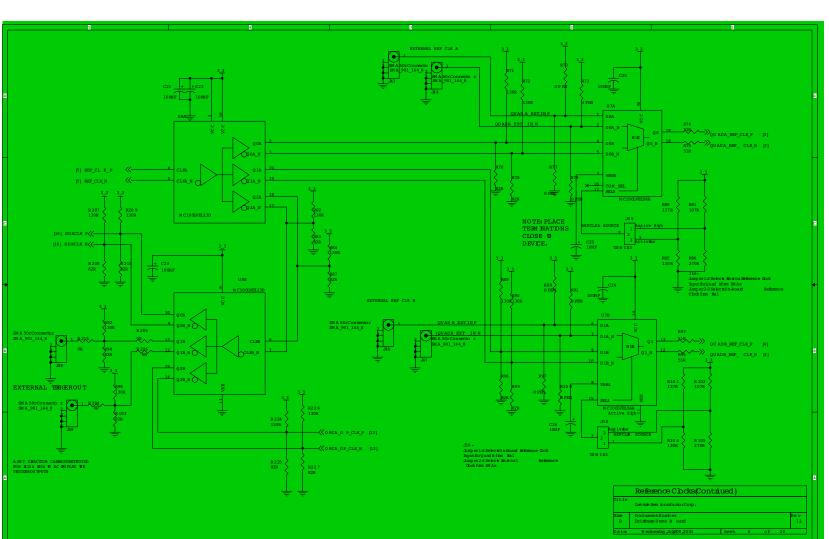

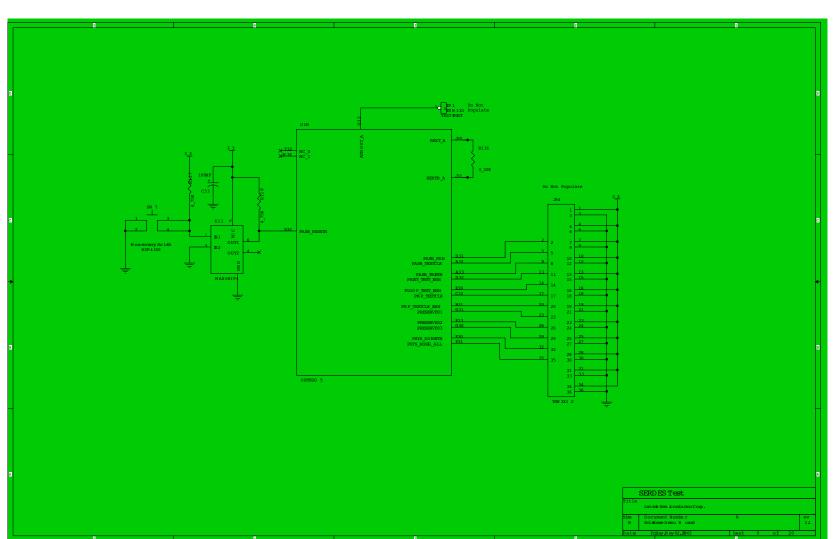

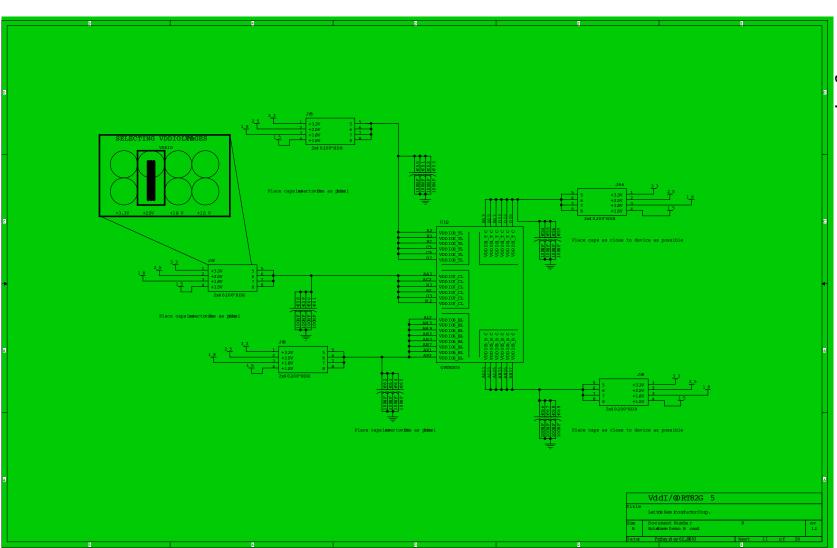

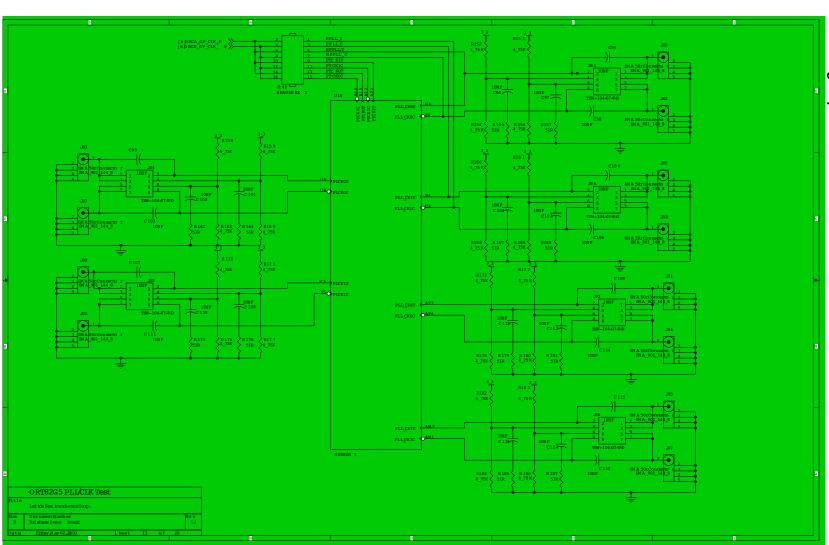

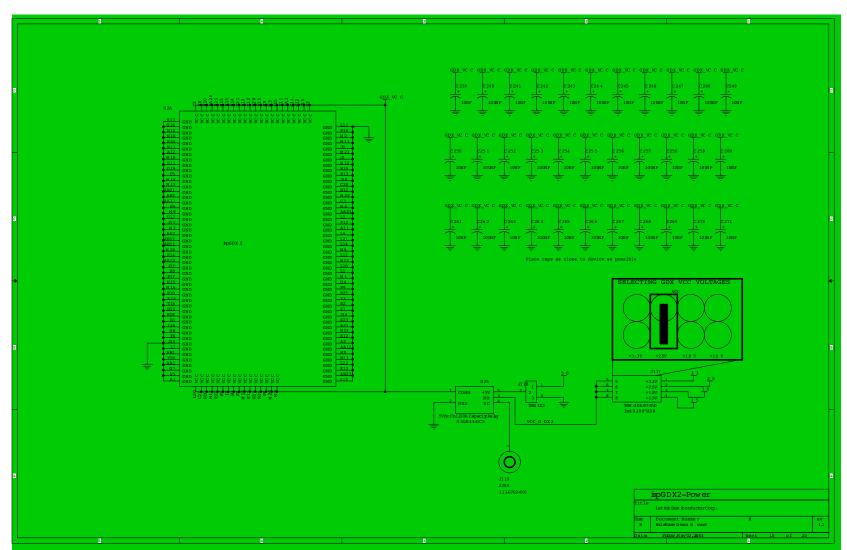

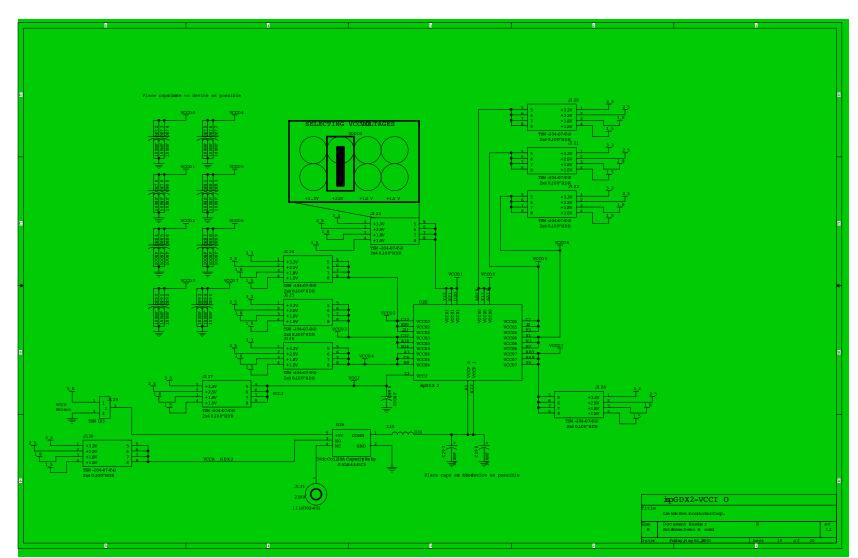

### **Appendix A. Schematics**

The current schematics for the High-Speed SERDES Briefcase Board are given in this appendix

Figure 5. Lattice High-Speed SERDES Briefcase Board Schematic

Figure 6. Lattice High-Speed SERDES Briefcase Board Schematic

Figure 7. Lattice High-Speed SERDES Briefcase Board Schematic

Figure 8. Lattice High-Speed SERDES Briefcase Board Schematic

Figure 9. Lattice High-Speed SERDES Briefcase Board Schematic

Figure 10. Lattice High-Speed SERDES Briefcase Board Schematic

Figure 11. Lattice High-Speed SERDES Briefcase Board Schematic

Figure 12. Lattice High-Speed SERDES Briefcase Board Schematic

Figure 13. Lattice High-Speed SERDES Briefcase Board Schematic

Figure 14. Lattice High-Speed SERDES Briefcase Board Schematic

Figure 15. Lattice High-Speed SERDES Briefcase Board Schematic

Figure 16. Lattice High-Speed SERDES Briefcase Board Schematic

Figure 17. Lattice High-Speed SERDES Briefcase Board Schematic

Figure 18. Lattice High-Speed SERDES Briefcase Board Schematic

C 173 + 10NF C11 VOD

C14 VOD

D31 VOD

D32 VOD

FF2 VOD

FF2 VOD

FF3 VOD

FF3 VOD

FF3 VOD

FF3 VOD

FF3 VOD

FF4 3 **3**V 15V GND Power& BypassORT82G

Figure 20. Lattice High-Speed SERDES Briefcase Board Schematic

Figure 21. Lattice High-Speed SERDES Briefcase Board Schematic

Figure 22. Lattice High-Speed SERDES Briefcase Board Schematic

Figure 23. Lattice High-Speed SERDES Briefcase Board Schematic

Figure 24. Lattice High-Speed SERDES Briefcase Board Schematic