# 40 V, 500 mA / 1.0 A Synchronous Buck Regulators with Ultralow Quiescent Current, SYNC $_{\rm IN}$ , CLK $_{\rm OUT}$ , and PGOOD

#### **FEATURES AND BENEFITS**

- Automotive AEC-Q100 qualified

- Input operating voltage range: 3.5 to 36 V

□ Withstands surge voltages to 40 V for load dump

- Low-Power (LP) mode—draws just 8  $\mu A$  from  $V_{IN}$  while maintaining 3.3 or 5.0  $V_{OUT}$

- AUTO mode allows automatic transition between PWM and LP mode based on load current

- Programmable PWM frequency (f<sub>SW</sub>): 250 kHz to 2.4 MHz

- PWM frequency dithering and controlled switch node slew rate reduce EMI/EMC signature

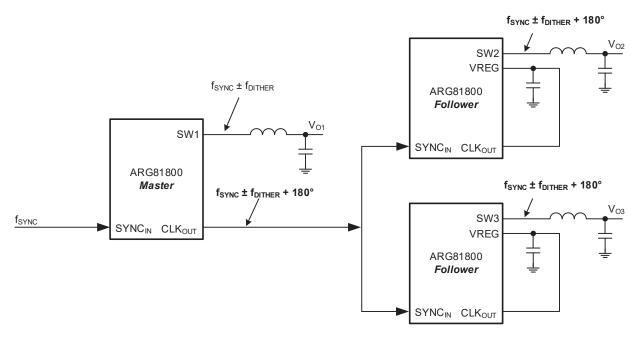

- CLK<sub>OUT</sub> allows interleaving and dithering of "downstream" regulators using their synchronization inputs

- Interleaving minimizes input filter capacitor requirement and improves EMI/EMC performance

- Synchronization of PWM frequency to external clock on  $SYNC_{IN}$  pin

- Adjustable output voltage: ±1.5% accuracy over operating temperature range (-40°C to 150°C)

- Maximized duty cycle at low V<sub>IN</sub> improves dropout

- · Soft recovery from dropout condition

- Adjustable soft-start time controls inrush current to accommodate a wide range of output capacitances

- External compensation provides flexibility to tune the system for maximum stability or fast transient response

Continued on next page...

#### **APPLICATIONS**

- · Infotainment

- Navigation Systems

- Instrument Clusters

- Audio Systems

- ADAS Applications

- Battery Powered Systems

- Industrial Systems

- · Network and Telecom

- Home Audio

- HVAC Systems

#### **DESCRIPTION**

The ARG81800 includes all the control and protection circuitry to produce a PWM regulator with  $\pm 1.5\%$  output voltage accuracy, with ultralow quiescent current to enable "keepalive" supply operation with minimal current draw from the supply during very light load regulation. There are two versions of the ARG81800 available, 500 mA and 1 A, so the physical size of the power components can be optimized for lower current systems, thus reducing PCB area and saving cost. PWM switching frequency can be programmed over a wide range to balance efficiency, component sizing, and EMC performance. If  $V_{\rm IN}$  decays and the duty cycle reaches its maximum, the ARG81800 will automatically fold back its PWM frequency to extend the duty cycle and maintain  $V_{\rm OUT}$ .

The ARG81800 employs Low-Power (LP) mode to maintain the output voltage at no load or very light load conditions while drawing only micro-amps from  $V_{\rm IN}$ . The ARG81800 includes a PWM/AUTO control pin so the system can dynamically force either PWM or AUTO mode by setting this pin high or low, respectively.

If the SYNC  $_{\rm IN}$  pin is driven by an external clock, the ARG81800 will be forced into PWM mode and synchronize to the incoming clock. The ARG81800 adds frequency dithering to the SYNC  $_{\rm IN}$  clock to reduce EMI/EMC. The ARG81800 provides a CLK  $_{\rm OUT}$  pin so "downstream" regulators can be easily interleaved and dithered via their synchronization inputs.

Continued on next page...

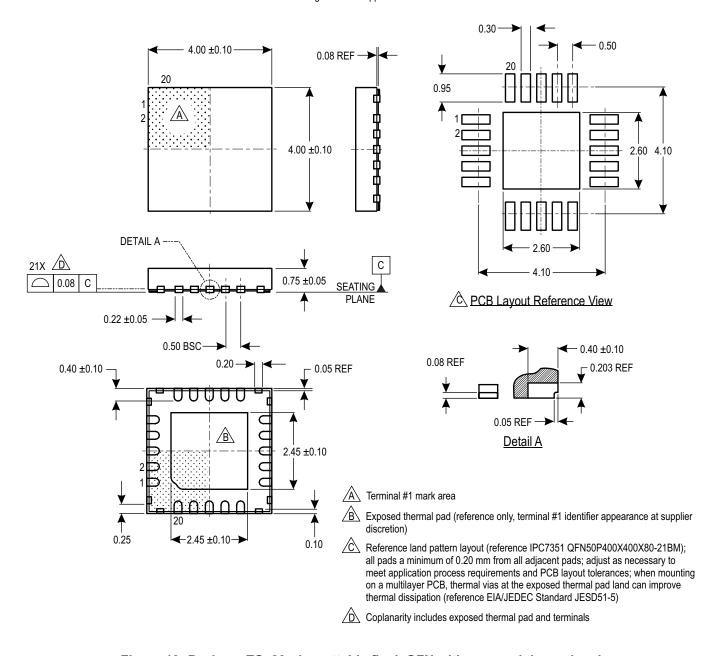

#### PACKAGE:

20-pin, 4 mm × 4 mm, QFN (ES) with wettable flank

Not to scale

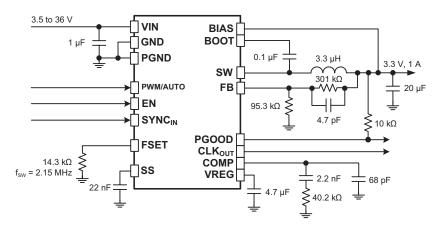

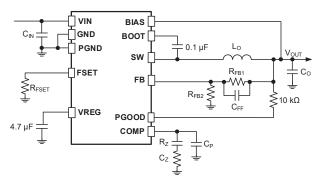

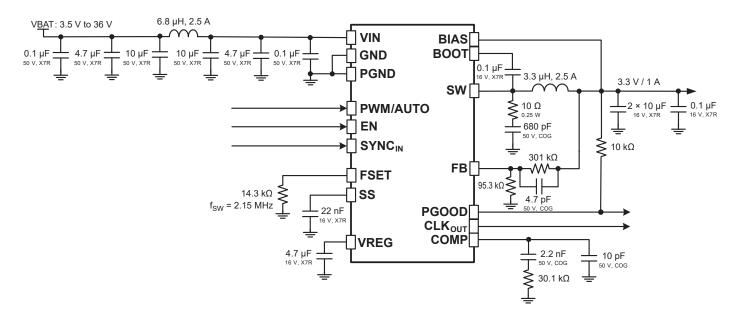

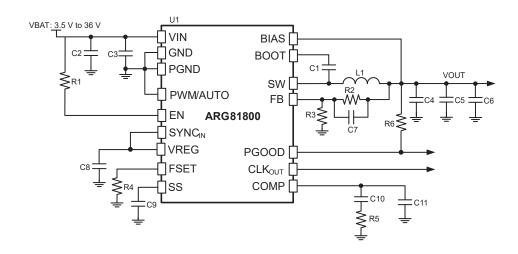

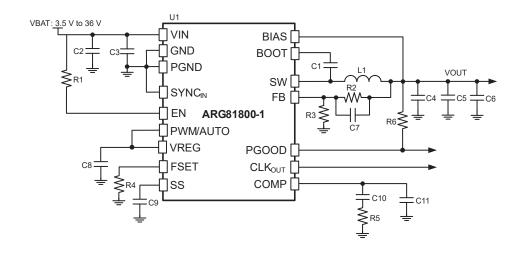

**Typical Application Diagram**

# 40 V, 500 mA / 1.0 A Synchronous Buck Regulators with Ultralow Quiescent Current, SYNC $_{\rm IN}$ , CLK $_{\rm OUT}$ , and PGOOD

#### **FEATURES AND BENEFITS**

- Enable input can command ultralow 1 μA shutdown current

- Open-drain PGOOD output with rising delay

- · Pre-bias startup allows quick restart and avoids reset

- Overvoltage, pulse-by-pulse current limit, hiccup mode short circuit, and thermal protections

- Robust FMEA: pin open/short and component faults

#### **DESCRIPTION**

The ARG81800 has external compensation, so it can be tuned to satisfy a wide range of system goals with many different external components over a wide range of PWM frequencies. The ARG81800 includes adjustable soft start to minimize inrush current. The ARG81800 monitors the feedback voltage to provide an open-drain power good signal. The Enable input can command an ultra-low current shutdown mode with  $V_{\rm OUT} = 0~\rm V$ .

Extensive protection features of the ARG81800 include pulse-by-pulse current limit, hiccup mode short circuit protection, BOOT open/short voltage protection,  $V_{\rm IN}$  undervoltage lockout,  $V_{\rm OUT}$  overvoltage protection, and thermal shutdown. The ARG81800 is supplied in a low profile 20-pin wettable flank QFN package (suffix "ES") with exposed power pad.

#### **SELECTION GUIDE**

| Part Number      | DC Current | Package                   | Packing                      | Lead Frame     |

|------------------|------------|---------------------------|------------------------------|----------------|

| ARG81800KESJSR   | 1 A        | 20-pin wettable flank QFN | 6000 pieces per 13-inch reel | 100% matte tin |

| ARG81800KESJSR-1 | 0.5 A      | package with thermal pad  | 0000 pieces per 13-incriteer | 100% matte tin |

<sup>\*</sup>Contact Allegro for additional packing options

#### **Table of Contents**

| Features and Benefits                                                          | 1 | Low-Power (LP) Mode                                                             | 20 |

|--------------------------------------------------------------------------------|---|---------------------------------------------------------------------------------|----|

| Description                                                                    | 1 | Protection Features                                                             | 21 |

| Package                                                                        | 1 | Undervoltage Lockout (UVLO)                                                     | 21 |

| Typical Application Diagram                                                    | 1 | Pulse-by-Pulse Peak Current Protection (PCP)                                    | 21 |

| Selection Guide                                                                | 2 | Overcurrent Protection (OCP) and Hiccup Mode                                    | 21 |

| Absolute Maximum Ratings                                                       | 3 | BOOT Capacitor Protection                                                       | 22 |

| Thermal Characteristics                                                        | 3 | Asynchronous Diode Protection                                                   | 22 |

| Functional Block Diagram                                                       | 4 | Overvoltage Protection (OVP)                                                    |    |

| Pinout Diagram and Terminal List                                               |   | SW Pin Protection                                                               |    |

| Electrical Characteristics                                                     |   | Pin-to-Ground and Pin-to-Short Protections                                      | 22 |

| Typical Performance Characteristics                                            | 1 | Thermal Shutdown (TSD)                                                          | 23 |

| Functional Description                                                         |   | Application Information                                                         |    |

| Overview1                                                                      | 6 | Design and Component Selection                                                  |    |

| Reference Voltage1                                                             | 6 | PWM Switching Frequency (R <sub>FSET</sub> )                                    |    |

| Internal VREG Regulator1                                                       |   | Output Voltage Setting                                                          |    |

| Oscillator/Switching Frequency1                                                |   | Output Inductor (L <sub>O</sub> )                                               |    |

| Synchronization (SYNC <sub>IN</sub> ) and Clock Output (CLK <sub>OUT</sub> ) 1 |   | Output Capacitors (C <sub>O</sub> )                                             |    |

| Frequency Dither                                                               |   | Output Voltage Ripple – Ultralow-I <sub>O</sub> LP Mode                         | 28 |

| Transconductance Error Amplifier                                               | 7 | Input Capacitors                                                                | 29 |

| Compensation Components                                                        |   | Bootstrap Capacitor                                                             | 29 |

| Power MOSFETs1                                                                 |   | Soft Start and Hiccup Mode Timing (C <sub>SS</sub> )                            | 29 |

| BOOT Regulator1                                                                | 8 | Compensation Components (R <sub>Z</sub> , C <sub>Z</sub> , and C <sub>P</sub> ) |    |

| Soft Start (Startup) and Inrush Current Control                                |   | Power Stage                                                                     |    |

| Slope Compensation                                                             |   | Error Amplifier                                                                 | 31 |

| Pre-Biased Startup1                                                            | 9 | A Generalized Tuning Procedure                                                  |    |

| Dropout1                                                                       | 9 | Power Dissipation and Thermal Calculations                                      |    |

| PGOOD Output                                                                   |   | EMI/EMC Aware PCB Design                                                        | 36 |

| Current Sense Amplifier                                                        |   | Typical Reference Designs                                                       |    |

| Pulse-Width Modulation (PWM)                                                   |   | Package Outline Drawing                                                         |    |

# 40 V, 500 mA / 1.0 A Synchronous Buck Regulators with Ultralow Quiescent Current, SYNC $_{\rm IN}$ , CLK $_{\rm OUT}$ , and PGOOD

#### **SPECIFICATIONS**

#### **ABSOLUTE MAXIMUM RATINGS** [1]

| Characteristic                 | Symbol              | Notes                             | Rating                                       | Unit |

|--------------------------------|---------------------|-----------------------------------|----------------------------------------------|------|

| VIN, EN, SS, BIAS Pin Voltage  |                     |                                   | -0.3 to 40                                   | V    |

| CW Din Voltage                 |                     | Continuous                        | -0.3 <sup>[2]</sup> to V <sub>IN</sub> + 0.3 | V    |

| SW Pin Voltage                 | V <sub>SW</sub>     | V <sub>IN</sub> ≤ 36 V, t < 50 ns | -1.0 to V <sub>IN</sub> + 2                  | V    |

| BOOT Din Voltage               | V                   | Continuous                        | $V_{SW} - 0.3$ to $V_{SW} + 5.5$             | V    |

| BOOT Pin Voltage               | V <sub>BOOT</sub>   | t < 1 ms                          | $V_{SW} - 0.3 \text{ to } V_{SW} + 7.0$      | V    |

| All Other Pin Voltages         |                     |                                   | -0.3 to 5.5                                  | V    |

| Operating Junction Temperature | T <sub>J(max)</sub> |                                   | -40 to 150                                   | °C   |

| Storage Temperature            | T <sub>stg</sub>    |                                   | -55 to 150                                   | °C   |

<sup>[1]</sup> Stresses beyond the ratings listed in this table may cause permanent damage to the device. The Absolute Maximum ratings are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the Electrical Characteristics table is not implied. Exposure to Absolute Maximum-rated conditions for extended periods may affect device reliability.

#### THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

| Characteristic             | Symbol        | Test Conditions [3]                    | Value | Unit |

|----------------------------|---------------|----------------------------------------|-------|------|

| Package Thermal Resistance | $R_{	hetaJA}$ | On 4-layer PCB based on JEDEC standard | 37    | °C/W |

$<sup>^{[3]}</sup>$  Additional thermal information available on the Allegro website.

<sup>[2]</sup> This voltage is a function of temperature.

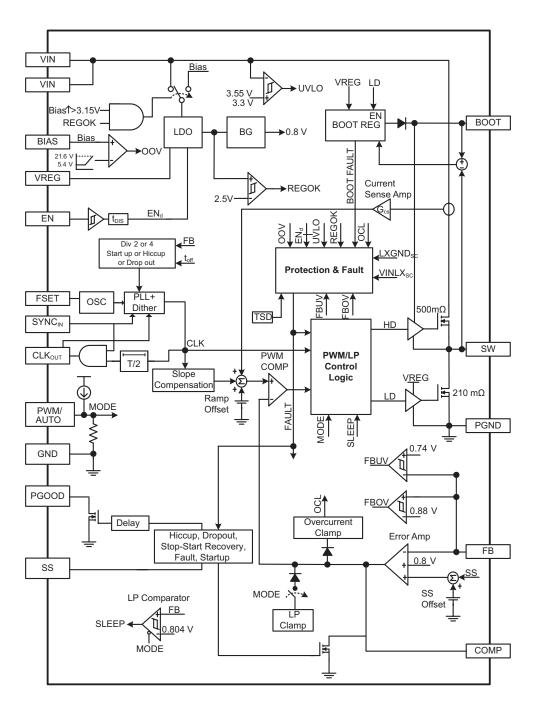

**Functional Block Diagram**

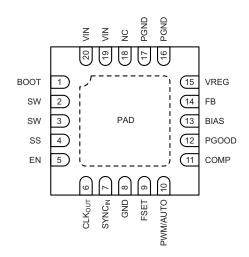

#### PINOUT DIAGRAM AND TERMINAL LIST

Package ES, 20-Pin QFN Pinout Diagram

#### **Terminal List Table**

| Number | Name               | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | воот               | This pin supplies the drive for the high-side N-channel MOSFET. Connect a 100 nF ceramic capacitor from BOOT to SW. Do not add any external resistor in series with the boot capacitor.                                                                                                                                                                                                                                                                                        |

| 2, 3   | SW                 | Regulator switch node output pins. Connect these pins to power inductor with a short and wide PCB trace.                                                                                                                                                                                                                                                                                                                                                                       |

| 4      | SS                 | Soft start pin. Connect a capacitor, $C_{SS}$ , from this pin to GND to set the start-up time. This capacitor also determines the hiccup period during overcurrent.                                                                                                                                                                                                                                                                                                            |

| 5      | EN                 | This pin must be set high to enable the ARG81800. If this pin is low, the ARG81800 will enter a very low current shutdown or "SLEEP" state where $V_{OUT}=0$ V. If the application does not require a logic level controlled enable, then this pin can be tied directly to $V_{IN}$ . Also, if this pin is floated, it will be pulled low by an internal pull-down resistor, disabling the ARG81800.                                                                           |

| 6      | CLK <sub>OUT</sub> | Dual function pin: Clock output pin for "Master" operation. Frequency dithering is added to this pin when the ARG81800 is operating as a Master. For "Follower" operation, this pin must be connected to VREG so dithering will not be internally added to SYNC <sub>IN</sub> ; see Figure 1. The exact functionality of this pin is dependent on the status of the SYNC <sub>IN</sub> pin; see Table 1 and the description for SYNC <sub>IN</sub> for additional details.     |

| 7      | SYNC <sub>IN</sub> | Triple function pin: High/Low/ExtClock. Setting this pin high sets $CLK_{OUT}$ to the internal oscillator frequency ( $f_{SW}$ ) but with 180 degree phase shift. Setting this pin low disables the $CLK_{OUT}$ pin. Applying an external clock (at $f_{SYNC}$ ) forces PWM mode, synchronizes the PWM switching frequency to the external clock plus dithering, and sets $CLK_{OUT}$ to the same dithered frequency but with 180 degree phase shift. See Table 1 for details. |

| 8      | GND                | Analog ground pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

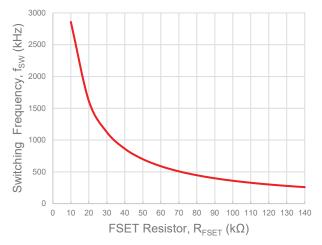

| 9      | FSET               | Frequency setting pin. A resistor, $R_{\mbox{\scriptsize FSET}},$ from this pin to GND sets the oscillator frequency, $f_{\mbox{\scriptsize SW}}.$                                                                                                                                                                                                                                                                                                                             |

| 10     | PWM/<br>AUTO       | Mode selection pin. High/Low. Setting this pin high forces PWM mode. Setting this pin low allows AUTO changeover between PWM and LP mode based on the load current.                                                                                                                                                                                                                                                                                                            |

| 11     | COMP               | Output of the error amplifier and compensation node for the current mode control loop. Connect a series RC network from this pin to GND for loop compensation.                                                                                                                                                                                                                                                                                                                 |

| 12     | PGOOD              | Power good output signal. PGOOD is an open-drain output that remains low until the output has achieved regulation for $t_{dPG(SU)}$ . The PGOOD pull-up resistor can be connected to VREG, VOUT, or any external supply voltage less than 5.5 V. PGOOD will pull low if the output voltage ( $V_{OUT}$ ) is out of range.                                                                                                                                                      |

| 13     | BIAS               | Connect this pin to the output of the regulator. This pin supplies the internal circuitry when the voltage level is high enough.                                                                                                                                                                                                                                                                                                                                               |

| 14     | FB                 | Feedback (negative) input to the error amplifier. Connect a resistor divider from the regulators output, V <sub>OUT</sub> , to this pin to program the output voltage.                                                                                                                                                                                                                                                                                                         |

| 15     | VREG               | Internal voltage regulator bypass capacitor pin. Connect a 4.7 µF capacitor from this pin to PGND and place it very close to the ARG81800.                                                                                                                                                                                                                                                                                                                                     |

| 16, 17 | PGND               | Power ground pins for the lower MOSFET, gate driver, and BOOT charge circuit.                                                                                                                                                                                                                                                                                                                                                                                                  |

| 18     | NC                 | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 19, 20 | VIN                | Power input for the control circuits and the drain of the internal high-side N-channel MOSFET. Bypass VIN to PGND with an X7R or X8R ceramic capacitor. Place the capacitor as close to the VIN and PGND pins as possible. Additional capacitors may be required depending on the application to comply with EMC requirements.                                                                                                                                                 |

| _      | PAD                | Exposed pad of the package providing enhanced thermal dissipation. This pad must be connected to the ground plane of the PCB with at least 6 vias directly in the pad.                                                                                                                                                                                                                                                                                                         |

# 40 V, 500 mA / 1.0 A Synchronous Buck Regulators with Ultralow Quiescent Current, SYNC $_{\rm IN},$ CLK $_{\rm OUT},$ and PGOOD

### ELECTRICAL CHARACTERISTICS: Valid at 3.5 V $\leq$ V<sub>IN</sub> $\leq$ 36 V, $-40^{\circ}$ C $\leq$ T<sub>J</sub> $\leq$ 150°C, unless otherwise specified

| Characteristics Symbol                       |                        | Test Conditions                                                                                        | Min. | Тур.               | Max. | Unit                 |

|----------------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------|------|--------------------|------|----------------------|

| INPUT VOLTAGE                                |                        | •                                                                                                      |      | ,                  |      | •                    |

| Input Voltage Range                          | V <sub>IN</sub>        | V <sub>IN</sub> must first rise above V <sub>INUV(ON)</sub> (max)                                      | 3.5  | _                  | 36   | V                    |

| VIN UVLO Start                               | V <sub>INUV(ON)</sub>  | V <sub>IN</sub> rising                                                                                 | 3.35 | 3.55               | 3.8  | V                    |

| VIN UVLO Stop                                | V <sub>INUV(OFF)</sub> | V <sub>IN</sub> falling                                                                                | 3.1  | 3.3                | 3.5  | V                    |

| VIN UVLO Hysteresis                          | V <sub>INUV(HYS)</sub> |                                                                                                        | -    | 250                | -    | mV                   |

| INPUT SUPPLY CURRENT                         |                        |                                                                                                        |      |                    |      |                      |

| Input Shutdown Current [2]                   | I <sub>IN(SD)</sub>    | V <sub>IN</sub> = 12 V, V <sub>EN</sub> = 0, V <sub>SW</sub> = V <sub>IN</sub> , T <sub>J</sub> = 25°C | _    | 1                  | 2    | μA                   |

| Input Current, PWM Mode [2]                  | I <sub>IN(PWM)</sub>   | V <sub>IN</sub> = 12 V, V <sub>EN</sub> = 2 V, no load, no switching                                   | -    | 5                  | 6.5  | mA                   |

| 2.2.1/                                       | T                      | V <sub>IN</sub> = 12 V, I <sub>OUT</sub> = 0 μA, T <sub>J</sub> = 25°C                                 | -    | 8                  | -    | μA                   |

| 3.3 V <sub>OUT</sub> LP Input Current [3][4] | I <sub>LP(3.3V)</sub>  | V <sub>IN</sub> = 12 V, I <sub>OUT</sub> = 50 μA, T <sub>J</sub> = 25°C                                | _    | 33                 | -    | μA                   |

| 5.0.1/                                       |                        | V <sub>IN</sub> = 12 V, I <sub>OUT</sub> = 0 μA, T <sub>J</sub> = 25°C                                 | _    | 8                  | -    | μA                   |

| 5.0 V <sub>OUT</sub> LP Input Current [3][4] | I <sub>LP(5.0V)</sub>  | V <sub>IN</sub> = 12 V, I <sub>OUT</sub> = 50 μA, T <sub>J</sub> = 25°C                                | -    | 44                 | -    | μA                   |

| REGULATION ACCURACY (FB PIN                  | 1)                     |                                                                                                        | `    |                    | •    |                      |

| Feedback Voltage Accuracy                    | V <sub>FB</sub>        | $-40$ °C < T <sub>J</sub> < 150°C, V <sub>IN</sub> $\ge$ 3.5 V, V <sub>FB</sub> = V <sub>COMP</sub>    | 788  | 800                | 812  | mV                   |

| SWITCHING FREQUENCY AND DI                   | THERING (FSE           | T PIN)                                                                                                 |      |                    |      |                      |

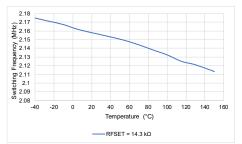

|                                              | f <sub>SW</sub>        | $R_{FSET}$ = 14.3 k $\Omega$                                                                           | 1.93 | 2.15               | 2.37 | MHz                  |

| DIAMA Conitabina Francisco                   |                        | R <sub>FSET</sub> = 34 kΩ                                                                              | 0.90 | 1.00               | 1.10 | MHz                  |

| PWM Switching Frequency                      |                        | R <sub>FSET</sub> = 71.5 kΩ                                                                            | 450  | 500                | 550  | kHz                  |

|                                              |                        | R <sub>FSET</sub> = 86.6 kΩ                                                                            | 360  | 410                | 460  | kHz                  |

| Dropout Switching Frequency                  | f <sub>DROP</sub>      |                                                                                                        | -    | f <sub>SW</sub> /4 | -    | -                    |

| PWM Frequency Dither Range                   | f                      | CLK <sub>OUT</sub> left open                                                                           | -    | ±5                 | ±6.5 | % of f <sub>SW</sub> |

| PWW Frequency Ditrier Range                  | f <sub>DITH(RNG)</sub> | CLK <sub>OUT</sub> connected to VREG                                                                   | -    | 0                  | -    | % of f <sub>SW</sub> |

| PWM Dither Modulation Frequency              | f <sub>DITH(MAG)</sub> |                                                                                                        | _    | ±0.5               | -    | % of f <sub>SW</sub> |

| PULSE WIDTH MODULATION (PW                   | M) TIMING AN           | D CONTROL                                                                                              |      |                    |      |                      |

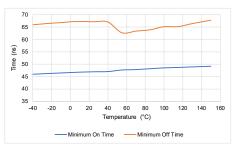

| Minimum Controllable SW On-Time              | t <sub>ON(MIN)</sub>   | $V_{IN}$ = 12 V, $I_{OUT}$ = 0.7 A, $V_{BOOT} - V_{SW}$ = 4.5 V                                        | -    | 60                 | 85   | ns                   |

| Minimum SW Off-Time                          | t <sub>OFF(MIN)</sub>  | V <sub>IN</sub> =12 V, I <sub>OUT</sub> = 0.7 A                                                        | -    | 85                 | 110  | ns                   |

| OOMB to OW Occurrent Octor                   | gm <sub>POWER1</sub>   | ARG81800                                                                                               | -    | 2.0                | -    | A/V                  |

| COMP to SW Current Gain                      | gm <sub>POWER2</sub>   | ARG81800-1                                                                                             | -    | 1.0                | -    | A/V                  |

|                                              | S <sub>E1</sub>        | f <sub>SW</sub> = 2.15 MHz, ARG81800                                                                   | 650  | 900                | 1100 | mA/µs                |

| Slane Companyation                           | S <sub>E2</sub>        | f <sub>SW</sub> = 2.15 MHz, ARG81800-1                                                                 | 325  | 450                | 550  | mA/µs                |

| Slope Compensation                           | S <sub>E3</sub>        | f <sub>SW</sub> = 252 kHz, ARG81800                                                                    | 75   | 100                | 125  | mA/µs                |

|                                              | S <sub>E4</sub>        | f <sub>SW</sub> = 252 kHz, ARG81800-1                                                                  | 35   | 50                 | 65   | mA/µs                |

| PWM Ramp Offset                              | V <sub>PWM(OFFS)</sub> |                                                                                                        | -    | 650                | -    | mV                   |

# 40 V, 500 mA / 1.0 A Synchronous Buck Regulators with Ultralow Quiescent Current, SYNC $_{\rm IN},$ CLK $_{\rm OUT},$ and PGOOD

### ELECTRICAL CHARACTERISTICS (continued): Valid at 3.5 V $\leq$ V<sub>IN</sub> $\leq$ 36 V, $-40^{\circ}$ C $\leq$ T<sub>J</sub> $\leq$ 150°C, unless otherwise specified

| Characteristics                                                                | Symbol                                | Test Conditions                                                                              | Min. | Тур.                           | Max. | Unit                     |

|--------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------|------|--------------------------------|------|--------------------------|

| LOW-POWER (LP) MODE                                                            | 1                                     |                                                                                              |      | ,                              |      |                          |

| LP Output Voltage Ripple [3][4]                                                | ΔV <sub>OUT(LP)</sub>                 | LP Mode, 8 V < V <sub>IN</sub> < 12 V                                                        | -    | 65                             | _    | mV                       |

| Lavar A. Davida Communitation about                                            | I <sub>PEAK(LP1)</sub>                | ARG81800, No Load, V <sub>IN</sub> = 12 V                                                    | 320  | 400                            | 500  | mA                       |

| Low I <sub>Q</sub> Peak Current Threshold                                      | I <sub>PEAK(LP2)</sub>                | ARG81800-1, No Load, V <sub>IN</sub> = 12 V                                                  | 160  | 212                            | 270  | mA                       |

| INTERNAL POWER SWITCHES                                                        | , , , , , , , , , , , , , , , , , , , |                                                                                              |      |                                |      |                          |

| High Cide MOCEET On Desistance                                                 |                                       | $T_J = 25^{\circ}C^{[3]}$ , $V_{BOOT} - V_{SW} = 4.5 \text{ V}$ , $I_{DS} = 800 \text{ mA}$  | _    | 500                            | 600  | mΩ                       |

| High-Side MOSFET On-Resistance                                                 | R <sub>DS(on)HS</sub>                 | $T_J = 150$ °C, $V_{BOOT} - V_{SW} = 4.5$ V, $I_{DS} = 800$ mA                               | -    | -                              | 1075 | mΩ                       |

| Law Oids MOOFFT On Basistan                                                    | _                                     | $T_J = 25^{\circ}C^{[3]}, V_{IN} \ge 4.5 \text{ V}, I_{DS} = 1 \text{ A}$                    | -    | 210                            | 250  | mΩ                       |

| Low-Side MOSFET On-Resistance                                                  | R <sub>DS(on)LS</sub>                 | $T_J = 150$ °C, $V_{IN} \ge 4.5$ V, $I_{DS} = 1$ A                                           | -    | -                              | 450  | mΩ                       |

| High-Side Leakage Current [5]                                                  | I <sub>LKG(HS)</sub>                  | $T_J = 25$ °C, $V_{IN} = 12$ V, $V_{EN} = 0$ V, $V_{SW} = 0$ V                               | -1.5 | -                              | 1.5  | μA                       |

| Low-Side Leakage Current                                                       | I <sub>LKG(HS)</sub>                  | T <sub>J</sub> = 25°C, V <sub>IN</sub> = 12 V, V <sub>EN</sub> = 0 V, V <sub>SW</sub> = 12 V | -1.5 | -                              | 1.5  | μA                       |

| Gate Drive Non-Overlap Time [3]                                                | t <sub>NO</sub>                       |                                                                                              | -    | 10                             | 25   | ns                       |

| Switch Node Rising Slew Rate                                                   | SR <sub>HS</sub>                      | 12 V < V <sub>IN</sub> < 16 V <sup>[3]</sup>                                                 | -    | 5                              | _    | V/ns                     |

| MOSFET CURRENT PROTECTION                                                      | THRESHOLD                             | S                                                                                            |      |                                |      |                          |

| Himb Cida Command Limit                                                        | I <sub>LIMHS1</sub>                   | $t_{ON} = t_{ON(MIN)}$ , ARG81800                                                            | 1.7  | 2.0                            | 2.3  | А                        |

| High-Side Current Limit                                                        | I <sub>LIMHS2</sub>                   | $t_{ON} = t_{ON(MIN)}, ARG81800-1$                                                           | 0.85 | 1.0                            | 1.15 | Α                        |

| Low-Side Current Limit                                                         | I <sub>LIMLSx</sub>                   |                                                                                              | -    | 50                             | _    | % of I <sub>LIMHSx</sub> |

| SYNCHRONIZATION INPUT (SYNC                                                    | IN PIN)                               |                                                                                              |      |                                |      |                          |

| Synchronization Frequency Range                                                | f <sub>SW(SYNC)</sub>                 |                                                                                              | 0.25 | -                              | 2.5  | MHz                      |

| SYNC <sub>IN</sub> Duty Cycle                                                  | DC <sub>SYNC</sub>                    |                                                                                              | 20   | 50                             | 70   | %                        |

| SYNC <sub>IN</sub> Pulse Width                                                 | t <sub>PWSYNC</sub>                   |                                                                                              | 80   | -                              | _    | ns                       |

| CVNC Voltage Thresholds                                                        | V <sub>SYNC(HI)</sub>                 | V <sub>SYNC(IN)</sub> rising                                                                 | -    | 1.35                           | 1.5  | V                        |

| SYNC <sub>IN</sub> Voltage Thresholds                                          | V <sub>SYNC(LO)</sub>                 | V <sub>SYNC(IN)</sub> falling                                                                | 8.0  | 1.2                            | _    | V                        |

| SYNC <sub>IN</sub> Hysteresis                                                  | V <sub>SYNC(HYS)</sub>                | V <sub>SYNC(HI)</sub> – V <sub>SYNC(LO)</sub>                                                | -    | 150                            | -    | mV                       |

| SYNC <sub>IN</sub> Pin Current                                                 | I <sub>SYNC</sub>                     | V <sub>SYNC(IN)</sub> = 5 V                                                                  | -    | ±1                             | -    | μA                       |

| CLOCK OUTPUT (CLK <sub>OUT</sub> PIN)                                          |                                       |                                                                                              |      |                                |      |                          |

| SYNC <sub>IN</sub> to CLK <sub>OUT</sub> Delay                                 | Φ <sub>SYNC(CLK)</sub>                | $R_{FSET}$ = 14.3 kΩ, $V_{SYNC(HI)}$ = 3.3 V, Dither disabled                                | -    | 1/(2×f <sub>SW</sub> )<br>± 70 | -    | ns                       |

| SW <sub>MASTER</sub> to SW <sub>FOLLOWER</sub> Delay [3] Φ <sub>SWM(SWF)</sub> |                                       | $R_{FSET}$ = 14.3 k $\Omega$ , $V_{SYNC(HI)}$ = 3.3 V                                        | -    | 1/(2×f <sub>SW</sub> )<br>± 30 | _    | ns                       |

| CLK Output Voltages                                                            | V <sub>CLK(OUT)H</sub>                | V <sub>VREG</sub> = 4.8 V                                                                    | 2.2  | _                              | _    | V                        |

| CLK <sub>OUT</sub> Output Voltages                                             | V <sub>CLK(OUT)L</sub>                | V <sub>VREG</sub> = 4.8 V                                                                    | -    | _                              | 0.6  | V                        |

# 40 V, 500 mA / 1.0 A Synchronous Buck Regulators with Ultralow Quiescent Current, SYNC $_{\rm IN}$ , CLK $_{\rm OUT}$ , and PGOOD

### ELECTRICAL CHARACTERISTICS (continued): Valid at 3.5 V $\leq$ V<sub>IN</sub> $\leq$ 36 V, $-40^{\circ}$ C $\leq$ T<sub>J</sub> $\leq$ 150°C, unless otherwise specified

| Characteristics                                 | Symbol                  | Test Conditions                                 | Min. | Тур.                | Max. | Unit                   |

|-------------------------------------------------|-------------------------|-------------------------------------------------|------|---------------------|------|------------------------|

| ERROR AMPLIFIER                                 | ·                       |                                                 | ,    | '                   |      |                        |

| Feedback Input Bias Current [2]                 | I <sub>FB</sub>         | V <sub>FB</sub> = 800 mV                        | -40  | _                   | -15  | nA                     |

| Open-Loop Voltage Gain                          | A <sub>VOL</sub>        |                                                 | -    | 65                  | -    | dB                     |

| Transconductance                                |                         | V <sub>FB</sub> > 400 mV                        | 550  | 750                 | 950  | μA/V                   |

| Transconductance                                | gm                      | 0 V < V <sub>FB</sub> < 400 mV                  | 275  | 375                 | 550  | μA/V                   |

| Output Current                                  | I <sub>EA</sub>         |                                                 | _    | ±75                 | -    | μA                     |

| COMP Pull-Down Resistance                       | R <sub>COMP</sub>       | FAULT = 1 or HICCUP = 1                         | _    | 1                   | -    | kΩ                     |

| SOFT START                                      |                         |                                                 |      |                     |      |                        |

| Startup (Source) Current                        | I <sub>SS</sub>         | HICCUP = FAULT = 0                              | -30  | -20                 | -10  | μA                     |

| Hiccup/Dropout (Sink) Current                   | I <sub>HIC</sub>        | HICCUP = 1 or Dropout Mode                      | 1    | 2.2                 | 5    | μA                     |

| Soft Start Delay Time [3]                       | t <sub>dSS</sub>        | C <sub>SS</sub> = 22 nF                         | _    | 440                 | -    | μs                     |

| Soft Start Ramp Time [3]                        | t <sub>SS</sub>         | C <sub>SS</sub> = 22 nF                         | _    | 880                 | -    | μs                     |

| FAULT/HICCUP Reset Voltage                      | V <sub>SSRST</sub>      | V <sub>SS</sub> falling due to HICCUP or FAULT  | _    | 200                 | 275  | mV                     |

| Hiccup OCP (and LP) Counter Enable<br>Threshold | V <sub>HIC/LP(EN)</sub> | V <sub>SS</sub> rising                          | -    | 2.3                 | -    | V                      |

|                                                 |                         | 0 V < V <sub>FB</sub> < 200 mV                  | _    | f <sub>SW</sub> / 4 | _    | _                      |

| Soft Start Frequency Foldback                   | f <sub>SW(SS)</sub>     | 200 mV < V <sub>FB</sub> < 400 mV               | _    | f <sub>SW</sub> / 2 | _    | _                      |

|                                                 |                         | 400 mV < V <sub>FB</sub>                        | _    | f <sub>SW</sub>     | -    | _                      |

| Maximum Voltage                                 | V <sub>SS(MAX)</sub>    | V <sub>EN</sub> = 0 V or FAULT without HICCUP   | _    | V <sub>VREG</sub>   | -    | -                      |

| Pull-Down Resistance                            | R <sub>SS(FLT)</sub>    |                                                 |      | 2                   |      | kΩ                     |

| HICCUP MODE COUNTS                              |                         |                                                 |      |                     |      |                        |

| High-Side Overcurrent Count                     | HIC <sub>OC</sub>       | After V <sub>SS</sub> > V <sub>HIC/LP(EN)</sub> | _    | 120                 | _    | f <sub>SW</sub> counts |

| SW Short-to-Ground Count                        | HIC <sub>SW(GND)</sub>  |                                                 | -    | 2                   | -    | f <sub>SW</sub> counts |

| BOOT Short Circuit Count                        | HIC <sub>BOOT(SC)</sub> |                                                 | -    | 120                 | -    | f <sub>SW</sub> counts |

| BOOT Open Circuit Count [3]                     | HIC <sub>BOOT(OC)</sub> |                                                 | -    | 7                   | -    | f <sub>SW</sub> counts |

# 40 V, 500 mA / 1.0 A Synchronous Buck Regulators with Ultralow Quiescent Current, SYNC $_{\rm IN}$ , CLK $_{\rm OUT}$ , and PGOOD

### ELECTRICAL CHARACTERISTICS (continued): Valid at 3.5 V $\leq$ V<sub>IN</sub> $\leq$ 36 V, $-40^{\circ}$ C $\leq$ T<sub>J</sub> $\leq$ 150°C, unless otherwise specified

| Characteristics                | Symbol                                             | Test Conditions                                                                        | Min. | Тур. | Max. | Unit                   |  |  |  |  |  |  |

|--------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------|------|------|------|------------------------|--|--|--|--|--|--|

| OUTPUT VOLTAGE PROTECTION      | OUTPUT VOLTAGE PROTECTION THRESHOLDS (VFB, OV, UV) |                                                                                        |      |      |      |                        |  |  |  |  |  |  |

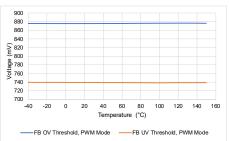

| VFB OV PWM Threshold           | V <sub>FB(OV)</sub>                                | V <sub>FB</sub> rising                                                                 | 850  | 880  | 900  | mV                     |  |  |  |  |  |  |

| VFB OV PWM Hysteresis          | V <sub>FB(OV,HYS)</sub>                            | V <sub>FB</sub> falling, relative to V <sub>FB(OV)</sub>                               | _    | -15  | _    | mV                     |  |  |  |  |  |  |

| VFB UV PWM Threshold           | V <sub>FB(UV)</sub>                                | V <sub>FB</sub> falling                                                                | 716  | 740  | 764  | mV                     |  |  |  |  |  |  |

| VFB UV PWM Hysteresis          | V <sub>FB(UV,HYS)</sub>                            | V <sub>FB</sub> rising, relative to V <sub>FB(UV)</sub>                                | _    | +15  | _    | mV                     |  |  |  |  |  |  |

| VFB UV LP Mode Threshold [3]   | V <sub>FB(UV,LP)</sub>                             | V <sub>FB</sub> falling                                                                | 665  | 700  | 735  | mV                     |  |  |  |  |  |  |

| POWER GOOD OUTPUT (PGOOD       | PIN)                                               |                                                                                        |      |      |      |                        |  |  |  |  |  |  |

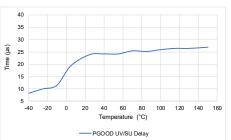

| PGOOD Startup (SU) Delay       | t <sub>dPG(SU)</sub>                               | Increasing V <sub>FB</sub> due to startup                                              | _    | 30   | -    | μs                     |  |  |  |  |  |  |

| PGOOD Undervoltage (UV) Delay  | t <sub>dPG(UV)</sub>                               | Decreasing VFB                                                                         | _    | 30   | _    | μs                     |  |  |  |  |  |  |

| PGOOD Overvoltage (OV) Delay   | t <sub>dPG(OV)</sub>                               | After an overvoltage event                                                             | -    | 240  | _    | f <sub>SW</sub> cycles |  |  |  |  |  |  |

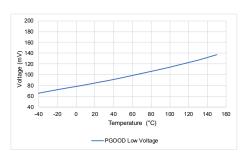

| PGOOD Low Voltage              | $V_{PG(L)}$                                        | I <sub>PGOOD</sub> = 5 mA                                                              | _    | 200  | 400  | mV                     |  |  |  |  |  |  |

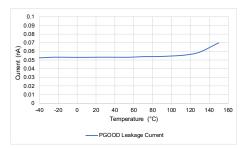

| PGOOD Leakage [1]              | I <sub>PG(LKG)</sub>                               | V <sub>PGOOD</sub> = 5.5 V                                                             | _    | -    | 2    | μA                     |  |  |  |  |  |  |

| PWM/AUTO INPUT                 |                                                    |                                                                                        |      |      |      |                        |  |  |  |  |  |  |

| PWM/AUTO High Threshold        | V <sub>HI(PWM)</sub>                               | V <sub>PWM/AUTO</sub> rising                                                           | 1.8  | 2.0  | 2.5  | V                      |  |  |  |  |  |  |

| PWM/AUTO Float Voltage         | V <sub>FLOAT(PWM)</sub>                            | V <sub>PWM/AUTO</sub> floating                                                         | 1.1  | 1.4  | 1.7  | V                      |  |  |  |  |  |  |

| PWM/AUTO Low Threshold         | V <sub>LO(PWM)</sub>                               | V <sub>PWM/AUTO</sub> falling                                                          | 0.6  | 0.8  | 1.0  | V                      |  |  |  |  |  |  |

| PWM to LP Transition Delay [3] | t <sub>dPWM(LP)</sub>                              | V <sub>PWM/AUTO</sub> = 0 V, V <sub>SS</sub> > V <sub>HIC/LP(EN)</sub> ,<br>PGOOD high | -    | 7.5  | -    | ms                     |  |  |  |  |  |  |

| ENABLE INPUT (EN PIN)          |                                                    |                                                                                        |      |      |      |                        |  |  |  |  |  |  |

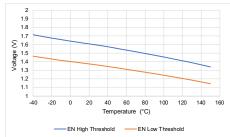

| Enable High Threshold          | V <sub>ENHI</sub>                                  | V <sub>EN</sub> rising                                                                 | _    | 1.6  | 2.0  | V                      |  |  |  |  |  |  |

| Enable Low Threshold           | V <sub>ENLO</sub>                                  | V <sub>EN</sub> falling                                                                | 0.8  | 1.4  | -    | V                      |  |  |  |  |  |  |

| Enable Input Hysteresis        | V <sub>ENHYS</sub>                                 | V <sub>ENHI</sub> – V <sub>ENLO</sub>                                                  | -    | 200  | -    | mV                     |  |  |  |  |  |  |

| Disable Delay                  | t <sub>DISDLY</sub>                                | V <sub>EN</sub> transitions low to when SW stops switching                             | -    | 120  | -    | f <sub>SW</sub> cycles |  |  |  |  |  |  |

| Enable Pin Input Current       | I <sub>EN</sub>                                    | V <sub>EN</sub> = V <sub>PWM/AUTO</sub> = 5 V                                          | _    | 12   | _    | μA                     |  |  |  |  |  |  |

### 40 V, 500 mA / 1.0 A Synchronous Buck Regulators with Ultralow Quiescent Current, SYNC $_{\rm IN}$ , CLK $_{\rm OUT}$ , and PGOOD

#### ELECTRICAL CHARACTERISTICS (continued): Valid at 3.5 V $\leq$ V<sub>IN</sub> $\leq$ 36 V, $-40^{\circ}$ C $\leq$ T<sub>J</sub> $\leq$ 150°C, unless otherwise specified

| Characteristics              | Symbol             | nbol Test Conditions                                                     |      | Тур.            | Max. | Unit |  |  |  |  |

|------------------------------|--------------------|--------------------------------------------------------------------------|------|-----------------|------|------|--|--|--|--|

| BOOT REGULATOR (BOOT PIN)    |                    |                                                                          |      |                 |      |      |  |  |  |  |

| BOOT Charging Frequency      | f <sub>BOOT</sub>  |                                                                          | _    | f <sub>SW</sub> | -    | _    |  |  |  |  |

| BOOT Voltage                 | V <sub>BOOT</sub>  | $V_{IN}$ = 12 V, $V_{BOOT} - V_{SW}$                                     | _    | 4.8             | 5.3  | V    |  |  |  |  |

| INTERNAL REGULATOR (VREG PIN | ۷)                 |                                                                          |      |                 |      |      |  |  |  |  |

| BIAS Disconnected            | V <sub>VREG1</sub> | 6 V < V <sub>VIN</sub> < 36 V, V <sub>BIAS</sub> = 0 V                   | 4.5  | 4.8             | 5.1  | V    |  |  |  |  |

| BIAS Connected               | V                  | VBIAS = 3.3V                                                             | 2.85 | 3.2             | 3.29 | V    |  |  |  |  |

| BIAS Connected               | $V_{VREG2}$        | 6 V < V <sub>BIAS</sub> < 20 V                                           | 4.5  | 4.8             | 5.1  | V    |  |  |  |  |

| BIAS Input Voltage Range     | V <sub>BIAS</sub>  |                                                                          | 3.3  | -               | 36   | V    |  |  |  |  |

| THERMAL SHUTDOWN PROTECTION  | ON (TSD)           |                                                                          |      |                 |      |      |  |  |  |  |

|                              |                    | $\rm T_{J}$ rising, PWM stops immediately and COMP and SS are pulled low | 155  | 170             | _    | °C   |  |  |  |  |

| TSD Hysteresis [3]           | T <sub>SDHYS</sub> | T <sub>J</sub> falling, relative to T <sub>TSD</sub>                     | -    | 20              | -    | °C   |  |  |  |  |

<sup>[1]</sup> Negative current is defined as coming out of the node or pin, positive current is defined as going into the node or pin.

<sup>[2]</sup> Thermally limited depending on input voltage, duty cycle, regulator load currents, PCB layout, and airflow.

<sup>[3]</sup> Ensured by design and characterization, not production tested.

<sup>[4]</sup> Using recommended external components specified in Table 3.

[5] At V<sub>IN</sub> = 36 V, I<sub>OUT</sub> = 0 A, and T<sub>J</sub> = 150°C, V<sub>OUT</sub> rises to overvoltage threshold due to leakage.

# 40 V, 500 mA / 1.0 A Synchronous Buck Regulators with Ultralow Quiescent Current, SYNC $_{\rm IN},$ CLK $_{\rm OUT},$ and PGOOD

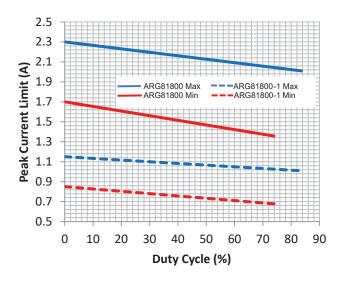

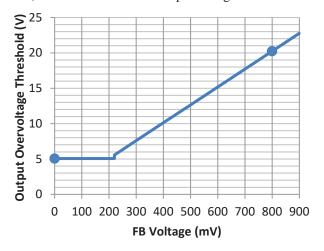

#### TYPICAL PERFORMANCE CHARACTERISTICS

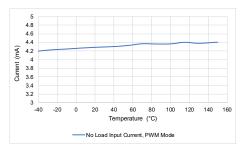

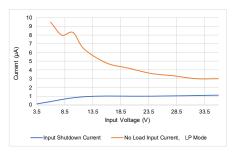

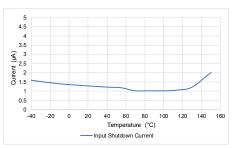

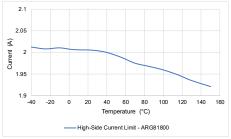

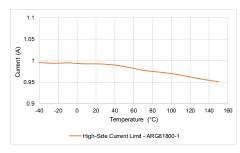

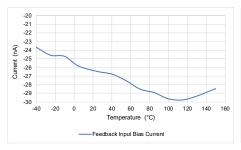

$V_{IN} = V_{EN} = 12$  V,  $C_{BOOT} = 0.1$   $\mu$ F,  $C_{SS} = 22$  nF, unless otherwise noted  $-40^{\circ}\text{C} \le T_{J} \le 150^{\circ}\text{C}$ . Typical Values are at  $T_{A} = 25^{\circ}\text{C}$ . ARG81800,  $V_{OUT} = 3.3$  V,  $f_{SW} = 2.15$  MHz. See Table 3 for External Component Values. ARG81800-1,  $V_{OUT} = 5.0$ V,  $f_{SW} = 0.4$  MHz. See Table 3 for External Component Values.

3.5 8.5 13.5 18.5 23.5 28.5 33.5 38.5 Input Voltage (V)

—No Load Input Current, PWM Mode

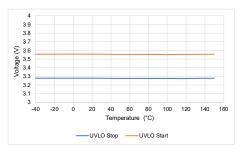

UVLO Start and Stop Thresholds vs. Temperature

No-Load Input Current (PWM Mode) vs. Input Voltage

No-Load Input Current (PWM Mode) vs. Temperature

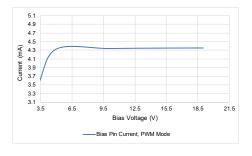

Input Current vs. Input Voltage

Input Shutdown Current vs. Temperature

EN High and Low Thresholds vs. Temperature

804

Bias Pin Current vs. Output Voltage

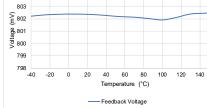

Feedback Voltage vs. Temperature

160

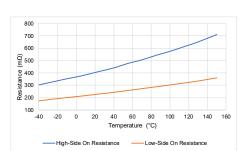

On Resistance (High-Side and Low-Side) vs. Temperature

#### TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN} = V_{EN} = 12$  V,  $C_{BOOT} = 0.1$   $\mu$ F,  $C_{SS} = 22$  nF, unless otherwise noted  $-40^{\circ}\text{C} \le T_{J} \le 150^{\circ}\text{C}$ . Typical Values are at  $T_{A} = 25^{\circ}\text{C}$ . ARG81800,  $V_{OUT} = 3.3$  V,  $f_{SW} = 2.15$  MHz. See Table 3 for External Component Values. ARG81800-1,  $V_{OUT} = 5.0$ V,  $f_{SW} = 0.4$  MHz. See Table 3 for External Component Values.

Minimum On and Off Time vs. Temperature

High-Side Current Limit vs. Temperature – ARG81800

High-Side Current Limit vs. Temperature – ARG81800-1

Feedback Input Bias Current vs. Temperature

PGOOD Delay (UV and SU) vs. Temperature

PGOOD Leakage Current vs. Temperature

PGOOD Low Voltage vs. Temperature

Feedback OV and UV Threshold vs. Temperature

Switching Frequency vs. Temperature

#### TYPICAL PERFORMANCE CHARACTERISTICS

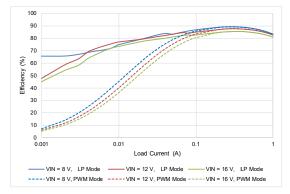

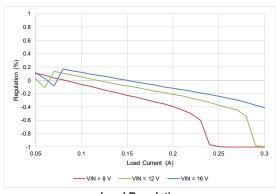

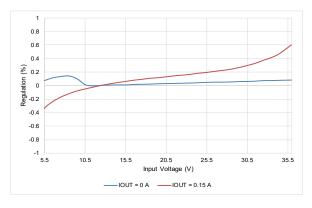

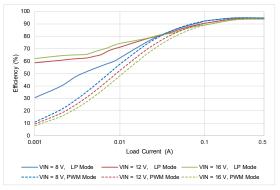

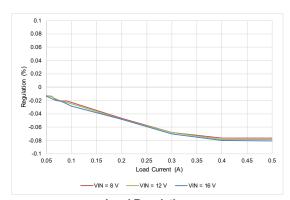

$V_{IN} = V_{EN} = 12 \text{ V}, C_{BOOT} = 0.1 \text{ } \mu\text{F}, C_{SS} = 22 \text{ nF}, \text{ unless otherwise noted } -40^{\circ}\text{C} \leq T_{J} \leq 150^{\circ}\text{C}. \text{ Typical Values are at } T_{A} = 25^{\circ}\text{C}.$  ARG81800,  $V_{OUT} = 3.3 \text{ V}, f_{SW} = 2.15 \text{ MHz}.$  See Table 3 for External Component Values. ARG81800-1,  $V_{OUT} = 5.0 \text{V}, f_{SW} = 0.4 \text{ MHz}.$  See Table 3 for External Component Values.

Efficency vs. Load Current  $V_{OUT} = 3.3 \text{ V}, f_{SW} = 2.15 \text{ MHz}$

$\label{eq:Vouter} \mbox{Load Regulation} \\ \mbox{V}_{\mbox{OUT}} = 3.3 \mbox{ V, } \mbox{f}_{\mbox{SW}} = 2.15 \mbox{ MHz, LP Mode}$

$\label{eq:Vout} \mbox{Line Regulation} $$V_{OUT} = 3.3 \ V, \, f_{SW} = 2.15 \ \mbox{MHz}, \, \mbox{LP Mode} $$$

Efficency vs. Load Current V<sub>OUT</sub> = 5.0 V, f<sub>SW</sub> = 400 kHz

$\label{eq:vout} \begin{tabular}{ll} Load Regulation \\ V_{OUT} = 5.0 \ V, f_{SW} = 400 \ kHz, PWM \ Mode \\ \end{tabular}$

$\label{eq:Vouter} \mbox{Line Regulation} \\ \mbox{V}_{\mbox{OUT}} = 5.0 \mbox{ V, } \mbox{f}_{\mbox{SW}} = 400 \mbox{ kHz, PWM Mode} \\$

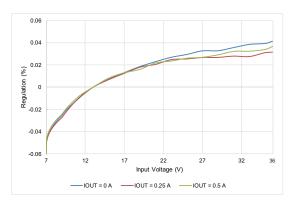

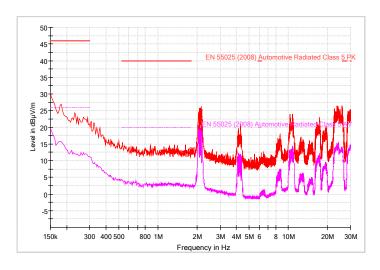

#### TYPICAL PERFORMANCE CHARACTERISTICS

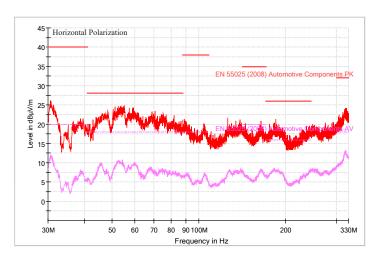

$V_{IN} = V_{EN} = 12 \text{ V}, C_{BOOT} = 0.1 \text{ } \mu\text{F}, C_{SS} = 22 \text{ nF}, \text{ unless otherwise noted } -40^{\circ}\text{C} \leq T_{J} \leq 150^{\circ}\text{C}. \text{ Typical Values are at } T_{A} = 25^{\circ}\text{C}.$  ARG81800,  $V_{OUT} = 3.3 \text{ V}, f_{SW} = 2.15 \text{ MHz}.$  See Table 3 for External Component Values. ARG81800-1,  $V_{OUT} = 5.0 \text{V}, f_{SW} = 0.4 \text{ MHz}.$  See Table 3 for External Component Values.

V<sub>OUT</sub> = 3.3 V, I<sub>OUT</sub> = 1.0 A, PWM Mode

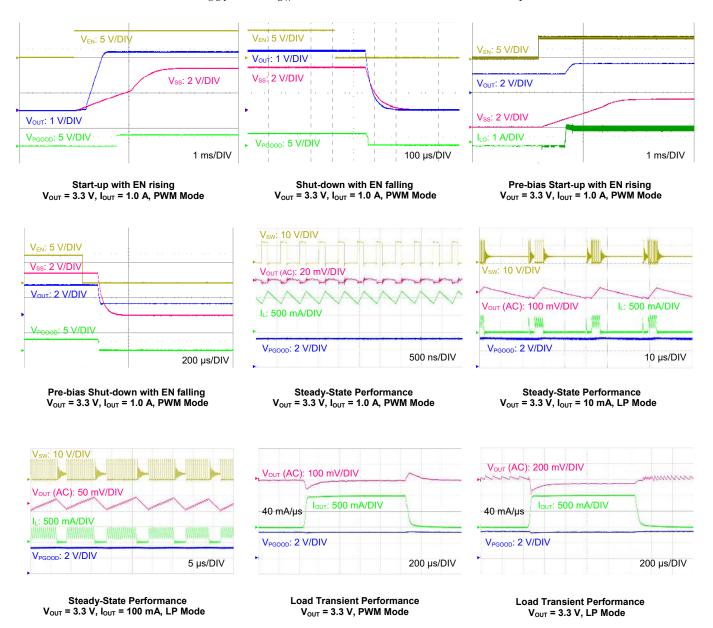

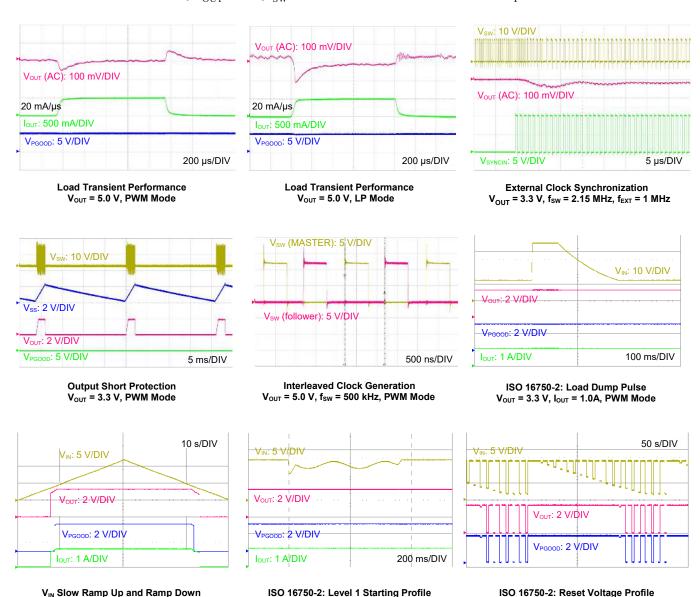

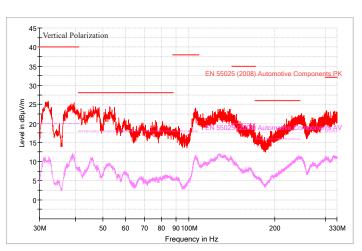

#### TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN} = V_{EN} = 12$  V,  $C_{BOOT} = 0.1$   $\mu$ F,  $C_{SS} = 22$  nF, unless otherwise noted  $-40^{\circ}\text{C} \le T_{J} \le 150^{\circ}\text{C}$ . Typical Values are at  $T_{A} = 25^{\circ}\text{C}$ . ARG81800,  $V_{OUT} = 3.3$  V,  $f_{SW} = 2.15$  MHz. See Table 3 for External Component Values. ARG81800-1,  $V_{OUT} = 5.0$ V,  $f_{SW} = 0.4$  MHz. See Table 3 for External Component Values.

V<sub>OUT</sub> = 3.3 V, I<sub>OUT</sub> = 1.0 A, PWM Mode

V<sub>OUT</sub> = 3.3 V, I<sub>OUT</sub> = 1.0 A, PWM Mode

# 40 V, 500 mA / 1.0 A Synchronous Buck Regulators with Ultralow Quiescent Current, SYNC $_{\rm IN}$ , CLK $_{\rm OUT}$ , and PGOOD

#### **FUNCTIONAL DESCRIPTION**

#### Overview

The ARG81800 is a wide input voltage (3.5 to 36 V) synchronous PWM buck regulator that integrates low  $R_{\rm DS(on)}$  high-side and low-side N-channel MOSFETs. The ARG81800 employs peak current mode control to provide superior line and load regulation, cycle-by-cycle current limit, fast transient response, and simple compensation. The features of the ARG81800 include ultralow  $I_Q$  LP mode, extremely low minimum on-time, maximized duty cycle for low dropout operation, soft recovery from dropout condition, and pre-bias startup capability.

Protection features of the ARG81800 include VIN undervoltage lockout, cycle-by-cycle overcurrent protection, BOOT overvoltage and undervoltage protection, hiccup mode short circuit protection, overvoltage protection, and thermal shutdown. In addition, the ARG81800 provides open circuit, adjacent pin short circuit, and pin-to-ground short circuit protection.

#### Reference Voltage

The ARG81800 incorporates an internal precision reference that allows output voltages as low as 0.8 V. The accuracy of the internal reference is  $\pm 1.5\%$  across  $-40^{\circ}$ C to 150°C. The output voltage of the regulator is programmed with a resistor divider between VOUT and the FB pin of the ARG81800.

#### Internal VREG Regulator

VREG is used as the power supply for internal control circuitry and a low-side MOSFET driver. The ARG81800 consists of two internal low dropout regulators, VIN LDO and Bias LDO, to generate VREG voltage. VIN LDO is powered from input voltage to generate 4.8 V for VREG supply. Bias LDO uses the BIAS pin as a supply to generate VREG voltage. When voltage at the BIAS pin exceeds 3.0 V, VIN LDO is deactivated and Bias LDO generates the VREG voltage. Bias LDO can be made more efficient than VIN LDO by providing an external voltage at the BIAS pin that is less than the input voltage. If the output voltage of the ARG81800 is programmed to be greater than 3.1 V, it is recommended to supply the output voltage to the BIAS pin to improve the efficiency of the regulator.

#### Oscillator/Switching Frequency

The PWM switching frequency of the ARG81800 is adjustable from 250 kHz to 2.4 MHz by programming the internal clock fre-

quency of the oscillator by connecting an FSET resistor from the FSET pin to GND. The internal clock has an accuracy of about  $\pm 10\%$  over the operating temperature range. Usually, an FSET resistor with  $\pm 1\%$  tolerance is recommended. A graph of switching frequency versus FSET resistor value is shown in the Design and Component Selection section. The ARG81800 will suspend operation if the FSET pin is shorted to GND or left open.

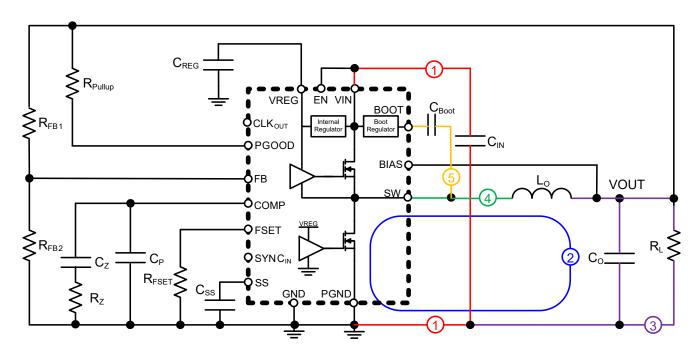

### Synchronization (SYNC<sub>IN</sub>) and Clock Output ( $CLK_{OUT}$ )

The Phase-Locked Loop (PLL) in the ARG81800 allows its internal oscillator to be synchronized to an external clock applied on the SYNC $_{\rm IN}$  pin. If the SYNC $_{\rm IN}$  pin is driven by an external clock, the ARG81800 will be forced to operate in PWM mode, with synchronized switching frequency, overriding the mode selection on the PWM/AUTO pin. The external clock must also satisfy the pulse width, duty cycle, and rise/fall time requirements shown in the Electrical Characteristics table. If the SYNC $_{\rm IN}$  pin is continuously pulled high, the ARG81800 outputs a 180-degree phase-shifted internal oscillator clock on the CLK $_{\rm OUT}$  pin, so "downstream" ARG81800 devices can be easily interleaved via their synchronization inputs. Figure 1 shows the usage of multiple ARG81800 devices in master-follower configuration. If the SYNC $_{\rm IN}$  pin is continuously pulled low, the device disables the CLK $_{\rm OUT}$  pin.

#### Frequency Dither

In addition to EMI-aware PCB layout, extensive filtering, controlled switch node transitions, and shielding, switching frequency dithering is an effective way to mitigate EMI concerns in switching power supplies. Frequency dither helps to minimize peak emissions by spreading the emissions across a wide range of frequencies. The ARG81800 provides frequency dither by spreading the switching frequency ±5% using a triangular modulated wave of 0.5% switching frequency.

The ARG81800 is capable of adding dither to the external clock applied on the SYNC $_{\rm IN}$  pin. This unique feature allows the minimizing of electromagnetic emissions even when the device is using external clock. Frequency dither scheme can be disabled by connecting the CLK $_{\rm OUT}$  pin to VREG pin. In master-follower configuration, the CLK $_{\rm OUT}$  pin of the follower device should be connected to VREG to avoid double-dithering.

# 40 V, 500 mA / 1.0 A Synchronous Buck Regulators with Ultralow Quiescent Current, SYNC $_{\rm IN},$ CLK $_{\rm OUT},$ and PGOOD

Figure 1: Master-Follower Configuration

Table 1: PWM Frequency, CLKOUT, and Dithering Settings

|                           |                   |                                                       | PWM Frequency and Dithering |                                |                          | CLK <sub>OUT</sub> Frequency and Dithering |                                |  |  |

|---------------------------|-------------------|-------------------------------------------------------|-----------------------------|--------------------------------|--------------------------|--------------------------------------------|--------------------------------|--|--|

| Device SYNC <sub>IN</sub> |                   | SW<br>Frequency                                       | Magnitude of<br>Dithering   | Dither Modulation<br>Frequency | Frequency                | Magnitude of<br>Dithering                  | Dither Modulation<br>Frequency |  |  |

|                           | Low               | f <sub>SW</sub>                                       | 10.05 v.f                   | 0.005 v.f                      | Disabled/Off             | None                                       | None                           |  |  |

| ARG81800/<br>ARG81800-1   | High              | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |                             | f <sub>SW</sub> + 180°         | ±0.05 × f <sub>SW</sub>  | 0.005 × f <sub>SW</sub>                    |                                |  |  |

|                           | f <sub>SYNC</sub> | f <sub>SYNC</sub>                                     | ±0.05 × f <sub>SW</sub>     | 0.005 × f <sub>SW</sub>        | f <sub>SYNC</sub> + 180° | ±0.05 × f <sub>SYNC</sub>                  | 0.005 × f <sub>SYNC</sub>      |  |  |

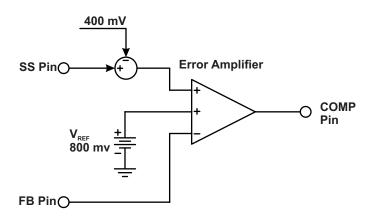

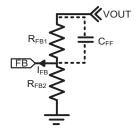

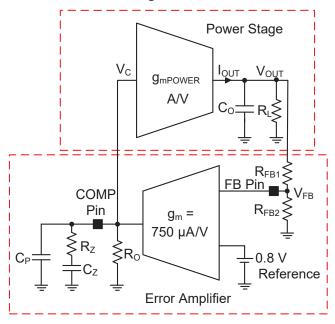

#### **Transconductance Error Amplifier**

The transconductance error amplifier's primary function is to control the regulator's output voltage. The error amplifier is a three-terminal input device with two positive inputs and one negative input, as shown in Figure 2. The negative input is simply connected to the FB pin and is used to sense the feedback voltage for regulation. The error amplifier performs an "analog OR" selection between its positive inputs and operates according to the positive input with the lowest potential. The two positive inputs are used for soft-start and steady-state regulation. The error amplifier regulates to the soft-start pin voltage minus 400 mV during startup and to the internal reference (VREF) during normal operation.

Figure 2: ARG81800 Error Amplifier

# 40 V, 500 mA / 1.0 A Synchronous Buck Regulators with Ultralow Quiescent Current, SYNC $_{\rm IN}$ , CLK $_{\rm OUT}$ , and PGOOD

#### **Compensation Components**

To stabilize the regulator, a series RC compensation network ( $R_Z$  and  $C_Z$ ) must be connected from the output of the error amplifier (COMP pin) to GND as shown in the applications schematic. In most instances, an additional low-value capacitor ( $C_P$ ) should be connected in parallel with the  $R_Z$ - $C_Z$  compensation network to reduce the loop gain at very high frequencies. However, if the  $C_P$  capacitor is too large, the phase margin of the converter may be reduced. Calculation of  $R_Z$ ,  $C_Z$ , and  $C_P$  is covered in the Component Selection section of this datasheet. If a fault occurs or the regulator is disabled, the COMP pin is pulled to GND via the approximately 1 k $\Omega$  internal resistor and PWM switching is inhibited.

#### **Power MOSFETs**

The ARG81800 includes a 500 m $\Omega$ , high-side N-channel MOSFET and a 210 m $\Omega$ , low-side N-channel MOSFET to provide synchronous rectification. When the ARG81800 is disabled via the EN input being low or a fault condition, its output stage is tristated by turning off both the upper and lower MOSFETs.

#### **BOOT Regulator**

The ARG81800 includes a BOOT regulator to supply the power for a high-side MOSFET gate driver. The voltage across the BOOT capacitor is typically 4.8 V. If the BOOT capacitor is missing, the device will detect a BOOT overvoltage. Similarly, if the BOOT capacitor is shorted, the ARG81800 will detect a BOOT undervoltage. Also, the BOOT regulator has a current limit to protect itself during a short-circuit condition.

#### Soft Start (Startup) and Inrush Current Control

The soft start function controls the inrush current at startup. The soft start pin (SS) is connected to GND via a capacitor. When the ARG81800 is enabled and all faults are cleared, the SS pin sources the charging current  $I_{\rm SS}$  and the voltage on the soft start capacitor  $C_{\rm SS}$  starts ramping upward from 0 V. When the voltage at the soft start pin exceeds the soft start offset voltage (SS Offset), typically 400 mV, the error amplifier will ramp up its output voltage above the PWM Ramp Offset. At this instant, the top and bottom MOSFETs will begin switching. There is a small delay  $(t_{\rm dSS})$  from the moment EN pin transitioning high to the moment soft start voltage reaching 400 mV to initiate PWM switching.

Immediately after the start of PWM switching, the error amplifier will regulate the voltage at the FB pin to the soft start pin voltage minus approximately 400 mV. During the active portion of soft

start, the voltage at the SS pin will rise from 400 mV to 1.2 V (a difference of 800 mV), the voltage at the FB pin will rise from 0 V to 800 mV, and the regulator output voltage will rise from 0 V to the set voltage determined by the feedback resistor divider.

During startup, PWM switching frequency is reduced to 25% of  $f_{SW}$  while FB is below 200 mV. If FB voltage is above 200 mV but below 400 mV, the switching frequency is 50% of  $f_{SW}$ . At the same time, the transconductance of the error amplifier, gm, is reduced to half of nominal value when FB is below 400 mV. When FB is above 400 mV, the switching frequency will be  $f_{SW}$  and the error amplifier gain will be the nominal value. The reduced switching frequency and error amplifier gain are necessary to help improve output regulation and stability when  $V_{OUT}$  is very low. During low  $V_{OUT}$ , the PWM control loop requires ontime near the minimum controllable on-time and very low duty cycles that are not possible at the nominal switching frequency.

When the voltage at the soft start pin reaches approximately 1.2 V, the error amplifier will switch over and begin regulating the voltage at the FB pin to the fixed internal bandgap reference voltage of 800 mV. The voltage at the soft start pin will continue to rise to the internal LDO regulator output voltage. If the ARG81800 is disabled or a fault occurs, the internal fault latch is set and the capacitor at the SS pin is discharged to ground very quickly through a 2 k $\Omega$  pull-down resistor. The device will clear the internal fault latch when the voltage at the SS pin decays to approximately 200 mV. However, if the device enters hiccup mode, the capacitor at the SS pin is slowly discharged through a current sink,  $I_{\rm HIC}$ . Therefore, the soft start capacitor  $C_{\rm SS}$  not only controls the startup time but also the time between soft start attempts in hiccup mode.

#### Slope Compensation

The ARG81800 incorporates internal slope compensation that ensures stable operation at PWM duty cycles above 50% for a wide range of input/output voltages, switching frequencies, and inductor values. As shown in the functional block diagram, the slope compensation signal is added to the sum of the current sense and PWM Ramp Offset. The relationship between slope compensation and adjustable switching frequency is given by

Equation 1:

$$S_E = 12.84 / (37.037 / f_{SW} - 3)$$

where  $f_{SW}$  is switching frequency in MHz and  $S_E$  is slope compensation in A/ $\mu$ s. Internal slope compensation in ARG81800-1 is half of that (Equation 1) in ARG81800.

## 40 V, 500 mA / 1.0 A Synchronous Buck Regulators with Ultralow Quiescent Current, SYNC<sub>IN</sub>, CLK<sub>OUT</sub>, and PGOOD

#### **Pre-Biased Startup**

If the output of the buck regulator is pre-biased at a certain output voltage level, the ARG81800 will modify the normal startup routine to prevent discharging the output capacitors. As described in the Soft Start (Startup) and Inrush Current Control section, the error amplifier usually becomes active when the voltage at the soft start pin exceeds 400 mV. If the output is pre-biased, the voltage at the FB pin will be non-zero. The device will not start switching until the voltage at SS pin rises to approximately  $V_{FB} \pm 400$  mV. From then on, the error amplifier becomes active, the voltage at the COMP pin rises, PWM switching starts, and  $V_{OUT}$  will ramp upward from the pre-bias level.

#### **Dropout**

The ARG81800 is designed to operate at extremely wide duty cycles to minimize any reduction in output voltage during dropout conditions (difference between input and output voltage drops to a minimum value) such as cold crank. During dropout, if the minimum off-time (85 ns typical) is reached for more than 5 consecutive switching cycles, the programmed switching frequency  $f_{SW}$  is reduced by a factor of 4 and the off-time is extended to 115 ns (typical). While operating with reduced frequency, if the device further reaches minimum off-time (115 ns typical) for more than 35 consecutive switching cycles, it continues to operate with reduced frequency. Otherwise, the device toggles back to the programmed switching frequency  $f_{SW}$ . In addition, during dropout operation, the soft start capacitor  $C_{SS}$  will discharge so that if the input voltage increases, the output voltage recovers with a slew rate set by the soft start ramp.

#### **PGOOD Output**

The ARG81800 provides a Power Good (PGOOD) status signal to indicate if the output voltage is within the regulation limits. Since the PGOOD output is an open-drain output, an external pull-up resistor must be used as shown in the applications schematic. PGOOD transitions high when the output voltage, sensed at the FB pin, is within regulation.

During start-up, PGOOD signal exhibits an additional delay of  $t_{dPG(SU)}$  after FB pin voltage reaches the regulation voltage. This delay helps to filter out any glitches on the FB pin voltage.

The PGOOD output is pulled low if either an undervoltage or overvoltage condition occurs or the ARG81800 junction temperature exceeds thermal shutdown threshold ( $T_{SD}$ ). The PGOOD overvoltage and undervoltage comparators incorporate a small amount of hysteresis ( $V_{FB(OV,HYS)}$ ,  $V_{FB(UV,HYS)}$ ) to prevent chattering and deglitch filtering ( $t_{dPG(UV)}$ ,  $t_{dPG(OV)}$ ) to eliminate false triggering. For other faults, PGOOD depends on the output voltage.

It is important that the correct status of PGOOD is reported during either the input supply ramp up or ramp down. During a supply ramp up, the PGOOD is designed to operate in the correct state from a very low input voltage. Also, during supply ramp down, the PGOOD is designed to operate in the correct state down to a very low input voltage.

#### **Current Sense Amplifier**

The ARG81800 incorporates a high-bandwidth current sense amplifier to monitor the current through the top MOSFET. This current signal is used to regulate the peak current when the top MOSFET is turned on. The current signal is also used by the protection circuitry for the cycle-by-cycle current limit and hiccup mode short circuit protection

#### **Pulse-Width Modulation (PWM)**

The ARG81800 employs fixed-frequency, peak current mode control to provide excellent load and line regulation, fast transient response, and simple compensation. A high-speed comparator and control logic is included in the ARG81800. The inverting input of the PWM comparator is connected to the output of the error amplifier. The non-inverting input is connected to the sum of the current sense signal, the slope compensation signal, and a DC PWM Ramp offset voltage (Ramp Offset).

At the beginning of each PWM cycle, the CLK signal sets the PWM flip flop, the bottom MOSFET is turned off, the top MOSFET is turned on, and the inductor current increases. When the voltage at the non-inverting of PWM comparator rises above the error amplifier output COMP, the PWM flip flop is reset, the top MOSFET is turned off, the bottom MOSFET is turned on, and the inductor current decreases. Since the PWM flip flop is reset, the dominant error amplifier may override the CLK signal in certain situations.

# 40 V, 500 mA / 1.0 A Synchronous Buck Regulators with Ultralow Quiescent Current, SYNC $_{\rm IN},$ CLK $_{\rm OUT},$ and PGOOD

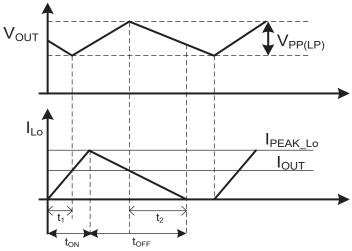

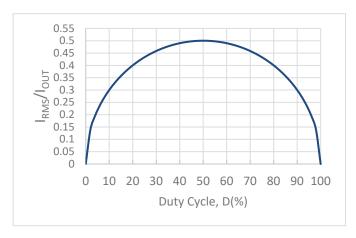

#### Low-Power (LP) Mode