Click here to ask about the production status of specific part numbers.

#### MAX98396

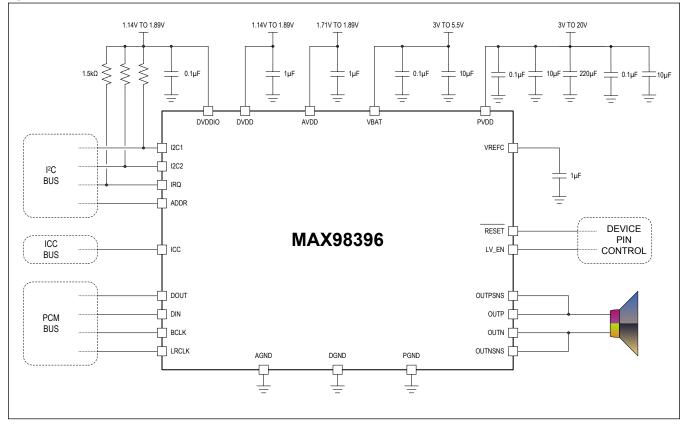

## 20V Digital Input Class-DG Amplifier with I/V Sense and Brownout Prevention

#### **General Description**

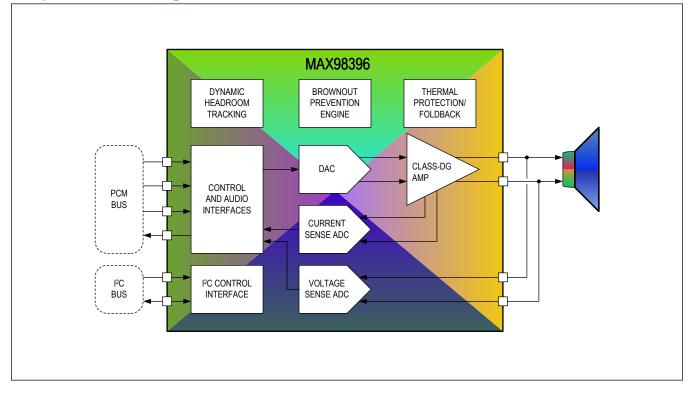

The MAX98396 is a high-efficiency, mono Class-DG speaker amplifier with industry-leading quiescent power featuring I/V sense, brownout-prevention engine (BPE), and dynamic-headroom tracking (DHT). The IC enables ultrasound applications by providing support for sample rates up to 192kHz, a higher passband (for  $f_s > 50$ kHz), and a bypass path for the ultrasound signals through the amplifier so it is not attenuated by the audio processing. Precision output current and voltage monitoring (I/V sense) enables the host device to run speaker protection algorithms. Spread-spectrum modulation (SSM) and edge rate control minimize EMI and eliminate the need for the output filtering found in traditional Class-D devices.

To achieve industry-leading quiescent power, the Class-DG amplifier employs two supply rails VBAT (3V to 5.5V) and PVDD (3V to 20V) to supply the speaker amplifier. The Class-DG amplifier switches between the two supply rails depending on the input signal level and/or the supply headroom. The brownout-prevention engine in the device allows it to reduce its contribution to the overall system power consumption by either attenuating or limiting the amplifier output when the device supply drops below a set of programmable thresholds. Additionally, as the power supply voltage varies due to sudden transients and declining battery life, DHT automatically optimizes the headroom available to the Class-DG amplifier to maintain consistent distortion and listening levels.

The device provides a PCM interface for audio data and a standard I<sup>2</sup>C interface for control data communication. The PCM interface supports audio playback using I<sup>2</sup>S, left-justified, and TDM audio data formats. A unique clocking structure eliminates the need for an external master clock for PCM communication, which reduces pin count and simplifies board layout. Enabling thermal foldback automatically reduces the output power when the temperature exceeds a user specified threshold. This allows for uninterrupted music playback even at high ambient temperatures. Traditional thermal protection is also available in addition to robust overcurrent protection.

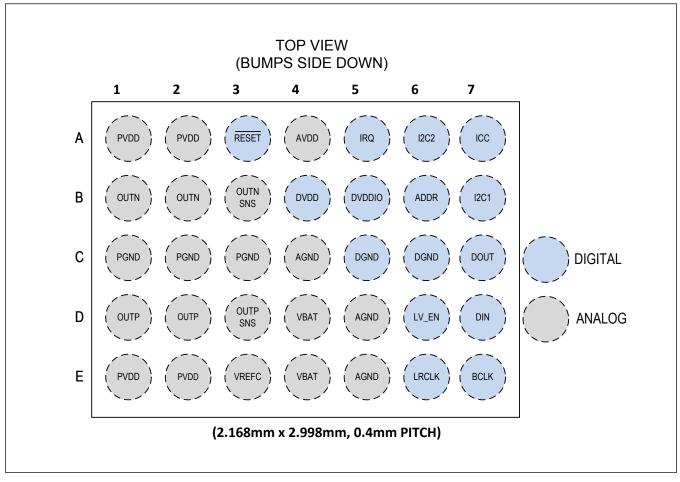

The device is available in a 0.4mm pitch, 35-bump waferlevel package (WLP). The device operates over the extended  $-40^{\circ}$ C to  $+85^{\circ}$ C temperature range.

#### **Applications**

- Mobile Speakers Smart Speakers Smart IoT Tablets

- Notebook Computers

Soundbars

SMBus is a trademark of Intel Corp.

#### **Benefits and Features**

- Wide Input Supply Range (3.0V to 20V)

- Class-DG Operation Enables Industry-Leading Quiescent Power

- + 12.7mW at  $V_{PVDD}$  = 12V ,  $V_{VBAT}$  = 3.8V

- 18mW at  $V_{PVDD}$  = 19V,  $V_{VBAT}$  = 5.0V

- Ultra-Low Noise Floor

- 15.5µV<sub>RMS</sub> Output Noise

- 118dB Dynamic Range

- Low Distortion

- -82dB THD+N at 1W into 8Ω, f = 1kHz

- -76dB THD+N at 1W into 8Ω, f = 6kHz

- Output Power at 1% THD+N:

- 20W into 8Ω, V<sub>PVDD</sub> = 19V

- 19W into 4Ω, V<sub>PVDD</sub> = 14V

- 60W Peak Output Power into 4Ω, V<sub>PVDD</sub> = 19V

- Speaker Amplifier Efficiency:

- 87% at 1W into  $8\Omega$ , V<sub>PVDD</sub> = 12V, V<sub>VBAT</sub> = 3.8V

- 83% at 1W into 4Ω, V<sub>PVDD</sub> = 12V, V<sub>VBAT</sub> = 3.8V

- 83% at 1W into 8 $\Omega$ , V<sub>PVDD</sub> = 19V, V<sub>VBAT</sub> = 5.0V

- 91% at 20W into 8Ω, V<sub>PVDD</sub> = 19V, V<sub>VBAT</sub> = 5.0V

- Class-D EMI Reduction Enables Filterless Operation

- Spread-Spectrum Modulation

- Switching-Edge Rate Control

- Integrated Speaker Current and Voltage Sense do not Require External Components

- Flexible Brownout-Prevention Engine

- I<sup>2</sup>S/16-Channel TDM and I<sup>2</sup>C Digital Interfaces

- Playback Support for 16-, 24-, and 32-Bit Data Words

- Playback and I/V Sense Support Sample Rates up to 192kHz

- Audio Processing Bypass Path

- Dynamic-Headroom Tracking Maintains a Consistent Listening Experience

- Extensive Click-and-Pop Suppression

- 35-Bump, WLP (0.4mm Pitch)

#### Ordering Information appears at end of data sheet.

## 20V Digital Input Class-DG Amplifier with I/V Sense and Brownout Prevention

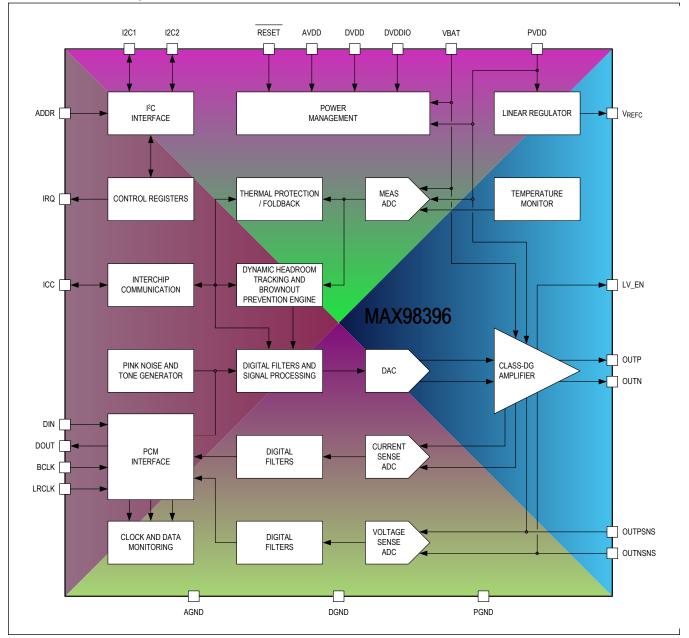

### Simplified Block Diagram

# 20V Digital Input Class-DG Amplifier with I/V Sense and Brownout Prevention

## TABLE OF CONTENTS

| General Description                            | 1  |

|------------------------------------------------|----|

| Applications                                   | 1  |

| Benefits and Features                          | 1  |

| Simplified Block Diagram                       | 2  |

| Absolute Maximum Ratings                       | 10 |

| Package Information                            | 10 |

| 35 WLP                                         | 10 |

| Electrical Characteristics                     | 11 |

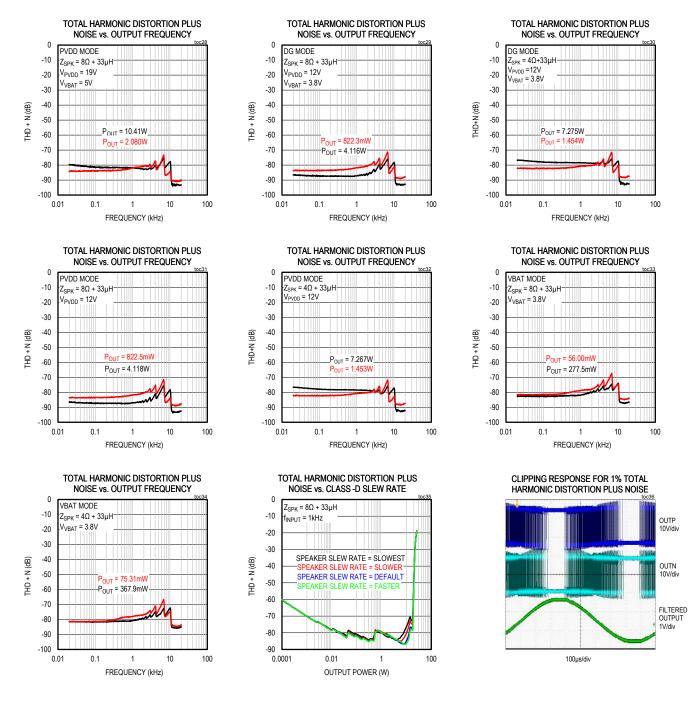

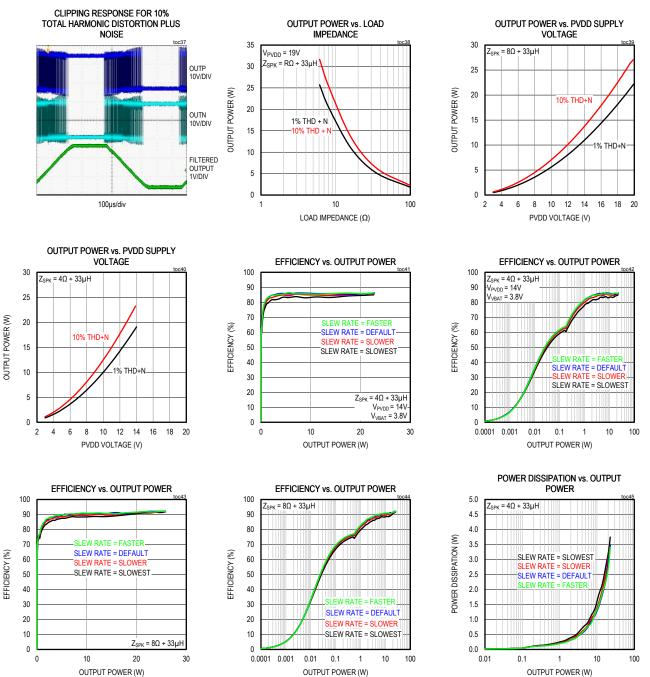

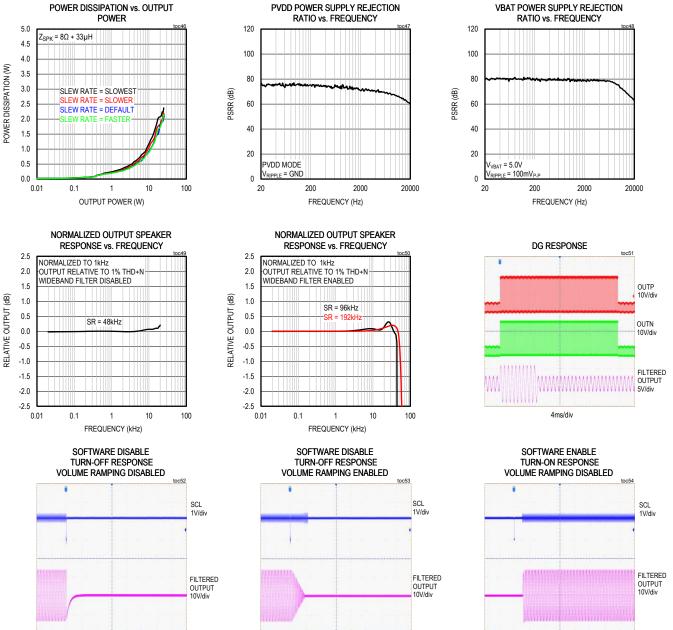

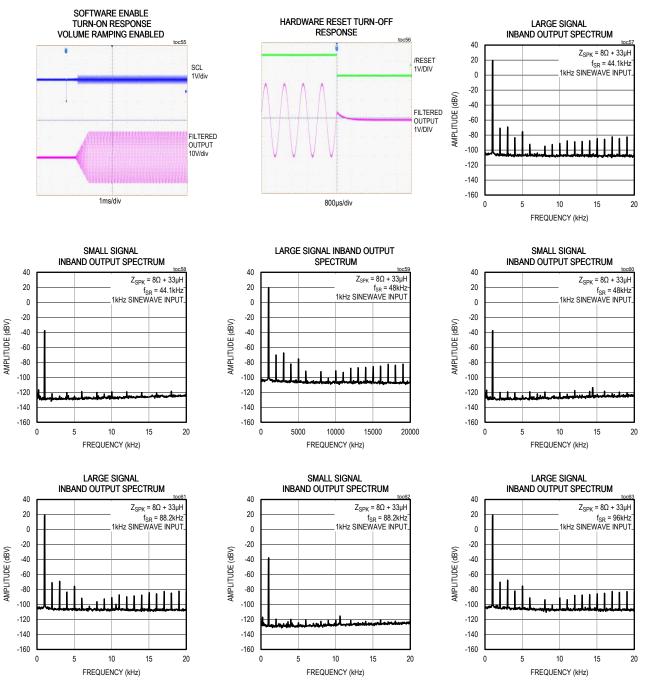

| Typical Operating Characteristics              | 26 |

| Pin Configuration                              | 36 |

| 35 WLP                                         | 36 |

| Pin Description                                | 36 |

| Functional Diagrams                            | 38 |

| Detailed Block Diagram                         | 38 |

| Detailed Description                           | 39 |

| Device State Control                           | 39 |

| Hardware Shutdown State                        | 39 |

| Software Shutdown State                        | 39 |

| Active State                                   | 40 |

| Device Sequencing                              | 40 |

| PCM Interface                                  | 41 |

| PCM Clock Configuration                        | 41 |

| PCM Data Format Configuration                  | 41 |

| I <sup>2</sup> S/Left-Justified Mode           | 41 |

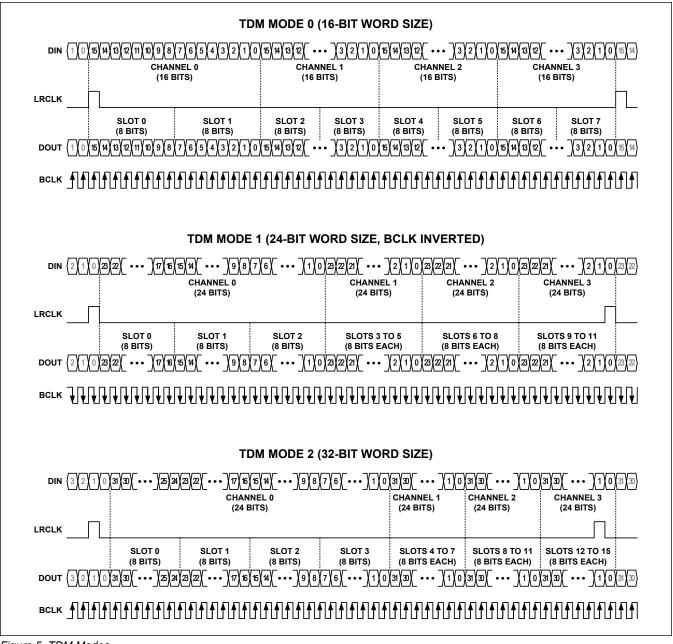

| TDM Modes                                      | 43 |

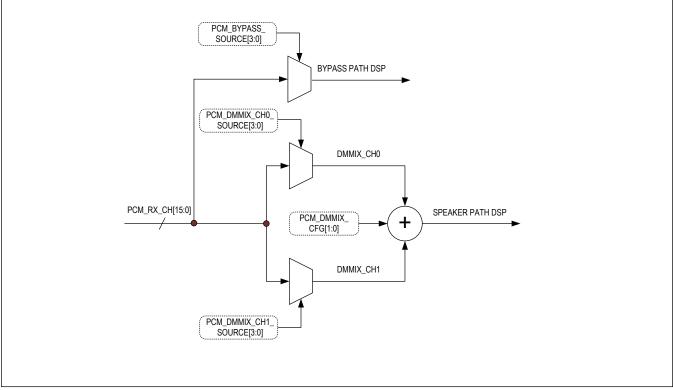

| PCM Data Path Configuration                    | 45 |

| PCM Data Input                                 | 46 |

| PCM Data Output                                | 46 |

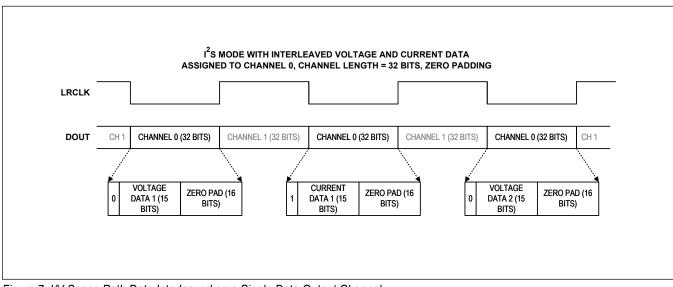

| Data Output Channel-Interleaved I/V Sense Data | 47 |

| Data Output Status Bits                        | 48 |

| PCM Interface Timing                           | 49 |

| Interrupts                                     | 49 |

| Interrupt Bit Field Composition                | 49 |

| Interrupt Output Configuration                 | 50 |

| Interrupt Sources                              | 50 |

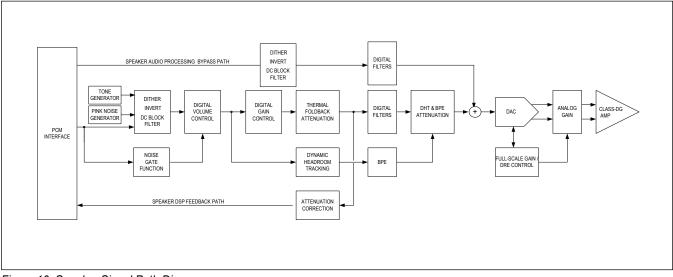

| Speaker Path                                   | 52 |

| Speaker Path Block Diagram                     | 52 |

| Speaker Playback Path                          | 52 |

# 20V Digital Input Class-DG Amplifier with I/V Sense and Brownout Prevention

# TABLE OF CONTENTS (CONTINUED)

| Speaker Path Noise Gate.                                       | . 52 |

|----------------------------------------------------------------|------|

| Speaker Path Dither                                            | . 53 |

| Speaker Path Data Inversion                                    | . 53 |

| Speaker Path DC Blocking Filter                                | . 53 |

| Speaker Path Digital Volume Control                            | . 53 |

| Speaker Path Digital Gain Control                              | . 53 |

| Speaker Path DSP Data Feedback Path                            | . 53 |

| Speaker Safe Mode                                              | . 53 |

| Speaker Audio Processing Bypass Path                           | . 53 |

| Bypass Path Data Inversion                                     | . 54 |

| Bypass Path Dither.                                            | . 54 |

| Bypass Path DC Blocking Filter                                 | . 54 |

| Speaker Maximum Peak Output Voltage Scaling                    | . 54 |

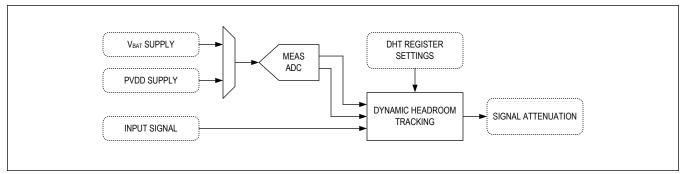

| Dynamic-Headroom Tracking (DHT)                                | . 54 |

| DHT Supply Tracking and Headroom                               | . 55 |

| DHT Mode 1 – Signal Distortion Limiter                         | . 56 |

| DHT Mode 2 – Signal Level Limiter.                             | . 60 |

| DHT Mode 3: Dynamic Range Compressor                           | . 62 |

| DHT Mode 4: Dynamic Range Compressor with Signal Level Limiter | . 64 |

| DHT Attenuation                                                | . 66 |

| DHT Attenuation Reporting                                      | . 68 |

| DHT Ballistics                                                 | . 68 |

| Speaker Amplifier                                              | . 69 |

| Speaker Amplifier Operating Modes                              | . 69 |

| Class-DG Mode Enabled                                          | . 69 |

| Delay for DG Mode                                              | . 69 |

| Class-DG Mode Disabled                                         | . 70 |

| NOVBAT Mode                                                    | . 70 |

| IDLE Mode                                                      | . 70 |

| Speaker Amplifier Ultra-Low EMI Filterless Operation           | . 70 |

| Speaker Amplifier Overcurrent Protection                       | . 71 |

| Speaker Current and Voltage Sense ADC Path                     | . 71 |

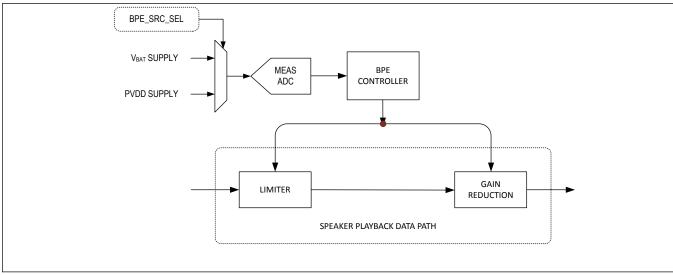

| Brownout-Prevention Engine                                     | . 71 |

| BPE State Controller and Level Thresholds                      |      |

| BPE Level Configuration Options                                | . 73 |

| BPE Gain Attenuation Function                                  | . 73 |

| BPE Limiter Function                                           | . 73 |

| Brownout Interrupts                                            | . 73 |

# 20V Digital Input Class-DG Amplifier with I/V Sense and Brownout Prevention

# TABLE OF CONTENTS (CONTINUED)

| Measurement ADC                                              | '4             |

|--------------------------------------------------------------|----------------|

| Measurement ADC Thermal Channel                              | '4             |

| Measurement ADC PVDD Channel 7                               | '4             |

| Measurement ADC VBAT Channel                                 | '4             |

| Clock and Data Monitors                                      | '5             |

| Input Data Monitor                                           | '5             |

| Clock Monitor                                                | '6             |

| Clock Activity and Frequency Detection7                      | '6             |

| Clock Frame Error Detection                                  | 7              |

| Speaker Monitor                                              | 7              |

| Thermal Protection                                           | '8             |

| Thermal Warning and Thermal Shutdown Configuration         7 | '8             |

| Thermal Shutdown Recovery Configuration                      | '8             |

| Thermal Foldback                                             | '8             |

| Tone Generator                                               | '9             |

| Pink Noise Generator                                         | '9             |

| Interchip Communication                                      | '9             |

| ICC Operation and Data Format                                | '9             |

| Multiamplifier Grouping                                      | 30             |

| I <sup>2</sup> C Serial Interface                            | 31             |

| Slave Address                                                | 31             |

| Bit Transfer                                                 | 32             |

| START and STOP Conditions                                    | 32             |

| Early STOP Conditions                                        | 33             |

| Acknowledge                                                  | 33             |

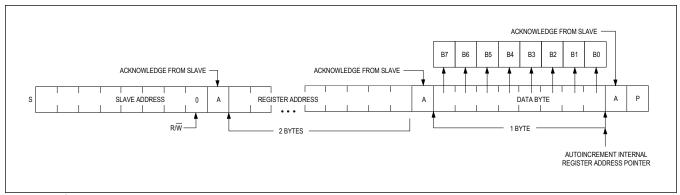

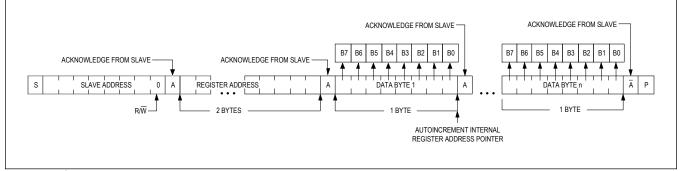

| Write Data Format                                            | 33             |

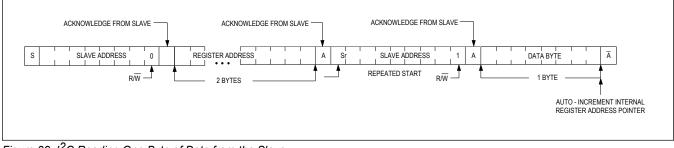

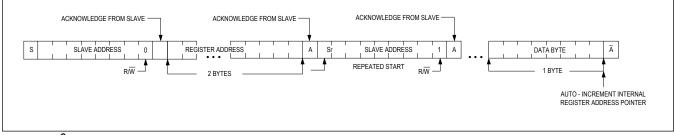

| Read Data Format                                             | 34             |

| I <sup>2</sup> C Register Map                                | 35             |

| Control Bit Field Types and Write Access Restrictions        | 35             |

| Register Map                                                 | 37             |

| Register Map                                                 | 37             |

| Register Details                                             | <del>)</del> 5 |

| Applications Information                                     | '0             |

| Layout and Grounding                                         | '0             |

| Recommended External Components                              | '0             |

| Typical Application Circuits                                 | '1             |

| Typical Application Circuit                                  | '1             |

| Ordering Information                                         | '1             |

# 20V Digital Input Class-DG Amplifier with I/V Sense and Brownout Prevention

# TABLE OF CONTENTS (CONTINUED)

| Revision History |  | 172 |

|------------------|--|-----|

|------------------|--|-----|

# 20V Digital Input Class-DG Amplifier with I/V Sense and Brownout Prevention

## LIST OF FIGURES

| Figure 1. Standard I <sup>2</sup> S Mode                                                                             | 42   |

|----------------------------------------------------------------------------------------------------------------------|------|

| Figure 2. Left-Justified Mode                                                                                        | 42   |

| Figure 3. Left-Justified Mode (LRCLK Inverted)                                                                       | 43   |

| Figure 4. Left-Justified Mode (BCLK Inverted)                                                                        | 43   |

| Figure 5. TDM Modes                                                                                                  | 45   |

| Figure 6. PCM Data Input                                                                                             | 46   |

| Figure 7. I/V Sense Path Data Interleaved on a Single Data Output Channel                                            | 48   |

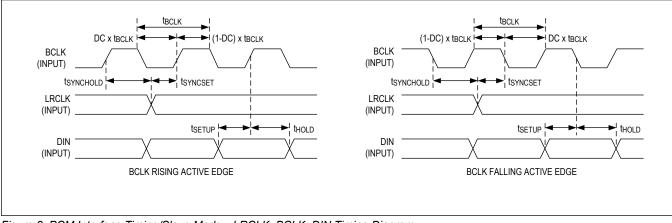

| Figure 8. PCM Interface Timing/Slave Mode—LRCLK, BCLK, DIN Timing Diagram                                            | 49   |

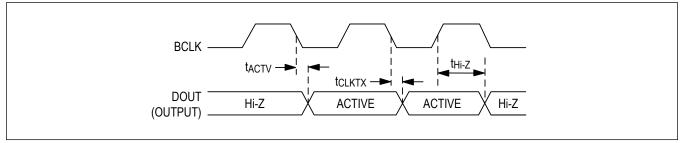

| Figure 9. PCM Interface Timing/DOUT Timing Diagram                                                                   | 49   |

| Figure 10. Speaker Signal Path Diagram                                                                               | 52   |

| Figure 11. Simplified Dynamic-Headroom Tracking System Block Diagram                                                 | 54   |

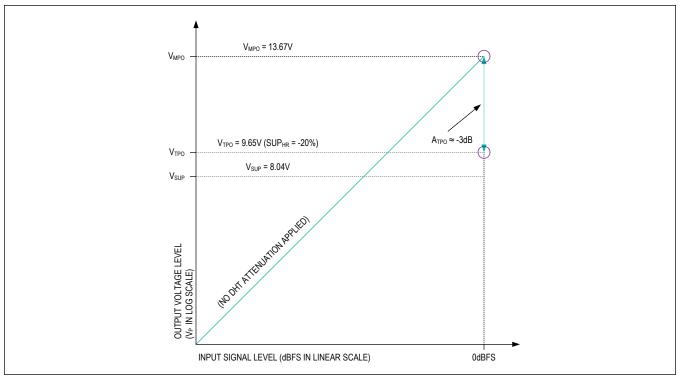

| Figure 12. V <sub>TPO</sub> and A <sub>TPO</sub> Calculation Example                                                 | 56   |

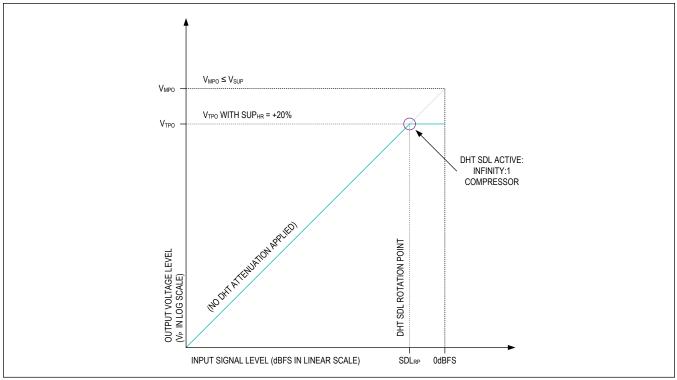

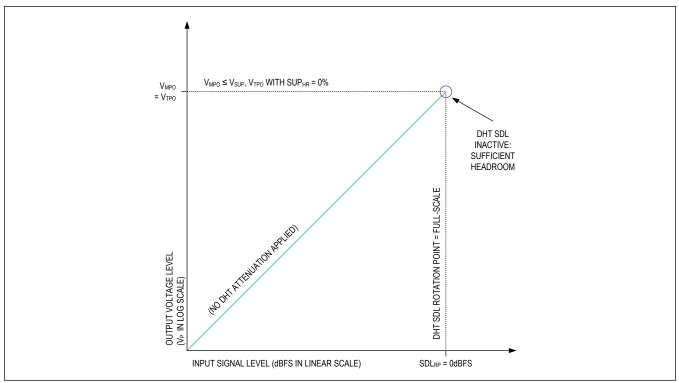

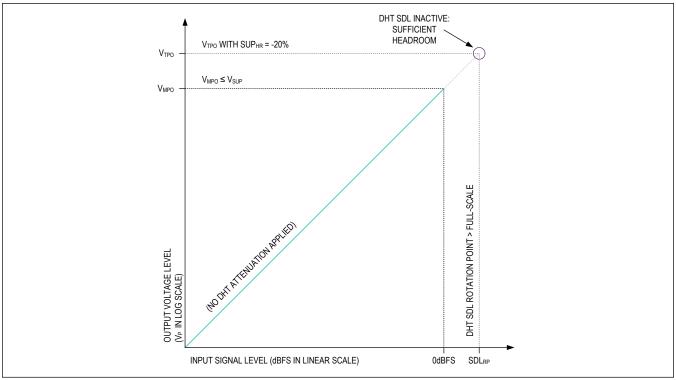

| Figure 13. Signal Distortion Limiter with $V_{MPO} \le V_{SUP}$ and +20% Headroom (SUP <sub>HR</sub> )               | 57   |

| Figure 14. Signal Distortion Limiter with $V_{MPO} \le V_{SUP}$ and 0% Headroom (SUP <sub>HR</sub> )                 | 57   |

| Figure 15. Signal Distortion Limiter with $V_{MPO} \le V_{SUP}$ and -20% Headroom (SUP <sub>HR</sub> )               | 58   |

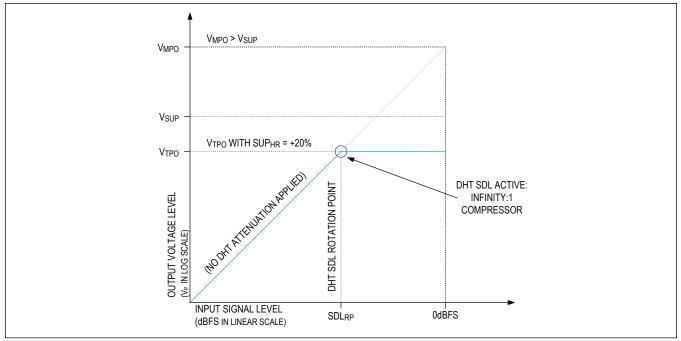

| Figure 16. Signal Distortion Limiter with V <sub>MPO</sub> > V <sub>SUP</sub> and +20% Headroom (SUP <sub>HR</sub> ) | 59   |

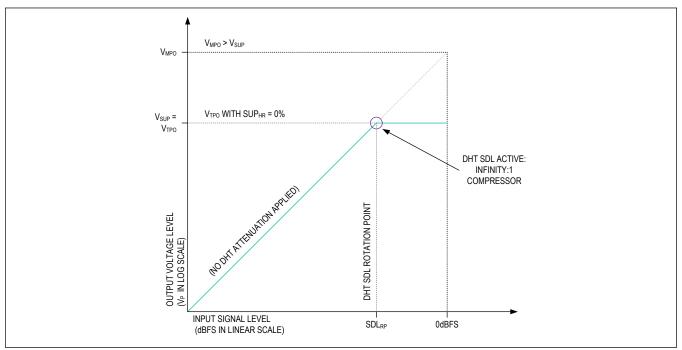

| Figure 17. Signal Distortion Limiter with V <sub>MPO</sub> > V <sub>SUP</sub> and 0% Headroom (SUP <sub>HR</sub> )   | 59   |

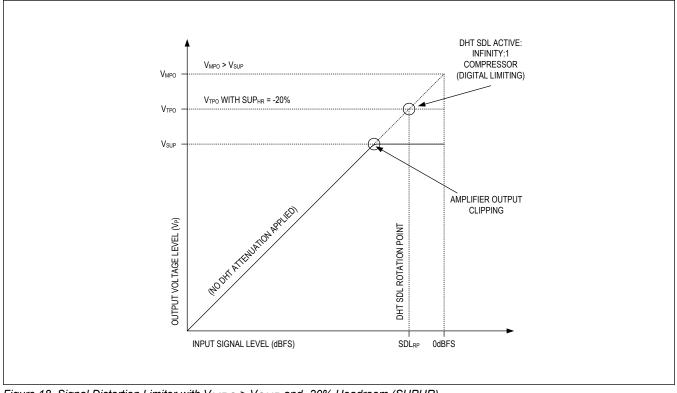

| Figure 18. Signal Distortion Limiter with V <sub>MPO</sub> > V <sub>SUP</sub> and -20% Headroom (SUPHR)              | 60   |

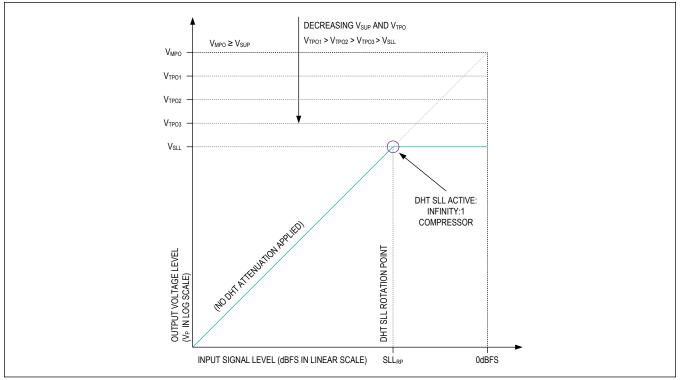

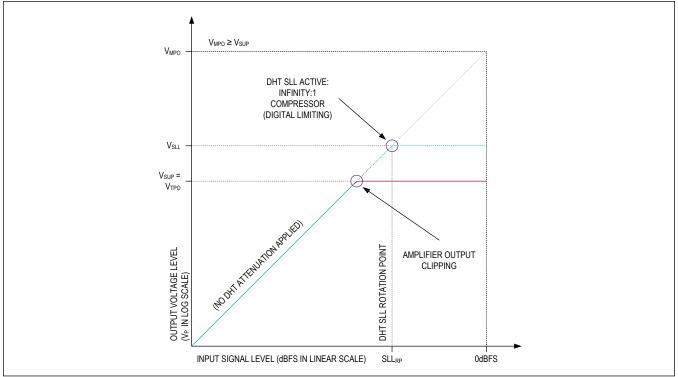

| Figure 19. Signal Level Limiter with V <sub>TPO</sub> > V <sub>SLL</sub> as V <sub>SUP</sub> Decreases               | 61   |

| Figure 20. Signal Level Limiter with V <sub>TPO</sub> < V <sub>SLL</sub> Showing Amplifier Output Clipping           | 62   |

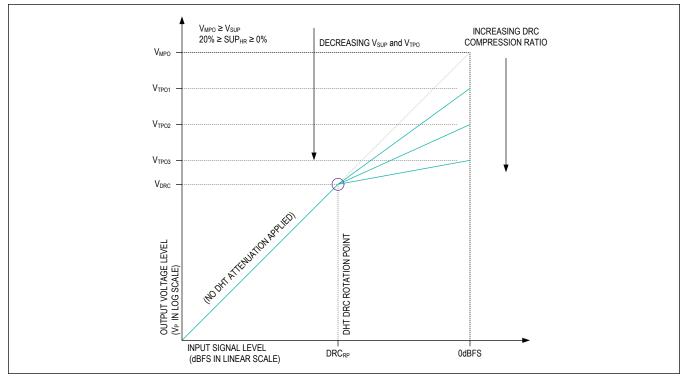

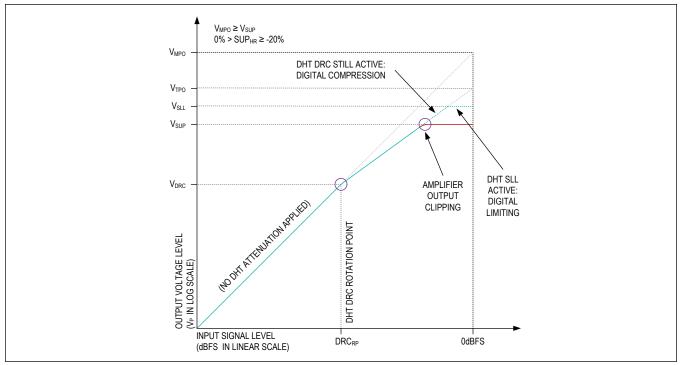

| Figure 21. Dynamic Range Compression with Decreasing $V_{SUP}$ and $SUP_{HR} \ge 0\%$                                | 63   |

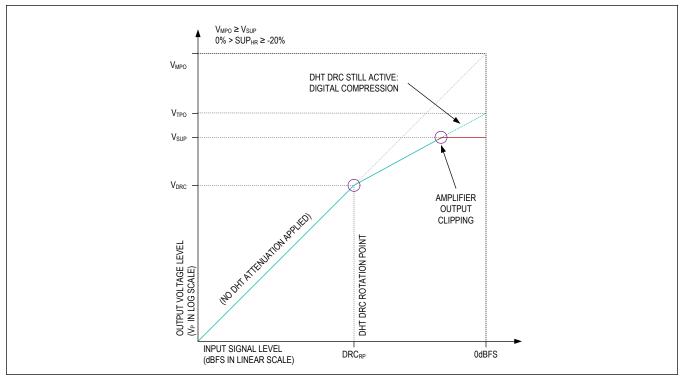

| Figure 22. Dynamic Range Compressor with SUP <sub>HR</sub> < 0% and Output Clipping                                  | 64   |

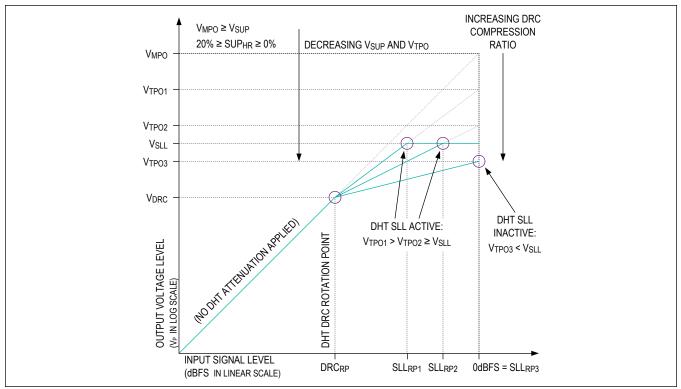

| Figure 23. DHT DRC and SLL with Decreasing V <sub>SUP</sub> (V <sub>TPO</sub> ), and SUP <sub>HR</sub> ≥ 0%          | 65   |

| Figure 24. DHT DRC and SLL with Decreasing V <sub>SUP</sub> (V <sub>TPO</sub> ), and SUP <sub>HR</sub> < 0%          | 66   |

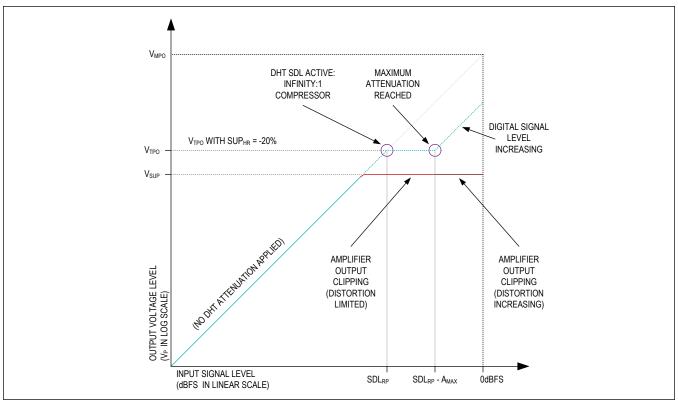

| Figure 25. Distortion Limiter Case with -20% Headroom and A <sub>MAX</sub> Exceeded                                  | 67   |

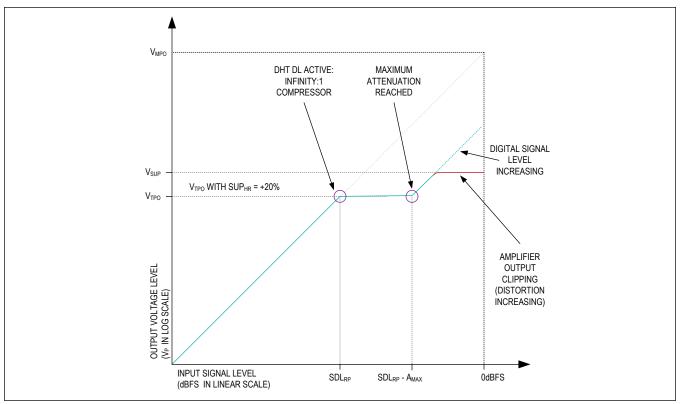

| Figure 26. Distortion Limiter Case with +20% Headroom and A <sub>MAX</sub> Exceeded                                  | 68   |

| Figure 27. BPE Block Diagram                                                                                         | 72   |

| Figure 28. Data Monitor Error Generation due to Input Data Stuck Error Detection                                     | 75   |

| Figure 29. Monitor Error Generation due to Input Data Magnitude Error Detection                                      | 76   |

| Figure 30. Clock Monitor LRCLK Rate Error Example With CMON_ERRTOL = 0x1                                             | 77   |

| Figure 31. Clock Monitor Framing Error Example In TDM Mode With PCM_BSEL = 0x6 and CMON_BSELTOL = 0x0                | ) 77 |

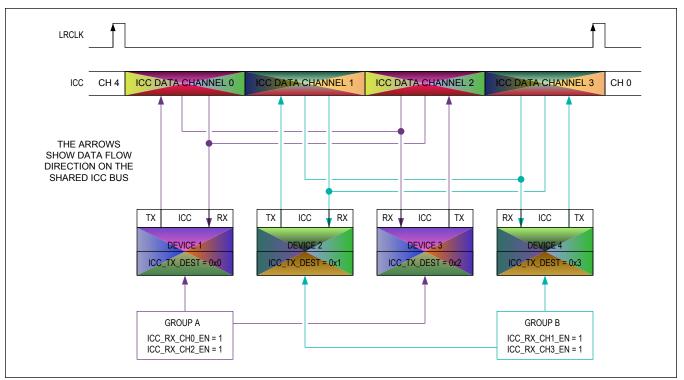

| Figure 32. ICC Multi-Group Example with 2 Groups and 4 Total Devices                                                 | 81   |

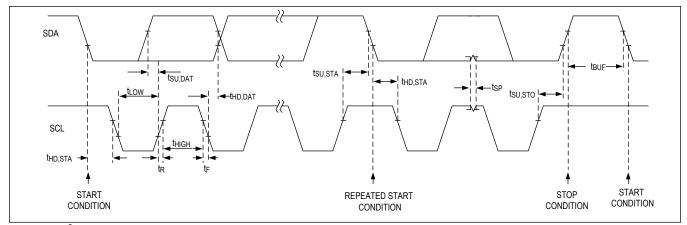

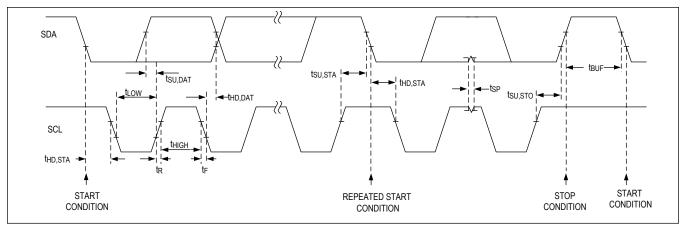

| Figure 33. I <sup>2</sup> C Interface Timing Diagram                                                                 | 82   |

| Figure 34. I <sup>2</sup> C START, STOP, and REPEATED START Conditions                                               | 83   |

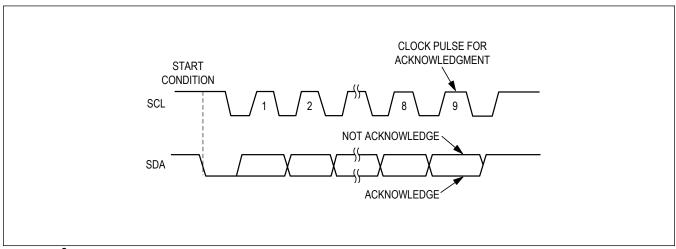

| Figure 35. I <sup>2</sup> C Acknowledge                                                                              | 83   |

| Figure 36. I <sup>2</sup> C Writing One Byte of Data to the Slave                                                    | 84   |

| Figure 37. I <sup>2</sup> C Writing n-Bytes of Data to the Slave                                                     | 84   |

| Figure 38. I <sup>2</sup> C Reading One Byte of Data from the Slave                                                  | 85   |

# 20V Digital Input Class-DG Amplifier with I/V Sense and Brownout Prevention

# LIST OF FIGURES (CONTINUED)

| Figure 39. I <sup>2</sup> C Reading n-Bytes of Data from the Slave |  |

|--------------------------------------------------------------------|--|

|--------------------------------------------------------------------|--|

# 20V Digital Input Class-DG Amplifier with I/V Sense and Brownout Prevention

## LIST OF TABLES

| Table 1. Typical Power-Up Sequence                                               | 40 |

|----------------------------------------------------------------------------------|----|

| Table 2. Typical Power-Down Sequence                                             | 40 |

| Table 3. Sample Rate Selection for I/V Sense                                     | 41 |

| Table 4. Supported I <sup>2</sup> S/Left-Justified Mode Configurations           | 42 |

| Table 5. Supported TDM Mode Configurations                                       | 43 |

| Table 6. Supported PCM Data Output Types                                         | 47 |

| Table 7. Interrupt Sources.                                                      | 50 |

| Table 8. Noise Gate/Idle Mode Threshold LSB Location by Input Data Configuration | 53 |

| Table 9. Brownout-Prevention Engine Levels                                       | 72 |

| Table 10. I <sup>2</sup> C Slave Address                                         | 81 |

| Table 11. Control Bit Types and Write Access Restrictions                        | 85 |

| Table 12. Component List    1                                                    | 70 |

## 20V Digital Input Class-DG Amplifier with I/V Sense and Brownout Prevention

#### **Absolute Maximum Ratings**

| VBAT to PGND                | 0.3V to +6.0V                    |

|-----------------------------|----------------------------------|

| PVDD to PGND                | 0.3V to +22V                     |

| PVDD to VBAT                | 0.3V to 22 - V <sub>VBAT</sub> V |

| AGND, DGND to PGND          |                                  |

| AVDD to AGND                | 0.3V to +2.2V                    |

| DVDD, DVDDIO to DGND        | 0.3V to +2.2V                    |

| OUTP, OUTN to PGND          | 0.3V to V <sub>PVDD</sub> + 0.3V |

| OUTPSNS or OUTNSNS to PGND  | 0.3V to +22 V                    |

| OUTPSNS and OUTNSNS to PGND | 0.3V to +13 V                    |

| VREFC to GND                |                                  |

| I2C1, I2C2, ADDR to GND     | 0.3V to +4.0V                    |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### **35 WLP**

| Package Code                                          | W352F3Z+1                      |  |  |  |

|-------------------------------------------------------|--------------------------------|--|--|--|

| Outline Number                                        | <u>21-100489</u>               |  |  |  |

| Land Pattern Number                                   | Refer to Application Note 1891 |  |  |  |

| Thermal Resistance, Single Layer Board:               |                                |  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                | 46.33                          |  |  |  |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) | N/A                            |  |  |  |

| Thermal Resistance, Four Layer Board:                 |                                |  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                |                                |  |  |  |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) | N/A                            |  |  |  |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/</u> <u>thermal-tutorial</u>.

## 20V Digital Input Class-DG Amplifier with I/V Sense and Brownout Prevention

#### **Electrical Characteristics**

| PARAMETER                                       | SYMBOL                  | CONDITIONS                                                           | MIN  | TYP        | MAX          | UNITS |

|-------------------------------------------------|-------------------------|----------------------------------------------------------------------|------|------------|--------------|-------|

| POWER SUPPLIES                                  |                         |                                                                      |      |            |              |       |

| VBAT Power Supply<br>Operating Voltage<br>Range | V <sub>VBAT</sub>       |                                                                      | 3.0  |            | 5.5          | v     |

| VBAT Voltage                                    | V <sub>VBAT</sub>       | Device is functional but parametric<br>performance is not guaranteed | 2.3  |            |              | V     |

| PVDD Power Supply<br>Operating Voltage<br>Range | V <sub>PVDD</sub>       |                                                                      | 3.0  |            | 20           | V     |

| PVDD Voltage                                    | V <sub>PVDD</sub>       | Device is functional but parametric<br>performance is not guaranteed | 2.3  |            |              | V     |

| AVDD Power Supply<br>Voltage Range              | V <sub>AVDD</sub>       |                                                                      | 1.71 | 1.8        | 1.89         | V     |

| DVDD Power Supply<br>Voltage Range              | V <sub>DVDD</sub>       |                                                                      | 1.14 | 1.2        | 1.89         | V     |

| DVDDIO Power Supply Voltage Range               | V <sub>DVDDIO</sub>     |                                                                      | 1.14 | 1.2<br>1.8 | 1.26<br>1.89 | - V   |

| VBAT Undervoltage<br>Lockout                    | V <sub>VBAT_</sub> UVLO | V <sub>VBAT</sub> falling                                            | 1.8  |            | 2.2          | V     |

| PVDD Undervoltage<br>Lockout                    | V <sub>PVDD_UVLO</sub>  | V <sub>PVDD</sub> falling                                            | 1.93 |            | 2.26         | V     |

| AVDD Undervoltage<br>Lockout                    | VAVDD_UVLO              | V <sub>AVDD</sub> falling                                            | 1.24 |            | 1.46         | V     |

| DVDD Undervoltage<br>Lockout                    | V <sub>DVDD_UVLO</sub>  | V <sub>DVDD</sub> falling                                            | 0.85 |            | 1.01         | V     |

| VBAT UVLO Hysteresis                            |                         | T <sub>A</sub> = +25°C                                               | 35   |            |              | mV    |

| PVDD UVLO Hysteresis                            |                         | T <sub>A</sub> = +25°C                                               | 30   |            |              | mV    |

| Supply Ramp Rate<br>VBAT                        |                         |                                                                      | 0.1  |            | 100          | V/ms  |

| Supply Ramp Rate<br>PVDD                        |                         |                                                                      | 0.1  |            | 100          | V/ms  |

## 20V Digital Input Class-DG Amplifier with I/V Sense and Brownout Prevention

#### **Electrical Characteristics (continued)**

| PARAMETER                                   | SYMBOL                                                                  | CONE                                                                   | ITIONS                                                                                  | MIN | TYP  | MAX | UNITS |

|---------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----|------|-----|-------|

| POWER CONSUMPTIO                            | N / QUIESCENT F                                                         | OWER CONSUMPT                                                          | ON                                                                                      |     |      |     |       |

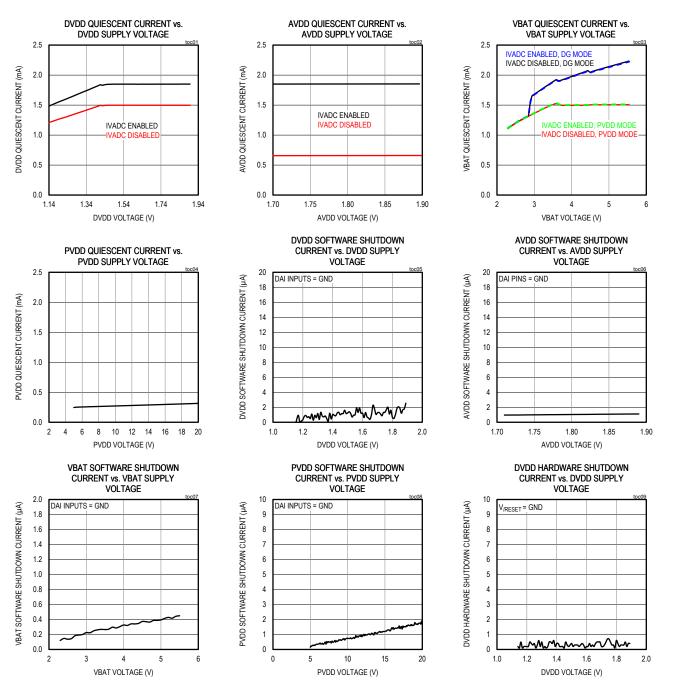

|                                             |                                                                         | All supplies, IV                                                       | V <sub>PVDD</sub> = 12V,<br>V <sub>VBAT</sub> = 3.8V, DG<br>mode                        |     | 16.5 | 25  | - mW  |

| Total Power                                 | Pa                                                                      | sense enabled                                                          | V <sub>PVDD</sub> = 19V,<br>V <sub>VBAT</sub> = 5.0V, DG<br>mode (Note 3)               |     | 22.3 | 30  |       |

| Consumption                                 | PQ                                                                      | All supplies, IV                                                       | V <sub>PVDD</sub> = 12V,<br>V <sub>VBAT</sub> = 3.8V, DG<br>mode                        |     | 12.7 |     |       |

|                                             |                                                                         | sense disabled                                                         | V <sub>PVDD</sub> = 19V,<br>V <sub>VBAT</sub> = 5.0V, DG<br>mode                        |     | 18   |     |       |

| Total Power                                 | D                                                                       | All supplies, IV                                                       | V <sub>PVDD</sub> = 12V,<br>V <sub>VBAT</sub> = 3.8V, DG<br>mode, noise gate<br>enabled |     | 1.7  |     | - mW  |

| Consumption                                 | PQ                                                                      | sense disabled                                                         | V <sub>PVDD</sub> = 19V,<br>V <sub>VBAT</sub> = 5.0V, DG<br>mode, noise gate<br>enabled |     | 1.9  |     |       |

| POWER CONSUMPTIO                            | N / SOFTWARE S                                                          | HUTDOWN                                                                |                                                                                         |     |      |     |       |

|                                             |                                                                         | VBAT = $3.8V$ , No B(<br>transactions, T <sub>A</sub> = +              |                                                                                         |     | 0.3  | 5   |       |

| VBAT Software                               | ISHDN_SW_VB                                                             | VBAT = $3.8V$ , No B(<br>transactions, T <sub>A</sub> = +              |                                                                                         |     |      | 15  |       |

| Shutdown Supply<br>Current                  | AT                                                                      | VBAT = 5.0V, No BCLK/LRCLK/DIN transactions, $T_A = +25^{\circ}C$      |                                                                                         |     | 0.4  | 5   | - μΑ  |

|                                             |                                                                         | VBAT = 5.0V, No B(<br>transactions, $T_A$ = +                          |                                                                                         |     | 15   |     |       |

|                                             | ISHON SW DV                                                             |                                                                        | PVDD = 5.0V, No BCLK/LRCLK/DIN<br>transactions, T <sub>A</sub> = +25°C                  |     |      | 5   |       |

| PVDD Software<br>Shutdown Supply<br>Current |                                                                         | PVDD = 5.0V, No BCLK/LRCLK/DIN<br>transactions, $T_A$ = +85°C (Note 3) |                                                                                         |     | 15   |     |       |

|                                             |                                                                         | PVDD = 12V, No BC transactions, $T_A$ = +                              |                                                                                         |     | 1    | 5   |       |

|                                             | PVDD = 12V, No BCLK/LRCLK/DIN<br>transactions, $T_A$ = +85°C (Note 3)   |                                                                        |                                                                                         |     | 15   | μA  |       |

|                                             | PVDD = 19V, No BCLK/LRCLK/DIN<br>transactions, $T_A = +25^{\circ}C$ 1.7 |                                                                        | 1.7                                                                                     | 5   |      |     |       |

|                                             |                                                                         | PVDD = 19V, No BC<br>transactions, T <sub>A</sub> = +                  |                                                                                         |     |      | 15  |       |

## 20V Digital Input Class-DG Amplifier with I/V Sense and Brownout Prevention

#### **Electrical Characteristics (continued)**

| PARAMETER                           | SYMBOL                                                                       | CONDITIONS                                                                                           | MIN | ТҮР  | MAX | UNITS      |

|-------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----|------|-----|------------|

| AVDD Software                       | ISHDN_SW_AV                                                                  | No BCLK/LRCLK/DIN transactions, $T_A = +25^{\circ}C$                                                 |     | 1.1  | 5   | - μΑ       |

| Shutdown Supply<br>Current          | DD                                                                           | No BCLK/LRCLK/DIN transactions, T <sub>A</sub> = +85°C (Note 3)                                      |     |      | 30  |            |

| DVDDIO+DVDD                         | ISHDN_SW_DV                                                                  | No BCLK/LRCLK/DIN transactions, T <sub>A</sub> = +25°C                                               |     | 6.6  | 15  |            |

| Software Shutdown<br>Supply Current | DD_DVDDIO                                                                    | No BCLK/LRCLK/DIN transactions, T <sub>A</sub> = +85°C (Note 3)                                      |     |      | 18  | μA         |

| POWER CONSUMPTION                   | N / HARDWARE S                                                               | SHUTDOWN                                                                                             |     |      |     |            |

|                                     |                                                                              | VBAT = 3.8V, T <sub>A</sub> = +25°C                                                                  |     | 0.3  | 5   |            |

| VBAT Hardware                       | ISHDN_HW_VB                                                                  | VBAT = 3.8V, T <sub>A</sub> = +85°C (Note 3)                                                         |     |      | 15  | ] <b>^</b> |

| Shutdown Supply<br>Current          | AT                                                                           | VBAT = 5.0V, T <sub>A</sub> = +25°C                                                                  |     | 0.4  | 5   | μA         |

|                                     |                                                                              | VBAT = 5.0V, T <sub>A</sub> = +85°C (Note 3)                                                         |     |      | 15  |            |

|                                     |                                                                              | PVDD = 5.0V, T <sub>A</sub> = +25°C                                                                  |     | 0.25 | 5   |            |

|                                     |                                                                              | PVDD = 5.0V, T <sub>A</sub> = +85°C (Note 3)                                                         |     |      | 15  |            |

| PVDD Hardware                       | ISHDN_HW_PV                                                                  | PVDD = 12V, T <sub>A</sub> = +25°C                                                                   |     | 1    | 5   | - μΑ       |

| Shutdown Supply<br>Current          | DD                                                                           | PVDD = 12V, T <sub>A</sub> = +85°C (Note 3)                                                          |     |      | 15  |            |

|                                     |                                                                              | PVDD = 19V, T <sub>A</sub> = +25°C                                                                   |     | 1.7  | 5   |            |

|                                     |                                                                              | PVDD = 19V, T <sub>A</sub> = +85°C (Note 3)                                                          |     |      | 15  |            |

| AVDD Hardware                       |                                                                              | T <sub>A</sub> = +25°C                                                                               |     | 0.1  | 1   |            |

| Shutdown Supply<br>Current          | ISHDN_HW_AV<br>DD                                                            | T <sub>A</sub> = +85°C (Note 3)                                                                      |     |      | 10  | μA         |

| DVDDIO+DVDD                         | I <sub>SHDN HW DV</sub>                                                      | T <sub>A</sub> = +25°C                                                                               |     | 0.2  | 6.0 |            |

| Hardware Shutdown<br>Supply Current | DD_DVDDIO                                                                    | T <sub>A</sub> = +85°C (Note 3)                                                                      |     |      | 10  | μA         |

| TURN-ON/OFF TIME                    |                                                                              |                                                                                                      |     |      |     |            |

|                                     |                                                                              | From EN bit set to 1 to full operation, volume ramp disabled (Note 4)                                |     | 1.4  | 3   | ms         |

| Turn-On Time                        | Time t <sub>ON</sub>                                                         | From EN bit set to 1 to full operation, volume ramp enabled (Note 4)                                 |     | 3    | 6   | ms         |

|                                     |                                                                              | From SPK_EN bit set to 1 to full<br>operation, EN = 1, volume ramp disabled                          |     | 0.85 |     | ms         |

| Turn-Off Time t <sub>OFF</sub>      |                                                                              | $T_A$ = +25°C, From full operation, EN bit<br>set to 0 to software shutdown, volume<br>ramp disabled |     | 20   | 100 | μs         |

|                                     | tOFF                                                                         | From full operation, EN bit set to 0 to software shutdown, volume ramp enabled                       |     | 2.3  | 6   | ms         |

|                                     | From SPK_EN bit set to 0 to amplifier disabled, volume ramp disabled, EN = 1 |                                                                                                      | 20  |      | μs  |            |

## 20V Digital Input Class-DG Amplifier with I/V Sense and Brownout Prevention

#### **Electrical Characteristics (continued)**

| PARAMETER                           | SYMBOL               | COND                                      | ITIONS                                                           | MIN                        | ТҮР            | MAX                   | UNITS   |

|-------------------------------------|----------------------|-------------------------------------------|------------------------------------------------------------------|----------------------------|----------------|-----------------------|---------|

| DIGITAL AUDIO PATH                  | 1                    | I                                         |                                                                  |                            |                |                       |         |

| DIGITAL AUDIO PATH /                | GAIN CONTROL         | S / DIGITAL VOLUM                         | E CONTROL                                                        |                            |                |                       |         |

| Digital Volume Control<br>(max)     | A <sub>SPK_VOL</sub> | SPK_VOL[6:0] = 0x0                        | 00                                                               |                            | 0              |                       | dB      |

| Digital Volume Control<br>Step Size |                      |                                           |                                                                  |                            | 0.5            |                       | dB      |

| Digital Volume Control<br>(min)     | A <sub>SPK_VOL</sub> | SPK_VOL[6:0] = 0x7                        | 7E                                                               |                            | -63            |                       | dB      |

| DIGITAL AUDIO PATH /                | FILTERING / DIO      | GITAL HIGHPASS FIL                        | TER CHARACTERIS                                                  | FICS (Note #               | 5)             |                       |         |

| DC Attenuation                      |                      |                                           |                                                                  | 80                         |                |                       | dB      |

| DC Blocking Cut Off<br>Frequency    |                      | f <sub>S</sub> = 8kHz, 16kHz, 32          | 2kHz                                                             |                            | 0.856<br>1.872 |                       | Hz      |

| DIGITAL AUDIO PATH /                | FILTERING / DIG      | J<br>GITAL FILTER CHAR                    | ACTERISTICS (LRCL                                                | K < 50kHz) (               | (Note 5)       |                       |         |

| Valid Sample Rates                  |                      |                                           | · · · · · ·                                                      | 16                         | ,              | 48                    | kHz     |

|                                     | fPLP                 | Ripple < δ <sub>P</sub>                   |                                                                  | 0.454 x<br>f <sub>S</sub>  |                |                       | Hz      |

| Passband Cutoff                     |                      | Droop < -3dB                              |                                                                  | 0.459 x<br>f <sub>S</sub>  |                |                       | Hz      |

| Passband Ripple                     | δ <sub>P</sub>       | f < f <sub>PLP</sub> , referenced<br>1kHz | f < f <sub>PLP</sub> , referenced to signal level at<br>1kHz     |                            |                | +0.25                 | dB      |

| Stopband Cutoff                     | f <sub>SLP</sub>     | Attenuation > $\delta_S$                  |                                                                  |                            |                | 0.49 x f <sub>S</sub> | Hz      |

| Stopband Attenuation                | δ <sub>S</sub>       | f > f <sub>SLP</sub>                      |                                                                  | 75                         |                |                       | dB      |

| Group Delay                         |                      | f = 1kHz                                  |                                                                  |                            | 6.1            |                       | Samples |

| DIGITAL AUDIO PATH /                | FILTERING / DIO      | GITAL FILTER CHAR                         |                                                                  | K > 50kHz) (               | (Note 5)       |                       |         |

| Valid Sample Rates                  |                      |                                           |                                                                  | 88.2                       |                | 192                   | kHz     |

|                                     | f <sub>PLP</sub>     |                                           | Ripple < δ <sub>P</sub> ,<br>88.2kHz ≤ f <sub>S</sub> ≤<br>96kHz | 0.227 x<br>f <sub>S</sub>  |                |                       | Hz      |

| Developed Ontoff                    |                      | SPK_WBAND_FIL                             | Droop < -3dB,<br>88.2kHz ≤ f <sub>S</sub> ≤<br>96kHz             | 0.314 x<br><sup>f</sup> S  |                |                       | Hz      |

| Passband Cutoff                     | f <sub>PLP</sub>     | T_EN = 0                                  | Ripple < $\delta_P$ ,<br>176.4kHz ≤ $f_S$ ≤<br>192kHz            | 0.1135 x<br>f <sub>S</sub> |                |                       | Hz      |

|                                     |                      |                                           | Droop < -3dB<br>cutoff, 176.4kHz ≤<br>f <sub>S</sub> ≤ 192kHz    | 0.232 x<br>f <sub>S</sub>  |                |                       | Hz      |

| Passband Ripple                     | δ <sub>P</sub>       | SPK_WBAND_FIL<br>T_EN = 0                 | f < f <sub>PLP</sub> , referenced<br>to signal level at<br>1kHz  | -0.25                      |                | +0.25                 | dB      |

## 20V Digital Input Class-DG Amplifier with I/V Sense and Brownout Prevention

#### **Electrical Characteristics (continued)**

| PARAMETER                                       | SYMBOL           | COND                                                                                         | ITIONS                                                             | MIN                       | TYP      | MAX                   | UNITS   |

|-------------------------------------------------|------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------|----------|-----------------------|---------|

| Stopband Cutoff                                 | f <sub>SLP</sub> | SPK_WBAND_FIL<br>T_EN = 0                                                                    | Attenuation < $\delta_S$                                           |                           |          | 0.49 x f <sub>S</sub> | Hz      |

| Stophand Attonuation                            | ō.               | SPK_WBAND_FIL                                                                                | f > f <sub>SLP,</sub> 88.2kHz ≤<br>f <sub>S</sub> ≤ 96kHz          | 80                        |          |                       | dB      |

| Stopband Attenuation                            | δ <sub>S</sub>   | T_EN = 0                                                                                     | f > f <sub>SLP,</sub> 176.4kHz<br>≤ f <sub>S</sub> ≤ 192kHz        | 65                        |          |                       | uв      |

| Group Delay                                     |                  | SPK_WBAND_FIL<br>T_EN = 0                                                                    | f = 1kHz                                                           |                           | 6.9      |                       | Samples |

| DIGITAL AUDIO PATH /                            | FILTERING / DIG  | GITAL FILTER CHAR                                                                            | ACTERISTICS (LRCL                                                  | K > 50kHz) (              | (Note 5) |                       | •       |

| Valid Sample Rates                              |                  |                                                                                              |                                                                    | 88.2                      |          | 192                   | kHz     |

|                                                 | fPLP             |                                                                                              | Ripple < δ <sub>P</sub> ,<br>88.2kHz ≤ f <sub>S</sub> ≤<br>96kHz   | 0.325 x<br>f <sub>S</sub> |          |                       | Hz      |

| Passband Cutoff                                 |                  | SPK_WBAND_FIL                                                                                | Droop < -3dB,<br>88.2kHz ≤ f <sub>S</sub> ≤<br>96kHz               | 0.463 x<br>f <sub>S</sub> |          |                       | Hz      |

|                                                 | fPLP             | T_EN = 1                                                                                     | Ripple < δ <sub>P</sub> ,<br>176.4kHz ≤ f <sub>S</sub> ≤<br>192kHz | 0.18 x f <sub>S</sub>     |          |                       | Hz      |

|                                                 |                  |                                                                                              | Droop < -3dB<br>cutoff, 176.4kHz ≤<br>f <sub>S</sub> ≤ 192kHz      | 0.3 x f <sub>S</sub>      |          |                       | Hz      |

| Passband Ripple                                 | δ <sub>P</sub>   | SPK_WBAND_FIL<br>T_EN = 1                                                                    | f < f <sub>PLP</sub> , referenced<br>to signal level at<br>1kHz    | -0.35                     |          | +0.35                 | dB      |

| Stopband Cutoff                                 | f <sub>SLP</sub> | SPK_WBAND_FIL<br>T_EN = 1                                                                    | Attenuation < $\delta_S$                                           |                           |          | 0.52 x f <sub>S</sub> | Hz      |

| Stopband Attenuation                            | δ <sub>S</sub>   | SPK_WBAND_FIL<br>T_EN = 1                                                                    | f > f <sub>SLP</sub>                                               | 77                        |          |                       | dB      |

| Group Delay                                     |                  | SPK_WBAND_FIL<br>T_EN = 1                                                                    | f = 1kHz                                                           |                           | 8.1      |                       | Samples |

| Max Device to Device<br>Group Delay Variability |                  | f <sub>IN</sub> = 1kHz                                                                       |                                                                    |                           | 1        |                       | μs      |

| CLASS-DG AMPLIFIER                              |                  |                                                                                              |                                                                    |                           |          |                       |         |

| Output Offset Voltage                           | V <sub>OS</sub>  | T <sub>A</sub> = +25°C, Z <sub>SPK</sub> =<br>DRE_EN = 0                                     | 8Ω + 33μΗ,                                                         | -3                        | ±0.65    | +3                    | mV      |

|                                                 |                  | Peak voltage,                                                                                |                                                                    |                           | -68      |                       |         |

| Click-and-Pop Level                             | К <sub>СР</sub>  | audio playback<br>silent, A-weighted,<br>32 samples per<br>second, $T_A =$<br>+25°C (Note 6) | V <sub>PVDD</sub> = 12V                                            |                           | -68      |                       | dBV     |

## 20V Digital Input Class-DG Amplifier with I/V Sense and Brownout Prevention

#### **Electrical Characteristics (continued)**

| PARAMETER                            | SYMBOL         | CON                                                                                                                  | DITIONS                                                                         | MIN | TYP  | MAX | UNITS             |

|--------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----|------|-----|-------------------|

|                                      | Лѕрк           | V <sub>PVDD</sub> = 12V, V <sub>VB</sub><br>1W, Z <sub>L</sub> = 8Ω + 33μ                                            |                                                                                 |     | 87   |     |                   |

| Efficiency                           | ηςρκ           | V <sub>PVDD</sub> = 12V, V <sub>VB</sub><br>1W, Z <sub>L</sub> = 4Ω + 33μ                                            | <sub>AT</sub> = 3.8V, P <sub>OUT</sub> =<br>H, f <sub>IN</sub> = 1kHz           |     | 83   |     | %                 |

| Efficiency                           | ηςρκ           | V <sub>PVDD</sub> = 19V, V <sub>VB</sub><br>1W, Z <sub>L</sub> = 8Ω + 33μ                                            |                                                                                 |     | 83   |     | 70                |

|                                      | ηςρκ           | $V_{PVDD}$ = 19V, $V_{VB}$<br>20W, $Z_L$ = 8 $\Omega$ + 33                                                           | <sub>AT</sub> = 5.0V, P <sub>OUT</sub> =<br>µH, f <sub>IN</sub> = 1kHz          | 91  |      |     |                   |

|                                      |                | V <sub>PVDD</sub> = 12V, Z <sub>L</sub> =<br>≤ 1%, f <sub>IN</sub> = 1kHz                                            | = 4Ω + 33µH, THD+N                                                              |     | 14   |     |                   |

| Output Power                         |                | V <sub>PVDD</sub> = 19V, Z <sub>L</sub> =<br>1%, f <sub>IN</sub> = 1kHz                                              | =8Ω + 33µH, THD+N ≤                                                             |     | 20   |     |                   |

|                                      | Роит           | V <sub>PVDD</sub> = 14V, Z <sub>L</sub> =<br>1%, f <sub>IN</sub> = 1kHz                                              | <sup>:</sup> 4Ω + 33µH, THD+N ≤                                                 |     | 19   |     | w                 |

|                                      |                | V <sub>PVDD</sub> = 12V, Z <sub>L</sub> =<br>10%, f <sub>IN</sub> = 1kHz                                             | <sup>:</sup> 4Ω + 33µH, THD+N ≤                                                 |     | 17.8 |     |                   |

|                                      |                | V <sub>PVDD</sub> = 19V, Z <sub>L</sub> =<br>10%, f <sub>IN</sub> = 1kHz                                             |                                                                                 | 25  |      |     |                   |

| Peak Output Power                    | Pout           | $Z_L = 4\Omega + 33\mu$ H; 5<br>signal)/1kHz (460 μ<br>signal) alternating<br>12dB; test duration<br>100°C and THD+N |                                                                                 | 60  |      | w   |                   |

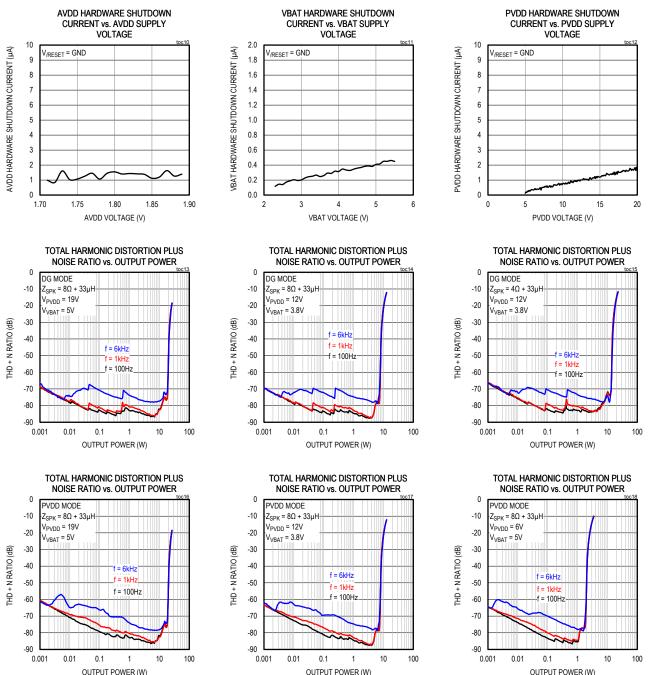

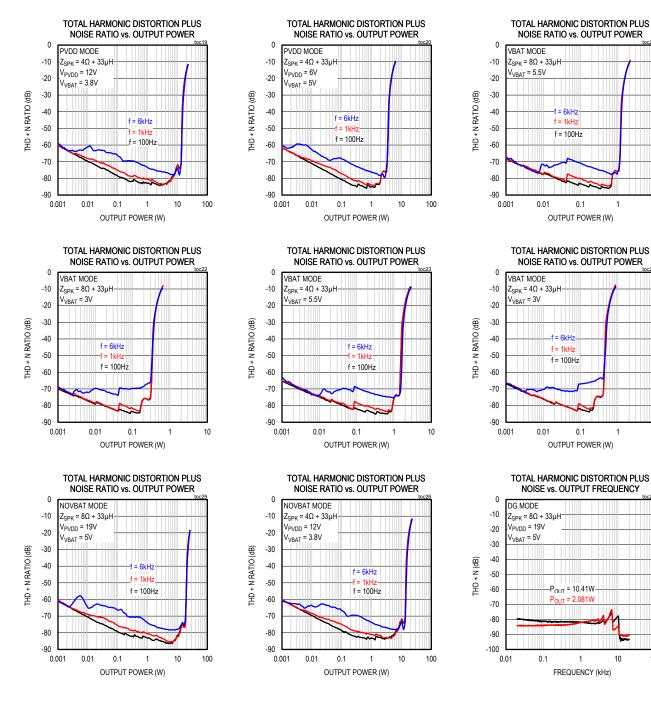

|                                      |                | f <sub>IN</sub> = 1kHz, P <sub>OUT</sub> =                                                                           | = 1W, Z <sub>L</sub> = 8Ω + 33μH                                                | -80 |      |     |                   |

|                                      |                | f <sub>IN</sub> = 1kHz, P <sub>OUT</sub> =                                                                           | = 2W, Z <sub>L</sub> = 4Ω + 33μH                                                |     | -80  |     | 1                 |

|                                      |                | f <sub>IN</sub> = 6kHz, P <sub>OUT</sub> =                                                                           | = 1W, Z <sub>L</sub> = 8Ω + 33μH                                                |     | -75  |     | 1                 |

|                                      |                |                                                                                                                      | = 2W, Z <sub>L</sub> = 4Ω + 33μH                                                |     | -73  |     | 1                 |

| <b>T</b> (a) (1) and a (1)           |                |                                                                                                                      | f <sub>IN</sub> = 1kHz, P <sub>OUT</sub> =<br>1W, Z <sub>L</sub> = 8Ω +<br>33μH | -75 | -82  |     |                   |

| Total Harmonic<br>Distortion + Noise | THD+N          | V <sub>PVDD</sub> = 12V                                                                                              | $f_{IN}$ = 1kHz, $P_{OUT}$ =<br>2W, $Z_L$ = 4 $\Omega$ +<br>33 $\mu$ H          |     | -80  |     | dB                |

|                                      |                |                                                                                                                      | f <sub>IN</sub> = 6kHz, P <sub>OUT</sub> =<br>1W, Z <sub>L</sub> = 8Ω +<br>33μH |     | -76  |     |                   |

|                                      |                | V <sub>PVDD</sub> = 14V                                                                                              | f <sub>IN</sub> = 6kHz, P <sub>OUT</sub> =                                      |     | -74  |     |                   |

| Intermodulation<br>Distortion        |                | ITU-R standard, f <sub>IN</sub><br>= -3dBFS                                                                          | i = 19kHz/20kHz, V <sub>IN</sub>                                                |     | -79  |     | dB                |

| Output Noise                         | e <sub>N</sub> | A-weighted                                                                                                           |                                                                                 |     | 15.5 |     | μV <sub>RMS</sub> |

## 20V Digital Input Class-DG Amplifier with I/V Sense and Brownout Prevention

#### **Electrical Characteristics (continued)**

| PARAMETER                       | SYMBOL                                     | COND                                                                                              | ITIONS                                                                                              | MIN  | TYP  | MAX | UNITS |

|---------------------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|------|-----|-------|

| Dynamic Range                   | DR                                         | Measured using EIA<br>output signal at 1kHz<br>output power at 1%T                                | z referenced to                                                                                     |      | 118  |     | dB    |

| CLASS-DG AMPLIFIER /            | POWER SUPP                                 | LY RIPPLE REJECTION                                                                               | <b>DN</b>                                                                                           |      |      |     |       |

| VBAT Supply Rejection DC        | PSRR                                       | V <sub>VBAT</sub> = 3.0V to 5.5                                                                   | V                                                                                                   | 65   | 85   |     | dB    |

|                                 |                                            |                                                                                                   | f <sub>RIPPLE</sub> = 217Hz                                                                         |      | 78   |     |       |

| VBAT Supply Rejection<br>AC     | PSRR                                       | V <sub>RIPPLE</sub> =<br>100mV <sub>P-P</sub>                                                     | f <sub>RIPPLE</sub> = 1kHz                                                                          |      | 78   |     | dB    |

|                                 |                                            | 100mVP-P                                                                                          | f <sub>RIPPLE</sub> = 20kHz                                                                         |      | 64   |     | 1     |

| PVDD Supply DC<br>Rejection     | PSRR                                       | SPK_MODE =<br>0x1(PVDD Mode)                                                                      | V <sub>PVDD</sub> = 3.0V to<br>20V                                                                  | 60   | 90   |     | dB    |

|                                 |                                            | SPK_MODE =                                                                                        | f <sub>RIPPLE</sub> = 217Hz                                                                         |      | 80   |     |       |

| PVDD Supply Rejection<br>AC     | PSRR                                       | 0x1(PVDD Mode),<br>V <sub>RIPPLE</sub> =                                                          | f <sub>RIPPLE</sub> = 1kHz                                                                          |      | 75   |     | dB    |

|                                 |                                            | 100mV <sub>P-P</sub>                                                                              | f <sub>RIPPLE</sub> = 20kHz                                                                         |      | 60   |     |       |

| AVDD Supply DC<br>Rejection     | PSRR                                       | V <sub>AVDD</sub> = 1.71V to 1.                                                                   | 89V                                                                                                 | 60   | 90   |     | dB    |

|                                 |                                            |                                                                                                   | f <sub>RIPPLE</sub> = 217Hz                                                                         |      | 90   |     |       |

| AVDD Supply Rejection           | PSRR                                       | V <sub>RIPPLE</sub> =<br>100mV <sub>P-P</sub>                                                     | f <sub>RIPPLE</sub> = 1kHz                                                                          |      | 90   |     | dB    |

|                                 |                                            | 10011112-0                                                                                        | f <sub>RIPPLE</sub> = 20kHz                                                                         |      | 70   |     |       |

| DVDD Supply DC<br>Rejection     | PSRR                                       | V <sub>DVDD</sub> = 1.14V to 1.                                                                   | 89V                                                                                                 |      | 100  |     | dB    |

|                                 |                                            |                                                                                                   | f <sub>RIPPLE</sub> = 217Hz                                                                         |      | 95   |     | 1     |

| DVDD Supply Rejection<br>AC     | PSRR                                       | V <sub>RIPPLE</sub> =<br>100mV <sub>P-P</sub>                                                     | f <sub>RIPPLE</sub> = 1kHz                                                                          |      | 95   |     | dB    |

|                                 |                                            | 10011112-0                                                                                        | f <sub>RIPPLE</sub> = 20kHz                                                                         |      | 95   |     | 1     |

| DVDDIO Supply DC<br>Rejection   | PSRR                                       | V <sub>DVDDIO</sub> = 1.14V to                                                                    | 1.89V                                                                                               |      | 100  |     | dB    |

|                                 |                                            |                                                                                                   | f <sub>RIPPLE</sub> = 217Hz                                                                         |      | 95   |     |       |

| DVDDIO Supply<br>Rejection AC   | PSRR                                       | V <sub>RIPPLE</sub> =<br>100mV <sub>P-P</sub>                                                     | f <sub>RIPPLE</sub> = 1kHz                                                                          |      | 95   |     | dB    |

|                                 |                                            | 100mVP-P                                                                                          | f <sub>RIPPLE</sub> = 20kHz                                                                         |      | 95   |     |       |

| CLASS-DG AMPLIFIER /            | POWER SUPP                                 |                                                                                                   | N                                                                                                   |      |      |     |       |

|                                 | f <sub>IN</sub> = 1kHz, P <sub>OUT</sub> = |                                                                                                   | V <sub>VBAT</sub> , f <sub>RIPPLE</sub> =<br>217Hz, V <sub>RIPPLE</sub> =<br>100mV <sub>P-P</sub>   | -78  | -85  |     |       |

| Power Supply<br>Intermodulation |                                            | V <sub>DVDD</sub> , f <sub>RIPPLE</sub> =<br>217Hz, V <sub>RIPPLE</sub> =<br>100mV <sub>P-P</sub> |                                                                                                     | -100 |      | dB  |       |

|                                 |                                            | -                                                                                                 | V <sub>DVDDIO</sub> , f <sub>RIPPLE</sub><br>= 217Hz, V <sub>RIPPLE</sub><br>= 100mV <sub>P-P</sub> |      | -100 |     |       |

## 20V Digital Input Class-DG Amplifier with I/V Sense and Brownout Prevention

#### **Electrical Characteristics (continued)**

| PARAMETER                              | SYMBOL           | CONDITIONS                                                                                                            | MIN                   | TYP | MAX                   | UNITS  |

|----------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------|-----|-----------------------|--------|

| Output Switching                       |                  | Constant across all sample rates in the 48kHz family                                                                  |                       | 472 |                       | kHz    |

| Frequency                              |                  | Constant across all sample rates in the 44.1kHz family                                                                |                       | 451 |                       | KIIZ   |

| Frequency Response<br>Deviation        |                  | Across the bandwidth 20Hz to 20kHz<br>referenced to f <sub>IN</sub> = 1kHz (Note 3)                                   | -0.25                 |     | +0.25                 | dB     |

| Gain Error                             | AVERROR          |                                                                                                                       | -0.5                  |     | +0.5                  | dB     |

| Channel-to-Channel<br>Phase Error      |                  | Output phase shift between multiple<br>devices from 20Hz to 20kHz, across all<br>sample rates and DAI operating modes |                       | 1   |                       | o      |

| Minimum Load<br>Resistance             |                  |                                                                                                                       |                       | 3.2 |                       | Ω      |

| Minimum Load<br>Inductance             |                  | In series with a $3.2\Omega$ load                                                                                     |                       | 0   |                       | μH     |

| Maximum Load<br>Inductance             |                  | In series with a $3.2\Omega$ load                                                                                     |                       | 100 |                       | μH     |

| Current Limit                          | I <sub>LIM</sub> | PVDD mode                                                                                                             | 6.2                   | 7   |                       | Α      |

| SPEAKER VOLTAGE AI                     | DC DC            |                                                                                                                       |                       |     |                       |        |

| Resolution                             |                  |                                                                                                                       |                       | 16  |                       | Bits   |

| Sample Rate                            | fSVSNS ADC       |                                                                                                                       | 8                     |     | 192                   | kHz    |

| Voltage Range                          | V <sub>SPK</sub> |                                                                                                                       |                       | ±22 |                       | V      |

| Dynamic Range                          | DNR              | f <sub>IN</sub> = 1kHz, AC measurement bandwidth<br>= 20Hz to 20kHz, unweighted                                       |                       | 81  |                       | dB     |

| Total Harmonic<br>Distortion + Noise   | THD+N            | f <sub>IN</sub> = 1kHz, V <sub>SPK</sub> = 8Vrms                                                                      |                       | -65 |                       | dB     |

|                                        |                  | DC blocking filter enabled                                                                                            | -0.2                  |     | +0.2                  |        |

| DC Offset Voltage                      |                  | DC blocking filter disabled, $T_A = +25^{\circ}C$<br>(Note 3)                                                         | -10                   |     | +10                   | mV     |

| Highpass Cutoff<br>Frequency           |                  | -3dB limit across all sample rates                                                                                    |                       |     | 2                     | Hz     |

| SPEAKER VOLTAGE A                      | DC / DIGITAL FIL | TER CHARACTERISTICS (f <sub>S</sub> < 50kHz) (No                                                                      | ote 5)                |     |                       |        |

| Passband Ripple                        |                  | f <sub>IN</sub> < f <sub>PLP,</sub> referenced to signal level at<br>1kHz                                             | -0.225                |     | +0.225                | dB     |

| Lowpass Filter Cutoff<br>Frequency     | f <sub>PLP</sub> | Droop < -3dB                                                                                                          | 0.44 x f <sub>S</sub> |     |                       | Hz     |

| Lowpass Filter<br>Stopband Frequency   | fSLP             | -40dB limit                                                                                                           |                       |     | 0.58 x f <sub>S</sub> | Hz     |

| Lowpass Filter<br>Stopband Attenuation |                  |                                                                                                                       | 40                    |     |                       | dB     |

| Group Delay                            |                  | f <sub>IN</sub> = 1kHz                                                                                                |                       | 8   |                       | Sample |

## 20V Digital Input Class-DG Amplifier with I/V Sense and Brownout Prevention

#### **Electrical Characteristics (continued)**

| PARAMETER                              | SYMBOL           | COND                        | ITIONS                                                                        | MIN                       | TYP | MAX                   | UNITS   |

|----------------------------------------|------------------|-----------------------------|-------------------------------------------------------------------------------|---------------------------|-----|-----------------------|---------|

| SPEAKER VOLTAGE A                      | DC / DIGITAL FI  | TER CHARACTERIS             | TICS (f <sub>S</sub> > 50kHz) (No                                             | ote 5)                    |     |                       |         |

| Passband Ripple                        |                  | IVADC_WBAND_F<br>ILT_EN = 0 | f <sub>IN</sub> ≤ f <sub>PLP</sub> ,<br>referenced to<br>signal level at 1kHz | -0.225                    |     | +0.225                | dB      |

|                                        | f <sub>PLP</sub> |                             | Ripple < δ <sub>Ρ</sub> ,<br>88.2kHz ≤ f <sub>S</sub> ≤<br>96kHz              | 0.26 x f <sub>S</sub>     |     |                       |         |

| Lowpass Filter Cutoff                  |                  | IVADC_WBAND_F               | Droop < -3dB,<br>88.2kHz ≤ f <sub>S</sub> ≤<br>96kHz                          | 0.31 x f <sub>S</sub>     |     |                       | LI      |

| Frequency                              | f <sub>PLP</sub> | ILT_EN = 0                  | Ripple < δ <sub>P</sub> ,<br>176.4kHz ≤ f <sub>S</sub> ≤<br>192kHz            | 0.13 x f <sub>S</sub>     |     |                       | Hz      |

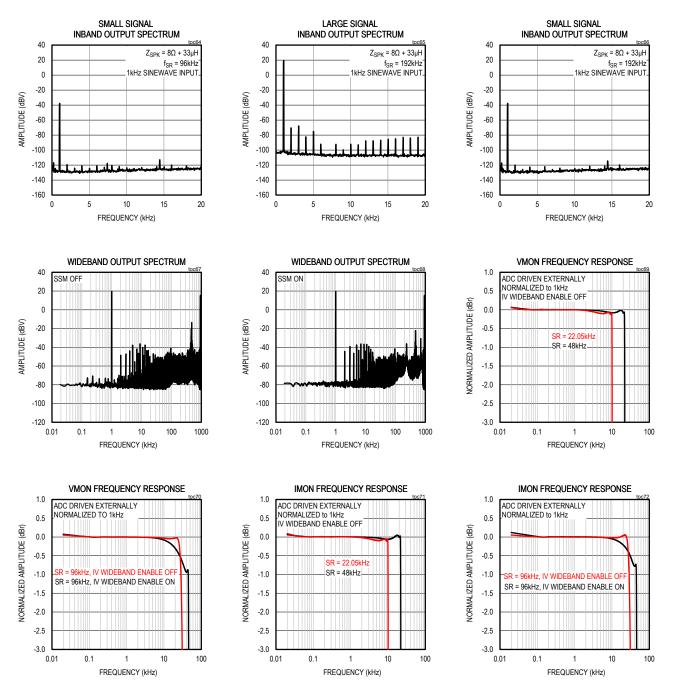

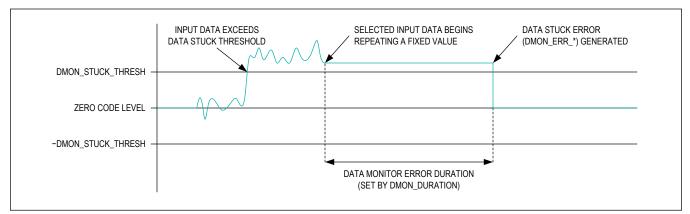

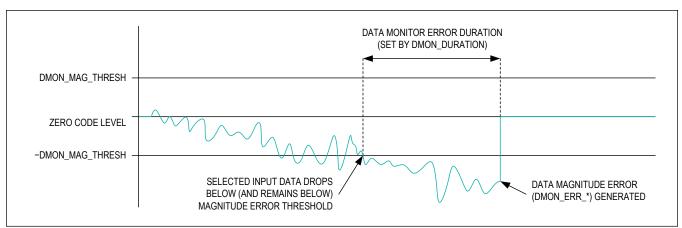

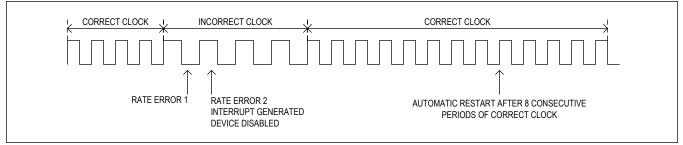

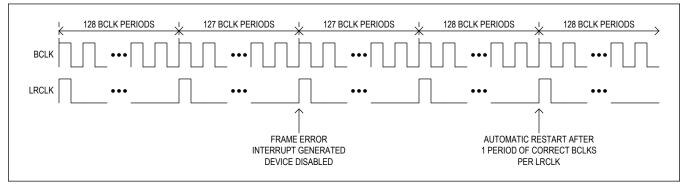

|                                        |                  |                             | Droop < -3dB,<br>176.4kHz ≤ f <sub>S</sub> ≤<br>192kHz                        | 0.189 x<br>f <sub>S</sub> |     |                       |         |