T-45-23-21

# 9305

## VARIABLE MODULUS COUNTER

**DESCRIPTION** — The '05 is a monolithic, high speed, variable modulus counter circuit. It is a semisynchronous counter which can be programmed without extra logic to provide division or counting by either 2 and 4, 5, 6, 7, 8 or 10, 12, 14, 16. A binary count sequence can be obtained for all of the preceding counter modulos as well as 50% duty cycle output for dividers of 8, 10, 12, 14, 16. The device also features asynchronous overriding Master Reset and Set inputs and the negation output of the final flip-flop output which allows the cascading of stages.

- VARIOUS BINARY COUNTING MODES MODULO 2 AND MODULO 5, 6, 7, 8 MODULO 10 (8421 BCD) 12, 14, 16

- VARIOUS DIVISION MODES WITH 50% DUTY CYCLE OUTPUT MODULO 8, 10, 12, 14, 16

- LOGIC SELECTION OF COUNTING MODE

- ASYNCHRONOUS MASTER RESET ANS SET INPUTS

- MULTISTAGE COUNTING OPERATION

**ORDERING CODE:** See Section 9

| 0::02::            |     |                                                                                          |                                                                                               |      |  |

|--------------------|-----|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------|--|

|                    | PIN | COMMERCIAL GRADE                                                                         | MILITARY GRADE                                                                                | PKG  |  |

| PKGS               | OUT | $V_{CC} = +5.0 \text{ V } \pm 5\%,$<br>$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ}\text{ C to } +125^{\circ}\text{ C}$ | TYPE |  |

| Plastic<br>DIP (P) | A   | 9305PC                                                                                   |                                                                                               | 9A   |  |

| Ceramic<br>DIP (D) | А   | 9305DC                                                                                   | 9305DM                                                                                        | 6A   |  |

| Flatpak<br>(F)     | А   | 9305FC                                                                                   | 9305FM                                                                                        | 3B   |  |

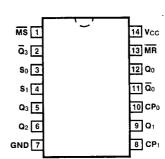

#### CONNECTION DIAGRAM PINOUT A

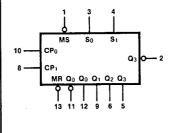

#### LOGIC SYMBOL

Vcc = Pin 14 GND = Pin 7

### INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES                         | DESCRIPTION                                        | 93XX (U.L.)<br>HIGH/LOW |  |

|-----------------------------------|----------------------------------------------------|-------------------------|--|

| S <sub>0</sub> , S <sub>1</sub>   | Select Inputs                                      | 1.0/1.0                 |  |

| CP <sub>0</sub>                   | First Stage Clock Pulse Input (Active Rising Edge) | 1.0/1.0                 |  |

|                                   | Three Stage Clock Pulse Input (Active Rising Edge) | 1.0/1.0                 |  |

| CP1<br>MS<br>MR                   | Master Set Input (Active LOW)                      | 1.0/1.0                 |  |

| MB                                | Master Reset Input (Active LOW)                    | 1.0/1.0                 |  |

|                                   | First Stage Output                                 | 16/8.0                  |  |

| Q <sub>0</sub> .                  | Complementary First Stage Output                   | 16/8.0                  |  |

|                                   | Three Stage Counter Outputs                        | 16/8.0                  |  |

| <u>Q</u> 1 — Q3<br><del>Q</del> 3 | Complementary Last Stage Output                    | 20/10                   |  |

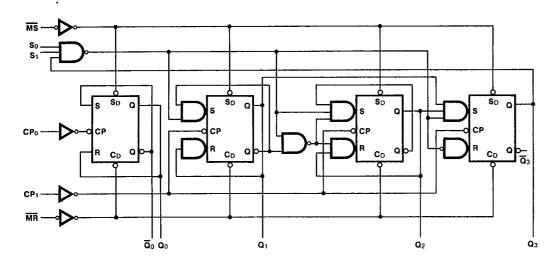

FUNCTIONAL DESCRIPTION — The '05 consists of four master/slave flip-flops which are separated into two functional units — a single toggle stage and a three stage synchronous counter. All four flip-flips change state on the LOW-to-HIGH transition of the clock. The three stage counter can be programmed with external connections to provide moduli of either 5, 6, 7 or 8. This basic configuration allows synchronous binary counting by the last three stages and independent modulo 2 operation with the first single stage.

A four stage binary counter with a modulo of 10, 12, 14 or 16 is obtained by applying the incoming clock to the single toggle stage and feeding its negation output to the clock input of the three stage counter. A 4-stage divider with 50% duty cycle output is produced by feeding the incoming clock to the three stage counter and clocking the single stage with the  $\overline{Q}_3$  output. In either the binary or 50% division mode the modulo (10, 12, 14, 16) is determined by the external programming connections for the three stage counter. These 4-stage counters or dividers are not fully synchronous (semisynchronous) but have only one flip-flop ripple delay in either configuration. Counter moduli other than 10, 12, 14, 16 can be formed with a few extra gates.

Several '05 variable modulus counters programmed in any modulo can be connected together without extra logic to form asynchronous (ripple) type multistage counters. This is done by connecting the Q3 output of the less significant counter to the clock input of the following counter.

The Master Set and Reset will asynchronously set or reset all four stages when activated. The active LOW Reset input when LOW will clear the counter, overriding the clock and forcing the outputs Q<sub>0</sub> — Q<sub>3</sub> LOW and outputs  $\overline{Q}_0$ ,  $\overline{Q}_3$  HIGH. The active LOW Set input when LOW will preset the counter, overriding the clock and forcing the outputs Q<sub>0</sub> — Q<sub>3</sub> HIGH and outputs  $\overline{Q}_0$ ,  $\overline{Q}_3$  LOW. The master set provides a synchronous clear, since the first clock pulse following the asynchronous master set will reset all stages. This action is independent of the molulo programmed.

#### LOGIC DIAGRAM

#### **COUNTING MODE**

The following are rules specifying the external connections required for various counter and divider modulos.

### **ASYNCHRONOUS MODE**

| INPUTS |    |     | OUT            | PUT            | s              |    |

|--------|----|-----|----------------|----------------|----------------|----|

| MS MR  | Qo | Q₀  | Q <sub>1</sub> | Q <sub>2</sub> | Q <sub>3</sub> | Q₃ |

| L H    | Н  | L   | Н              | Н              | Н              | L  |

| H · L  | L  | Н   | L              | L              | L              | Н  |

| нн     | CO | UNT | •              |                |                |    |

<sup>\*</sup>As determined by programming connections.

#### **PROGRAMMING CONNECTIONS** FOR LAST THREE STAGES

| So S1             | MODULO |

|-------------------|--------|

| NC NC             | 5      |

| Q <sub>1</sub> NC | 6<br>6 |

| Q <sub>2</sub> NC | 7      |

| NC Q <sub>2</sub> | 7      |

| Q1 Q2             | 8      |

| Q2 Q1             | 8      |

NC = Not Connected

#### **CONNECTIONS FOR MODULO** 10, 12, 14, 16 BINARY COUNTERS **AND 50% DUTY CYCLE DIVIDERS**

For\_Binary Counting Q<sub>0</sub> connected to CP<sub>1</sub> Incoming clock to CPo

For 50% Duty Cycle Output Q<sub>3</sub> connected to CP<sub>0</sub> Incoming Clock to CP1

#### **ALTERNATE PROGRAMMING CONNECTIONS** FOR LAST THREE STAGES\*\*

|        |                  | •                            |                                                                                                                                                               |                                                      |

|--------|------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| MODULO | INP              | UTS<br>S1                    | OUTPUT                                                                                                                                                        | AVAILABLE<br>OUTPUT<br>FAN-OUT                       |

| 5      | Q <sub>3</sub>   | Q <sub>3</sub>               | Q3                                                                                                                                                            | 14/8.0                                               |

| 6      | Q <sub>1</sub>   | Q <sub>1</sub>               | Q <sub>1</sub>                                                                                                                                                | 14/7.0                                               |

| 7      | Q <sub>2</sub>   | $Q_2$                        | Q <sub>2</sub>                                                                                                                                                | 14/7.0                                               |

| 8      | Q <sub>1</sub>   | $Q_2$                        | Q <sub>2</sub>                                                                                                                                                | 15/7.0                                               |

| 8      | Q <sub>2</sub>   | Q <sub>1</sub>               | Q <sub>1</sub>                                                                                                                                                | 15/7.0                                               |

|        | 5<br>6<br>7<br>8 | 5 Q3<br>6 Q1<br>7 Q2<br>8 Q1 | S <sub>0</sub> S <sub>1</sub> 5 Q <sub>3</sub> Q <sub>3</sub> 6 Q <sub>1</sub> Q <sub>1</sub> 7 Q <sub>2</sub> Q <sub>2</sub> 8 Q <sub>1</sub> Q <sub>2</sub> | 5 Q3 Q3 Q3<br>6 Q1 Q1 Q1<br>7 Q2 Q2 Q2<br>8 Q1 Q2 Q2 |

"The alternate programming connections program the counter and conveniently terminate unused select inputs (NC). Since these inputs form the inputs to a single NAND gate (See logic diagram), their connection to the counter outputs for the various count modulos provides the indicated output drive.

H = HIGH Voltage Level

L = LOW Voltage Level

05

| SYMBOL | PARAMETER                    | 93XX |     | UNITS | CONDITIONS                                    |

|--------|------------------------------|------|-----|-------|-----------------------------------------------|

|        |                              | Min  | Max |       | 33.151113113                                  |

| Isc    | Output Short Circuit Current | -20  | -70 | mA    | V <sub>CC</sub> = Max, V <sub>OUT</sub> = 0 V |

| lcc    | Power Supply Current         |      | 66  | mA    | V <sub>CC</sub> = Max                         |

AC CHARACTERISTICS: V<sub>CC</sub> = +5.0 V, T<sub>A</sub> = +25°C (See Section 3 for waveforms and load configurations)

| SYMBOL           |                                                                              | 93XX<br>C <sub>L</sub> = 15 pF |          |       | CONDITIONS                                                                                        |

|------------------|------------------------------------------------------------------------------|--------------------------------|----------|-------|---------------------------------------------------------------------------------------------------|

|                  | PARAMETER                                                                    |                                |          | UNITS |                                                                                                   |

|                  |                                                                              | Min                            | Max      | ]     |                                                                                                   |

| f <sub>max</sub> | Maximum Count Frequency                                                      | 23                             |          | MHz   | Modulo 16 (S <sub>0</sub> to Q <sub>1</sub> , S <sub>1</sub> to                                   |

| tpLH<br>tpHL     | Propagation Delay<br>CP₀ to Ō₃ (Modulo 16 Connection)                        |                                | 38<br>48 | ns    | Q <sub>2</sub> , Q <sub>0</sub> to CP <sub>1</sub> , input to CP <sub>0</sub> )<br>Figs. 3-1, 3-8 |

| tplH<br>tpHL     | Propagation Delay<br>CP <sub>0</sub> to Q <sub>0</sub>                       |                                | 21<br>30 | ns    | Modulo-16<br>Figs. 3-1, 3-8                                                                       |

| tpLH<br>tpHL     | Propagation Delay<br>CP <sub>1</sub> to $\overline{Q}_3$ or $\overline{Q}_3$ |                                | 23<br>30 | ns    | Modulo-8<br>Figs. 3-1, 3-8                                                                        |

| tрLН             | Propagation Delay MS to Q <sub>1</sub>                                       |                                | 26       | ns    | Modulo-8<br>Figs. 3-1, 3-16                                                                       |

| t <sub>PHL</sub> | Propagation Delay<br>MR to Q <sub>1</sub>                                    |                                | 35       | ns    | Modulo-8<br>Figs. 3-1, 3-16                                                                       |

AC OPERATING REQUIREMENTS: VCC = +5.0 V, TA = +25°C

| SYMBOL           | PARAMETER                              | 93  | 3XX | UNITS | CONDITIONS |

|------------------|----------------------------------------|-----|-----|-------|------------|

|                  |                                        | Min | Max | 7     |            |

| tw               | CP <sub>0</sub> Pulse Width            | 22  |     | ns    | Fig. 3-8   |

| tw               | MR or MS Pulse Width                   | 24  |     | ns    | Fig. 3-16  |

| t <sub>rec</sub> | Recovery Time<br>MS to CP <sub>1</sub> | 25  |     | ns    | Fig. 3-16  |

| t <sub>rec</sub> | Recovery Time MR to CP1                | 30  |     | ns    | Fig. 3-16  |

6-19