## Single-chip Type with Built-in FET Switching Regulator Series

# Step-up and inverted 2-channel DC/DC converter with Built-in Power MOSFET

#### **BD8317GWL**

#### Description

The BD8317GWL is step-up and inverted 2-channel switching regulator with integrated internal high-side MOSFET. With wide input range from 2.5~5.5V ,it suitable for application of portable item. In addition,The small package design is ideal for miniaturizing the power supply.

#### Features

- Wide input voltage range of 2.5V to 5.5 V

- High frequency operation 0.8MHz

- Incorporates Nch FET of  $230m \Omega/22V$  and Pch Pow FET of  $230m \Omega/15V$

- Incorporates Soft Start (4.2msec(typ))and hight side switch of boost channel

- Independent ON/OFF signal(STB). Built-in discharge SW for step up channel

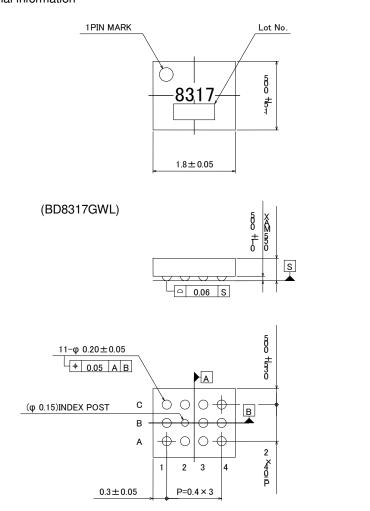

- Small package UCSP50L1(1.8mm×1.5mm, 4×3 grid, 11pin, WLCSP)

- Circuits protection OCP,SCP,UVLO,TSD

## Important Specifications

Input voltage range 2.5~5.5 [V] Output boost voltage Input voltage(max)~18 [V] Output inverted voltage -9.0~-1.0 [V] Maximum current 1.0A](max) Operating frequency 0.8 [MHz] (typ.) Nch FET ON resistance  $230[m\Omega]$ Pch FET ON resistance  $230[m\Omega]$ Standby current  $1[\mu A](max)$

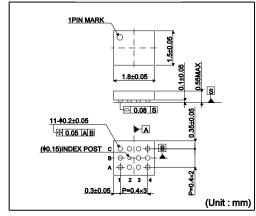

#### Package

UCSP50L1 (WLCSP) 1.8mm × 1.5mm × 0.5mm, 4 × 3glid,11pin,

#### Application

- LCD battery

- CCD battery

- Portable items that are represented by mobile phone and DSC

STRUCTURE : Silicon Monolithic Integrated Circuit

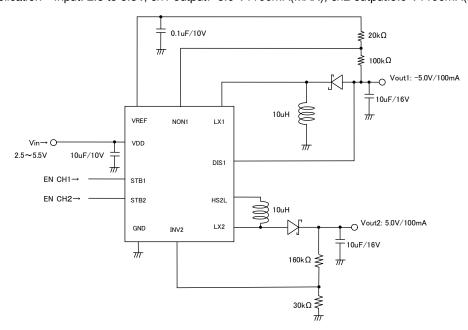

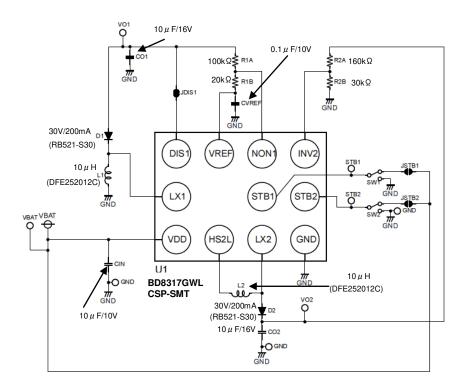

● Typical Application Input: 2.5 to 5.5V, ch1 output: -5.0 V /100mA(MAX), ch2 output:5.0 V /100mA(MAX)

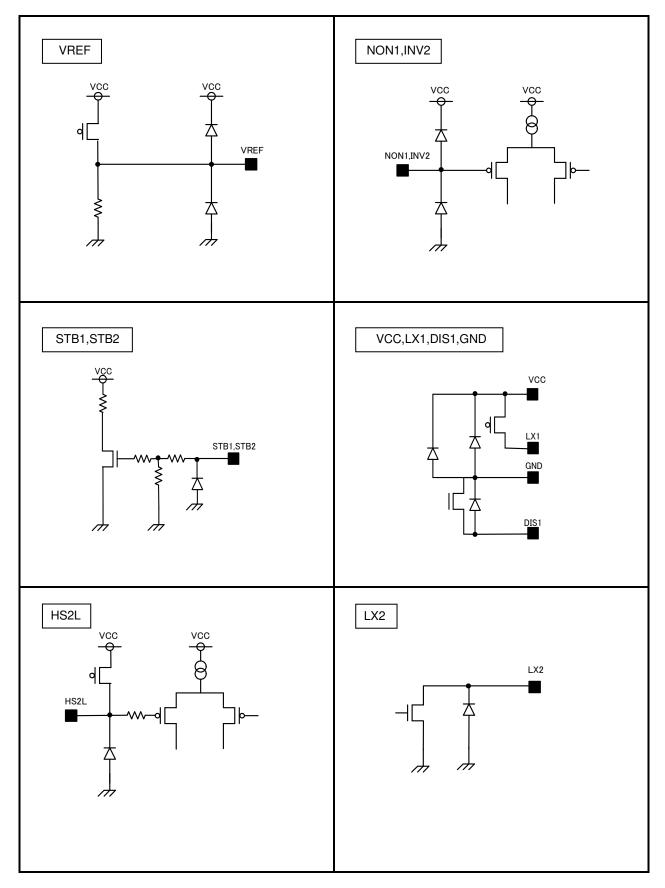

Figure 1. Application schematic

## ●Pin Description

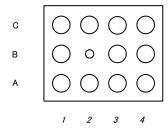

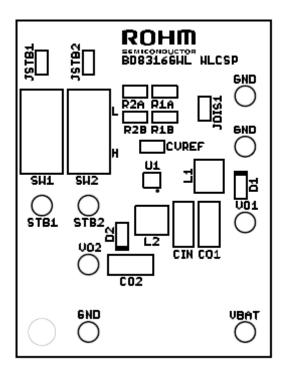

Figure 2. Pin assignment (Bottom view)

| Pin No. | Pin Name                                                                                   | Function                                                                                                                                                                                                                                      |  |  |  |  |  |

|---------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| A-1     | VDD                                                                                        | Power input voltage pin. Connect to input ceramic capacitor bigger than 0.47uF.                                                                                                                                                               |  |  |  |  |  |

| A-2     | HS2L                                                                                       | oad SW output pin .Connect to inductor                                                                                                                                                                                                        |  |  |  |  |  |

| A-3     | LX2                                                                                        | Boost channel drain Nch Power MOS. Connect to diode and inductor.                                                                                                                                                                             |  |  |  |  |  |

| A-4     | GND                                                                                        | Ground connection                                                                                                                                                                                                                             |  |  |  |  |  |

| B-1     | LX1                                                                                        | PchPowerMOS drain of boost channel. Connect to diode and inductor                                                                                                                                                                             |  |  |  |  |  |

| B-3     | STB1                                                                                       | Enable pin of inverted channel. ON threshold set to 1.5V. Integrated pull down resistance (800kΩ (typ))                                                                                                                                       |  |  |  |  |  |

| B-4     | STB2                                                                                       | Enable pin of boost channel.  ON threshold set to 1.5V. Integrated pull down resistance ( $800$ k $\Omega$ (typ))                                                                                                                             |  |  |  |  |  |

| C-1     | DIS1                                                                                       | Discharge SW of inverted channel. Connect to output of inverted channel. STB1 disable , Output pin voltage is discharged by $100\Omega$ (typ)                                                                                                 |  |  |  |  |  |

| C-2     | C-2 VREF Reference voltage of inverted channel.  1.0V(typ) is included in error amp offset |                                                                                                                                                                                                                                               |  |  |  |  |  |

| C-3     | NON1                                                                                       | Feedback pin of inverted channel. Connect to feedback resistance and set output voltage. The method of output voltage setting is P16/20. When inverted cannel is disable, the pin is discharged by integrated resistance (150 $\Omega$ (typ)) |  |  |  |  |  |

| C-4     | INV2                                                                                       | Feedback pin of boost channel. Connect to feedback resistance and set output voltage.  The method of output voltage setting is P16/20.                                                                                                        |  |  |  |  |  |

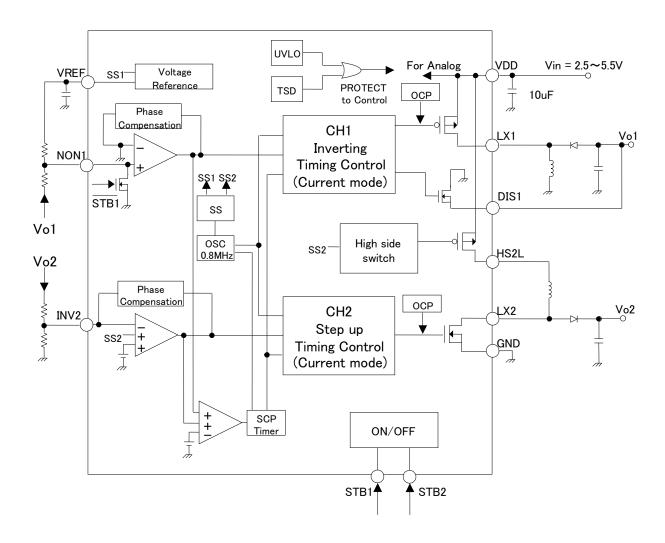

### Block Diagram

Figure 3. Block diagram

#### Function blacks description

#### 1. Voltage Reference

This block generates ERROR AMP reference voltage.

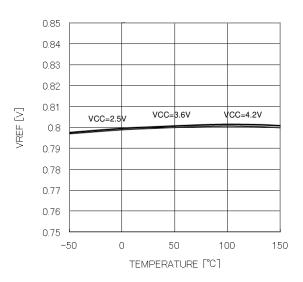

The reference voltage of CH1 is 1.0V, The reference voltage of CH2 is 0.8V.

#### 2.UVLO

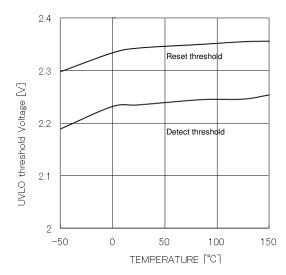

Circuit for preventing malfunction at low voltage input.

This circuit prevents malfunction at the start of DC/DC converter and low input voltage .The function monitors VCC pin voltage and if VCC voltage is lower than 2.2V, function turns off all output of FETs and DC/DC converter , and reset the timer latch of the internal SCP circuit and soft-start circuit.

#### 3.SCP

Short-circuit protection function based on timer latch system.

When the voltage of NON1 pin is higher than 0V or INV2 pin voltage is lower than 0.8V, the internal SCP circuit starts counting.

SCP circuit detects output of Error AMP. Since internal Error AMP has highly gain as high as 80dB or more, if input erroramp voltage cross reference voltage, the output voltage of Error AMP goes high and detects SCP.

The internal counter is in synch with OSC, the latch circuit activates after the counter counts oscillations to turn off DC/DC converter output (about 40.9 msec ).

To reset the latch circuit, turn off the STB pin once. Then, turn it on again or turn on the power supply voltage again.

#### 4.OSC

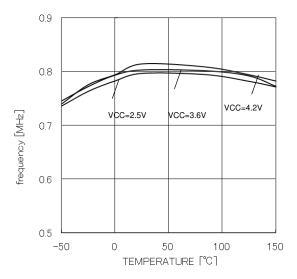

This function determine oscillation frequency . Oscillation frequency of DC/DC converter set at 0.8MHz.

#### 5.ERROR AMP

Error amplifier watch output voltage and output PWM control signals.

The internal reference voltage for Error AMP of ch1 is set at 0V.

The internal reference voltage for Error AMP of ch2 is set at 0.8V.

#### 6. Timing Control

Voltage-pulse width converter for controlling output voltage corresponding to input voltage.

Comparing the internal SLOPE waveform with the ERROR AMP output voltage, PWM COMP controls the pulse width and outputs to the driver.

Max Duties of ch1 and ch2 are set at 86%.

#### 7.SOFT START

Circuit for preventing in-rush current at the start of DC/DC converter by bringing the output voltage.

Soft-start time is in synch with the internal OSC, and the output voltage of the DC/DC converter reaches the set voltage after about 4.2m sec.

#### 8.OCP

Circuit for preventing malfunction at over current.

Under input current over electrical characteristics, it supply minimum duty to DC/DC converter and IC stop safety by SCP detected.

#### 9.TSD

Circuit for preventing malfunction at high Temperature .

When it detects an abnormal temperature exceeding Maximum Junction Temperature (Tj=150°C), it turns OFF all Output FET, and turns OFF DC/DC Comparator Output.

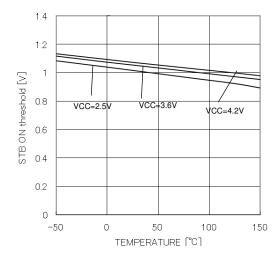

#### 10. ON/OFF

Voltage applied on STB pin to control ON/OFF channel of each channel.

Turned ON when a voltage of 1.5 V or higher is applied and turned OFF when the terminal is open or 0 V is applied. Incorporates approximately 800 k $\Omega$  pull-down resistance.

## ● Absolute maximum ratings(T=25°C)

| Parameter                    | Symbol    | Rating             | Unit |

|------------------------------|-----------|--------------------|------|

|                              | VDD       | <b>−0.3~7</b>      | V    |

| Maximum power supply voltage | STB1,STB2 | <b>−0.3~7</b>      | V    |

|                              | IHS2L     | 1.0                | Α    |

| Maximum input current        | ILX1      | 1.0                | Α    |

|                              | ILX2      | 1.0                | Α    |

|                              | VDD-LX1   | 15                 | V    |

|                              | LX2       | 22                 | V    |

| Maximum input voltage        | NON1      | <b>-0.3∼7</b>      | V    |

|                              | INV2      | <b>-0.3∼7</b>      | V    |

|                              | DIS1      | -9 <b>~</b> 0.3    | V    |

| Power dissipation            | Pd        | 730                | mW   |

| Operating temperature range  | Topr      | <del>-35~+85</del> | °C   |

| Storage temperature range    | Tstg      | <b>−55~+150</b>    | °C   |

| Junction temperature         | Tjmax     | +150               | °C   |

<sup>((\*1)</sup> When mounted on 74.2 × 74.2 × 1.6mm and operated over 25°C Pd reduces by 4.96mW/°C.

## Recommended operating conditions

| Parameter               | Cymahal | Standard value |     |      | Units   |

|-------------------------|---------|----------------|-----|------|---------|

| Parameter               | Symbol  | MIN            | TYP | MAX  | UIII LS |

| Power supply voltage    | VDD     | 2.5            | _   | 5.5  | V       |

| Inverted output voltage | V01     | -9.0           | _   | -1.0 | V       |

| Step up output voltage  | VO2     | VCC            | -   | 18   | V       |

## ●Electrical characteristics(Ta=25°C, VDD=3.6V)

| Parameter                        |                 | 0 1 1          | Standard value |       | 11    | O and this are |                                                     |

|----------------------------------|-----------------|----------------|----------------|-------|-------|----------------|-----------------------------------------------------|

|                                  |                 | Symbol         | MIN            | TYP   | MAX   | Unit           | Conditions                                          |

| [Low voltage input m             | alfunction prev | enting circuit | ]              |       |       |                |                                                     |

| Detect threshold voltage         |                 | Vuv            | _              | 2.2   | 2.35  | V              | VDD sweep down                                      |

| Hysteresis voltage               |                 | ∆ Vu∨hy        | 50             | 100   | 150   | mV             |                                                     |

| [Oscillator]                     |                 |                |                |       |       |                |                                                     |

| Oscillating frequency            |                 | Fosc           | 0.72           | 0.8   | 0.88  | MHz            |                                                     |

| LX1 Max Duty                     |                 | Dmax1          | 82             | 86    | 90    | %              |                                                     |

| LX2 Max Duty                     |                 | Dmax2          | 82             | 86    | 90    | %              |                                                     |

| 【Error AMP, VREF】                |                 |                |                |       |       |                |                                                     |

| CH1output voltage                |                 | V01            | -5.06          | -5.00 | -4.94 | V              | NON1 feedback resistance $20k\Omega$ , $100k\Omega$ |

| VREF line regulation             |                 | DVLi           | _              | 4.0   | 12.5  | mV             | VDD=2.5∼5.5V                                        |

| INV threshold voltage            | ;               | VINV           | 0.792          | 0.800 | 0.808 | V              |                                                     |

| NON1 input bias curr             | ent             | INON1          | -50            | 0     | 50    | nA             | STB1=3.6V, NON1=-0.2V                               |

| INV2 input bias curre            | nt              | IINV2          | -50            | 0     | 50    | nA             | INV2=1.2V                                           |

| CH1 Soft start time              |                 | TSS1           | 3.7            | 4.2   | 4.7   | ms             |                                                     |

| CH2 Soft start time              |                 | TSS2           | 3.7            | 4.2   | 4.7   | ms             |                                                     |

| 【Internal FET】                   |                 |                |                |       |       |                |                                                     |

| LX1 PMOS ON resistance           |                 | Ron1p          | _              | 230   | 480   | mΩ             |                                                     |

| DIS1discharge resista            | ance            | RDIS1          | _              | 100   | 160   | Ω              | VSTB1=0V, IDIS1=-1mA                                |

| NON1 discharge resis             | stance          | Rnon1          | -              | 150   | 240   | Ω              | VSTB1=0V, INON1=1mA                                 |

| LX2HighsideSW ON resistance      |                 | Ron2p          | _              | 130   | 220   | mΩ             |                                                     |

| LX2 NMOS ON resist               | ance            | Ron2n          | _              | 230   | 480   | mΩ             |                                                     |

| LX1 OCP threshold                |                 | Iocp1          | 1.2            | 2.4   | -     | Α              |                                                     |

| LX2 OCP threshold                |                 | Iocp2          | 1.2            | 2.4   | _     | Α              |                                                     |

| HS2L leak current                |                 | IleakH1        | -1             | 0     | 1     | uA             |                                                     |

| LX1 leak current                 |                 | I leak1        | -1             | 0     | 1     | uA             |                                                     |

| LX2 leak current                 |                 | I leak2        | -1             | 0     | 1     | uA             |                                                     |

| [STB]                            |                 |                |                |       |       |                |                                                     |

| STB pin                          | Active          | VsтвН          | 1.5            | _     | 5.5   | V              |                                                     |

| Control voltage                  | Non-active      | VstBL          | -0.3           | _     | 0.3   | V              |                                                     |

| STB pin pull down resistance     |                 | Rstb1          | 500            | 800   | 1400  | kΩ             |                                                     |

| 【Circuit current】                |                 |                |                |       |       |                |                                                     |

| Standby current                  |                 | <b>I</b> STB   | -              | _     | 1     | uA             |                                                     |

| Circuit current of operation VDD |                 | IDD            | _              | 500   | 650   | uA             | STB1=STB2=3.6V<br>NON1=-0.2V, INV2=1.2V             |

<sup>©</sup>This product is not designed for normal operation within a radioactive environment.

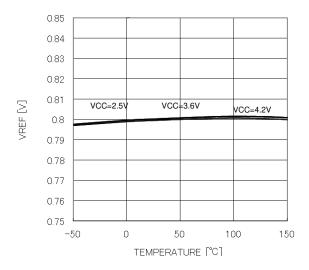

## ■Reference data

(unless otherwise specified Ta=25°C, VCC=3.6V)

Figure 4. VREF vs temp

Figure 5. INV2 threshold vs temp

Figure 6. Oscillation frequency vs temp

Figure 7. UVLO detect threshold Vs temp

Figure 8. STB ON threshold voltage vs temp

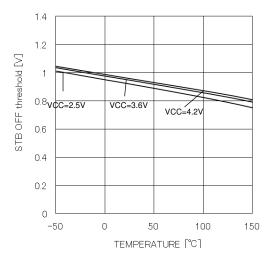

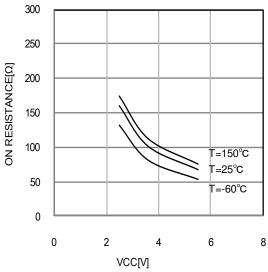

Figure 10. LX1 high side FET ON registance vs VCC

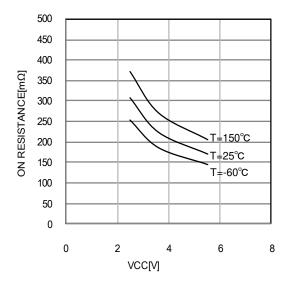

Figure 9. STB OFF threshold voltage vs temp

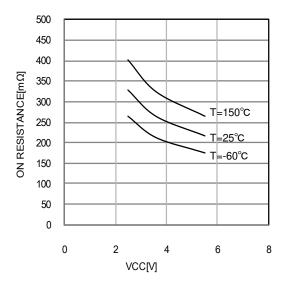

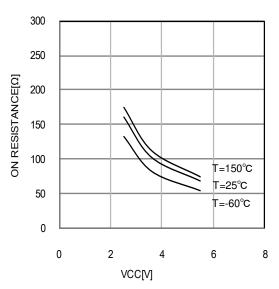

Figure 11. LX2 high side FET ON registance vs VCC

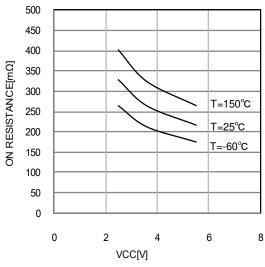

Figure 12. HS2L high side FET ON registance vs VCC

Figure 13. DIS1 discharge SW ON registance vs VCC

Figure 14. NON1 discharge SW ON registance vs VCC

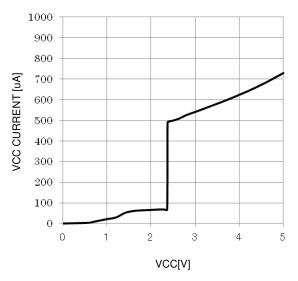

Figure 15. VCC input current vs VCC (STB ON)

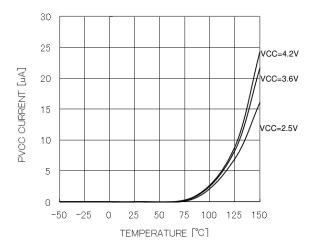

Figure 16. VCC input current vs Temp (STB OFF)

●Example of Application1 Input: 2.5 to 5.5 V, ch1 output: -5.0 V / 100m A(MAX), ch2 output:5.0V/100mA(MAX)

Figure 17. Example of Application1

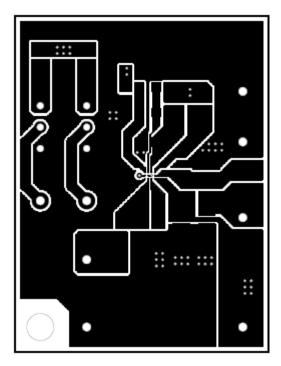

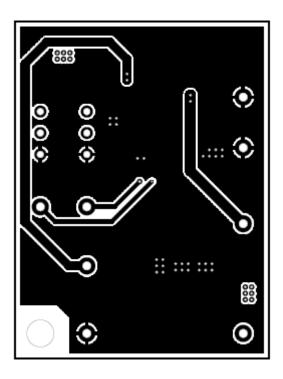

●Example of Board Layout ROHM SMD Evaluation Board

Figure 18. Assembly Layer

Figure 19. Bottom Layer

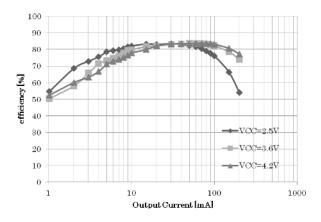

■Typical Performance Characteristic (Unless otherwise specified, Ta = 25°C, VCC = 3.6V)

(Example of application 1)

100 90 80 70 efficiency[%] 60 50 40 30 20 10 0 10 100 1000 Output current [mA]

Figure 20. CH1 Power conversion efficiency vs output current

Figure 21. CH2 Power conversion efficiency vs output current

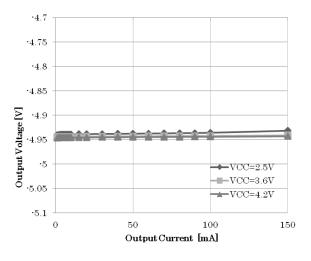

Figure 22. CH1 Output voltage vs Output Current

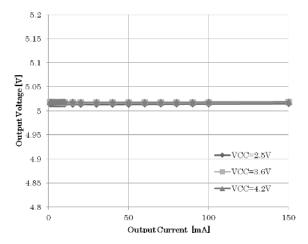

Figure 23. CH2 Output voltage vs Output Current

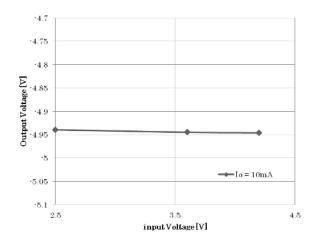

Figure 24. CH1 Output voltage vs Input voltage

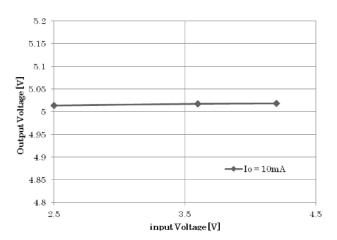

Figure 25. CH2 Output voltage vs Input voltage

Figure 26. CH1 Output current response (output current : 10mA ⇔ 100mA)

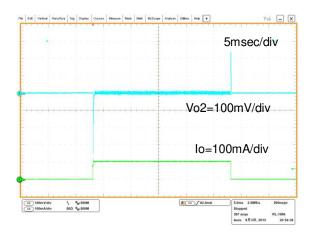

Figure 27. CH2 Output current response (output current : 10mA ⇔ 100mA)

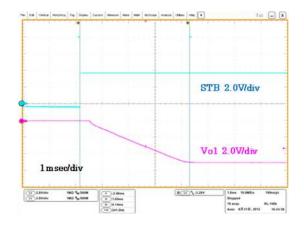

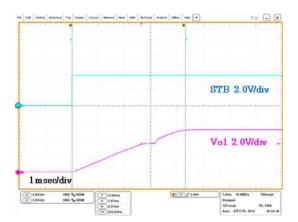

Figure 28. CH1 Soft start waveform

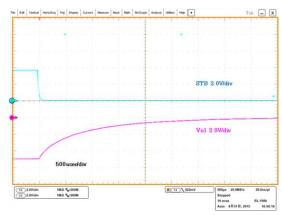

Figure 30. CH1 Discharge waveform [500usec/div]

Figure 29. CH2 Soft start waveform

#### Selection of Parts for Applications

#### (1)Output inductor

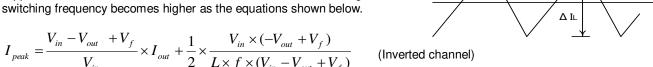

A shielded inductor that satisfies the current rating (current value, Ipeak as shown in the drawing below) and has a low DCR (direct current resistance component) is recommended.

Inductor values affect output ripple current greatly.

Ripple current can be reduced as the inductor L value becomes larger and the switching frequency becomes higher as the equations shown below.

Fig.ure 31. Ripple current

$$I_{\textit{peak}} = \frac{I_{\textit{out}} \times V_{\textit{out}}}{V_{\textit{in}} \times \eta} + \frac{1}{2} \times \frac{V_{\textit{in}} \times (V_{\textit{out}} - V_{\textit{in}})}{L \times f \times V_{\textit{out}}} \tag{Boost channel}$$

η: Efficiency(<0.92), f: Switching frequency(1.6MHz), L: inductance,

The second terms of equations above are ripple current of the inductor(∠IL of Fig.32) which should be set at about 20 to 50% of the maximum output current.

\* Current over the inductor rating flowing in the inductor brings the inductor into magnetic saturation, which may lead to lower efficiency or output bad oscillation. Select an inductor with an adequate margin so that the peak current does not exceed the rated current of the inductor.

#### (2) Output capacitor

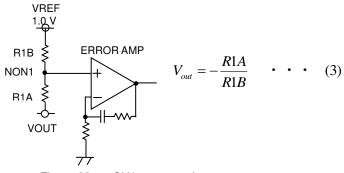

CH1

The reference voltage of CH1 is 1.0V and the internal reference voltage of the ERROR AMP is 0 V. Output voltage should be obtained by referring to Equation (3) of Fig.33.

Figure 32. CH1output setting

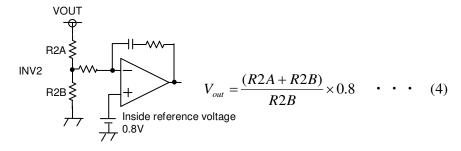

CH2

The internal reference voltage of the ERROR AMP is 0.8 V. Output voltage should be obtained by referring to Equation (4) of Fig.34.

Figure 33 CH2 output setting

### (3) Output capacitor

A ceramic capacitor with low ESR is recommended for output in order to reduce output ripple.

There must be an adequate margin between the maximum rating and output voltage of the capacitor, taking the DC bias

property into consideration.

Output ripple voltage when ceramic capacitor is used is obtained by the following equation.

$$Vpp = \angle IL \times \frac{I}{2 \pi \times f \times Co} + \angle IL \times R_{ESR} \quad [V]$$

Co is set within the range of 1~20uF.

Setting must be performed so that output ripple is within the allowable ripple voltage.

## ●I/O Equivalence Circuit

Figure 34. I/O Equivalence Circuit

#### Operation Notes

#### 1.) Absolute maximum ratings

This produced with strict quality control. However, the IC may be destroyed if operated beyond its absolute maximum ratings. If the device is destroyed by exceeding the recommended maximum ratings, the failure mode will be difficult to determine. (E.g. short mode, open mode) Therefore, physical protection counter-measures (like fuse) should be implemented when operating conditions beyond the absolute maximum ratings anticipated.

#### 2.) GND potential

Make sure GND is connected at lowest potential.

#### 3.) Setting of heat

Make sure that power dissipation does not exceed maximum ratings.

#### 4.) Pin short and mistake fitting

Avoid placing the IC near hot part of the PCB. This may cause damage to IC. Also make sure that the output-to-output and output to GND condition will not happen because this may damage the IC.

#### 5.) Actions in strong magnetic field

Exposing the IC within a strong magnetic field area may cause malfunction.

#### 6.) Mutual impedance

Use short and wide wiring tracks for the main supply and ground to keep the mutual impedance as small as possible. Use inductor and capacitor network to keep the ripple voltage minimum.

#### 7.) Thermal shutdown circuit (TSD circuit)

The IC incorporates a built-in thermal shutdown circuit (TSD circuit). The thermal shutdown circuit (TSD circuit) is designed only to shut the IC off to prevent runaway thermal operation. It is not designed to protect the IC or guarantee its operation. Do not continue to use the IC after operating this circuit or use the IC in an environment where the operation of this circuit is assumed.

#### 8.)Rush current at the time of power supply injection.

An IC which has plural power supplies, or CMOS IC could have momentaly rush current at the time of power supply injection. Because there exists inside logic uncertainty state. Please take care about power supply coupling capacity and width of power Supply and GND pattern wiring.

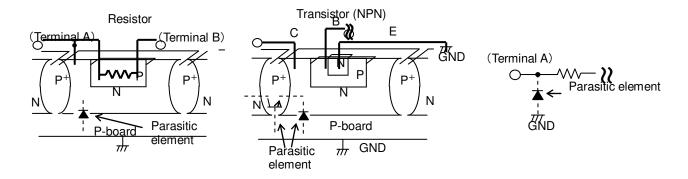

#### 9.)IC Terminal Input

This IC is a monolithic IC that has a P- board and P+ isolation for the purpose of keeping distance between elements. A P-N junction is formed between the P-layer and the N-layer of each element, and various types of parasitic elements are then formed. For example, an application where a resistor and a transistor are connected to a terminal (shown in Fig.36):

OWhen GND > (terminal A) at the resistor and GND > (terminal B) at the transistor (NPN), the P-N junction operates as a parasitic diode.

OWhen GND > (terminal B) at the transistor (NPN), a parasitic NPN transistor operates as a result of the NHayers of other elements in the proximity of the aforementioned parasitic diode.

Parasitic elements are structurally inevitable in the IC due to electric potential relationships. The operation of parasitic elements Induces the interference of circuit operations, causing malfunctions and possibly the destruction of the IC. Please be careful not to use the IC in a way that would cause parasitic elements to operate. For example, by applying a voltage that is lower than the GND (P-board) to the input terminal.

Figure 35. Simplified structure of a Bipolar IC

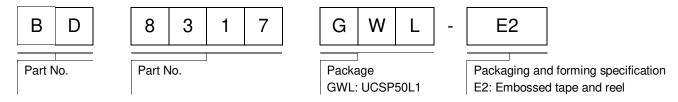

#### Ordering part number

## External information

## UCSP50L1 (BD8317GWL)

## **Notice**

## **Precaution on using ROHM Products**

1. Our Products are designed and manufactured for application in ordinary electronic equipments (such as AV equipment, OA equipment, telecommunication equipment, home electronic appliances, amusement equipment, etc.). If you intend to use our Products in devices requiring extremely high reliability (such as medical equipment (Note 1), transport equipment, traffic equipment, aircraft/spacecraft, nuclear power controllers, fuel controllers, car equipment including car accessories, safety devices, etc.) and whose malfunction or failure may cause loss of human life, bodily injury or serious damage to property ("Specific Applications"), please consult with the ROHM sales representative in advance. Unless otherwise agreed in writing by ROHM in advance, ROHM shall not be in any way responsible or liable for any damages, expenses or losses incurred by you or third parties arising from the use of any ROHM's Products for Specific Applications.

(Note1) Medical Equipment Classification of the Specific Applications

| JAPAN   | USA      | EU         | CHINA    |  |

|---------|----------|------------|----------|--|

| CLASSⅢ  | CLACCIII | CLASS II b | CL ACCTI |  |

| CLASSIV | CLASSII  | CLASSⅢ     | CLASSⅢ   |  |

- 2. ROHM designs and manufactures its Products subject to strict quality control system. However, semiconductor products can fail or malfunction at a certain rate. Please be sure to implement, at your own responsibilities, adequate safety measures including but not limited to fail-safe design against the physical injury, damage to any property, which a failure or malfunction of our Products may cause. The following are examples of safety measures:

- [a] Installation of protection circuits or other protective devices to improve system safety

- [b] Installation of redundant circuits to reduce the impact of single or multiple circuit failure

- 3. Our Products are designed and manufactured for use under standard conditions and not under any special or extraordinary environments or conditions, as exemplified below. Accordingly, ROHM shall not be in any way responsible or liable for any damages, expenses or losses arising from the use of any ROHM's Products under any special or extraordinary environments or conditions. If you intend to use our Products under any special or extraordinary environments or conditions (as exemplified below), your independent verification and confirmation of product performance, reliability, etc, prior to use, must be necessary:

- [a] Use of our Products in any types of liquid, including water, oils, chemicals, and organic solvents

- [b] Use of our Products outdoors or in places where the Products are exposed to direct sunlight or dust

- [c] Use of our Products in places where the Products are exposed to sea wind or corrosive gases, including Cl<sub>2</sub>, H<sub>2</sub>S, NH<sub>3</sub>, SO<sub>2</sub>, and NO<sub>2</sub>

- [d] Use of our Products in places where the Products are exposed to static electricity or electromagnetic waves

- [e] Use of our Products in proximity to heat-producing components, plastic cords, or other flammable items

- [f] Sealing or coating our Products with resin or other coating materials

- [g] Use of our Products without cleaning residue of flux (even if you use no-clean type fluxes, cleaning residue of flux is recommended); or Washing our Products by using water or water-soluble cleaning agents for cleaning residue after soldering

- [h] Use of the Products in places subject to dew condensation

- 4. The Products are not subject to radiation-proof design.

- 5. Please verify and confirm characteristics of the final or mounted products in using the Products.

- 6. In particular, if a transient load (a large amount of load applied in a short period of time, such as pulse. is applied, confirmation of performance characteristics after on-board mounting is strongly recommended. Avoid applying power exceeding normal rated power; exceeding the power rating under steady-state loading condition may negatively affect product performance and reliability.

- 7. De-rate Power Dissipation (Pd) depending on Ambient temperature (Ta). When used in sealed area, confirm the actual ambient temperature.

- 8. Confirm that operation temperature is within the specified range described in the product specification.

- 9. ROHM shall not be in any way responsible or liable for failure induced under deviant condition from what is defined in this document.

## Precaution for Mounting / Circuit board design

- 1. When a highly active halogenous (chlorine, bromine, etc.) flux is used, the residue of flux may negatively affect product performance and reliability.

- 2. In principle, the reflow soldering method must be used on a surface-mount products, the flow soldering method must be used on a through hole mount products. If the flow soldering method is preferred on a surface-mount products, please consult with the ROHM representative in advance.

For details, please refer to ROHM Mounting specification

#### **Precautions Regarding Application Examples and External Circuits**

- 1. If change is made to the constant of an external circuit, please allow a sufficient margin considering variations of the characteristics of the Products and external components, including transient characteristics, as well as static characteristics.

- You agree that application notes, reference designs, and associated data and information contained in this document are presented only as guidance for Products use. Therefore, in case you use such information, you are solely responsible for it and you must exercise your own independent verification and judgment in the use of such information contained in this document. ROHM shall not be in any way responsible or liable for any damages, expenses or losses incurred by you or third parties arising from the use of such information.

#### **Precaution for Electrostatic**

This Product is electrostatic sensitive product, which may be damaged due to electrostatic discharge. Please take proper caution in your manufacturing process and storage so that voltage exceeding the Products maximum rating will not be applied to Products. Please take special care under dry condition (e.g. Grounding of human body / equipment / solder iron, isolation from charged objects, setting of lonizer, friction prevention and temperature / humidity control).

## **Precaution for Storage / Transportation**

- 1. Product performance and soldered connections may deteriorate if the Products are stored in the places where:

- [a] the Products are exposed to sea winds or corrosive gases, including Cl2, H2S, NH3, SO2, and NO2

- [b] the temperature or humidity exceeds those recommended by ROHM

- [c] the Products are exposed to direct sunshine or condensation

- [d] the Products are exposed to high Electrostatic

- Even under ROHM recommended storage condition, solderability of products out of recommended storage time period

may be degraded. It is strongly recommended to confirm solderability before using Products of which storage time is

exceeding the recommended storage time period.

- 3. Store / transport cartons in the correct direction, which is indicated on a carton with a symbol. Otherwise bent leads may occur due to excessive stress applied when dropping of a carton.

- 4. Use Products within the specified time after opening a humidity barrier bag. Baking is required before using Products of which storage time is exceeding the recommended storage time period.

#### **Precaution for Product Label**

QR code printed on ROHM Products label is for ROHM's internal use only.

#### **Precaution for Disposition**

When disposing Products please dispose them properly using an authorized industry waste company.

#### **Precaution for Foreign Exchange and Foreign Trade act**

Since concerned goods might be fallen under listed items of export control prescribed by Foreign exchange and Foreign trade act, please consult with ROHM in case of export.

#### **Precaution Regarding Intellectual Property Rights**

- 1. All information and data including but not limited to application example contained in this document is for reference only. ROHM does not warrant that foregoing information or data will not infringe any intellectual property rights or any other rights of any third party regarding such information or data.

- 2. ROHM shall not have any obligations where the claims, actions or demands arising from the combination of the Products with other articles such as components, circuits, systems or external equipment (including software).

- 3. No license, expressly or implied, is granted hereby under any intellectual property rights or other rights of ROHM or any third parties with respect to the Products or the information contained in this document. Provided, however, that ROHM will not assert its intellectual property rights or other rights against you or your customers to the extent necessary to manufacture or sell products containing the Products, subject to the terms and conditions herein.

#### **Other Precaution**

- 1. This document may not be reprinted or reproduced, in whole or in part, without prior written consent of ROHM.

- 2. The Products may not be disassembled, converted, modified, reproduced or otherwise changed without prior written consent of ROHM.

- In no event shall you use in any way whatsoever the Products and the related technical information contained in the Products or this document for any military purposes, including but not limited to, the development of mass-destruction weapons.

- 4. The proper names of companies or products described in this document are trademarks or registered trademarks of ROHM, its affiliated companies or third parties.

Notice-PGA-E Rev.001

#### **General Precaution**

- 1. Before you use our Products, you are requested to care fully read this document and fully understand its contents. ROHM shall not be in an y way responsible or liable for failure, malfunction or accident arising from the use of a ny ROHM's Products against warning, caution or note contained in this document.

- 2. All information contained in this docume nt is current as of the issuing date and subject to change without any prior notice. Before purchasing or using ROHM's Products, please confirm the latest information with a ROHM sale s representative.

- 3. The information contained in this doc ument is provided on an "as is" basis and ROHM does not warrant that all information contained in this document is accurate an d/or error-free. ROHM shall not be in an y way responsible or liable for any damages, expenses or losses incurred by you or third parties resulting from inaccuracy or errors of or concerning such information.

**Notice – WE** © 2015 ROHM Co., Ltd. All rights reserved. Rev.001