# Low-Noise, 900kHz, RRIO, Precision OPERATIONAL AMPLIFIER Zerø-Drift Series

Check for Samples: OPA378 OPA2378

#### **FEATURES**

- LOW NOISE

- 0.4 $\mu$ V<sub>PP</sub>, 0.1Hz to 10Hz

- 20nV/√Hz at 1kHz

- ZERØ-DRIFT SERIES

- LOW OFFSET VOLTAGE: 20μV

- LOW OFFSET DRIFT: 0.1µV/°C

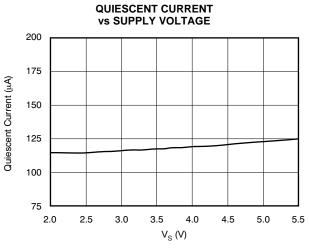

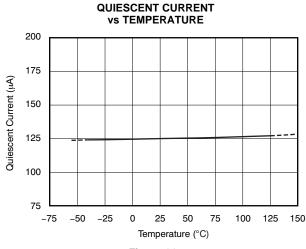

- QUIESCENT CURRENT: 125µA

- GAIN BANDWIDTH: 900kHz

- RAIL-TO-RAIL INPUT/OUTPUT

- EMI FILTERING

- SUPPLY VOLTAGE: 2.2V to 5.5V

- microSIZE PACKAGES: SC70 and SOT23

#### **APPLICATIONS**

- PORTABLE MEDICAL DEVICES

- GLUCOSE METERS

- OXYGEN METERING

- HEART RATE MONITORS

- WEIGH SCALES

- BATTERY-POWERED INSTRUMENTS

- THERMOPILE MODULES

- HANDHELD TEST EQUIPMENT

- SENSOR SIGNAL CONDITIONING

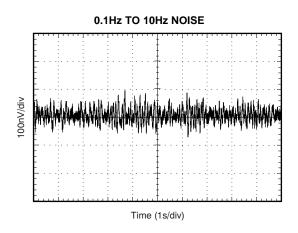

# O.1Hz TO 10Hz NOISE

#### **DESCRIPTION**

The OPA378 and OPA2378 represent a new generation of Zerø-Drift, microPOWER™ operational amplifiers that use a proprietary auto-calibration technique to provide minimal input offset voltage (20μV) and offset voltage drift (0.1μV/°C). The combination of low input voltage noise, high gain bandwidth (900kHz), and low power (150µA max) enable these devices achieve to performance for low-power precision applications. In addition, the excellent PSRR performance, coupled with a wide input supply range of 2.2V to 5.5V and rail-to-rail input and output, makes it an outstanding choice for single-supply applications that run directly from batteries without regulation.

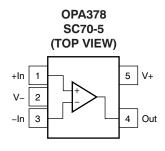

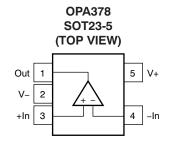

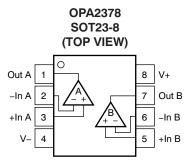

The OPA378 (single version) is available in both a *microSIZE* SC70-5 and a SOT23-5 package. The OPA2378 (dual version) is offered in a SOT23-8 package. All versions are specified for operation from -40°C to +125°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

microPOWER is a trademark of Texas Instruments Incorporated. All other trademarks are the property of their respective owners.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### PACKAGE INFORMATION(1)

| PRODUCT | PACKAGE-LEAD | PACKAGE DESIGNATOR | PACKAGE MARKING |

|---------|--------------|--------------------|-----------------|

| OPA378  | SOT23-5      | DBV                | OAZI            |

| OPA378  | SC70-5       | DCK                | BTS             |

| OPA2378 | SOT23-8      | DCN                | OCAI            |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

#### ABSOLUTE MAXIMUM RATINGS(1)

Over operating free-air temperature range (unless otherwise noted).

|                                       |                            | OPA378, OPA2378                        | UNIT |  |  |  |

|---------------------------------------|----------------------------|----------------------------------------|------|--|--|--|

| Supply Voltage, $V_S = (V+) - (V-)$   |                            | +7                                     | V    |  |  |  |

| Signal Innut Tarminala                | Voltage <sup>(2)</sup>     | $(V-) - 0.3 \le V_{IN} \le (V+) + 0.3$ | V    |  |  |  |

| Signal Input Terminals                | Current <sup>(2)</sup>     | ±10                                    | mA   |  |  |  |

| Output Short-Circuit (3)              |                            | Continuous                             |      |  |  |  |

| Operating Temperature, T <sub>A</sub> |                            | -55 to +150                            | °C   |  |  |  |

| Storage Temperature, T <sub>A</sub>   |                            | -65 to +150                            | °C   |  |  |  |

| Junction Temperature, T <sub>J</sub>  |                            | +150                                   | °C   |  |  |  |

|                                       | Human Body Model (HBM)     | 4000                                   | V    |  |  |  |

| ESD Ratings                           | Charged Device Model (CDM) | 1000                                   | V    |  |  |  |

|                                       | Machine Model (MM)         | 200                                    | V    |  |  |  |

- (1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not supported.

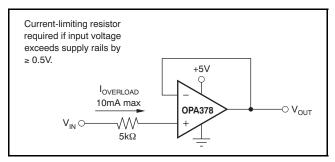

- (2) Input terminals are diode-clamped to the power-supply rails. Input signals that can swing more than 0.3V beyond the supply rails should be current limited to 10mA or less.

- (3) Short-circuit to ground, one amplifier per package.

#### **PIN CONFIGURATIONS**

# ELECTRICAL CHARACTERISTICS: $V_S = +2.2V$ to +5.5V

**Boldface** limits apply over the specified temperature range,  $T_A = -40^{\circ}C$  to +125°C. At  $T_A = +25^{\circ}C$ ,  $R_L = 10k\Omega$  connected to  $V_S/2$ ,  $V_{CM} = V_S/2$ , and  $V_{OUT} = V_S/2$ , unless otherwise noted.

|                                                 |                      |                                                                                                                | OP          | A378, OPA2 | 378, OPA2378 |                    |  |

|-------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------|-------------|------------|--------------|--------------------|--|

| PARAMETER                                       |                      | TEST CONDITIONS                                                                                                | MIN         | TYP        | MAX          | UNIT               |  |

| OFFSET VOLTAGE                                  |                      |                                                                                                                |             |            |              |                    |  |

| Input Offset Voltage, OPA378                    | $V_{OS}$             | $V_{CM} = V -$                                                                                                 |             | 20         | 50           | μV                 |  |

| vs Temperature                                  | dV <sub>OS</sub> /dT |                                                                                                                |             | 0.1        | 0.25         | μV/°C              |  |

| Input Offset Voltage, OPA2378                   |                      |                                                                                                                |             | 20         | 70           | μV                 |  |

| vs Temperature dV <sub>OS</sub> /d <sup>T</sup> |                      | -40°C to +125°C                                                                                                |             | 0.25       | 0.4          | μV/°C              |  |

|                                                 |                      | -40°C to +85°C                                                                                                 |             | 0.15       | 0.25         | μV/°C              |  |

| vs Power Supply, OPA378                         | PSRR                 | $V_{CM} = 0V$ , $V_{S} = +2.2V$ to $+5.5V$                                                                     |             | 1.5        | 5            | μV/V               |  |

| over Temperature                                |                      | $V_{CM} = 0V, V_{S} = +2.2V \text{ to } +5.5V$                                                                 |             | 3          | 8            | μV/V               |  |

| vs Power Supply, OPA2378                        |                      | $V_{CM} = 0V$ , $V_{S} = +2.2V$ to $+5.5V$                                                                     |             |            | 10           | μV/V               |  |

| over Temperature                                |                      | $V_{CM} = 0V, V_{S} = +2.2V \text{ to } +5.5V$                                                                 |             | 3          | 13           | μV/V               |  |

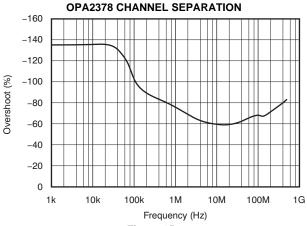

| Channel Separation (Dual Version)               |                      | At dc                                                                                                          |             | 135        |              | dB                 |  |

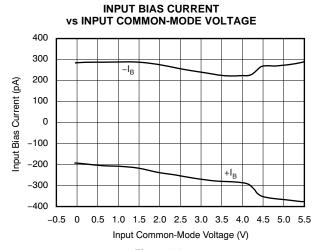

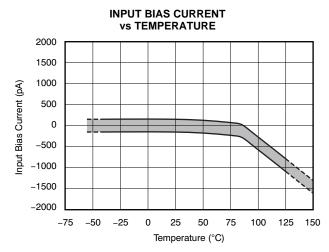

| INPUT BIAS CURRENT                              |                      |                                                                                                                |             |            |              |                    |  |

| Input Bias Current, OPA378                      | $I_{B}$              |                                                                                                                |             | ±150       | ±550         | pA                 |  |

| Input Bias Current, OPA2378                     |                      |                                                                                                                |             | ±150       | ±670         | pA                 |  |

| over Temperature, OPA378 and 0                  | OPA2378              |                                                                                                                |             |            | ±2           | nA                 |  |

| Input Offset Current, OPA378                    | Ios                  |                                                                                                                |             | ±0.3       | ±1.1         | nA                 |  |

| Input Offset Current, OPA2378                   |                      |                                                                                                                |             | ±0.3       | ±1.34        | nA                 |  |

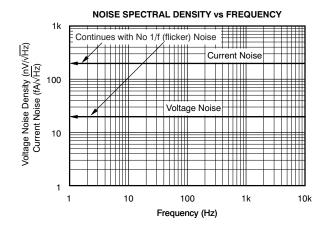

| NOISE                                           |                      |                                                                                                                |             |            |              |                    |  |

| Input Voltage Noise                             | $\mathbf{e}_{n}$     | $f = 0.1Hz$ to 10Hz, $V_S = +5.5V$                                                                             |             | 0.4        |              | $\mu V_{PP}$       |  |

| Input Voltage Noise Density                     | $e_{n}$              | f = 1kHz                                                                                                       |             | 20         |              | nV/√ <del>Hz</del> |  |

| Input Current Noise                             | $i_n$                | f = 10Hz                                                                                                       |             | 200        |              | fA/√Hz             |  |

| INPUT VOLTAGE RANGE                             |                      |                                                                                                                |             |            |              |                    |  |

| Common-Mode Voltage Range                       | $V_{CM}$             |                                                                                                                | (V-) - 0.05 |            | (V+) + 0.05  | V                  |  |

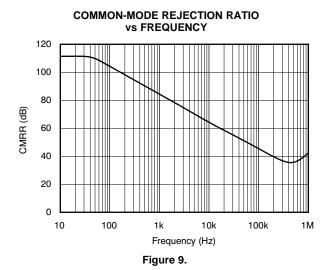

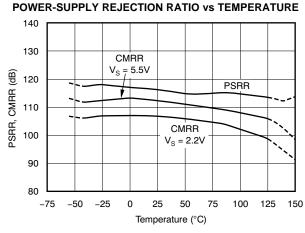

| Common-Mode Rejection Ratio                     | CMRR                 | $(V-) - 0.05V < V_{CM} < (V+) + 0.05V, V_{S} = 5.5V$                                                           | 100         | 112        |              | dB                 |  |

|                                                 |                      | $(V-) - 0.05V < V_{CM} < (V+) + 0.05V, V_S = 2.2V$                                                             | 94          | 106        |              | dB                 |  |

| over Temperature                                |                      | $(V-) - 0.05V < V_{CM} < (V+) + 0.05V, V_S = 5.5V$                                                             | 96          |            |              | dB                 |  |

|                                                 |                      | $(V-) - 0.05V < V_{CM} < (V+) + 0.05V, V_S = 2.2V$                                                             | 90          |            |              | dB                 |  |

| INPUT CAPACITANCE                               |                      |                                                                                                                |             |            |              |                    |  |

| Differential                                    | $C_{IN}$             |                                                                                                                |             | 4          |              | pF                 |  |

| Common-Mode                                     |                      |                                                                                                                |             | 5          |              | pF                 |  |

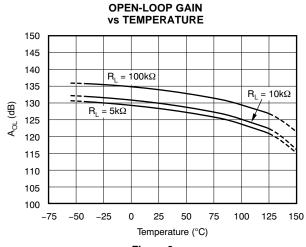

| OPEN-LOOP GAIN                                  |                      |                                                                                                                |             |            |              |                    |  |

| Open-Loop Voltage Gain                          | $A_{OL}$             | $50 \text{mV} < \text{V}_{\text{O}} < (\text{V+}) - 50 \text{mV}, \ \text{R}_{\text{L}} = 100 \text{k}\Omega$  | 110         | 134        |              | dB                 |  |

|                                                 |                      | $100 \text{mV} < \text{V}_{\text{O}} < (\text{V+}) - 100 \text{mV}, \ \text{R}_{\text{L}} = 10 \text{k}\Omega$ | 110         | 130        |              | dB                 |  |

| over Temperature                                |                      | $100 \text{mV} < \text{V}_{\text{O}} < (\text{V+}) - 100 \text{mV},  \text{R}_{\text{L}} = 10 \text{k}\Omega$  | 106         |            |              | dB                 |  |

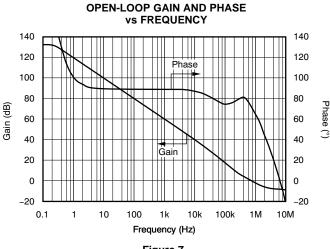

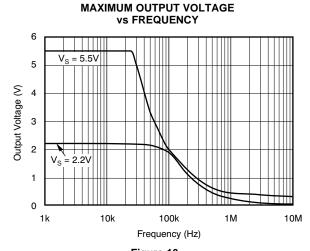

| FREQUENCY RESPONSE                              |                      |                                                                                                                |             |            |              |                    |  |

| Gain-Bandwidth Product                          | GBW                  |                                                                                                                |             | 900        |              | kHz                |  |

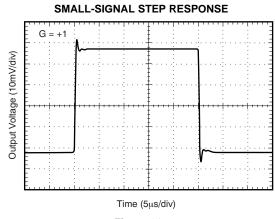

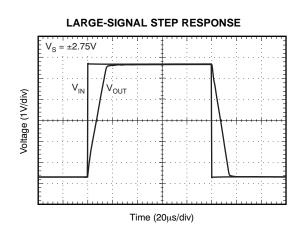

| Slew Rate                                       | SR                   | G = +1                                                                                                         |             | 0.4        |              | V/µs               |  |

| Settling Time 0.1%                              | $t_{S}$              | $V_S = 5.5V$ , 2V Step, $G = +1$                                                                               |             | 7          |              | μs                 |  |

| Settling Time 0.01%                             | t <sub>S</sub>       | $V_S = 5.5V$ , 2V Step, $G = +1$                                                                               |             | 9          |              | μs                 |  |

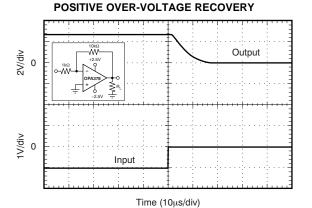

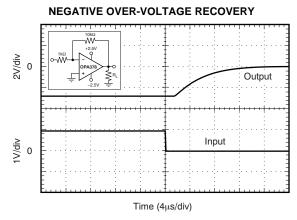

| Overload Recovery Time                          |                      | $V_{IN} \times Gain > V_{S}$                                                                                   |             | 4          |              | μs                 |  |

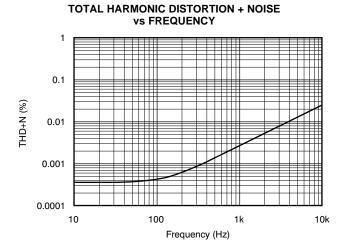

| THD + Noise                                     | THD + N              | $V_S = 5V$ , $V_O = 3V_{PP}$ , $G = +1$ , $f = 1kHz$                                                           |             | 0.003      |              | %                  |  |

# ELECTRICAL CHARACTERISTICS: $V_s = +2.2V$ to +5.5V (continued)

**Boldface** limits apply over the specified temperature range,  $T_A = -40^{\circ}C$  to +125°C. At  $T_A = +25^{\circ}C$ ,  $R_L = 10k\Omega$  connected to  $V_S/2$ ,  $V_{CM} = V_S/2$ , and  $V_{OUT} = V_S/2$ , unless otherwise noted.

|                                            |                   |                                  | 0   | PA378, OPA23  | 78   |      |

|--------------------------------------------|-------------------|----------------------------------|-----|---------------|------|------|

| PARAMETER                                  |                   | TEST CONDITIONS                  | MIN | TYP           | MAX  | UNIT |

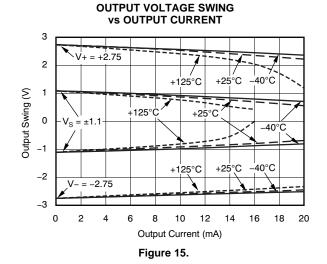

| OUTPUT                                     |                   |                                  |     |               |      |      |

| Voltage Output Swing from Rail, OPA378     | Vo                | $R_L = 10k\Omega$                |     | 6             | 8    | mV   |

| over Temperature                           |                   | $R_L = 10k\Omega$                |     | 8             | 13   | mV   |

| Voltage Output Swing from Rail,<br>OPA2378 | Vo                | $R_L = 10k\Omega$                |     | 6             | 10   | mV   |

| over Temperature                           |                   | $R_L = 10k\Omega$                |     | 8             | 15   | mV   |

| Voltage Output Swing from Rail             |                   | $R_L = 100k\Omega$               |     | 0.7           | 2    | mV   |

| over Temperature                           |                   | $R_L = 100k\Omega$               |     |               | 3    | mV   |

| Short-Circuit Current                      | I <sub>SC</sub>   |                                  |     | ±30           |      | mA   |

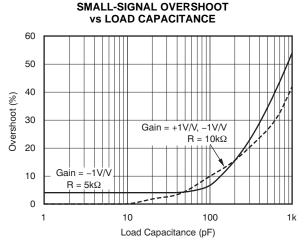

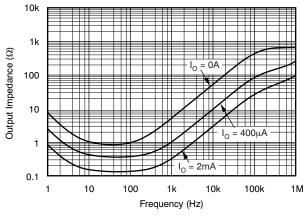

| Capacitive Load Drive                      | C <sub>LOAD</sub> |                                  |     | See Figure 18 | •    | pF   |

| Open-Loop Output Impedance                 | Z <sub>O</sub>    |                                  |     | See Figure 23 |      | Ω    |

| POWER SUPPLY                               |                   |                                  |     |               |      |      |

| Specified Voltage Range                    | Vs                |                                  | 2.2 |               | 5.5  | V    |

| Quiescent Current (per Amplifier)          | IQ                | $I_{O} = 0$ mA, $V_{S} = +5.5$ V |     | 125           | 150  | μΑ   |

| over Temperature                           |                   |                                  |     |               | 165  | μΑ   |

| TEMPERATURE RANGE                          |                   |                                  |     |               |      |      |

| Specified Range                            |                   |                                  | -40 |               | +125 | °C   |

| Operating Range                            |                   |                                  | -55 |               | +150 | °C   |

| Thermal Resistance                         | $\theta_{JA}$     |                                  |     |               |      | °C/W |

| SOT23-5                                    |                   |                                  |     | 200           |      | °C/W |

| SC70-5                                     |                   |                                  |     | 250           |      | °C/W |

| SOT23-8                                    |                   |                                  |     | 100           |      | °C/W |

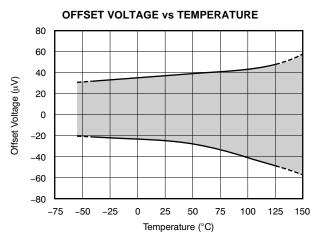

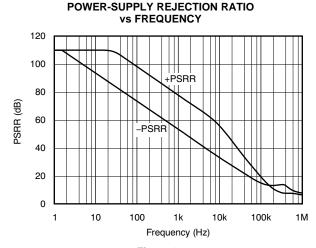

#### **TYPICAL CHARACTERISTICS**

At  $T_A$  = +25°C,  $R_L$  = 10k $\Omega$ ,  $V_S$  = +5.5V and  $V_{OUT}$  =  $V_S/2$ , unless otherwise noted.

#### Figure 1.

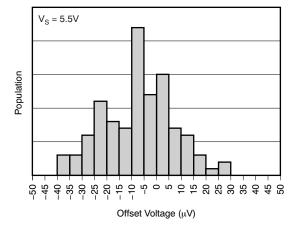

# OFFSET VOLTAGE PRODUCTION DISTRIBUTION

Figure 3.

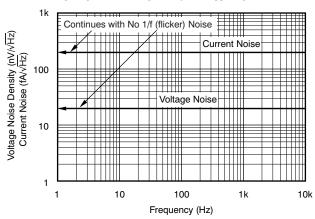

# INPUT CURRENT AND VOLTAGE NOISE SPECTRAL DENSITY vs FREQUENCY

Figure 2.

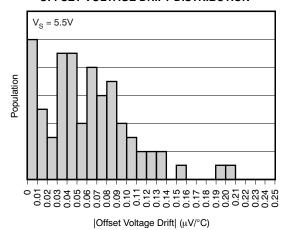

#### OFFSET VOLTAGE DRIFT DISTRIBUTION

Figure 4.

# TEXAS INSTRUMENTS

#### **TYPICAL CHARACTERISTICS (continued)**

At  $T_A$  = +25°C,  $R_L$  = 10k $\Omega$ ,  $V_S$  = +5.5V and  $V_{OUT}$  =  $V_S/2$ , unless otherwise noted.

Figure 5.

Figure 6.

Figure 7.

Figure 8.

**COMMON-MODE REJECTION RATIO AND**

Figure 10.

#### **TYPICAL CHARACTERISTICS (continued)**

At  $T_A$  = +25°C,  $R_L$  = 10k $\Omega$ ,  $V_S$  = +5.5V and  $V_{OUT}$  =  $V_S/2$ , unless otherwise noted.

Figure 11.

Figure 12.

Figure 13.

Figure 14.

Figure 16.

#### **TYPICAL CHARACTERISTICS (continued)**

At  $T_A$  = +25°C,  $R_L$  = 10k $\Omega$ ,  $V_S$  = +5.5V and  $V_{OUT}$  =  $V_S/2$ , unless otherwise noted.

Figure 17.

Figure 18.

Figure 19.

Figure 20.

Figure 21.

Figure 22.

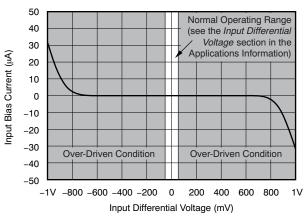

#### **TYPICAL CHARACTERISTICS (continued)**

At  $T_A$  = +25°C,  $R_L$  = 10k $\Omega$ ,  $V_S$  = +5.5V and  $V_{OUT}$  =  $V_S/2$ , unless otherwise noted.

#### **OPEN-LOOP OUTPUT IMPEDANCE vs FREQUENCY**

# INPUT BIAS CURRENT vs INPUT DIFFERENTIAL VOLTAGE

Figure 24.

Figure 25.

#### APPLICATIONS INFORMATION

The OPA378 and OPA2378 are unity-gain stable, precision operational amplifiers that are free from phase reversal. The use of proprietary Zerø-Drift circuitry gives the benefit of low input offset voltage over time and temperature as well as lowering the 1/f noise component. This design provides the optimization of gain, noise, and power, making the OPA378 series one of the best performers in this bandwidth range. As a result of the high PSRR, this device works well in applications that run directly from battery power without regulation. They are optimized for low-voltage, single-supply operation. These miniature, high-precision, low quiescent current amplifiers offer high-impedance inputs that have a common-mode range 100mV beyond the supplies, excellent CMRR, and a rail-to-rail output that swings within 10mV of the supplies. This design results in superior performance for driving analog-to-digital converters (ADCs) without degradation of differential linearity.

#### **OPERATING VOLTAGE**

The OPA378 and OPA2378 can be used with single or dual supplies from an operating range of  $V_S = +2.2V$  ( $\pm 1.1V$ ) and up to  $V_S = +5.5V$  ( $\pm 2.75V$ ). This device does not require symmetrical supplies, only a differential supply voltage of 2.2V to 5.5V. A power-supply rejection ratio of 1.5 $\mu$ V/V (typical) ensures that the device functions with an unregulated battery source. Supply voltages higher than +7V can permanently damage the device; see the Absolute Maximum Ratings table. Key parameters are assured over the specified temperature range,  $T_A = -40^{\circ}$ C to +125°C. Parameters that vary over the supply voltage or temperature range are shown in the Typical Characteristics section of this data sheet.

#### **INPUT VOLTAGE**

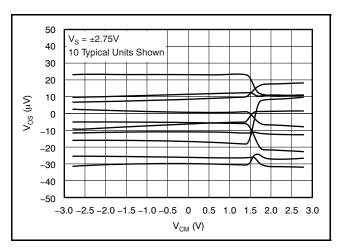

The OPA378 and OPA2378 input common-mode voltage range extends 0.05V beyond the supply rails. The OPA378 achieves a common-mode rejection ratio of 112dB (typical) over the common-mode voltage range. Figure 26 shows the variation of offset voltage over the entire specified common-mode range for 10 typical units.

Figure 26. Offset Voltage versus Common-Mode Voltage

Normally, input bias current is about 150pA; however, input voltages exceeding the power supplies can cause excessive current to flow into or out of the input pins. Momentary voltages greater than the power supply can be tolerated if the input current is limited to 10mA. This limitation is easily accomplished with an input resistor, as Figure 27 shows.

Figure 27. Input Current Protection

#### INPUT DIFFERENTIAL VOLTAGE

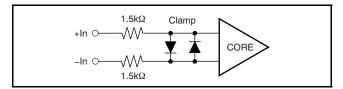

The typical input bias current of the OPA378 during normal operation is approximately 150pA. In over-driven conditions, the bias current can increase significantly (see Figure 24). The most common cause of an over-driven condition occurs when the op amp is outside of the linear range of operation. When the output of the op amp is driven to one of the supply rails the feedback loop requirements cannot be satisfied and a differential input voltage develops across the input pins. This differential input voltage results in activation of parasitic diodes inside the front end input chopping switches that combine with  $1.5 \mathrm{k}\Omega$  EMI filter resistors to create the equivalent circuit shown in Figure 28.

Figure 28. Equivalent Input Circuit

#### INTERNAL OFFSET CORRECTION

The OPA378 and OPA2378 family of op amps use an auto-calibration technique with a time-continuous 350kHz op amp in the signal path. This amplifier is zero-corrected every 3 $\mu$ s using a proprietary technique. Upon power-up, the amplifier requires approximately 100 $\mu$ s to achieve specified V<sub>OS</sub> accuracy. This architecture has no aliasing or flicker noise.

#### NOISE

The OPA378 series of op amps have excellent distortion characteristics. Total harmonic distortion + noise is below 0.003% (G = +1,  $V_O = 3V_{RMS}$ , and f = 1kHz, with a 10k $\Omega$  load). Design of low-noise op amp circuits requires careful consideration of a variety of possible noise contributors: noise from the signal source, noise generated in the op amp, and noise from the feedback network resistors. The total noise of the circuit is the root-sum-square combination of all the noise components.

#### **EMI SUSCEPTIBILITY AND INPUT FILTERING**

Operational amplifiers vary in their susceptibility to electromagnetic interference (EMI). If conducted EMI enters the operational amplifier, the dc offset observed at the amplifier output may shift from its nominal value while the EMI is present. This shift is a result of signal rectification associated with the internal semiconductor junctions. While all operational amplifier pin functions can be affected by EMI, the input pins are likely to be the most susceptible. The

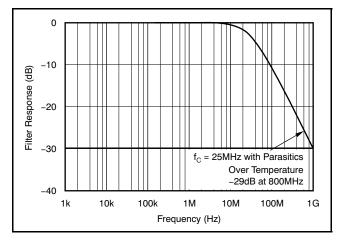

OPA378 operational amplifier family incorporates an internal input low-pass filter that reduces the amplifier response to EMI. Both common-mode and differential-mode filtering are provided by the input filter. The filter is designed for a cutoff frequency of approximately 25MHz (–3dB), with a roll-off of 20dB per decade. Figure 29 shows the EMI filter.

Figure 29. EMI Filter

#### **GENERAL LAYOUT GUIDELINES**

Attention to good layout practices is always recommended. Keep traces short and, when possible, use a printed circuit board (PCB) ground plane with surface-mount components placed as close to the device pins as possible. Place a 0.1µF capacitor closely across the supply pins. These guidelines should be applied throughout the analog circuit to improve performance.

For lowest offset voltage and precision performance, circuit layout and mechanical conditions should be optimized. Avoid temperature gradients that create thermoelectric (Seebeck) effects in the thermocouple junctions formed from connecting dissimilar conductors. These thermally-generated potentials can be made to cancel by assuring they are equal on both input terminals. Other layout and design considerations include:

- Use low thermoelectric-coefficient conditions (avoid dissimilar metals).

- Thermally isolate components from power supplies or other heat sources.

- Shield op amp and input circuitry from air currents, such as cooling fans.

Following these guidelines reduces the likelihood of junctions being at different temperatures, which can cause thermoelectric voltages of  $0.1\mu\text{V/°C}$  or higher, depending on materials used.

#### **ELECTRICAL OVERSTRESS**

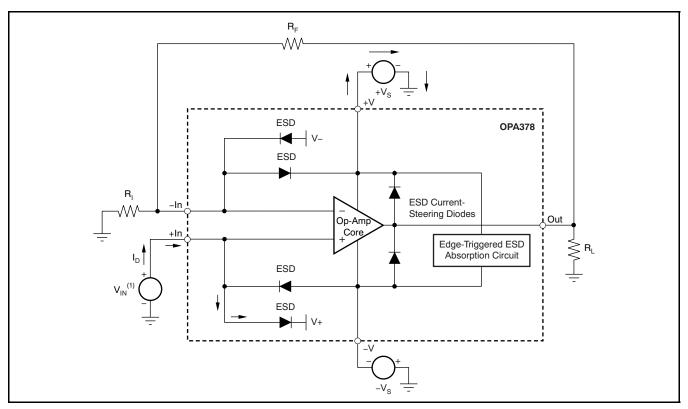

Designers often ask questions about the capability of an operational amplifier to withstand electrical overstress. These questions tend to focus on the device inputs, but may involve the supply voltage pins or even the output pin. Each of these different pin functions have electrical stress limits determined by the voltage breakdown characteristics of the particular semiconductor fabrication process and specific circuits connected to the pin. Additionally, internal electrostatic discharge (ESD) protection is built into these circuits to protect them from accidental ESD events both before and during product assembly.

It is helpful to have a good understanding of this basic ESD circuitry and its relevance to an electrical overstress event. Figure 30 shows the ESD circuits contained in the OPA378 (indicated by the dashed line area). The ESD protection circuitry involves several current-steering diodes connected from the input and output pins and routed back to the internal power-supply lines, where they meet at an absorption device internal to the operational amplifier. This protection circuitry is intended to remain inactive during normal circuit operation.

(1)  $V_{IN} = +V_S + 500$ mV.

Figure 30. Equivalent Internal ESD Circuitry and Its Relation to a Typical Circuit Application

An ESD event produces a short duration, high-voltage pulse that is transformed into a short duration, high-current pulse as it discharges through a semiconductor device. The ESD protection circuits are designed to provide a current path around the operational amplifier core to prevent it from being damaged. The energy absorbed by the protection circuitry is then dissipated as heat.

When an ESD voltage develops across two or more of the amplifier device pins, current flows through one or more of the steering diodes. Depending on the path that the current takes, the absorption device may activate. The absorption device has a trigger, or threshold voltage, that is above the normal operating voltage of the OPA378 but below the device breakdown voltage level. Once this threshold is exceeded, the absorption device quickly activates and clamps the voltage across the supply rails to a safe level.

When the operational amplifier connects into a circuit such as that illustrated in Figure 30, the ESD protection components are intended to remain inactive and not become involved in the application circuit operation. However, circumstances may arise where an applied voltage exceeds the operating voltage range of a given pin. Should this condition occur, there is a risk that some of the internal ESD protection circuits may be biased on, and conduct current. Any such current flow occurs through steering diode paths and rarely involves the absorption device.

Figure 30 depicts a specific example where the input voltage,  $V_{IN}$ , exceeds the positive supply voltage (+V<sub>S</sub>) by 300mV or more. Much of what happens in the circuit depends on the supply characteristics. If +V<sub>S</sub> can sink the current, one of the upper input steering diodes conducts and directs current to +V<sub>S</sub>. Excessively high current levels can flow with increasingly higher  $V_{IN}$ . As a result, the datasheet specifications recommend that applications limit the input current to 10mA.

If the supply is not capable of sinking the current,  $V_{IN}$  may begin sourcing current to the operational amplifier, and then take over as the source of positive supply voltage. The danger in this case is that the voltage can rise to levels that exceed the operational amplifier absolute maximum ratings. In extreme but rare cases, the absorption device triggers on while  $+V_S$  and  $-V_S$  are applied. If this event happens, a direct current path is established between the  $+V_S$  and  $-V_S$  supplies. The power dissipation of the absorption device is quickly exceeded, and the extreme internal heating destroys the operational amplifier.

Another common question involves what happens to the amplifier if an input signal is applied to the input while the power supplies  $+V_S$  and/or  $-V_S$  are at 0V. Again, it depends on the supply characteristic while at 0V, or at a level below the input signal amplitude. If the supplies appear as high impedance, then the operational amplifier supply current may be supplied by the input source via the current steering diodes. This state is not a normal bias condition; the amplifier most likely will not operate normally. If the supplies are low impedance, then the current through the steering diodes can become quite high. The current level depends on the ability of the input source to deliver current, and any resistance in the input path.

#### **APPLICATION IDEAS**

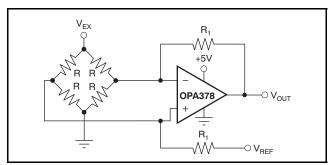

Figure 31 shows the basic configuration for a bridge amplifier.

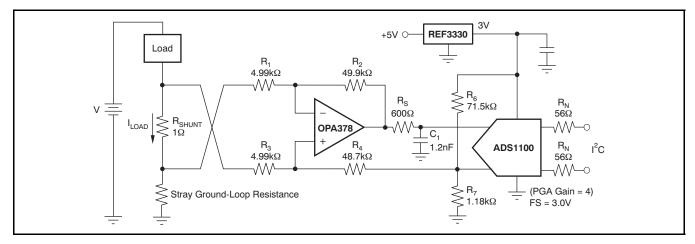

A low-side current shunt monitor is shown in Figure 32.  $R_N$  are optional resistors used to isolate the ADS8325 from the noise of the digital two-wire bus. Because the ADS8325 is a 16-bit converter, a precise reference is essential for maximum accuracy. If absolute accuracy is not required, and the 5V power supply is sufficiently stable, the REF3330 may be omitted.

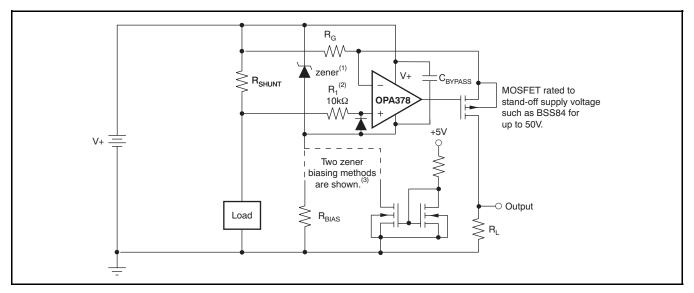

Figure 33 shows a high-side current monitor. The load current develops a voltage drop across  $R_{\text{SHUNT}}.$  The noninverting input monitors this voltage and is duplicated on the inverting input.  $R_{\text{G}}$  then has the same voltage drop as  $R_{\text{SHUNT}}.$   $R_{\text{G}}$  can be sized to provide whatever current is most convenient to the designer based on design constraints. The current from  $R_{\text{G}}$  then flows through the MOSFET and to resistor  $R_{\text{L}}$ , creating a voltage that can be read. Note that  $R_{\text{L}}$  and  $R_{\text{G}}$  set the voltage gain of the circuit.

The supply voltage for the op amp is derived from the zener diode. For the OPA378  $V_S$  must be between 2.2V and 5.5V. Two possible methods to bias the zener are shown in the circuit of Figure 33: the customary resistor bias and the current monitor. The current monitor biasing achieves the lowest possible voltage. Resistor  $R_1$  and the diode on the noninverting input provide short-circuit protection.

Figure 31. Single Op Amp Bridge Amplifier

NOTE: 1% resistors provide adequate common-mode rejection at small ground-loop errors.

Figure 32. Low-Side Current Monitor

- (1) Zener rated for op amp supply capability (that is, 5.1V for the OPA378).

- (2) Current-limiting resistor.

- (3) Choose zener biasing resistor or dual NMOSFETs (2N7002, NTZD511ON, SM6K2T110).

Figure 33. High-Side Current Monitor

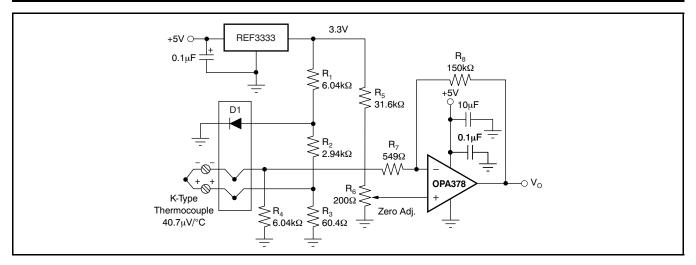

Figure 34. Temperature Measurement

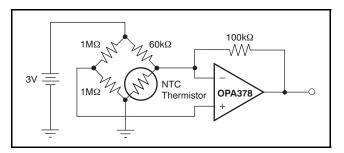

Figure 35. Thermistor Measurement

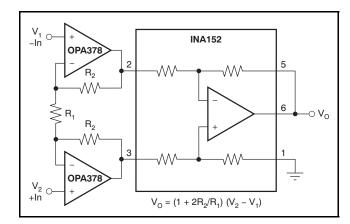

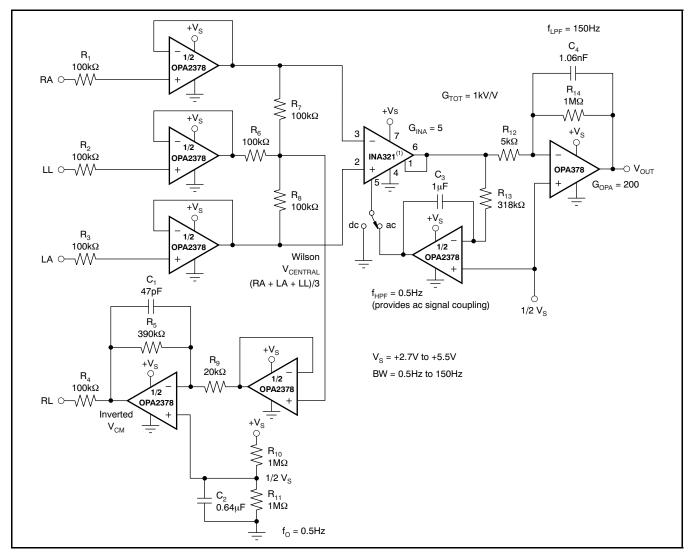

Figure 36. Precision Instrumentation Amplifier

(1) Other instrumentation amplifiers can be used, such as the INA326, which has lower noise but higher quiescent current.

Figure 37. Single-Supply, Very Low Power ECG Circuit

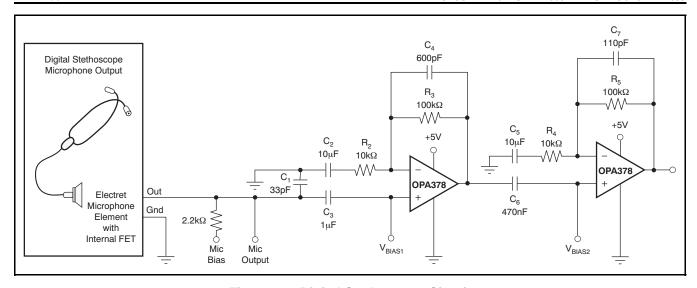

Figure 38. Digital Stethoscope Circuit

#### **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| C | hanges from Revision C (June 2009) to Revision D                                                                                                            | Page |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Changed OPA2378 orderable status to production data; updated references throughout document                                                                 | 1    |

| • | Changed first sentence of Description section                                                                                                               | 1    |

| • | Deleted footnote 2 from Package Information table                                                                                                           | 2    |

| • | Added OPA2378 parameters to the Offset Voltage section of the Electrical Characteristics table                                                              | 3    |

| • | Deleted footnote 1 from Electrical Characteristics table                                                                                                    | 3    |

| • | Added <i>OPA378</i> to the Offset Voltage, <i>Input Offset Voltage</i> and <i>vs Power Supply</i> parameters of the Electrical Characteristics table        | 3    |

| • | Added typical specification to the OPA378 Offset Voltage, <i>Over Temperature</i> parameter of the Electrical Characteristics table                         | 3    |

| • | Added Offset Voltage, Channel Separation parameter to the Electrical Characteristics table                                                                  | 3    |

| • | Added OPA2378 parameters to the Input Bias Current section of the Electrical Characteristics table                                                          | 3    |

| • | Added <i>OPA378</i> to the Input Bias Current, <i>Input Bias Current</i> and <i>Input Offset Current</i> parameters of the Electrical Characteristics table | 3    |

| • | Added typical specification to the Input Bias Current, Input Offset Current, OPA378 parameter of the Electrical Characteristics table                       | 3    |

| • | Added OPA378 to the Output, Voltage Output Swing from Rail parameter of the Electrical Characteristics                                                      | 4    |

| • | Added typical specification to the OPA378 Output, Over Temperature parameter of the Electrical Characteristics table                                        | 4    |

| • | Added the OPA2378 Output, Voltage Output Swing from Rail and Over Temperature parameters to the Electrical Characteristics table                            | 4    |

| • | Updated Figure 18                                                                                                                                           | 8    |

| • | Added Figure 25                                                                                                                                             | 9    |

| • | Updated Figure 32                                                                                                                                           | 14   |

| • | Updated Figure 33 and changed footnote 3                                                                                                                    | 14   |

10-Dec-2020

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| OPA2378AIDCNR    | ACTIVE | SOT-23       | DCN                | 8    | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | OCAI                    | Samples |

| OPA2378AIDCNT    | ACTIVE | SOT-23       | DCN                | 8    | 250            | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | OCAI                    | Samples |

| OPA378AIDBVR     | ACTIVE | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | OAZI                    | Samples |

| OPA378AIDBVT     | ACTIVE | SOT-23       | DBV                | 5    | 250            | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | OAZI                    | Samples |

| OPA378AIDCKR     | ACTIVE | SC70         | DCK                | 5    | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | BTS                     | Samples |

| OPA378AIDCKT     | ACTIVE | SC70         | DCK                | 5    | 250            | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | BTS                     | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

#### PACKAGE OPTION ADDENDUM

10-Dec-2020

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jun-2023

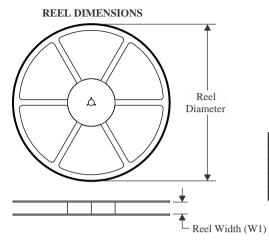

#### TAPE AND REEL INFORMATION

# TAPE DIMENSIONS KO P1 BO W Cavity A0

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

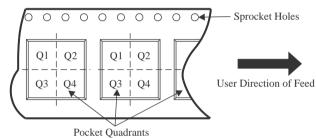

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| OPA2378AIDCNR | SOT-23          | DCN                | 8 | 3000 | 179.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| OPA378AIDBVR  | SOT-23          | DBV                | 5 | 3000 | 178.0                    | 8.4                      | 3.3        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| OPA378AIDBVT  | SOT-23          | DBV                | 5 | 250  | 178.0                    | 8.4                      | 3.3        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| OPA378AIDCKR  | SC70            | DCK                | 5 | 3000 | 178.0                    | 9.0                      | 2.4        | 2.5        | 1.2        | 4.0        | 8.0       | Q3               |

| OPA378AIDCKR  | SC70            | DCK                | 5 | 3000 | 179.0                    | 8.4                      | 2.2        | 2.5        | 1.2        | 4.0        | 8.0       | Q3               |

| OPA378AIDCKT  | SC70            | DCK                | 5 | 250  | 178.0                    | 9.0                      | 2.4        | 2.5        | 1.2        | 4.0        | 8.0       | Q3               |

| OPA378AIDCKT  | SC70            | DCK                | 5 | 250  | 179.0                    | 8.4                      | 2.2        | 2.5        | 1.2        | 4.0        | 8.0       | Q3               |

www.ti.com 3-Jun-2023

#### \*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| OPA2378AIDCNR | SOT-23       | DCN             | 8    | 3000 | 213.0       | 191.0      | 35.0        |

| OPA378AIDBVR  | SOT-23       | DBV             | 5    | 3000 | 445.0       | 220.0      | 345.0       |

| OPA378AIDBVT  | SOT-23       | DBV             | 5    | 250  | 445.0       | 220.0      | 345.0       |

| OPA378AIDCKR  | SC70         | DCK             | 5    | 3000 | 180.0       | 180.0      | 18.0        |

| OPA378AIDCKR  | SC70         | DCK             | 5    | 3000 | 213.0       | 191.0      | 35.0        |

| OPA378AIDCKT  | SC70         | DCK             | 5    | 250  | 180.0       | 180.0      | 18.0        |

| OPA378AIDCKT  | SC70         | DCK             | 5    | 250  | 213.0       | 191.0      | 35.0        |

#### NOTES:

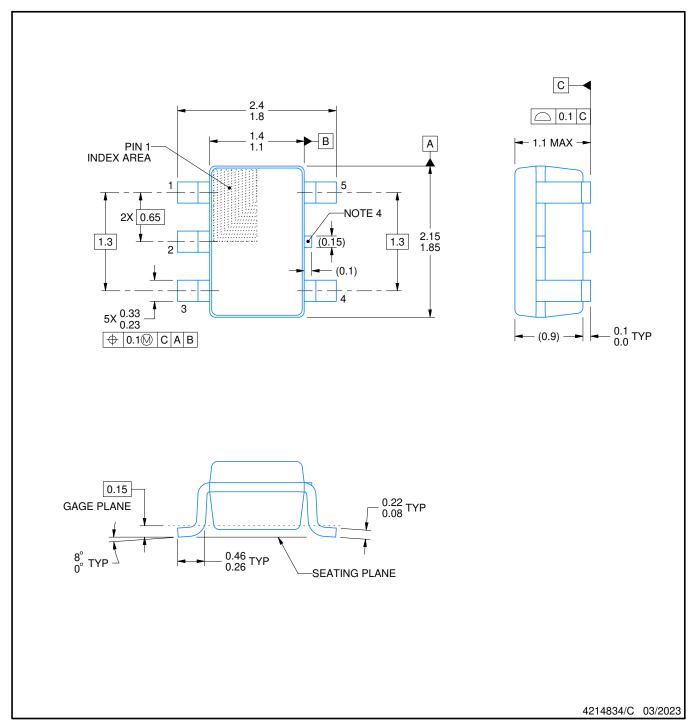

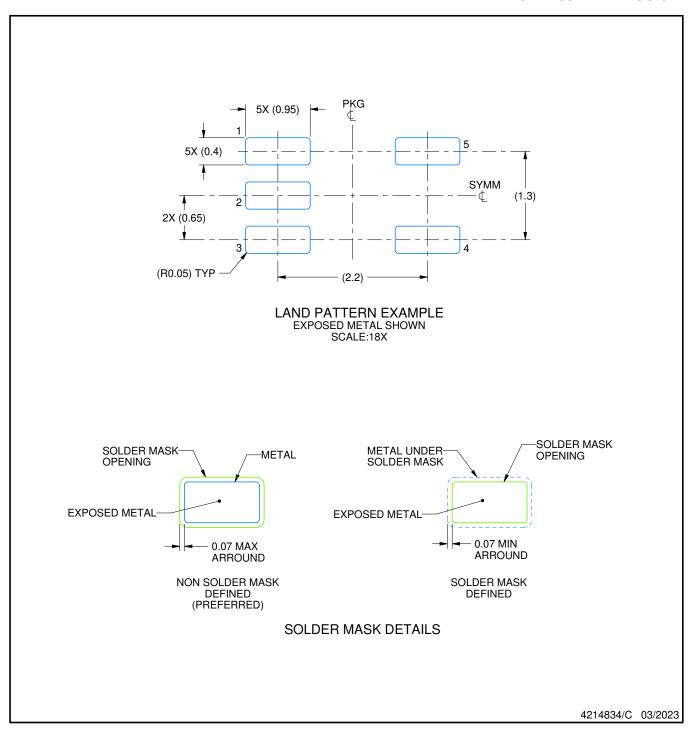

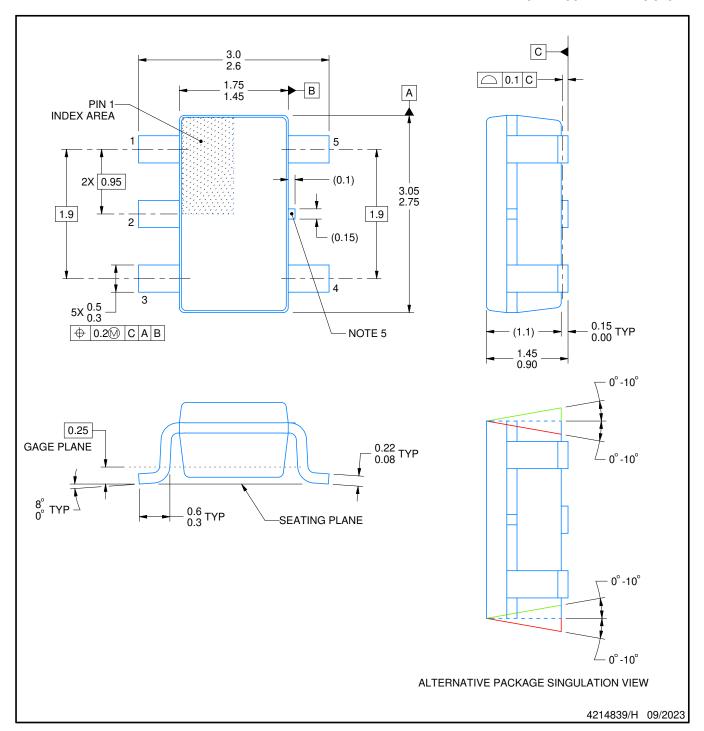

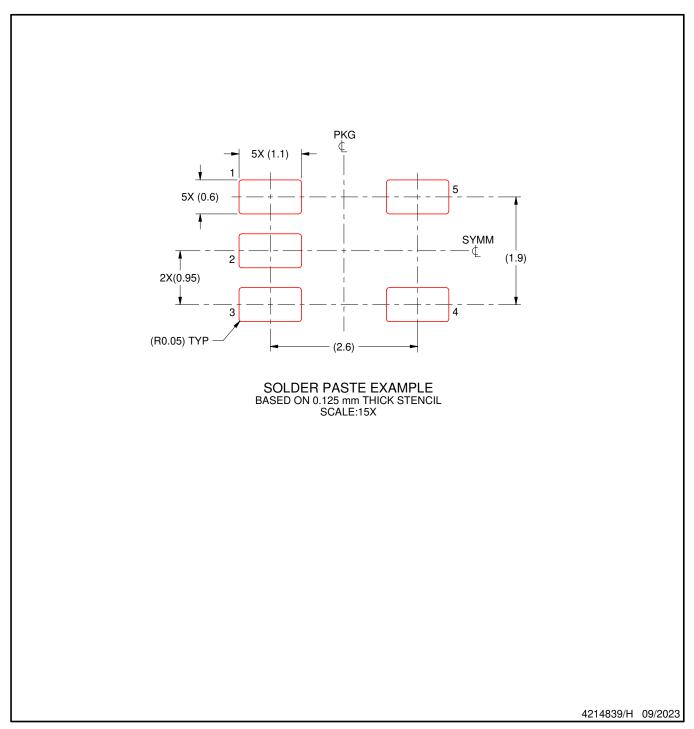

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

This drawing is subject to change without notice.

Reference JEDEC MO-203.

Support pin may differ or may not be present.

NOTES: (continued)

4. Publication IPC-7351 may have alternate designs.5. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

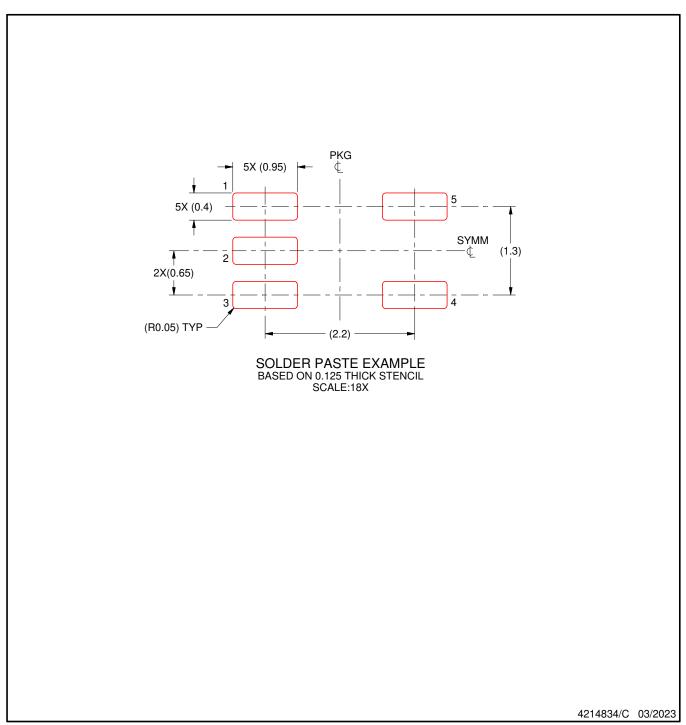

NOTES: (continued)

- 6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 7. Board assembly site may have different recommendations for stencil design.

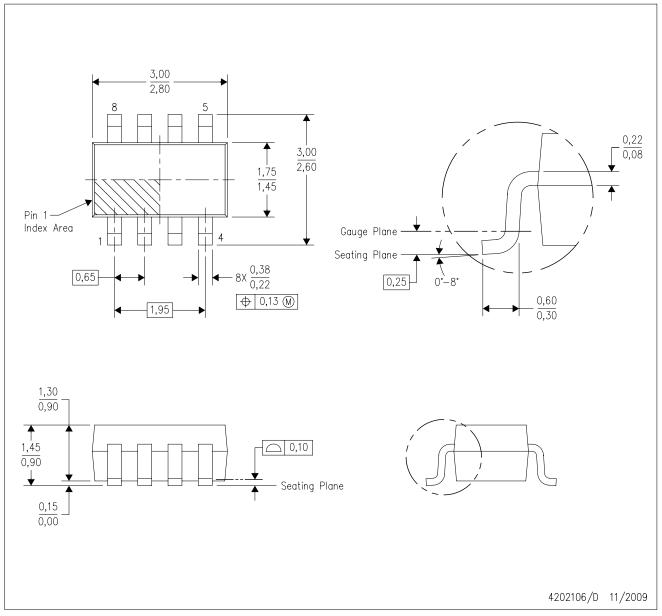

DCN (R-PDSO-G8)

PLASTIC SMALL-OUTLINE PACKAGE (DIE DOWN)

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Package outline exclusive of metal burr & dambar protrusion/intrusion.

- D. Package outline inclusive of solder plating.

- E. A visual index feature must be located within the Pin 1 index area.

- F. Falls within JEDEC MO-178 Variation BA.

- G. Body dimensions do not include flash or protrusion. Mold flash and protrusion shall not exceed 0.25 per side.

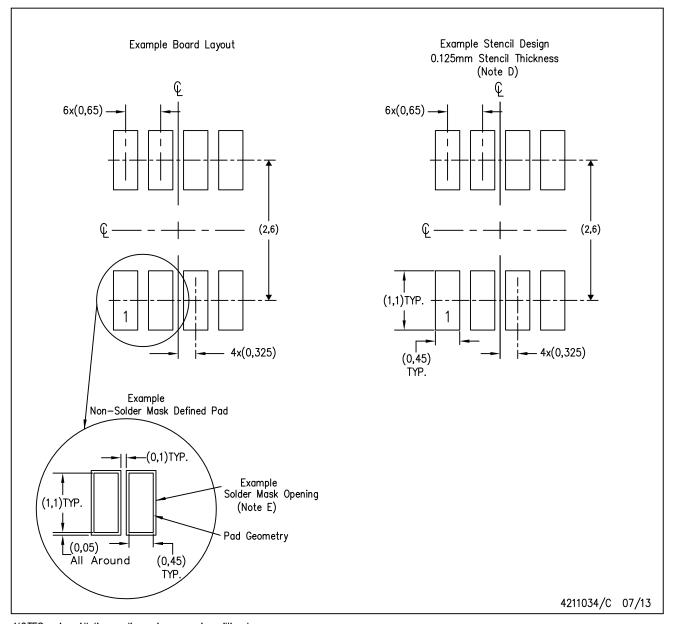

DCN (R-PDSO-G8)

PLASTIC SMALL-OUTLINE PACKAGE (DIE DOWN)

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

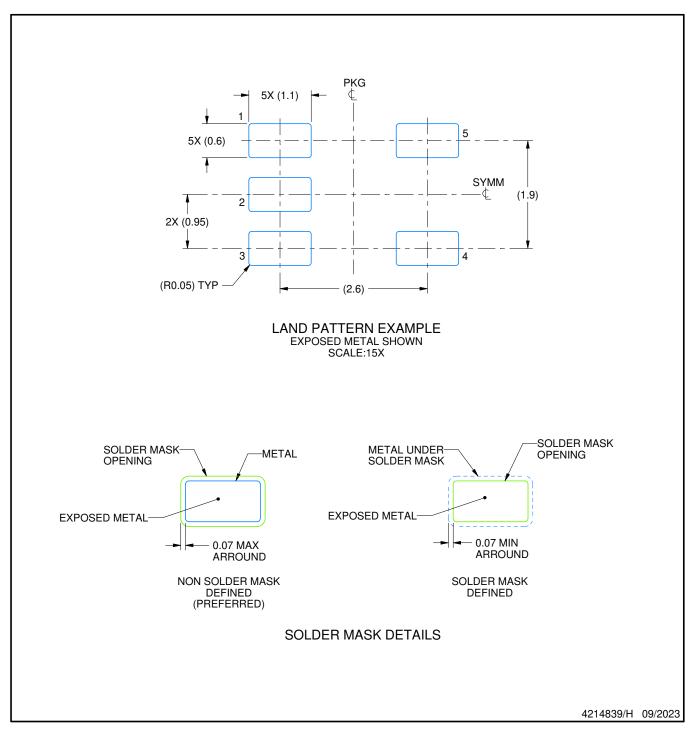

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. Reference JEDEC MO-178.

- 4. Body dimensions do not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.25 mm per side.

- 5. Support pin may differ or may not be present.

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated