## **Datasheet**

# BT830 Bluetooth v4.0 Dual-Mode UART HCI Module

Version 1.9

BT830 - SA

BT830 - ST

## **REVISION HISTORY**

| Revision | Date         | Changes                                                                                   | Approved By   |

|----------|--------------|-------------------------------------------------------------------------------------------|---------------|

| 1.0      | 23 July 2014 | Initial Version                                                                           | Jonathan Kaye |

| 1.1      | 10 Nov 2014  | Updated pin definitions                                                                   | Jonathan Kaye |

| 1.2      | 10 Aug 2015  | Added Tape/Reel information                                                               | Jonathan Kaye |

| 1.3      | 30 Sept 2015 | Added additional antenna information                                                      | Andrew Chen   |

| 1.4      | 15 Dec 2015  | Replaced tray image with new one                                                          | Maggie Teng   |

| 1.5      | 17 Aug 2016  | Changed Hardware Integration Guide to Datasheet.                                          | Sue White     |

| 1.6      | 31 Aug 2016  | Updated Declaration of Conformity                                                         | Tom Smith     |

| 1.7      | 16 May 2016  | Updated Declaration of Conformity for RED standards                                       | Tom Smith     |

| 1.8      | 07 Sept 2017 | Added Japan (MIC) certification/antenna information Transferred to the new Laird template | Maggie Teng   |

| 1.9      | 05 Mar 2019  | Updated logos and URLs                                                                    | Sue White     |

## **CONTENTS**

| 1  | Sco  | ppe                                      | 4  |

|----|------|------------------------------------------|----|

| 2  | Оре  | erational Description                    | 4  |

| 3  | Blo  | ck Diagram and Descriptions              | 5  |

| 4  | Spe  | ecifications                             | 6  |

| 5  | Pin  | Definitions                              | 7  |

| 6  | DC   | Electrical Characteristic                | 9  |

| 7  | RF   | Characteristics                          | 10 |

| 8  | Inte | erface                                   | 11 |

| 8  | 8.1  | PIO                                      | 11 |

| 1  | 8.2  | WLAN Coexistence Interface               | 11 |

| ;  | 8.3  | UART Interface                           | 12 |

| 1  | 8.4  | PCM Interface                            | 12 |

| 8  | 8.5  | GCI Interface                            | 14 |

| ;  | 8.6  | Slots and Sample Formats                 | 14 |

| 8  | 8.7  | PCM Timing Information                   | 15 |

| ;  | 8.8  | PCM Slave Timing                         | 18 |

| 8  | 8.9  | PCM Slave Mode Timing Parameters         | 18 |

| ;  | 8.10 | PCM_CLK and PCM_SYNC Generation          | 19 |

| ;  | 8.11 | PCM Configuration                        | 19 |

| 1  | 8.12 | Digital Audio Interface (I2S)            | 20 |

| 9  | Pov  | wer Supply and Regulation                | 22 |

| ,  | 9.1  | Voltage Regulator Enable and Reset       | 22 |

| ,  | 9.2  | Power Sequencing                         | 23 |

| 10 | Ant  | tenna Performance                        | 23 |

|    | 10.1 | Multilayer Chip Antenna                  | 23 |

|    | 10.2 | NanoBlade                                | 25 |

| 11 | Med  | chanical Dimensions and Land Pattern     | 26 |

| 12 | Imp  | plementation Note                        | 28 |

|    | 12.1 | PCB Layout on Host PCB                   | 28 |

| 13 | App  | olication Note for Surface Mount Modules | 29 |

|    | 13.1 | Introduction                             | 29 |

|    | 13.2 | Shipping                                 | 29 |

|    | 13.3 | Reflow Parameters                        | 31 |

| 14 | FC   | C and IC Regulatory                      | 32 |

| 15 | Eur  | ropean Union Regulatory                  | 35 |

| 16 | Jap  | pan (MIC) Certification                  | 35 |

| 17 | Ord  | dering Information                       | 36 |

| 18 | Blue | etooth SIG Approvals                     | 37 |

#### SCOPE

This document describes key hardware aspects of the Laird BT830 Bluetooth HCI modules. This document is intended to assist device manufacturers and related parties, with the integration of this module into their host devices. Data in this document are drawn from a number of sources including data sheets for the CSR8811. Because the BT830 is currently in development stage, this document is preliminary and the information in this document is subject to change. Visit https://connectivity.lairdtech.com/ to obtain the most recent version of this document.

#### 2 OPERATIONAL DESCRIPTION

The BT830 series of UART HCI devices are designed to meet the needs of OEMs adding robust Bluetooth connectivity and using embedded Bluetooth stacks within their products.

Leveraging the market-leading CSR8811 chipset, the BT830 series provides exceptionally low power consumption with outstanding range. Supporting the latest Bluetooth v4.0 specification with EDR (Enhanced Data Rate), the Laird BT830 series enables OEMs to accelerate their development time for leveraging either Classic Bluetooth or Bluetooth Low Energy (BLE) into their operating system-based devices.

With a footprint as small as 8.5 x 13 mm, yet output power at 7 dBm, these modules are ideal for applications where designers need high performance in minimal size. For maximum flexibility in systems integration, the modules are designed to support a UART interface plus GPIO and additionally I2S and PCM audio interfaces.

These modules present an HCI interface and have native support for Windows and Linux Bluetooth software stacks. All BT830 series devices are fully qualified as Bluetooth Hardware Controller Subsystem products. This allows designers to integrate their existing pre-approved Bluetooth host and profile subsystem stacks to gain a Bluetooth END product approval for their products.

The BT830 series is engineered to provide excellent RF performance with integrated antenna and additional band pass filters. It further reduces regulatory and testing requirements for OEMs and ensures a hassle free development cycle.

A fully featured, low-cost developer's kit is available for prototyping, debug, and integration testing of the BT830 series modules and further reduces risk and time in development cycles.

BT830-SA BTv4.0 Dual Mode UART HCI Module (Integrated Antenna)

BT830-ST BTv4.0 Dual Mode UART HCI Module (SMT Pad for External Antenna)

## Features and Benefits (3) From

- Bluetooth v4.0 dual mode (Classic Bluetooth and BLE)

- Compact footprint

- 3-wire Wi-Fi coexistence scheme

- High antenna radiation gain and efficiency

- Good interference rejection for multi-com system (GSM/WCDMA)

- Class 1 output 7 dBm

- UART, GPIO, I2S, and PCM

- Industrial temperature range

- Bluetooth hardware controller subsystem

- FCC, IC, and CE approvals

- Host Wake up

## **Application Areas**

- Medical devices

- ePOS terminals

- Barcode scanners

- Industrial cable replacement

- M2M connectivity

- Automotive Diagnostic Equipment

- Personal Digital Assistants (PDA)

- Bluetooth HID device (keyboard, mouse, and joystick)

https://connectivity.lairdtech.com

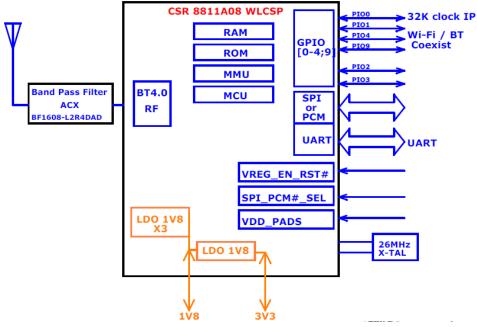

## 3 BLOCK DIAGRAM AND DESCRIPTIONS

Figure 2: BT830 module block diagram

## CS8811A08 (Main chip)

The BT830 is based on the CSR8811A08 dual mode chip. The chip is a single-chip radio with on-chip LDO regulators and baseband IC for Bluetooth 2.4 GHz systems including EDR to 3 Mbps.

Dedicated signal and baseband processing is included for full Bluetooth operation. The chip provides PCM/I2S and UART interfaces. Up to four general purpose I/Os are available for general use such as Wi-Fi coexistence or general indicators.

**Note:** The purpose of the SPI interface is to access the module's inner settings such as selecting different WLAN CO-EXIST scheme. The SPI interface can also be used to place the module in RF test mode. You cannot use the module over the SPI interface for normal operation as the main host interface.

| Antenna<br>Options  | BT830-SA – The antenna is a ceramic monopole chip antenna. BT830-ST – Provides a SMT pad for connecting an external antenna.                          |  |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Band Pass<br>Filter | The band pass filter filters the out-of-band emissions from the transmitter to meet the specific regulations for type approvals of various countries. |  |  |

| Crystal             | The embedded 26 MHz crystal is used for generating the clock for the entire module.                                                                   |  |  |

## 4 SPECIFICATIONS

Table 1: BT830 specifications

| Categories        | Feature             | Implementation                                                                                         |

|-------------------|---------------------|--------------------------------------------------------------------------------------------------------|

| Wireless          | Bluetooth (B)       | V4.0 Dual Mode                                                                                         |

| Specification     | Frequency           | 2.402 - 2.480 GHz                                                                                      |

|                   | Maximum Transmit    | Class 1                                                                                                |

|                   | Power               | +7 dBm from antenna                                                                                    |

|                   | Receive Sensitivity | -89 dBm                                                                                                |

|                   | Range               | Circa 100 meters                                                                                       |

|                   | Data Rates          | Up to 3 Mbps (over the air)                                                                            |

| Host Interface    | UART                | RX, TX, CTS, RTS                                                                                       |

|                   | GPIO                | Six configurable lines                                                                                 |

|                   |                     | (1.8V/3.3V configurable by VDD_PADS)                                                                   |

| Operational Modes | HCI                 | Host Controller Interface over UART                                                                    |

| Coexistence       | 802.11 (Wi-Fi)      | 3 wire CSR schemes supported                                                                           |

|                   |                     | (Unity-3 and Unity-3e)                                                                                 |

| Supply Voltage    | Supply              | 3.3V +/-10%                                                                                            |

|                   |                     | <b>Note:</b> See <i>Implementation Note</i> for details on different DC power selections on the BT830. |

| Power Consumption | Current             | Idle Mode ~4.3 mA (Master; ACL link; No traffic)                                                       |

|                   |                     | File Transfer ~7.1 mA (Master; ACL link; Transmit)                                                     |

| Antenna Option    | Internal (BT830-SA) | Multilayer ceramic antenna with up to 40% efficiency.                                                  |

|                   | External (BT830-ST) | SMT pad for external antenna                                                                           |

| Physical          | Dimensions          | 8.5 x 13 x 1.6 mm (BT830 - module)                                                                     |

| Environmental     | Operating           | -30°C to +85°C                                                                                         |

|                   | Storage             | -40°C to +85°C                                                                                         |

| Miscellaneous     | Lead Free           | Lead-free and RoHS compliant                                                                           |

|                   | Warranty            | 1-Year Warranty                                                                                        |

| Approvals         | Bluetooth®          | Hardware Controller Subsystem Approved                                                                 |

|                   | FCC / IC / CE       | All BT830 series (BT830-SA; BT830-ST)                                                                  |

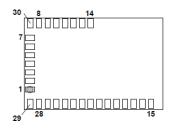

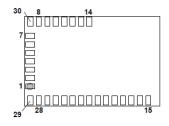

#### **PIN DEFINITIONS** 5

| Table 2 | able 2: BT830 pin definitions |                                                                |                  |                                                                                                      |              |  |  |  |

|---------|-------------------------------|----------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------|--------------|--|--|--|

| #       | Pin Name                      | I/O                                                            | Supply<br>Domain | Description                                                                                          | lf<br>Unused |  |  |  |

| 1       | VDD_PADS                      | DC voltage input                                               | (1.75V-3.6V)     | Positive DC supply for configuring digital I/O level.                                                | N/A          |  |  |  |

| 2       | GND                           | GND                                                            | -                | Ground                                                                                               | GND          |  |  |  |

| 3       | PIO2                          | Bidirectional, tri-<br>state, with weak<br>internal pull- down | VDD_PADS         | Programmable input/output line                                                                       | NC           |  |  |  |

| 4       | UART_RTS                      | Bidirectional, tri-<br>state,<br>with weak internal<br>pull-up | VDD_PADS         | UART request to send, active low                                                                     | NC           |  |  |  |

| 5       | UART_TX                       | Bidirectional, tri-<br>state,<br>with weak internal<br>pull-up | VDD_PADS         | UART data output, active high                                                                        | NC           |  |  |  |

| 6       | UART_CTS                      | Bidirectional, tri-<br>state,<br>with weak internal<br>pull-up | VDD_PADS         | UART clear to send, active low                                                                       | NC           |  |  |  |

| 7       | UART_RX                       | Bidirectional, tri-<br>state,<br>with weak internal<br>pull-up | VDD_PADS         | UART data input, active high                                                                         | NC           |  |  |  |

| 8       | VREG_EN_RST#                  | Input with strong internal pull-down                           | VDD_PADS         | Take high to enable internal regulators. Also acts as active low reset. Maximum voltage is VDD_PADS. | N/A          |  |  |  |

| 9       | VREG_IN_HV                    | Analogue regulator input                                       | 3.3V             | Module main DC power supply; Input to internal high-voltage regulator                                | N/A          |  |  |  |

| 10      | VREG_OUT_HV                   | Analogue regulator input/output                                | 1.8V             | Output from internal high-voltage regulator and input to low-voltage internal regulators.            | N/C          |  |  |  |

| 11      | GND                           | GND                                                            | -                | Ground                                                                                               | GND          |  |  |  |

| 12      | GND                           | GND                                                            | -                | Ground                                                                                               | GND          |  |  |  |

| 13      | GND                           | GND                                                            | -                | Ground                                                                                               | GND          |  |  |  |

| 14      | GND                           | GND                                                            | -                | Ground                                                                                               | GND          |  |  |  |

| 15      | GND                           | GND                                                            | -                | Ground                                                                                               | GND          |  |  |  |

| 16      | GND                           | GND                                                            | -                | Ground                                                                                               | GND          |  |  |  |

| 17      | RF                            |                                                                |                  | BT830-ST – RF signal out (50 ohm)<br>BT830-SA – No connection                                        |              |  |  |  |

| 18      | GND                           | GND                                                            | -                | Ground                                                                                               | GND          |  |  |  |

| #  | Pin Name                       | I/O                                                            | Supply<br>Domain                                                                          | Description                                                                                        | If<br>Unused |

|----|--------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------|

| 19 | PCM_SYNC/<br>SPI_CS#/<br>PIO23 | Bidirectional, tri-<br>state, with weak<br>internal pull-down  | VDD_PADS                                                                                  | PCM synchronous data sync SPI chip select, active low programmable input/output line  *See Note 1. | NC           |

| 20 | PCM_CLK/<br>SPI_CLK/ PIO24     | Bidirectional, tri-<br>state, with weak<br>internal pull-down  | VDD_PADS PCM synchronous data clock SPI clock Programmable input/output line *See Note 1. |                                                                                                    | NC           |

| 21 | PCM_IN/<br>SPI_MOSI/<br>PIO21  | Input, tri-state, with<br>weak internal pull-<br>down          | VDD_PADS                                                                                  | PCM synchronous data input<br>SPI data input<br>Programmable input/output line<br>*See Note 1.     | NC           |

| 22 | PCM_OUT/<br>SPI_MISO/<br>PIO22 | Output, tri-state,<br>with weak internal<br>pull- down         | VDD_PADS                                                                                  | PCM synchronous data output SPI data output Programmable input/output line *See Note 1.            | NC           |

| 23 | GND                            | GND                                                            | -                                                                                         | Ground                                                                                             | GND          |

| 24 | PIO0/<br>32K_CLK_IN            | Bidirectional, tri-<br>state, with weak<br>internal pull- down | VDD_PADS                                                                                  | Programmable input/output line and 32kHz sleep clock input                                         | NC           |

| 25 | PIO1/<br>BT_ACTIVE             | Bidirectional, tri-<br>state, with weak<br>internal pull- down | VDD_PADS                                                                                  | Programmable input/output line;<br>Wi-Fi and BT 3-wire coexistance                                 | NC           |

| 26 | PIO9/<br>BT_PRIORITY           | Bidirectional, tri-<br>state, with weak<br>internal pull- down | VDD_PADS                                                                                  | Programmable input/output line;<br>Wi-Fi and BT 3-wire coexistance                                 | NC           |

| 27 | PIO4/<br>WLAN_ACTIVE           | Bidirectional, tri-<br>state, with weak<br>internal pull- down | VDD_PADS                                                                                  | Programmable input/output line;<br>Wi-Fi and BT 3-wire coexistance                                 | NC           |

| 28 | SPI_PCM#_SEL                   | Input with weak internal pull-down                             | VDD_PADS                                                                                  | Control line to select SPI or PCM interface, high = SPI, low = PCM *See Note 1.                    | NC           |

| 29 | PIO3/<br>Host Wake up          | Bidirectional, tri-<br>state, with weak<br>internal pull- down | VDD_PADS                                                                                  | Programmable input/output line;<br>Host wake up from BT, active High.                              | NC           |

| 30 | GND                            | GND                                                            | -                                                                                         | Ground                                                                                             | GND          |

Note 1: The purpose of the SPI interface is to access the module's inner settings such as selecting different WLAN CO-EXIST scheme. The SPI interface can also be used to put the module in RF test mode. You cannot use the module over the SPI interface for normal operation as the main host interface.

## 6 DC ELECTRICAL CHARACTERISTIC

Table 3: Absolute maximum ratings

| asio or riscordio mammam ratingo |      |                  |      |  |  |

|----------------------------------|------|------------------|------|--|--|

| Rating                           | Min  | Max              | Unit |  |  |

| Storage temperature              | -40  | +85              | ٥C   |  |  |

| VREG_IN_HV                       | 2.3  | 4.8              | V    |  |  |

| VREG_OUT_HV                      | 1.7  | 2.0              | V    |  |  |

| VDD_PADS                         | -0.4 | 3.6              | V    |  |  |

| Other terminal voltages          | -0.4 | VDD_PADS + 0.4 V | V    |  |  |

Table 4: Recommended operating conditions

| Rating                | Min      | Max      | Unit |

|-----------------------|----------|----------|------|

| Operating temperature | -30      | +85      | °C   |

| VREG_IN_HV            | 3.0      | 3.6      | V    |

| VREG_OUT_HV           | 1.75     | 1.95     | V    |

| VDD_PADS              | 1.75     | 3.6      | V    |

| VREG_EN_RST#          | VDD_PADS | VDD_PADS | V    |

Table 5: High-voltage Linear Regulator

| Normal Operation                                        | Min  | Тур  | Max  | Unit   |

|---------------------------------------------------------|------|------|------|--------|

| Input voltage (VREG_IN_HV)                              | 3.0  | 3.3  | 3.6  | V      |

| Output voltage (VREG_OUT_HV)                            | 1.75 | 1.85 | 1.95 | V      |

| Temperature coefficient                                 | -200 | -    | 200  | ppm/°C |

| Output noise (frequency range 100Hz to100kHz)           | -    | -    | 0.4  | mV rms |

| Settling time (settling time within 10% of final value) | -    | -    | 5    | μs     |

| Output current                                          | -    | -    | 100  | mA     |

Table 6: Digital I/O Characteristics

| Normal Operation                          | Min                | Тур      | Max               | Unit |  |  |  |  |

|-------------------------------------------|--------------------|----------|-------------------|------|--|--|--|--|

| Input Voltage                             |                    |          |                   |      |  |  |  |  |

| VIL input logic level low                 | -0.4               | -        | 0.4               | V    |  |  |  |  |

| VIH input logic level high                | 0.7 x<br>VDD_PADS  | -        | VDD_PADS<br>+ 0.4 | V    |  |  |  |  |

|                                           | Output Volta       | age      |                   |      |  |  |  |  |

| VOL output logic level low, IOL = 4.0 mA  | -                  | -        | 0.4               | V    |  |  |  |  |

| VOH output logic level high, IOL = 4.0 mA | 0.75 x<br>VDD_PADS | -        | -                 | V    |  |  |  |  |

| li di | nput and Tristate  | Currents |                   |      |  |  |  |  |

| Strong pull-up                            | -150               | -40      | -10               | μΑ   |  |  |  |  |

| Strong pull-down                          | 10                 | 40       | 150               | μΑ   |  |  |  |  |

| Weak pull-up                              | -5                 | -1.0     | -0.33             | μΑ   |  |  |  |  |

| Weak pull-down                            | 0.33               | 1.0      | 5.0               | μΑ   |  |  |  |  |

| CI input capacitance                      | 1.0                | -        | 5.0               | pF   |  |  |  |  |

**Table 7: Current Consumption**

| Normal                | Operation         | Avg. | Unit       |

|-----------------------|-------------------|------|------------|

| Idle                  |                   | 5    | mA         |

| Inquiry               |                   | 891  | μ <b>A</b> |

| File Transfer (ACL)   | Transmit (Master) | 7.1  | mA         |

|                       | Receive (Slave)   | 11.5 | mA         |

| LE Connected (Master) |                   | 292  | μΑ         |

| LE Scan (Master)      |                   | 448  | μΑ         |

Current consumption values are taken with:

- VREG\_IN\_HV pin = 3.15V

- RF TX power set to 0dBm

- XTAL used with PSKEY\_LP\_XTAL\_LVL = 8

- LEDs disconnected

## 7 RF CHARACTERISTICS

Table 8: RF Characteristics

| RF Characteristics, VREG_IN_HV/VDD_PADS = 3.3V @ room temperature unless otherwise specified | Min | Тур. | Max | BT. Spec. | Unit |

|----------------------------------------------------------------------------------------------|-----|------|-----|-----------|------|

| Maximum RF Transmit Power                                                                    |     | 7    | 8   | 20        | dBm  |

| RF power variation over temperature range                                                    |     | 1.5  |     | -         | dB   |

| RF power variation over supply voltage range                                                 |     |      | 0.2 | -         | dB   |

| RF power variation over BT band                                                              |     | 3    |     | -         | dB   |

| RF power control range                                                                       | -21 |      | 8   | -         | dBm  |

| 20 dB band width for modulated carrier                                                       |     |      |     | 1000      | kHz  |

https://connectivity.lairdtech.com

| ACP                                     | $F = F_0 \pm 2MHz$ |     | -20     |     |

|-----------------------------------------|--------------------|-----|---------|-----|

|                                         | $F = F_0 \pm 3MHz$ |     | -40     |     |

|                                         | $F = F_0 > 3MHz$   |     | -40     |     |

| Drift rate                              |                    | 5   | ≤20     | kHz |

| ΔF <sub>1avg</sub>                      |                    | 165 | 140<175 | kHz |

| ΔF1 <sub>max</sub>                      |                    | 168 | 140<175 | kHz |

| ΔF <sub>2avg</sub> / ΔF <sub>1avg</sub> |                    | 0.9 | >=0.8   |     |

Table 9: BDR and EDR receiver sensitivity

| RF Characteristics, VREG_IN_HV/VDD_PADS = 3.3V @ room temp. | Packet Type | Min | Тур | Max | BT. Spec. | Unit |

|-------------------------------------------------------------|-------------|-----|-----|-----|-----------|------|

| Sensitivity for 0.1% BER                                    | DH1         |     | -87 |     | -70       | dBm  |

|                                                             | DH3         |     | -87 |     |           | dBm  |

|                                                             | DH5         |     | -87 |     |           | dBm  |

|                                                             | 2-DH5       |     | -91 |     |           | dBm  |

|                                                             | 3-DH5       |     | -85 |     |           | dBm  |

| Sensitivity variation over BT band                          | All         |     | 3   |     |           | dB   |

| Sensitivity variation over temperature range                | All         |     | TBD |     |           | dB   |

#### 8 INTERFACE

#### 8.1 PIO

PIO lines are configured through software to have either weak or strong pull-ups or pull-downs. All PIO lines are configured as inputs with weak pull-downs at reset and have additional individual bus-keeper configuration.

#### 8.2 WLAN Coexistence Interface

Dedicated hardware is provided to implement a variety of WLAN coexistence schemes. The following are supported:

- Channel skipping AFH

- Priority signaling

- Channel signaling

- Host passing of channel instructions

The BT830 supports the following WLAN coexistence schemes:

- Unity-3

- Unity-3e

More information is available in the BT830 Configuration File application note, available on the documentation tab of the BT830 Product Page at Lairdtech.com.

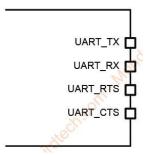

#### 8.3 UART Interface

This is a standard UART interface for communicating with other serial devices. The CSR8811 UART interface provides a simple mechanism for communicating with other serial devices using the RS-232 protocol.

Figure 1: Signals that implement the UART function

The above figure shows the four signals that implement the UART function. When BT830 is connected to another digital device, UART\_RX and UART\_TX transfer data between the two devices. The remaining two signals, UART\_CTS and UART\_RTS, implement RS232 hardware flow control where both are active low indicators. The default configuration of UART is 115200 bauds; None parity check; 1 stop bit; 8 bits per byte.

**Note**: With a standard PC, an accelerated serial port adapter card is required to communicate with the UART at its maximum data rate.

#### 8.4 PCM Interface

The audio PCM interface on the BT830 supports the following:

- Continuous transmission and reception of PCM encoded audio data over Bluetooth.

- Processor overhead reduction through hardware support for continual transmission and reception of PCM data.

- A bidirectional digital audio interface that routes directly into the baseband layer of the firmware. It does not pass through the HCI protocol layer.

- Hardware on the BT830 for sending data to and from a SCO connection.

- Up to three SCO connections on the PCM interface at any one time.

- PCM interface master, generating PCM\_SYNC and PCM\_CLK.

- PCM interface slave, accepting externally generated PCM\_SYNC and PCM\_CLK.

- Various clock formats including:

- Long Frame Sync

- Short Frame Sync

- GCI timing environments.

- 13-bit or 16-bit linear, 8-bit μ-law, or A-law companded sample formats.

- Receives and transmits on any selection of three of the first four slots following PCM SYNC.

The PCM configuration options are enabled by setting PSKEY PCM CONFIG32.

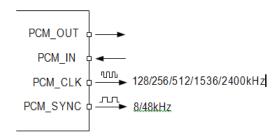

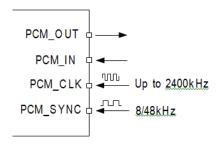

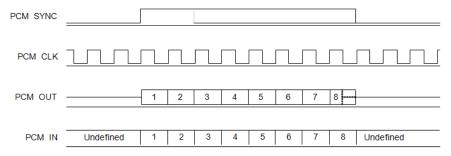

#### 8.4.1 PCM Interface Master/Slave

When configured as the master of the PCM interface, the BT830 generates PCM\_CLK and PCM\_SYNC.

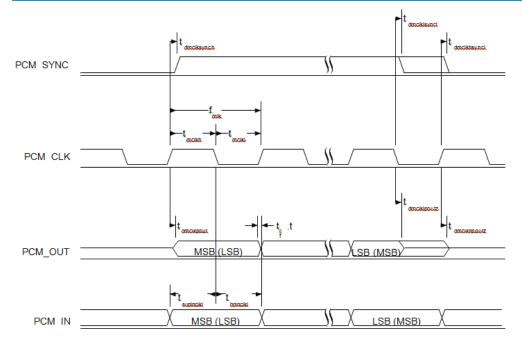

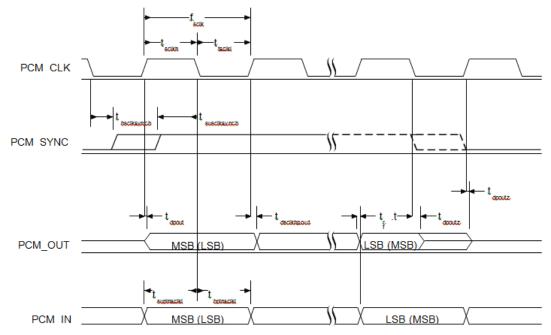

Figure 2: PCM Interface Master

Figure 3: PCM Interface Slave

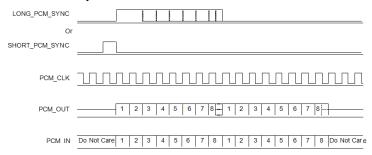

#### 8.4.2 Long FranceSprc

Figure 4: Long Frame Sync (shown with 8-bit Companded Sample)

Long Frame Sync indicates a clocking format that controls the transfer of PCM data words or samples. In Long Frame Sync, the rising edge of PCM\_SYNC indicates the start of the PCM word. When the BT830 is configured as PCM master, generating PCM\_SYNC and PCM\_CLK, then PCM\_SYNC is eight bits long. When the BT830 is configured as PCM Slave, PCM\_SYNC is from one cycle PCM\_CLK to half the PCM\_SYNC rate.

BT830 samples PCM\_IN on the falling edge of PCM\_CLK and transmits PCM\_OUT on the rising edge. PCM\_OUT is configurable as high impedance on the falling edge of PCM\_CLK in the LSB position or on the rising edge.

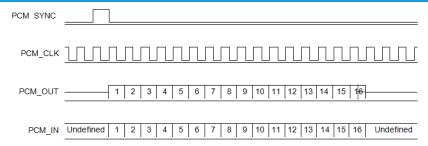

#### 8.4.3 Short Frame Sunc

In Short Frame Sync, the falling edge of PCM\_SYNC indicates the start of the PCM word. PCM\_SYNC is always one clock cycle long.

Figure 5: Short Frame Sync (Shown with 16-bit Sample)

As with Long Frame Sync, BT830 samples PCM\_IN on the falling edge of PCM\_CLK and transmits PCM\_OUT on the rising edge. PCM\_OUT is configurable as high impedance on the falling edge of PCM\_CLK in the LSB position or on the rising edge.

#### 8.4.4 Multi-Slot Operation

More than one SCO connection over the PCM interface is supported using multiple slots. Up to three SCO connections are carried over any of the first four slots.

Figure 6: Multi-slot operation with 2 Slots and 8-bit companded samples

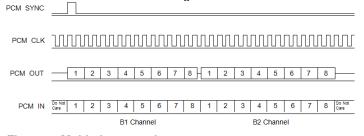

#### 8.5 GCI Interface

BT830 is compatible with the GCI, a standard synchronous 2B+D ISDN timing interface. The two 64 kbps B channels are accessed when this mode is configured.

Figure 7: Multi-slot operation

The start of frame is indicated by the rising edge of PCM\_SYNC and runs at 8 kHz.

## 8.6 Slots and Sample Formats

BT830 receives and transmits on any selection of the first four slots following each sync pulse. Slot durations are either 8 or 16 clock cycles:

- 8 clock cycles for 8-bit sample formats

- 16 clock cycles for 8-bit, 13-bit, or 16-bit sample formats

#### BT830 supports:

- 13-bit linear, 16-bit linear, and 8-bit μ-law or A-law sample formats

- A sample rate of 8 ksps

- Little or big endian bit order

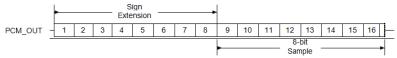

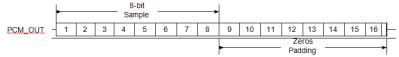

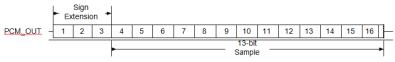

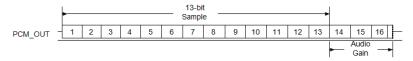

- For 16-bit slots, the three or eight unused bits in each slot are filled with sign extension, padded with zeros or a programmable 3-bit audio attenuation compatible with some codecs.

A 16-bit slot with 8-bit companded sample and sign extension selected.

A 16-bit slot with 8-bit companded sample and zeros padding selected

A 16-bit slot with 13-bit linear sample and sign extension selected

Figure 8: 16-bit slot Length and sample formats

## 8.7 **FOMTiningInformation**

Table 10: PCM Timing information

| Symbol       | Parameter                                                |                                                            | Min | Тур | Max   | Unit        |

|--------------|----------------------------------------------------------|------------------------------------------------------------|-----|-----|-------|-------------|

| fmclk        | Clk PCM_CLK frequency 4MHz DDS generation. Frequency     |                                                            | -   | 128 | -     | kHz         |

|              |                                                          | selection is programmable.                                 |     | 256 |       |             |

|              |                                                          |                                                            |     | 512 |       |             |

|              |                                                          | 48MHz DDS generation. Frequency selection is programmable. | 2.9 | -   | -     | kHz         |

| -            | PCM_SYNC frequency for                                   | r SCO connection                                           | -   | 8   | -     | kHz         |

| tmclkh (a)   | PCM_CLK high                                             | 4MHz DDS generation                                        | 980 | -   | -     | ns          |

| tmclkl a)    | PCM_CLK low                                              | 4MHz DDS generation                                        | 730 | -   | -     | ns          |

| _            | PCM_CLK jitter                                           | 48MHz DDS generation                                       | -   | -   | 21    | ns<br>pk-pk |

| tdmclksynch  | Delay time from                                          | 4MHz DDS generation                                        | -   | -   | 20    | ns          |

|              | PCM_CLK high to<br>PCM_SYNC high                         | 48MHz DDS generation                                       | -   | -   | 40.83 | ns          |

| tdmclkpout   | Delay time from PCM_Cl                                   | LK high to valid PCM_OUT                                   | -   | -   | 20    | ns          |

| tdmclklsyncl | Delay time from                                          | 4MHz DDS generation                                        | -   | -   | 20    | ns          |

|              | PCM_CLK low to<br>PCM_SYNC low (long<br>frame sync only) | 48MHz DDS generation                                       | -   | -   | 40.83 | ns          |

https://connectivity.lairdtech.com

(a) Assumes normal system clock operation. Figures vary during low-power modes, when system clock speeds are reduced.

Table 11: PCM Master Mode Timing Parameters

| Symbol       | Para                                                   | Min                  | Тур | Max | Unit  |    |

|--------------|--------------------------------------------------------|----------------------|-----|-----|-------|----|

| tdmclkhsyncl | Delay time from PCM_CLK                                | 4MHz DDS generation  | -   | -   | 20    | ns |

|              | high to PCM_SYNC low                                   | 48MHz DDS generation | -   | -   | 40.83 | ns |

| tdmclklpoutz | Delay time from PCM_CLK lingh impedance                | -                    | -   | 20  | ns    |    |

| tdmclkhpoutz | Delay time from PCM_CLK high to PCM_OUT high impedance |                      | -   | -   | 20    | ns |

| tsupinclkl   | Set-up time for PCM_IN valid to PCM_CLK low            |                      | 20  | -   | -     | ns |

| thpinclkl    | Hold time for PCM_CLK low to PCM_IN invalid            |                      | 0   | -   | -     | ns |

Figure 9: PCM Master Timing Long Frame Sync

Figure 10: PCM Master Timing Short Frame Sync

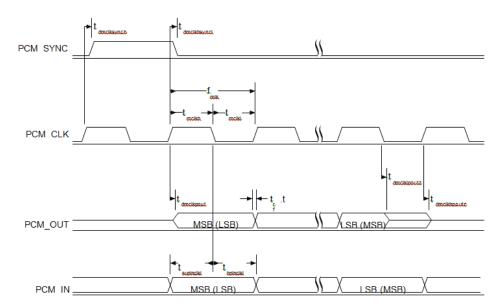

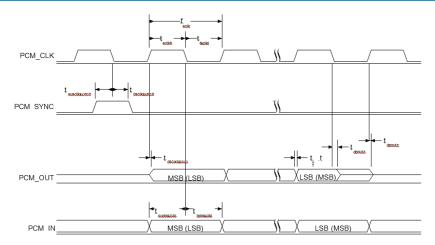

## 8.8 PCM Slave Timing

| Symbol | Parameter                               | Min | Тур | Max  | Unit |

|--------|-----------------------------------------|-----|-----|------|------|

| fsclk  | PCM clock frequency (Slave mode: input) | 64  | -   | 2048 | kHz  |

| fsclk  | PCM clock frequency (GCI mode)          | 128 | -   | 4096 | kHz  |

| tsclkl | PCM_CLK low time                        | 200 | -   | -    | ns   |

| tsclkh | PCM_CLK high time                       | 200 | -   | -    | ns   |

## 8.9 PCM Slave Mode Timing Parameters

| Symbol       | Parameter                                                                                             | Min | Тур | Max | Unit |

|--------------|-------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| thsclksynch  | Hold time from PCM_CLK low to PCM_SYNC high                                                           | 2   | -   | -   | ns   |

| tsusclksynch | Set-up time for PCM_SYNC high to PCM_CLK low                                                          | 20  | -   | -   | ns   |

| †dpout       | Delay time from PCM_SYNC or PCM_CLK, whichever is later, to valid PCM_OUT data (long frame sync only) | -   | -   | 15  | ns   |

| tdsclkhpout  | Delay time from CLK high to PCM_OUT valid data                                                        | -   | -   | 15  | ns   |

| tdpoutz      | Delay time from PCM_SYNC or PCM_CLK low, whichever is later, to PCM_OUT data line high impedance      | -   | -   | 20  | ns   |

| tsupinsclkl  | Set-up time for PCM_IN valid to CLK low                                                               | 20  | -   | -   | ns   |

| thpinsclkl   | Hold time for PCM_CLK low to PCM_IN invalid                                                           | 2   | -   | -   | ns   |

Figure 11: PCM Slave Timing Long Frame Sync

Figure 12: PCM Slave Timing Short Frame Sync

## 8.10 PCM\_CLK and PCM\_SYNC Generation

BT830 has two methods of generating PCM CLK and PCM SYNC in master mode:

- Generating these signals by DDS from BT830internal 4MHz clock. Using this mode limits PCM\_CLK to 128, 256 or 512 kHz and PCM\_SYNC to 8 kHz.

- Generating these signals by DDS from an internal 48MHz clock enables a greater range of frequencies to be generated with low jitter but consumes more power. To select this second method, set bit to 48M\_PCM\_CLK\_GEN\_EN in PSKEY\_PCM\_CONFIG32. When in this mode and with long frame sync, the length of PCM\_SYNC is either 8 or 16 cycles of PCM\_CLK, determined by LONG\_LENGTH\_SYNC\_EN in PSKEY\_PCM\_CONFIG32.

Equation 8.1 describes PCM\_CLK frequency when generated from the internal 48MHz clock:

$$f = \frac{CNT\_RATE}{CNT\_LIMIT} \times 24MHz$$

#### Equation 8.1: PCM\_CLK Frequency Generated Using the Internal 48MHz Clock

Set the frequency of PCM SYNC relative to PCM CLK using Equation 8.2:

$$f = \frac{PCM\_CLK}{SYNC\_LIMIT \times 8}$$

#### Equation 8.2: PCM\_SYNC Frequency Relative to PCM\_CLK

CNT\_RATE, CNT\_LIMIT and SYNC\_LIMIT are set using PSKEY\_PCM\_LOW\_JITTER\_CONFIG. As an example, to generate PCM\_CLK at 512kHz with PCM\_SYNC at 8kHz, set SKEY\_PCM\_LOW\_JITTER\_CONFIG to 0x08080177.

## 8.11 PCM Configuration

Configure the PCM by using PSKEY\_PCM\_CONFIG32 and PSKEY\_PCM\_LOW\_JITTER\_CONFIG (see your PSKey file). The default for PSKEY\_PCM\_CONFIG32 is 0x00800000.

**For example:** First slot following sync is active, 13-bit linear voice format, long frame sync and interface master generating 256kHz PCM\_CLK from 4MHz internal clock with no tri-state of PCM\_OUT).

## 8.12 Digital Audio Interface (I<sup>2</sup>S)

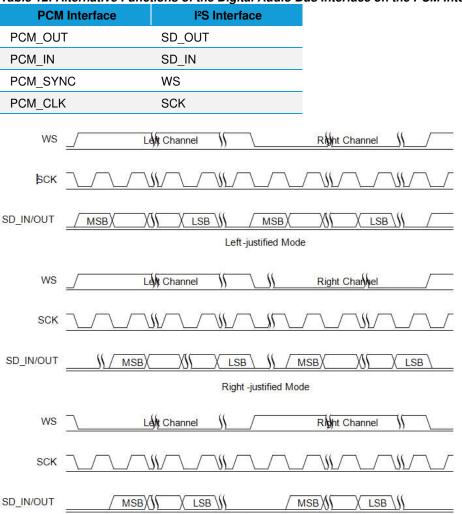

The digital audio interface supports the industry standard formats for I<sup>2</sup>S, left-justified or right-justified. The interface shares the same pins as the PCM interface which means each audio bus is mutually exclusive in its usage. Table 12 lists these alternative functions. Figure 11 shows the timing diagram.

Table 12: Alternative Functions of the Digital Audio Bus Interface on the PCM Interface.

Figure 13: PCM Configuration

The internal representation of audio samples within BT830is 16-bit and data on SD\_OUT is limited to 16-bit per channel.

Table 13: Digital Audio Interface Slave Timing

| Symbol | Parameter     | Min | Тур | Max | Unit |

|--------|---------------|-----|-----|-----|------|

| -      | SCK Frequency | -   | -   | 6.2 | MHz  |

| -      | WS Frequency  | -   | -   | 96  | kHz  |

| tch    | SCK high time | 80  | -   | -   | ns   |

| tcl    | SCK low time  | 80  | -   | -   | ns   |

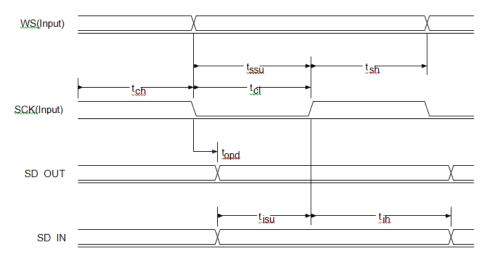

Table 14: I2S Slave Mode Timing

| Symbol | Parameter                           | Min | Тур | Max | Unit |

|--------|-------------------------------------|-----|-----|-----|------|

| tssu   | WS valid to SCK high set-up time    | 20  | -   | -   | ns   |

| tsh    | SCK high to WS invalid hold time    | 2.5 | -   | -   | ns   |

| topd   | SCK low to SD_OUT valid delay time  | -   | -   | 20  | ns   |

| tisu   | SD_IN valid to SCK high set-up time | 20  | -   | -   | ns   |

| tih    | SCK high to SD_IN invalid hold time | 2.5 | -   | -   | ns   |

Figure 14: Digital Audio Interface Slave Timing

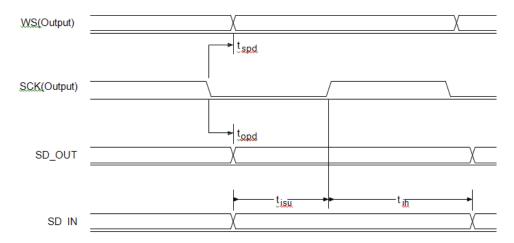

Table 15: Digital Audio Interface Master Timing

| Symbol | Parameter     | Min | Тур | Max | Unit |

|--------|---------------|-----|-----|-----|------|

| -      | SCK Frequency | -   | -   | 6.2 | MHz  |

| -      | WS Frequency  | -   | -   | 96  | kHz  |

Table 16: I2S Master Mode Timing Parameters, WS and SCK as Outputs

| ns |

|----|

|    |

| ns |

| ns |

| ns |

|    |

Figure 15: Digital Audio Interface Master Timing

## 9 POWER SUPPLY AND REGULATION

BT830 can be powered by either of the two sources listed below:

**Method #1** – Apply 3.3 V on pin-9, High-voltage linear regulator input (VREG\_IN\_HV), to generate the main 1.8 V out put on pin-10 (VREG\_OUT\_HV).

A minimum 1.5  $\mu$  F capacitor must be connected to the Pin-10 (VREG\_OUT\_HV). Low ESR capacitors such as multilayer ceramic types should be used. In this case, the VDD PADS can be either 3.3V or 1.8V.

**Method #2** – Apply 1.8V on pin-10 High-voltage linear regulator output (VREG\_OUT\_HV), to generate the internal voltage for the system. Be sure to left Pin-9 un-connected in this method. In this case, the VDD\_PADS can only be set at 1.8V.

Note: The I/O signal voltage level (VDD\_PADS) should be equal or less than the power supply mentioned voltage above.

## 9.1 Voltage Regulator Enable and Reset

A single pin, VREG\_EN\_RST#, controls both the high-voltage linear regulator enables and the digital reset function. The VREG\_EN\_RST# pin remains active controlling the reset function if the HV linear regulator is not used; the pin must be driven high to take the device out of reset.

The regulator is enabled by taking the VREG EN RST# pin above 1.0V. The regulator can also be controlled by the software.

The VREG\_EN\_RST# is also connected internally to the reset function, and is powered from the VDD\_PADS supply, so voltages above VDD\_PADS must not be applied to this pin. The VREG\_EN\_RST# pin is pulled down internally.

The VREG\_EN\_RST# pin is an active low reset. Assert the reset signal for a period greater than five milliseconds to ensure a full reset.

Note:

The regulator enables are released as soon as VREG\_EN\_RST# is low, so the regulators shut down. Therefore do not take VREG\_EN\_RST# low for less than five millilseconds, as a full reset is not guaranteed.

Other reset sources are:

- Power-on reset

- Via a software-configured watchdog timer

A warm reset function is also available under software control. After a warm reset the RAM data remains available.

## 9.2 Power Sequencing

CSR recommends that all power supplies are powered at the same time. The order of powering the supplies relative to the I/O supply, VDD\_PADS to VREG\_IN\_HV or VREG\_OUT\_HV, is not important.

#### 10 ANTENNA PERFORMANCE

## 10.1 Multilayer Chip Antenna

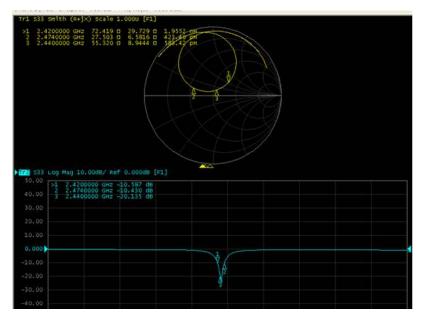

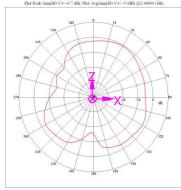

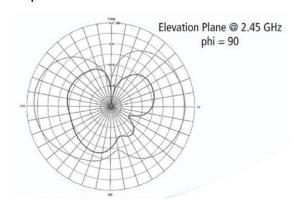

Figure 16 illustrates this antenna's performance.

| Unit in dBi @2.44GHz | XY-plane |      | XZ-plane |      | YZ-plane |      | Efficiency |

|----------------------|----------|------|----------|------|----------|------|------------|

| Onit in abi @2.44GH2 | Peak     | Avg. | Peak     | Avg. | Peak     | Avg. | Efficiency |

| AT3216-B2R7HAA       | -2.2     | -5.9 | -0.7     | -5.0 | -1.3     | -3.7 | 40%        |

Figure 16: BT830 gain table for the multilayer chip antenna

Figure 17: Network Analyzer output

## XY-plane

Far-field Power Distribution(H+V) on X-Y Plane

Plot Peak Gase(H+V)r-22 dBi; Plot AppGase(H+V)r-59 dBi; @2 44000 GHz

#### Unit : dBi

|          | Peak gain | Avg. gain |

|----------|-----------|-----------|

| XY-plane | -2.2      | -5.9      |

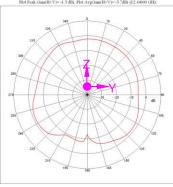

## XZ-plane

Far-field Power Distribution(H+V) on X-Z Plane

|          | Peak gain | Avg. gain |

|----------|-----------|-----------|

| XZ-plane | -0.7      | -5.0      |

## YZ-plane

Far-field Power Distribution(H+V) on Y-Z Plane

|          | Peak gain | Avg. gain |

|----------|-----------|-----------|

| YZ-plane | -1.3      | -3.7      |

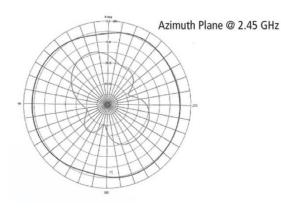

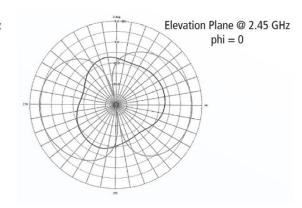

## 10.2 NanoBlade

The following describes the performance of the NanoBlue antenna (EBL2449A1-15UFL):

| Parameter              | Performance               |

|------------------------|---------------------------|

| Frequency Range        | 2.4-2.5 GHz               |

| Gain                   | 2.0 dBi                   |

| Polarization           | Linear                    |

| Impedance              | 50 ohms                   |

| VSWR                   | <2.0:1                    |

| Dimensions (L x W x H) | 1.88 in x .5 in x .032 in |

| Weight                 | 2 grams                   |

## XY-plane

## XZ-plane

## YZ-plane

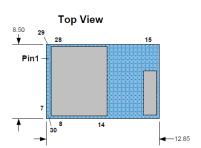

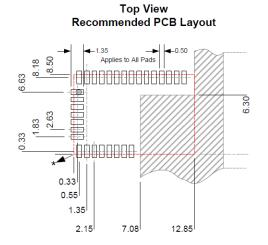

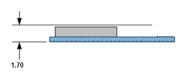

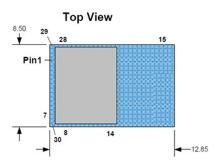

## 11 MECHANICAL DIMENSIONS AND LAND PATTERN

## 11.1 BT830-SA Mechanical Drawing

#### **Bottom View Device Pads**

Side View

\* Dimensions from corner of BT830 edge

⊕ Pin1

**Note**: Dimensions are in millimetres (mm).

Tolerances: .xx  $\pm 0.03$  mm for PCB PAD;  $\pm 0.15$ mm for module size.

.x ±1.3 mm

## 11.2 BT830-ST Mechanical Drawing

#### **Bottom View Device Pads**

#### Side View

\* Dimensions from corner of BT830 edge

© Pin1

**Note**: Dimensions are in millimetres (mm).

Tolerances: .xx  $\pm 0.03$  mm for PCB PAD;  $\pm 0.15$ mm for module size.

.x ±1.3 mm

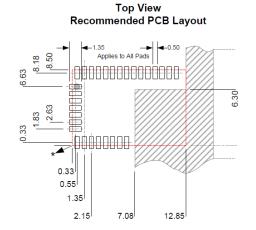

#### 12 IMPLEMENTATION NOTE

#### 12.1 PCB Layout on Host PCB

#### Checklist (for PCB):

- Must locate the BT830 module close to the edge of PCB.

- Use solid GND plane on inner layer (for best EMC and RF performance).

- Place GND vias as close to module GND pads as possible

- Route traces to avoid noise being picked up on VCC supply.

- Antenna Keep-out area:

- Ensure there is no copper in the antenna keep-out area on any layers of the host PCB.

- Keep all mounting hardware and metal clear of the area to allow proper antenna radiation.

- For best antenna performance, place the BT830 module on the edge of the host PCB, preferably in the corner with the antenna facing the corner.

- A different host PCB thickness dielectric will have small effect on antenna.

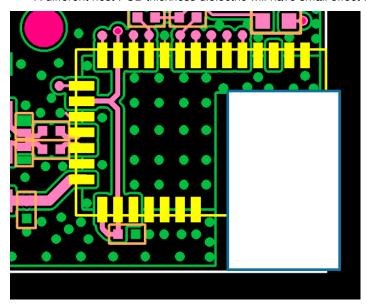

Figure 18: Recommend Antenna keep-out area (in White) used on the BT830-SA

#### 12.1.1 Antenna Keep-out and Proximity to Metal or Plastic

Checklist (for metal /plastic enclosure):

- Minimum safe distance for metals without seriously compromising the antenna (tuning) is 40 mm top/bottom and 30 mm left or right.

- Metal close to the BT830-SA chip monopole antenna (bottom, top, left, right, any direction) will have degradation on the antenna performance. The amount of degradation is entirely system dependent which means some testing by customers is required (in their host application).

- Any metal closer than 20 mm starts to significantly degrade performance (S11, gain, radiation efficiency).

- It is best that the customer tests the range with mock-up (or actual prototype) of the product to assess effects of enclosure height (and material whether metal or plastic).

## 12.1.2 DC Power Supply Options for Using BT830 Module

#### Using DC power 3.3 V

Power the on Pin-9 (VREG\_IN\_HV) with 3.3 V and pull-high on Pin-8 (VREG\_EN\_RST#) to turn on the internal regulator. The BT830 module generates 1.8 V output on Pin-10 (VREG\_OUT\_HV) which can supply to the other DC pin of the board.

Using DC power 1.8 V

Leave the Pin-9 (VREG\_IN\_HV) no connection, power the Pin-10 (VREG\_OUT\_HV) with 1.8 V and pull-high on Pin-8 (VREG\_EN\_RST#) to turn on the internal regulator.

## 13 APPLICATION NOTE FOR SURFACE MOUNT MODULES

#### 13.1 Introduction

Laird surface mount modules are designed to conform to all major manufacturing guidelines. This application note is intended to provide additional guidance beyond the information that is presented in the user manual. This application note is considered a living document and is updated as new information is presented.

The modules are designed to meet the needs of a number of commercial and industrial applications. They are easy to manufacture and they conform to current automated manufacturing processes.

#### 13.2 Shipping

#### 13.2.1 Tray Package

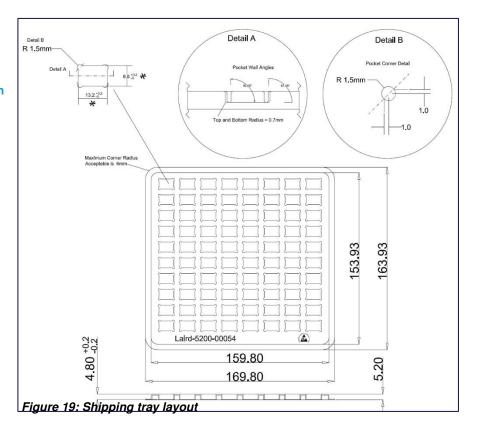

Modules are shipped in ESD (Electrostatic Discharge) safe trays that can be loaded into most manufacturers pick and place machines. Layouts of the trays are provided in Error! Reference source not found..

https://connectivity.lairdtech.com

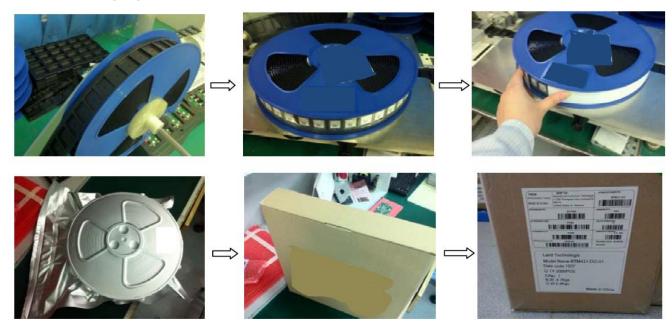

#### 13.2.2 Tape and Reel Package Information

**Note**: Ordering information for Tape and Reel packaging is an addition of T/R to the end of the full module part number. For example, BT830 becomes BT830-Sx-xx-T/R.

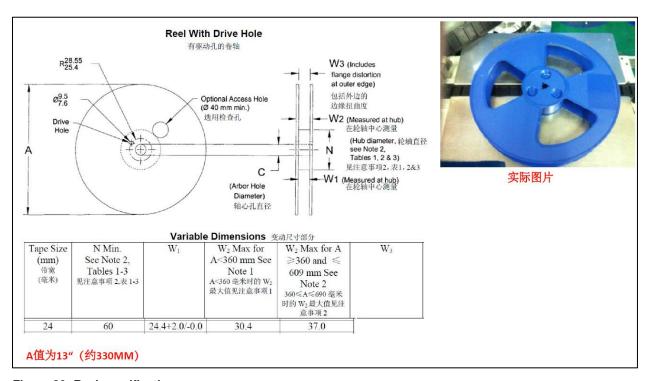

Figure 20: Reel specifications

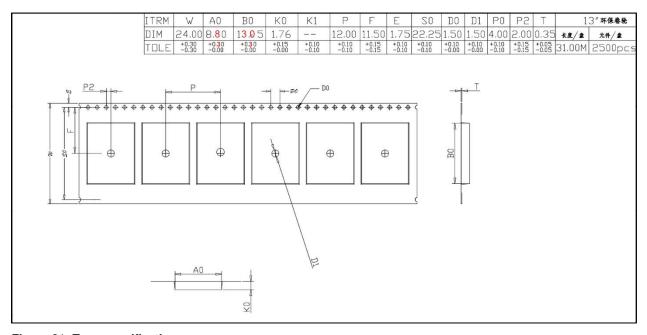

Figure 21: Tape specifications

There are 2500 BT830 modules taped in a reel (and packaged in a pizza box) and five boxes per carton (12,500 modules per carton). Reel, boxes, and carton are labeled with the appropriate labels. See Figure 22.

#### 13.2.2.1 Packaging Process

Figure 22: BT800 packaging process

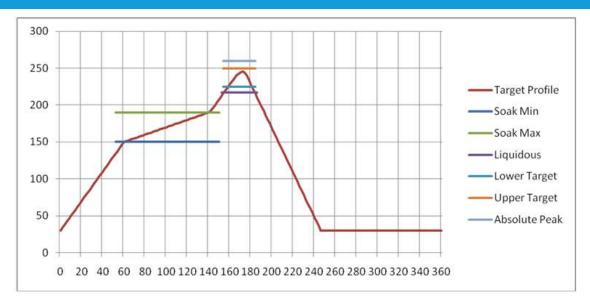

#### 13.3 Reflow Parameters

Prior to any reflow, it is important to ensure the modules were packaged to prevent moisture absorption. New packages contain desiccate (to absorb moisture) and a humidity indicator card to display the level maintained during storage and shipment. If directed to *bake units* on the card, see Table 17 and follow instructions specified by IPC/JEDEC J-STD-033. A copy of this standard is available from the JEDEC website: <a href="http://www.jedec.org/sites/default/files/docs/istd033b01.pdf">http://www.jedec.org/sites/default/files/docs/istd033b01.pdf</a>

**Note**: The shipping tray cannot be heated above 65°C. If baking is required at the higher temperatures displayed in in Table 17, the modules must be removed from the shipping tray.

Any modules not manufactured before exceeding their floor life should be re-packaged with fresh desiccate and a new humidity indicator card. Floor life for MSL (Moisture Sensitivity Level) 3 devices is 168 hours in ambient environment ≤30°C/60%RH.

Table 17: Recommended baking times and temperatures

|     | 125°C<br>Baking Temp.   |                                              |                         |                                              | 40°C/ ≤ 5%RH<br>Baking Temp. |                                              |

|-----|-------------------------|----------------------------------------------|-------------------------|----------------------------------------------|------------------------------|----------------------------------------------|

| MSL | Saturated<br>@ 30°C/85% | Floor Life Limit<br>+ 72 hours<br>@ 30°C/60% | Saturated<br>@ 30°C/85% | Floor Life Limit<br>+ 72 hours<br>@ 30°C/60% | Saturated<br>@ 30°C/85%      | Floor Life Limit<br>+ 72 hours @<br>30°C/60% |

| 3   | 9 hours                 | 7 hours                                      | 33 hours                | 23 hours                                     | 13 days                      | 9 days                                       |

Laird surface mount modules are designed to be easily manufactured, including reflow soldering to a PCB. Ultimately it is the responsibility of the customer to choose the appropriate solder paste and to ensure oven temperatures during reflow meet the requirements of the solder paste. Laird surface mount modules conform to J-STD-020D1 standards for reflow temperatures.

Important: During reflow, modules should not be above 260° and not for more than 30 seconds.

Figure 13-23: Recommended Reflow Temperature

Temperatures should not exceed the minimums or maximums presented in Table 18.

Table 18: Recommended Maximum and minimum temperatures

| Specification                      | Value  | Unit     |

|------------------------------------|--------|----------|

| Temperature Inc./Dec. Rate (max)   | 1~3    | °C / Sec |

| Temperature Decrease rate (goal)   | 2-4    | °C / Sec |

| Soak Temp Increase rate (goal)     | .5 - 1 | °C / Sec |

| Flux Soak Period (Min)             | 70     | Sec      |

| Flux Soak Period (Max)             | 120    | Sec      |

| Flux Soak Temp (Min)               | 150    | °C       |

| Flux Soak Temp (max)               | 190    | °C       |

| Time Above Liquidous (max)         | 70     | Sec      |

| Time Above Liquidous (min)         | 50     | Sec      |

| Time In Target Reflow Range (goal) | 30     | Sec      |

| Time At Absolute Peak (max)        | 5      | Sec      |

| Liquidous Temperature (SAC305)     | 218    | °C       |

| Lower Target Reflow Temperature    | 240    | °C       |

| Upper Target Reflow Temperature    | 250    | °C       |

| Absolute Peak Temperature          | 260    | °C       |

## 14 FCC AND IC REGULATORY

| Model     | US/FCC   | CANADA/IC   |

|-----------|----------|-------------|

| BT830     | SQGBT830 | 3147A-BT830 |

| BT830     | SQGBT830 | 3147A-BT830 |

| DVK-BT830 | SQGBT830 | 3147A-BT830 |

The BT830 family has been designed to operate with the antenna listed below having a maximum gain of 0.5 dBi. The required antenna impedance is 50 ohms.

| Item | Model    | Part Number                  | Mfg.    | Туре       | Peak Gain (dBi) | Connector |

|------|----------|------------------------------|---------|------------|-----------------|-----------|

| 1    | BT830-SA | AT3216-B2R7HAA               | ACX     | Chip       | 0.5             | N/A       |

| 2    | BT830-ST | S181FL-L-RMM-2450S           | Nearson | Dipole     | 2.0             | UFL       |

| 3    | BT830-ST | EBL2449A1-15UFL              | Laird   | PCB Dipole | 2.0             | UFL       |

| 4    | BT830-ST | MAF94190                     | Laird   | Dipole     | 2.0             | UFL       |

| 5    | BT830-ST | WRR2400-IP04-B<br>(MAF94019) | Laird   | Dipole     | 1.5             | UFL       |

## 14.1 Documentation Requirements

In order to ensure regulatory compliance, when integrating the BT830 into a host device, it is necessary to meet the documentation requirements set forth by the applicable regulatory agencies. The following sections (FCC, Industry Canada, and European Union) outline the information that may be included in the user's guide and external labels for the host devices into which the BT830 is integrated.

#### **FCC**

Note:

You must place "Contains FCC ID: SQG-BT830" on the host product in such a location that it can be seen by an operator at the time of purchase.

#### **User's Guide Requirements**

The BT830 complies with FCC Part 15 Rules for a Modular Approval. To leverage Laird's grant, the conditions below must be met for the host device into which the BT830 is integrated:

The transmitter module is not co-located with any other transmitter or antenna that is capable of simultaneous operation.

As long as the conditions above are met, further transmitter testing is typically not required. However, the OEM integrator is still responsible for testing its end-product for any additional compliance requirements required with this module installed, such as (but not limited to) digital device emissions and PC peripheral requirements.

#### **IMPORTANT:**

In the event that the conditions above cannot be met (for example certain device configurations or co-location with another transmitter), then the FCC authorization is no longer considered valid and the FCC ID cannot be used on the final product. In these circumstances, the OEM integrator will be responsible for re-evaluating the end product (including the transmitter) and obtaining a separate FCC authorization.

When using Laird's FCC grant for the BT830, the integrator must include specific information in the user's guide for the device into which the BT830 is integrated. The integrator must not provide information to the end user regarding how to install or remove this RF module in the user's manual of the device into which the BT830 is integrated. The following FCC statements must be added in their entirety and without modification into a prominent place in the user's guide for the device into which the BT830 is integrated:

**IMPORTANT NOTE**: To comply with FCC requirements, the BT830 must not be co-located or operating in conjunction with any other antenna or transmitter.

#### 14.1.1.1 Federal Communication Commission Interference Statement

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be

Americas: +1-800-492-2320 Europe: +44-1628-858-940

Europe: +44-1628-858-940 Hong Kong: +852 2923 0610

determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one of the following measures:

- Reorient or relocate the receiving antenna.

- 1. Increase the separation between the equipment and receiver.

- 2. Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- 3. Consult the dealer or an experienced radio/TV technician for help.

**FCC Caution:** Any changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate this equipment.

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) This device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

**IMPORTANT NOTE:** FCC Radiation Exposure Statement:

This equipment complies with FCC radiation exposure limits set forth for an uncontrolled environment.

#### **Industry Canada**

Note:

You must place "Contains IC ID: 3147A-BT830" on the host product in such a location that it can be seen by an operator at the time of purchase.

#### RF Radiation Hazard Warning

Using higher gain antennas and types of antennas not certified for use with this product is not allowed. The device shall not be co-located with another transmitter.

Cet avertissement de sécurité est conforme aux limites d'exposition définies par la norme CNR-102 at relative aux fréquences radio.

This radio transmitter (Contains IC ID: 3147A-BT830) has been approved by Industry Canada to operate with the antenna types listed in table above with the maximum permissible gain and required antenna impedance for each antenna type indicated. Antenna types not included in this list, having a gain greater than the maximum gain indicated for that type, are strictly prohibited for use with this device.

Le présent émetteur radio (Contains IC ID: 3147A-BT830) a été approuvé par Industrie Canada pour fonctionner avec les types d'antenne énumérés ci-dessous et ayant un gain admissible maximal et l'impédance requise pour chaque type d'antenne. Les types d'antenne non inclus dans cette liste, ou dont le gain est supérieur au gain maximal indiqué, sont strictement interdits pour l'exploitation de l'émetteur.

Under Industry Canada regulations, this radio transmitter may only operate using an antenna of a type and maximum (or lesser) gain approved for the transmitter by Industry Canada. To reduce potential radio interference to other users, the antenna type and its gain should be so chosen that the equivalent isotropically radiated power (e.i.r.p.) is not more than that necessary for successful communication.

Conformément à la réglementation d'Industrie Canada, le présent émetteur radio peut fonctionner avec une antenne d'un type et d'un gain maximal (ou inférieur) approuvé pour l'émetteur par Industrie Canada. Dans le but de réduire les risques de brouillage radioélectrique à l'intention des autres utilisateurs, il faut choisir le type d'antenne et son gain de sorte que la puissance isotrope rayonnée équivalente (p.i.r.e.) ne dépasse pas l'intensité nécessaire à l'établissement d'une communication satisfaisante.

This device complies with Industry Canada license-exempt RSS standard(s). Operation is subject to the following two conditions: (1) this device may not cause interference, and (2) this device must accept any interference, including interference that may cause undesired operation of the device.

Le présent appareil est conforme aux CNR d'Industrie Canada applicables aux appareils radio exempts de licence. L'exploitation est autorisée aux deux conditions suivantes : (1) l'appareil ne doit pas produire de brouillage, et (2) l'utilisateur de l'appareil doit accepter tout brouillage radioélectrique subi, même si le brouillage est susceptible d'en compromettre le fonctionnement.

Americas: +1-800-492-2320 Europe: +44-1628-858-940

Europe: +44-1628-858-940 Hong Kong: +852 2923 0610

#### 15 EUROPEAN UNION REGULATORY

The BT830 has been tested for compliance with relevant standards for the EU market. BT830 modules were tested with a 0.5 dBi chip antenna.

The OEM should consult with a qualified test house before entering their device into an EU member country to make sure all regulatory requirements have been met for their complete device.

Reference the Declaration of Conformities listed below for a full list of the standards that the modules were tested to. Test reports are available upon request.

## 15.1 EU Declarations of Conformity - BT830-SA and BT830-ST

| Manufacturer           | Laird                                        |         |                                          |

|------------------------|----------------------------------------------|---------|------------------------------------------|

| Products               | BT830-SA and BT830-ST                        | A.C.    | C. C |

| Product<br>Description | Bluetooth v4.0 Class 1 UART HCI              | 2 de 18 | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1    |

| <b>EU Directives</b>   | 2014/53/EU – Radio Equipment Directive (RED) |         |                                          |

#### Reference standards used for presumption of conformity:

| Article Number | Requirement                                                           | Reference standard(s)                                           |

|----------------|-----------------------------------------------------------------------|-----------------------------------------------------------------|

| 3.1a           | Low voltage equipment safety                                          | EN 60950-1:2006 +A11:2009 +A1:2010 +A12:2011 +A2:2013           |

|                | DE Evenoure                                                           | EN 62311:2008                                                   |

|                | RF Exposure                                                           | EN 62479:2010                                                   |

| 3.1b           | Protection requirements with respect to electromagnetic compatibility | EN 301 489-1 v2.2.0 (2017-03)<br>EN 301 489-17 v3.2.0 (2017-03) |

| 3.2            | Means of the efficient use of the radio frequency spectrum (ERM)      | EN 300 328 v2.1.1 (2016-11)                                     |

#### Declaration:

We, Laird, declare under our sole responsibility that the essential radio test suites have been carried out and that the above product to which this declaration relates is in conformity with all the applicable essential requirements of Article 3 of the EU Radio Equipment Directive 2014/53/EU, when used for its intended purpose.

| Place of Issue:                 | Laird<br>W66N220 Commerce Court, Cedarburg, WI 53012 USA<br>tel: +1-262-375-4400 fax: +1-262-364-2649 |

|---------------------------------|-------------------------------------------------------------------------------------------------------|

| Date of Issue:                  | May 2017                                                                                              |

| Name of Authorized Person:      | Thomas T Smith, Director of EMC Compliance                                                            |

| Signature of Authorized Person: | Thomas T. Smutt                                                                                       |

## 16 JAPAN (MIC) CERTIFICATION

The BT830-SA/BT830-ST is approved for use in the Japanese market. The part numbers listed below hold WW type certification. Refer to **ARIB-STD-T66** for further guidance on OEM's responsibilities.

| Item | Model    | Part Number                  | Mfg.    | Туре       | Peak Gain (dBi) | Connector |

|------|----------|------------------------------|---------|------------|-----------------|-----------|

| 1    | BT830-SA | AT3216-B2R7HAA               | ACX     | Chip       | 0.5             | N/A       |

| 2    | BT830-ST | S181FL-L-RMM-2450S           | Nearson | Dipole     | 2.0             | UFL       |

| 3    | BT830-ST | EBL2449A1-15UFL              | Laird   | PCB Dipole | 2.0             | UFL       |

| 4    | BT830-ST | MAF94190                     | Laird   | Dipole     | 2.0             | UFL       |

| 5    | BT830-ST | WRR2400-IP04-B<br>(MAF94019) | Laird   | Dipole     | 1.5             | UFL       |

To use our ID, the following Geteki logo and ID must be placed on your product:

## 17 ORDERING INFORMATION

| Part Number | Description                                              |

|-------------|----------------------------------------------------------|

| BT830-SA    | BTv4.0 Dual Mode UART HCI Module with integrated Antenna |

| BT830-ST    | BTv4.0 Dual Mode UART HCI Module – Trace Pin             |

| DVK-BT830   | Development Kit for BT830 Module                         |

## 17.1 General Comments

This is a preliminary datasheet. Please check with Laird for the latest information before commencing a design. If in doubt, ask.

https://connectivity.lairdtech.com

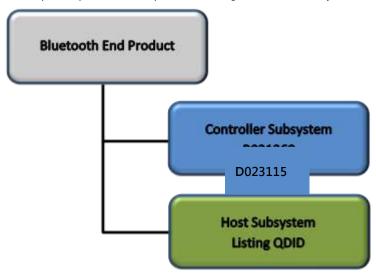

#### 18 BLUETOOTH SIG APPROVALS

#### 18.1 Application Note: Subsystem Combinations

This application note covers the procedure for generating a new Declaration ID for a Subsystem combination on the Bluetooth SIG website. In the instance of subsystems, a member can combine two or more subsystems to create a complete Bluetooth End Product solution.

Subsystem listings referenced as an example:

| Design Name                         | Owner                    | Declaration ID | Link to listing on the SIG website                      |

|-------------------------------------|--------------------------|----------------|---------------------------------------------------------|

| BT830                               | Laird                    | D023115        | https://www.bluetooth.org/tpg/QLI_viewQDL.cfm?qid=23115 |

| Embedded CE 6.0<br>(Host Subsystem) | Microsoft<br>Corporation | B012893        | https://www.bluetooth.org/tpg/QLI_viewQDL.cfm?qid=12893 |

#### 18.1.1 Laird Customer Declaration ID Procedure

This procedure assumes that the member is simply combining two subsystems to create a new design, without any modification to the existing, qualified subsystems. This is achieved by using the Listing interface on the Bluetooth SIG website. Figure 24 shows the basic subsystem combination of a controller and host subsystem. The Controller provides the RF/BB/LM and HCI layers, with the Host providing L2CAP, SDP, GAP, RFCOMM/SPP and any other specific protocols and profiles existing in the Host subsystem listing. The design may also include a Profile Subsystem.

The controller provides the RF/BB/LM and HCI layers, with the Host providing L2CAP, SDP, GAP, RFCOMM/SPP and any other specific protocols and profiles existing in the Host subsystem listing. The design may also include a Profile Subsystem.

Figure 24: Basic subsystem combination of a controller and host subsystem

The Qualification Process requires each company to registered as a member of the Bluetooth SIG - http://www.bluetooth.org

The following link provides a link to the Bluetooth Registration page: https://www.bluetooth.org/login/register/

For each Bluetooth Design it is necessary to purchase a Declaration ID. This can be done before starting the new qualification, either through invoicing or credit card payment. The fees for the Declaration ID will depend on your membership status, please refer to the following webpage:

https://www.bluetooth.org/en-us/test-qualification/qualification-overview/fees

For a detailed procedure of how to obtain a new Declaration ID for your design, please refer to the following SIG document:

https://www.bluetooth.org/DocMan/handlers/DownloadDoc.ashx?doc\_id=283698&vId=317486

#### BT830 Datasheet

To start the listing, go to: https://www.bluetooth.org/tpg/QLI\_SDoc.cfm.

In step 1, select the option, **Reference a Qualified Design** and enter the Declaration IDs of each subsystem used in the End Product design. You can then select your pre-paid Declaration ID from the drop down menu or go to the Purchase Declaration ID page, (please note that unless the Declaration ID is pre-paid or purchased with a credit card, it will not be possible to proceed until the SIG invoice is paid.

Once all the relevant sections of step 1 are finished, complete steps 2, 3, and 4 as described in the help document. Your new Design will be listed on the SIG website and you can print your Certificate and DoC.

For further information please refer to the following training material:

https://www.bluetooth.org/en-us/test-qualification/qualification-overview/listing-process-updates