# CY28341

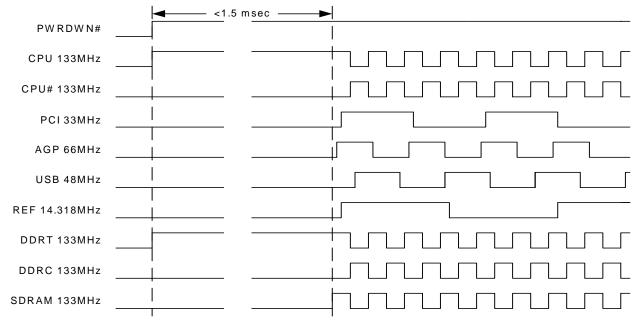

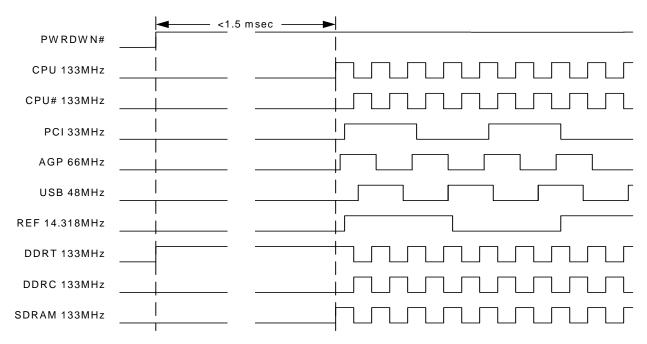

Universal Single-Chip Clock Solution for VIA P4M266/KM266 **DDR Systems**

# Features

- Supports VIA<sup>™</sup> P4M266/KM266 chipsets

- Supports Pentium® 4, Athlon<sup>™</sup> processors

- Supports two DDR DIMMS

- Supports three SDRAMS DIMMS at 100 MHz

- Provides:

- Two different programmable CPU clock pairs

- Six differential SDRAM DDR pairs

- Three low-skew/low-jitter AGP clocks

- Seven low-skew/low-jitter PCI clocks

- One 48M output for USB

- One programmable 24M or 48M for SIO

- Dial-a-Frequency<sup>™</sup> and Dial-a-dB<sup>™</sup> features

- Spread Spectrum for best electromagnetic interference (EMI) reduction

- Watchdog feature for systems recovery

- SMBus-compatible for programmability

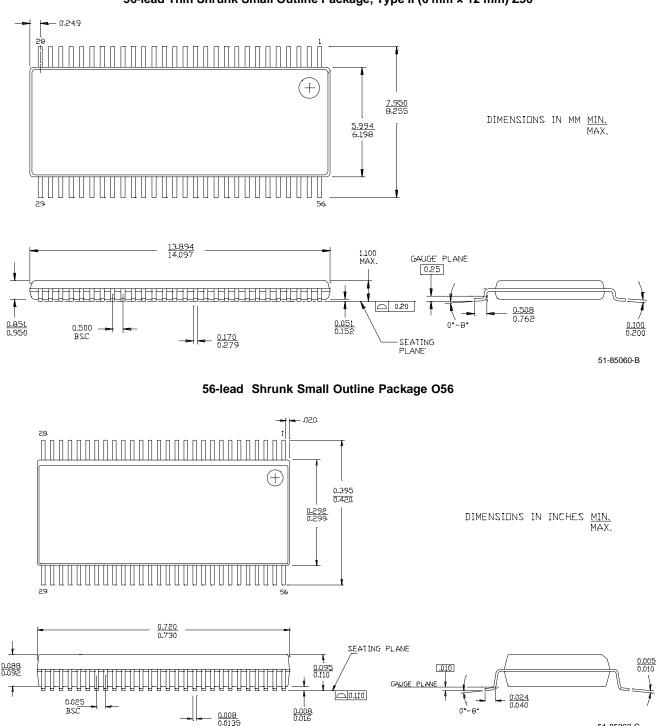

- 56-pin SSOP and TSSOP packages

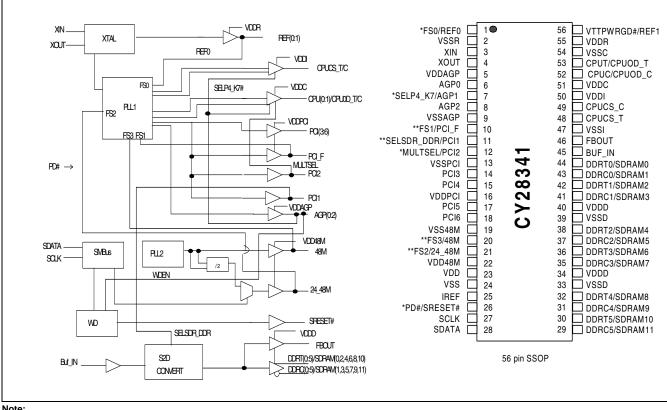

**Block Diagram**

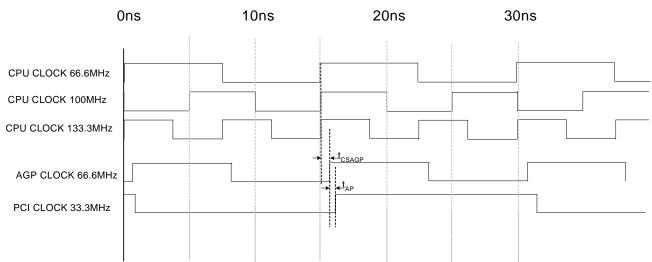

#### CPU FS(3:0) AGP PCI 0000 66.80 33.40 66.80 0001 100.00 66.80 33.40 0010 120.00 60.00 30.00 66.67 0011 133.33 33.33 0100 72.00 72.00 36.00 0101 105.00 70.00 35.00 0110 160.00 64.00 32.00 0111 140.00 70.00 35.00 1000 77.00 77.00 38.50 73.33 1001 110.00 36.67 1010 180.00 60.00 30.00 60.00 1011 150.00 30.00 1100 60.00 30.00 90.00 1101 66.67 33.33 100.00 1100 200.00 66.67 33.33 1111 133.33 66.67 33.33

Table 1. Frequency Selection Table

Pin Configuration<sup>[1]</sup>

#### Note:

1. Pins marked with [\*] have internal pull-up resistors. Pins marked with [\*\*] have internal pull-down resistors.

San Jose

٠

# Pin Description<sup>[2]</sup>

| Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Name                                  | PWR                                                                                                                                                                                                          | I/O       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | XIN                                   |                                                                                                                                                                                                              | Ι         | Oscillator Buffer Input. Connect to a crystal or to an external clock.                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | XOUT                                  | VDD                                                                                                                                                                                                          | 0         | <b>Oscillator Buffer Output</b> . Connect to a crystal. Do not connect when an external clock is applied at $X_{IN}$ .                                                                                                                                                                                                                                                                                                                                                            |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FS0/REF0                              | VDD                                                                                                                                                                                                          | I/O<br>PU | <b>Power-on Bidirectional Input/Output</b> . At power-up, FS0 is the input. When the power supply voltage crosses the input threshold voltage, FS0 state is latched and this pin becomes REF0, buffered copy of signal applied at XIN.                                                                                                                                                                                                                                            |

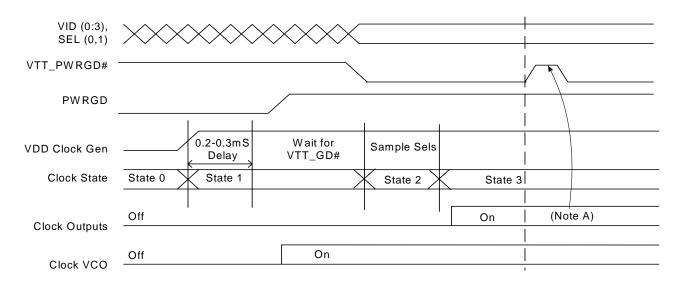

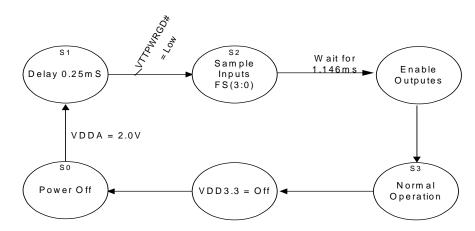

| 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | VTTPWRGD#                             | VDDR                                                                                                                                                                                                         | I         | If SELP4_K7 = 1, with a P4 processor setup as CPUT/C. At power-up,<br>VTT_PWRGD# is an input. When this input transitions to a logic LOW, the FS<br>(3:0) and MULTSEL are latched and all output clocks are enabled. After the<br>first HIGH to LOW transition on VTT_PWRGD#, this pin is ignored and will not<br>effect the behavior of the device thereafter. When the VTT_PWRGD# feature<br>is not used, please connect this signal to ground through a 10K $\Omega$ resistor. |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | REF1                                  | VDDR                                                                                                                                                                                                         | 0         | If SELP4_K7 = 0, with an Athlon (K7) processor as CPU_OD(T:C). VTT_PWRGD# function is disabled, and the feature is ignored. This pin becomes REF1 and is a buffered copy of the signal applied at $X_{IN}$ .                                                                                                                                                                                                                                                                      |

| 44,42,38,<br>36,32,30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DDRT<br>(0:5)/SDRAM(0,2,4,6,<br>8,10) | VDDD                                                                                                                                                                                                         | 0         | These pins are programmable through strapping pin11, SELSDR_DDR#.If<br>SELSDR_DDR#.= 0, these pins are configured for DDR clock outputs. They<br>are "True" copies of signal applied at Pin45, BUF_IN. In this mode, VDDD must<br>be 2.5VIf SeISDR_DDR#.= 1, these pins are configured for<br>SDRAM(0,2,4,6,8,10) single ended clock outputs, copies of (and in phase with)<br>signal applied at Pin45, BUF_IN. In this mode, VDDD must be 3.3V                                   |

| 43,41,37<br>35,31,29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DDRC<br>(0:5)/SDRAM(1,3,5,7,<br>9,11) | VDDD                                                                                                                                                                                                         | 0         | These pins are programmable through strapping pin11, SELSDR_DDR#.If<br>SelSDR_DDR#.= 0, these pins are configured for DDR clock outputs. They are<br>"Complementary" copies of signal applied at Pin45, BUF_IN. In this mode,<br>VDDD must be 2.5VIf SelSDR_DDR#.= 1, these pins are configured for<br>SDRAM(1,3,5,7,9,11) single-ended clock outputs, copies of (and in phase with)<br>signal applied at Pin45, BUF_IN. In this mode, VDDD must be 3.3V.                         |

| 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SELP4_K7 / AGP1                       | VDDAG<br>P                                                                                                                                                                                                   | I/O<br>PU | <b>Power-on Bidirectional Input/Output</b> . At power-up, SELP4_K7 is the input.<br>When the power supply voltage crosses the input threshold voltage, SELP4_K7<br>state is latched and this pin becomes AGP1 clock output. SELP4_K7 = 1, P4<br>mode. SELP4_K7 = 0, K7 mode.                                                                                                                                                                                                      |

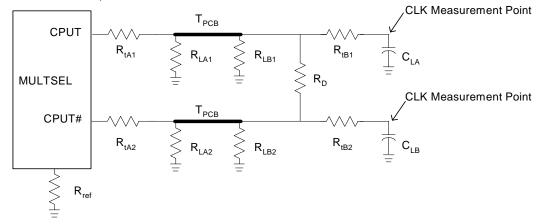

| 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | MULTSEL / PCI2                        | VDDPCI                                                                                                                                                                                                       | I/O<br>PU | <b>Power-on Bidirectional Input/Output</b> . At power-up, MULTSEL is the input. When the power supply voltage crosses the input threshold voltage, MULTSEL state is latched and this pin becomes PCI2 clock output. MULTSEL = 0, loh is 4 x IREFMULTSEL = 1, loh is 6 x IREF.                                                                                                                                                                                                     |

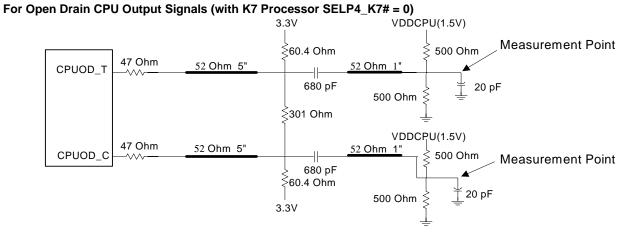

| 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CPUT/CPUOD_T                          | VDDC                                                                                                                                                                                                         | 0         | <b>3.3V CPU Clock outputs</b> . This pin is programmable through strapping pin7, SELP4_K7. If SELP4_K7 = 1, this pin is configured as the CPUT Clock Output. If SELP4_K7 = 0, this pin is configured as the CPUOD_T Open Drain Clock Output. See <i>Table 1</i> .                                                                                                                                                                                                                 |

| 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CPUC/CPUOD_C                          | VDDC                                                                                                                                                                                                         | 0         | <b>3.3V CPU Clock outputs</b> . This pin is programmable through strapping pin7, SELP4_K7. If SELP4_K7 = 1, this pin is configured as the CPUC Clock Output. If SELP4_K7 = 0, this pin is configured as the CPUOD_C Open Drain Clock Output. See <i>Table 1</i> .                                                                                                                                                                                                                 |

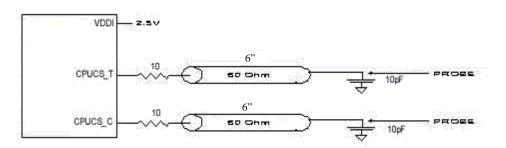

| 48,49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CPUCS_T/C                             | VDDI                                                                                                                                                                                                         | 0         | 2.5V CPU Clock Outputs for Chipset. See Table 1.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 14,15,17,<br>18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PCI (3:6)                             | VDDPCI                                                                                                                                                                                                       | 0         | PCI Clock Outputs. Are synchronous to CPU clocks. See Table 1.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10     FS1/PCI_F     VDDPCI     I/O     Power-on Bidirectional Input/Output. At put the power supply voltage crosses the input the power supply voltage crosses the power sup the power sup the power supply voltage crosses the power |                                       | <b>Power-on Bidirectional Input/Output</b> . At power-up, FS0 is the input. When the power supply voltage crosses the input threshold voltage, FS1 state is latched and this pin becomes PCI_F clock output. |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | FS3/48M                               | VDD48M                                                                                                                                                                                                       | I/O<br>PD | <b>Power-on Bidirectional Input/Output</b> . At power-up, FS3 is the input. When the power supply voltage crosses the input threshold voltage, FS3 state is latched and this pin becomes 48M, a USB clock output.                                                                                                                                                                                                                                                                 |

# Pin Description<sup>[2]</sup> (continued)

| Pin   | Name                 | PWR        | I/O       | Description                                                                                                                                                                                                                                                                                                                                                                  |

|-------|----------------------|------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11    | SELSDR_DDR#/PCI<br>1 | VDDPCI     |           | <b>Power-on Bidirectional Input/Output</b> . At power-up, SELSDR_DDR is the input. When the power supply voltage crosses the input threshold voltage, SELSDR_DDR state is latched and this pin becomes PCI clock output.SelSDR_DDR#. = 0, DDR Mode. SelSDR_DDR#. = 1, SDR Mode.                                                                                              |

| 21    | FS2/24_48M           | VDD48M     |           | <b>Power-on Bidirectional Input/Output</b> . At power-up, FS2 is the input. When the power supply voltage crosses the input threshold voltage, FS2 state is latched and this pin becomes 24_48M, a SIO programmable clock output.                                                                                                                                            |

| 6     | AGP0                 | VDDAG<br>P | 0         | AGP Clock Output. Is synchronous to CPU clocks. See Table 1.                                                                                                                                                                                                                                                                                                                 |

| 8     | AGP2                 | VDDAG<br>P | 0         | AGP Clock Output. Is synchronous to CPU clocks. See Table 1.                                                                                                                                                                                                                                                                                                                 |

| 25    | IREF                 |            | Ι         | Current reference programming input for CPU buffers. A precise resistor is attached to this pin, which is connected to the internal current reference.                                                                                                                                                                                                                       |

| 28    | SDATA                |            | I/O       | Serial Data Input. Conforms to the Philips I2C specification of a Slave Receive/Transmit device. It is an input when receiving data. It is an open drain output when acknowledging or transmitting data.                                                                                                                                                                     |

| 27    | SCLK                 |            | Ι         | Serial Clock Input. Conforms to the Philips I2C specification.                                                                                                                                                                                                                                                                                                               |

| 26    | PD#/SRESET#          |            | I/O<br>PU | <b>Power-down Input/System Reset Control Output</b> . If Byte6 Bit7 = 0, this pin becomes a SRESET# open drain output, and the internal pulled up is not active. See system reset description. If Byte6 Bit7 = 1 (default), this pin becomes PD# input with an internal pull-up. When PD# is asserted LOW, the device enters power-down mode. See power management function. |

| 45    | BUF_IN               |            |           | If SelSDR_DDR#.= 0, 2.5V CMOS type input to the DDR differential buffers.If SelSDR_DDR#.= 1, 3.3V CMOS type input to the SDR buffer.                                                                                                                                                                                                                                         |

| 46    | FBOUT                |            |           | If SelSDR_DDR#.= 0, 2.5V single ended SDRAM buffered output of the signal applied at BUF_IN. It is in phase with the DDRT(0:5) signals.If SelSDR_DDR#.= 1, 3.3V single ended SDRAM buffered output of the signal applied at BUF_IN. It is in phase with the SDRAM(0:11) signals                                                                                              |

| 5     | VDDAGP               |            |           | 3.3V Power Supply for AGP clocks                                                                                                                                                                                                                                                                                                                                             |

| 51    | VDDC                 |            |           | 3.3V Power Supply for CPUT/C clocks                                                                                                                                                                                                                                                                                                                                          |

| 16    | VDDPCI               |            |           | 3.3V Power Supply for PCI clocks                                                                                                                                                                                                                                                                                                                                             |

| 55    | VDDR                 |            |           | 3.3V Power Supply for REF clock                                                                                                                                                                                                                                                                                                                                              |

| 50    | VDDI                 |            |           | 2.5V Power Supply for CPUCS_T/C clocks                                                                                                                                                                                                                                                                                                                                       |

| 22    | VDD48M               |            |           | 3.3V Power Supply for 48M                                                                                                                                                                                                                                                                                                                                                    |

| 23    | VDD                  |            |           | 3.3V Common Power Supply                                                                                                                                                                                                                                                                                                                                                     |

| 34,40 | VDDD                 |            |           | If SelSDR_DDR#.= 0, 2.5V Power Supply for DDR clocksIf SelSDR_DDR#.= 1, 3.3V Power Supply for SDR clocks.                                                                                                                                                                                                                                                                    |

| 9     | VSSAGP               |            |           | Ground for AGP clocks                                                                                                                                                                                                                                                                                                                                                        |

| 13    | VSSPCI               |            |           | Ground for PCI clocks                                                                                                                                                                                                                                                                                                                                                        |

| 54    | VSSC                 |            |           | Ground for CPUT/C clocks                                                                                                                                                                                                                                                                                                                                                     |

| 33,39 | VSSD                 |            |           | Ground for DDR clocks                                                                                                                                                                                                                                                                                                                                                        |

| 19    | VSS48M               |            |           | Ground for 48M clock                                                                                                                                                                                                                                                                                                                                                         |

| 47    | VSSI                 |            |           | Ground for ICPUCS_T/C clocks                                                                                                                                                                                                                                                                                                                                                 |

| 24    | VSS                  |            |           | Common Ground                                                                                                                                                                                                                                                                                                                                                                |

| Note: | - I                  |            |           |                                                                                                                                                                                                                                                                                                                                                                              |

2. PU = internal Pull-up. PD = internal Pull-down. Typically = 250 kW (range 200 kW to 500 kW).

#### Serial Data Interface

To enhance the flexibility and function of the clock synthesizer, a two-signal serial interface is provided. Through the Serial Data Interface, various device functions such as individual clock output buffers, etc., can be individually enabled or disabled.

The registers associated with the Serial Data Interface initializes to their default setting upon power-up, and therefore use of this interface is optional. Clock device register changes are normally made upon system initialization, if any are required. The interface can also be used during system operation for power management functions.

#### Table 2. Command Code Definition

#### Data Protocol

The clock driver serial protocol accepts Byte Write, Byte Read, Block Write, and Block Read operation from the controller. For Block Write/Read operation, the bytes must be accessed in sequential order from lowest to highest byte (most significant bit first) with the ability to stop after any complete byte has been transferred. For Byte Write and Byte Read operations, the system controller can access individual indexed bytes. The offset of the indexed byte is encoded in the command code, as described in *Table 2*.

The Block Write and Block Read protocol is outlined in *Table 3*, while *Table 4* outlines the corresponding Byte Write and Byte Read protocol. The slave receiver address is 11010010 (D2h).

| Bit | Description                                                                                                                 |

|-----|-----------------------------------------------------------------------------------------------------------------------------|

|     | 0 = Block Read or Block Write operation<br>1 = Byte Read or Byte Write operation                                            |

|     | Byte offset for Byte Read or Byte Write operation. For Block Read or Block Write operations, these bits should be "0000000" |

Table 3. Block Read and Block Write Protocol

|       | Block Write Protocol                                          |       | Block Read Protocol                                           |

|-------|---------------------------------------------------------------|-------|---------------------------------------------------------------|

| Bit   | Description                                                   | Bit   | Description                                                   |

| 1     | Start                                                         | 1     | Start                                                         |

| 2:8   | Slave address – 7 bits                                        | 2:8   | Slave address – 7 bits                                        |

| 9     | Write                                                         | 9     | Write                                                         |

| 10    | Acknowledge from slave                                        | 10    | Acknowledge from slave                                        |

| 11:18 | Command Code – 8-bit "00000000" stands for<br>Block operation | 11:18 | Command Code – 8-bit "00000000" stands for<br>Block operation |

| 19    | Acknowledge from slave                                        | 19    | Acknowledge from slave                                        |

| 20:27 | Byte Count – 8 bits                                           | 20    | Repeat start                                                  |

| 28    | Acknowledge from slave                                        | 21:27 | Slave address – 7 bits                                        |

| 29:36 | Data byte 0 – 8 bits                                          | 28    | Read                                                          |

| 37    | Acknowledge from slave                                        | 29    | Acknowledge from slave                                        |

| 38:45 | Data byte 1 – 8 bits                                          | 30:37 | Byte count from slave – 8 bits                                |

| 46    | Acknowledge from slave                                        | 38    | Acknowledge                                                   |

|       | Data Byte N/Slave acknowledge                                 | 39:46 | Data byte from slave – 8 bits                                 |

|       | Data Byte N – 8 bits                                          | 47    | Acknowledge                                                   |

|       | Acknowledge from slave                                        | 48:55 | Data byte from slave – 8 bits                                 |

|       | Stop                                                          | 56    | Acknowledge                                                   |

|       |                                                               |       | Data bytes from slave/Acknowledge                             |

|       |                                                               |       | Data byte N from slave – 8 bits                               |

|       |                                                               |       | Not Acknowledge                                               |

|       |                                                               |       | Stop                                                          |

# Table 4. Byte Read and Byte Write Protocol

|       | Byte Write Protocol                                                                                                                          |       | Byte Read Protocol                                                                                                                           |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Bit   | Description                                                                                                                                  | Bit   | Description                                                                                                                                  |

| 1     | Start                                                                                                                                        | 1     | Start                                                                                                                                        |

| 2:8   | Slave address – 7 bits                                                                                                                       | 2:8   | Slave address – 7 bits                                                                                                                       |

| 9     | Write                                                                                                                                        | 9     | Write                                                                                                                                        |

| 10    | Acknowledge from slave                                                                                                                       | 10    | Acknowledge from slave                                                                                                                       |

| 11:18 | Command Code – 8 bits "1xxxxxx" stands for<br>byte operationbit[6:0] of the command code<br>represents the offset of the byte to be accessed | 11:18 | Command Code – 8 bits "1xxxxxx" stands for<br>byte operationbit[6:0] of the command code<br>represents the offset of the byte to be accessed |

| 19    | Acknowledge from slave                                                                                                                       | 19    | Acknowledge from slave                                                                                                                       |

| 20:27 | Byte Count – 8 bits                                                                                                                          | 20    | Repeat start                                                                                                                                 |

| 28    | Acknowledge from slave                                                                                                                       | 21:27 | Slave address – 7 bits                                                                                                                       |

| 29    | Stop                                                                                                                                         | 28    | Read                                                                                                                                         |

|       |                                                                                                                                              | 29    | Acknowledge from slave                                                                                                                       |

|       |                                                                                                                                              | 30:37 | Data byte from slave – 8 bits                                                                                                                |

|       |                                                                                                                                              | 38    | Not Acknowledge                                                                                                                              |

|       |                                                                                                                                              | 39    | Stop                                                                                                                                         |

# **Serial Control Registers**

# Byte 0: Frequency Select Register

| Bit | @Pup        | Pin# | Name       | Description                                                                                                                                                                                                                                    |

|-----|-------------|------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | 0           |      | Reserved   | Reserved                                                                                                                                                                                                                                       |

| 6   | H/W Setting | 21   | FS2        | For Selecting Frequencies see Table 1.                                                                                                                                                                                                         |

| 5   | H/W Setting | 10   | FS1        | For Selecting Frequencies see Table 1.                                                                                                                                                                                                         |

| 4   | H/W Setting | 1    | FS0        | For Selecting Frequencies see Table 1.                                                                                                                                                                                                         |

| 3   | 0           |      |            | If this bit is programmed to "1," it enables Write to bits (6:4,1) for selecting the frequency via software (SMBus). If this bit is programmed to a "0," it enables only Read of bits (6:4,1), which reflects the hardware setting of FS(0:3). |

| 2   | H/W Setting | 11   | SELSDR_DDR | Only for reading the hardware setting of the SDRAM interface mode, status of SELSDR_DDR# strapping.                                                                                                                                            |

| 1   | H/W Setting | 20   | FS3        | For Selecting frequencies see Table 1.                                                                                                                                                                                                         |

| 0   | H/W Setting | 7    | SELP4_K7   | Only for reading the hardware setting of the CPU interface mode, status of SELP4_K7# strapping.                                                                                                                                                |

# Byte 1: CPU Clocks Register

| Bit | @Pup | Pin#  | Name                         | Description                                                                                                                                                                                              |

|-----|------|-------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | 0    |       | MODE                         | 0 = Down Spread. 1 = Center Spread. See Table 9.                                                                                                                                                         |

| 6   | 1    |       | SSCG                         | 1 = Enable (default). 0 = Disable                                                                                                                                                                        |

| 5   | 1    |       | SST1                         | Select spread bandwidth. See Table 9.                                                                                                                                                                    |

| 4   | 1    |       | SST0                         | Select spread bandwidth. See Table 9.                                                                                                                                                                    |

| 3   | 1    | 48,49 | CPUCS_T, CPUCS_C             | 1 = output enabled (running). 0 = output disabled asynchronously in a LOW state.                                                                                                                         |

| 2   | 1    | 53,52 | CPUT/CPUOD_T<br>CPUC/CPUOD_C | 1 = output enabled (running). 0 = output disable.                                                                                                                                                        |

| 1   | 1    | 53,52 | CPUT/C                       | In K7 mode, this bit is ignored.In P4 mode, 0 = when PD# asserted LOW,<br>CPUT stops in a HIGH state, CPUC stops in a LOW state. In P4 mode, 1 =<br>when PD# asserted LOW, CPUT and CPUC stop in High-Z. |

| 0   | 1    | 11    | MULT0                        | Only For reading the hardware setting of the Pin11 MULT0 value.                                                                                                                                          |

# Byte 2: PCI Clock Register

| Bit | @Pup | Pin# | Name    | Description                                                                      |

|-----|------|------|---------|----------------------------------------------------------------------------------|

| 7   | 0    |      | PCI_DRV | PCI clock output drive strength 0 = Normal, 1 = increase the drive strength 20%. |

| 6   | 1    | 10   | PCI_F   | 1 = output enabled (running). 0 = output disabled asynchronously in a LOW state. |

| 5   | 1    | 18   | PCI6    | 1 = output enabled (running). 0 = output disabled asynchronously in a LOW state. |

| 4   | 1    | 17   | PCI5    | 1 = output enabled (running). 0 = output disabled asynchronously in a LOW state. |

| 3   | 1    | 15   | PCI4    | 1 = output enabled (running). 0 = output disabled asynchronously in a LOW state. |

| 2   | 1    | 14   | PCI3    | 1 = output enabled (running). 0 = output disabled asynchronously in a LOW state. |

| 1   | 1    | 12   | PCI2    | 1 = output enabled (running). 0 = output disabled asynchronously in a LOW state. |

| 0   | 1    | 11   | PCI1    | 1 = output enabled (running). 0 = output disabled asynchronously in a LOW state. |

#### Byte 3: AGP/Peripheral Clocks Register

| Bit | @Pup | Pin#  | Name   | Description                                                                                                              |  |

|-----|------|-------|--------|--------------------------------------------------------------------------------------------------------------------------|--|

| 7   | 0    | 21    | 24_48M | "0" = pin21 output is 24MHz. Writing a "1" into this register asynchronously changes the frequency at pin21 to 48 MHz.   |  |

| 6   | 1    | 20    | 48MHz  | 1 = output enabled (running). 0 = output disabled asynchronously in a LOW state.                                         |  |

| 5   | 1    | 21    | 24_48M | 1 = output enabled (running). 0 = output disabled asynchronously in a LOW state.                                         |  |

| 4   | 0    | 6,7,8 | DASAG1 | Programming these bits allow shifting skew of the AGP(0:2) signals relative to their default value. See <i>Table 5</i> . |  |

| 3   | 0    | 6,7,8 | DASAG0 |                                                                                                                          |  |

| 2   | 1    | 8     | AGP2   | 1 = output enabled (running). 0 = output disabled asynchronously in a LOW state.                                         |  |

| 1   | 1    | 7     | AGP1   | 1 = output enabled (running). 0 = output disabled asynchronously in a LOW state.                                         |  |

| 0   | 1    | 6     | AGP0   | 1 = output enabled (running). 0 = output disabled asynchronously in a LOW state.                                         |  |

#### Table 5. Dial-a-Skew<sup>™</sup> AGP(0:2)

| DASAG (1:0) | AGP(0:2) Skew Shift |

|-------------|---------------------|

| 00          | Default             |

| 01          | –280 ps             |

| 10          | +280 ps             |

| 11          | +480 ps             |

# Byte 4: Peripheral Clocks Register

| Bit | @Pup | Pin#  | Name   | Description                                                                                                                                     |  |

|-----|------|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7   | 1    | 20    | 48M    | 1 = normal strength, 0 = high strength<br>1 = normal strength, 0 = high strength                                                                |  |

| 6   | 1    | 21    | 24_48M | 1 = normal strength, 0 = high strength<br>1 = normal strength, 0 = high strength                                                                |  |

| 5   | 0    | 6,7,8 | DARAG1 | Programming these bits allow modifying the frequency ratio of the AGP(2:0), PCI(6:1, F) clocks relative to the CPU clocks. See <i>Table 6</i> . |  |

| 4   | 0    | 6,7,8 | DARAG0 |                                                                                                                                                 |  |

| 3   | 1    | 1     | REF0   | 1 = output enabled (running). 0 = output disabled asynchronously in a LOW state.                                                                |  |

| 2   | 1    | 56    | REF1   | 1 = output enabled (running). 0 = output disabled asynchronously in a LOW state. (K7 Mode only.)                                                |  |

| 1   | 1    | 1     | REF0   | 1 = normal strength, 0 = high strength                                                                                                          |  |

| 0   | 1    | 56    | REF1   | 1 = normal strength, 0 = high strength (K7 Mode only.)                                                                                          |  |

# Table 6. Dial-A-Ratio<sup>™</sup> AGP(0:2)

| DARAG (1:0) | CU/AGP Ratio                |

|-------------|-----------------------------|

| 00          | Frequency Selection Default |

| 01          | 2/1                         |