### NFC frontend CLRC663 *plus* push your design further – best performance at lowest power consumption

LAURENT DARDÉ NEXT GENERATION HIGH-PERFORMANCE JÜRGEN SCHRODER MULTI-PROTOCOL NFC FRONTEND

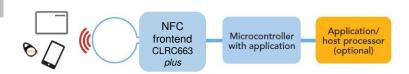

#### **NFC product portfolio**

#### **Connected NFC tag solutions**

Our connected NFC tag solutions include a NFC Forum RF interface, an EEPROM, and a field-detection function (NTAG F) or a field- detection function with an I<sup>2</sup>C interface (NTAG I<sup>2</sup>C *plus*).

#### NFC frontend solutions

Our standalone frontends, which work seamlessly with the NFC Reader Library, are the most flexible way to add NFC to a system.

#### **NFC controller solutions**

Our NFC controller solutions enable higher integration with fewer components combining an NFC frontend with an advanced 32-bit microcontroller.

Options include integrated firmware, for an easy, standardized interface, or a freely programmable microcontroller with the ability to load fully-custom applications.

#### **Integrated Firmware**

#### **Customizable Firmware**

### CLRC663 plus – push your design further

### CLRC663 plus – product features

#### **Characteristics**

- 350mA maximum operating transmitter current with limiting value of 500mA

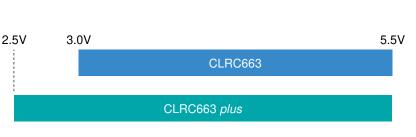

- > Power supply voltage: 2.5 to 5.5V

- > Extended operating temperature range: -40 to +105°C

- > 512byte FIFO buffer for highest transaction performance

- Flexible and efficient power saving modes including hard power down, standby and low-power card detection

- Integrated PLL provides external system clock from 27.12MHz RF crystal

#### Licenses and supported standards

- Includes NXP ISO/IEC14443-A, NXP MIFARE<sup>®</sup> and Innovatron ISO/IEC14443-B licenses

- > Crypto 1 intellectual property licensing rights

- > Hardware supports for MIFARE Classic encryption

- EMVCo 2.6 L1 analog compliancy on RF level and digital compliancy with NXP NFC reader library

#### Interfaces

- Host interfaces: SPI (10Mbit/s), I<sup>2</sup>C (1000kbit/s) and UART (1228.8kbit/s)

- SAM interface in X-mode

- Up-to 8 general purpose inputs/outputs

#### Supported RF protocols

#### **Reader and Writer mode**

- > ISO/IEC 14443A/MIFARE

- > ISO/IEC 14443B

- > JIS X 6319-4 (comparable with FeliCa1 scheme)

- > ISO/IEC 15693 (ICODE-SLIX, ICODE-DNA)

- > ISO/IEC 18000-3 mode 3/ EPC Class-1 HF (ICODE-ILT)

#### Peer to Peer mode

Passive-Initiator according to ISO/IEC 14443A (106kbit/s) and FeliCa (212 and 424kbit/s)

#### Allows to read and write

- All MIFARE<sup>®</sup> family: Ultralight, Classic 1K & 4K, DESFire EV1 & EV2 and Plus EV1

- All NTAG<sup>®</sup> family incl. NTAG I<sup>2</sup>C plus

- > All SmartMX<sup>®</sup> family incl. SmartMX2 P40 & P60

#### Packages

- > HVQFN32

- > Wettable flanks

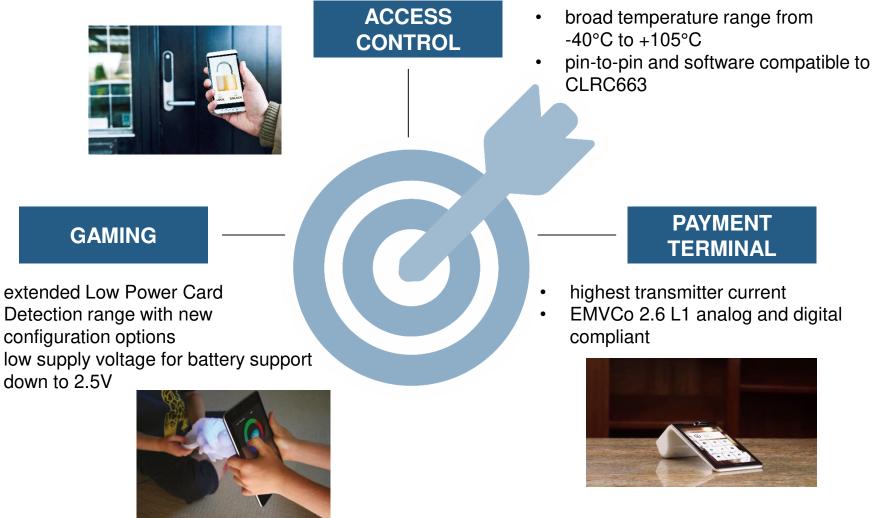

### CLRC663 plus - target markets

•

POSITIONING

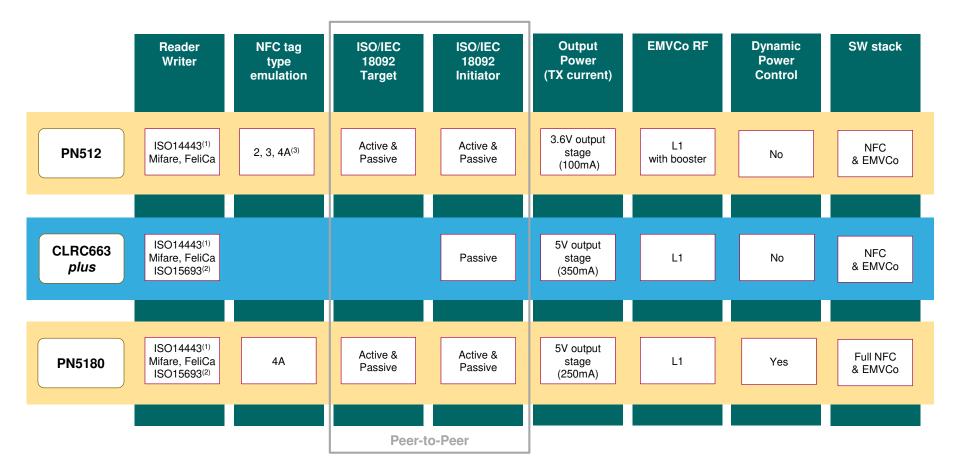

### CLRC663 plus vs. other NXP NFC frontends

- 1. ISO/IEC14443

- 2. ISO/IEC15693

- 3. No software available for NFC tag type 2 and 3 emulation

### CLRC663 plus vs. PN5180 and PN7462

| Feature                                                | CLRC663 plus                    | PN5180                     | PN7462                                | Comment                                                                                        |

|--------------------------------------------------------|---------------------------------|----------------------------|---------------------------------------|------------------------------------------------------------------------------------------------|

| Package                                                | HVQFN32                         | HVQFN40<br>TFBGA64         | HVQFN64                               | CLRC663 <i>plus</i> is pin-to-pin compatible with CLRC663                                      |

| RF transmitter supply voltage                          | 2.5 to 5.5V                     | 2.7 to 5.5V                | 3 to 5.5V                             | CLRC663 <i>plus</i> enables better support for battery powered systems                         |

| General Purpose Input/Output pins (e.g. to drive LEDs) | 4<br>up-to 8                    | up-to 7<br>outputs only    | 12<br>up-to 21                        | PN5180 has up-to 7 general purpose outputs on TFBGA64 package only                             |

| Max. operating transmitter current                     | 350mA<br>(lim. 500mA)           | 250mA<br>with DPC          | 250mA<br>with DPC                     | CLRC663 <i>plus</i> enables more flexibility in the antenna design                             |

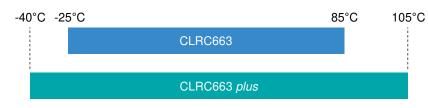

| Temperature range                                      | -40 to +105°C                   | -30 to +85°C               | -40 to +85°C                          | CLRC663 <i>plus</i> has an automotive or industrial temperature range                          |

| Low power card detection                               | range: very good<br>power: best | range: best<br>power: good | range: best<br>power: good            | CLRC663 <i>plus</i> offers the lowest power consumption                                        |

| Complete set of field proven software libraries        | NFC &<br>EMVCo                  | Full NFC<br>& EMVCo        | Full NFC<br>& EMVCo                   | Full NFC forum certified library; EMVCo 2.6                                                    |

| Waveform Control                                       | Yes                             | Yes<br>(adaptive)          | Yes<br>(adaptive)                     | Adaptive Waveform Control improves wave<br>shape stability under detuned conditions            |

| Adaptive Range Control                                 | No                              | Yes                        | Yes                                   | Adaptive Range Control increases sensibility<br>and robustness under detuned conditions        |

| Freely programmable MCU (flash)                        | No                              | No                         | Cortex M0<br>(160kB)                  | PN7462 enables an 1-chip reader solution                                                       |

| Host interfaces                                        | SPI, I <sup>2</sup> C, UART     | SPI                        | USB, HSUART,<br>SPI, I <sup>2</sup> C | PN7462 has also two master interfaces (SPI, I <sup>2</sup> C) and one contact reader interface |

| SAM Interface                                          | Yes<br>with X-mode              | No                         | Yes                                   | The SAM interface allows to store keys in a secure container                                   |

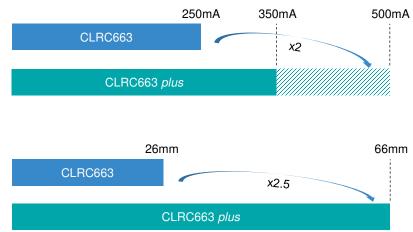

## CLRC663 *plus* vs. CLRC663

### CLRC663 plus vs. CLRC663

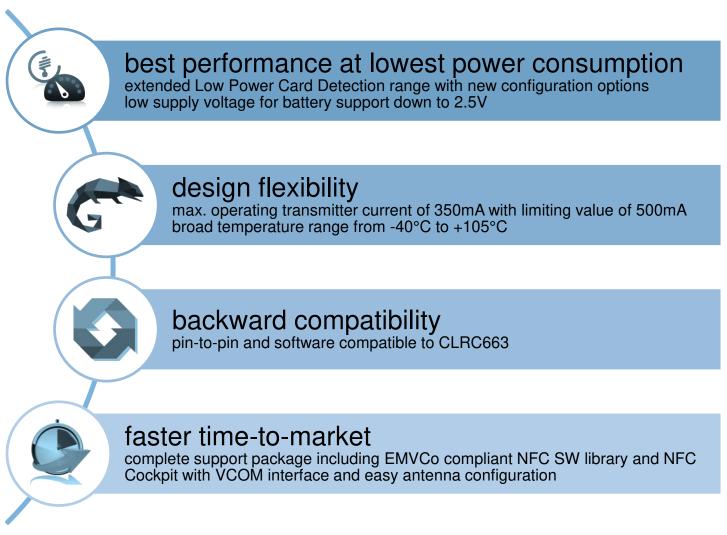

Maximum operating transmitter current increases by 40% for CLRC663 *plus* with 2x the limiting value of the CLRC663

CLRC663 *plus* has new configuration options<sup>(2)</sup> enabling up-to 2.5x the detection range in LPCD<sup>(1)</sup> mode

CLRC663 *plus* has an automotive or industrial operating temperature range: -40 to +105°C

CLRC663 *plus* enables better support for battery powered systems

New LPCD configuration options are Charge Pump (enabled/disabled) and LPCD Filter (enabled/disabled)

### CLRC663 *plus* – LPCD in details

| Card type                       | Standard<br>(CLRC663) | Charge pump<br>enabled | LPCD_FILTER<br>enabled | Charge pump<br>+<br>LPCD_FILTER<br>enabled |

|---------------------------------|-----------------------|------------------------|------------------------|--------------------------------------------|

| MIFARE <sup>®</sup> Ultralight  | 11 mm <sup>(2)</sup>  | 16 mm                  | 29 mm                  | 25 mm                                      |

| NTAG                            | 19 mm                 | 24 mm                  | 37 mm                  | 33 mm                                      |

| MIFARE DESFire <sup>®</sup> EV2 | 19 mm                 | 24 mm                  | 39 mm                  | 35 mm                                      |

| JCOP DIF                        | 12 mm                 | 17 mm                  | 30 mm                  | 27 mm                                      |

| ISO RefPICC Class 6             | 4 mm                  | 7 mm                   | 18 mm                  | 23 mm                                      |

| EMVCo RefPICC                   | 26 mm                 | 29 mm                  | 57 mm                  | 66 mm                                      |

- The basic idea of the LPCD<sup>(1)</sup> is to provide a function that turns off the RF field when no card is used. This saves energy and allows battery powered NFC Reader designs

- The CLRC663 and CLRC663 plus offer a standalone LPCD function, which replaces the normal active card polling that is triggered by the host µController

- CLRC663 plus offers additional features to extend the LPCD performance

- Charge Pump increases the RF field strength during the RF-on time

- LPCD Filter reduces the risk of fail detections especially in case of spike noise

(CLEV6630B) operated with external power supply at room temperature

### CLRC663 plus – wettable flank package

- In the case of standard HVQFN packages (e.g. CLRC663 family), there is no exposed pin to visually determine whether or not the package is successfully soldered onto the PCB. The package edge has exposed copper for the terminals, these are prone to oxidation, making sidewall solder wetting difficult

- The CLRC663 plus, with wettable flank HVQFN package, enables 100% automatic visual inspection post-assembly ensuring higher quality of assembly

## **TECHNICAL OVERVIEW**

### CLRC663 plus – quick references

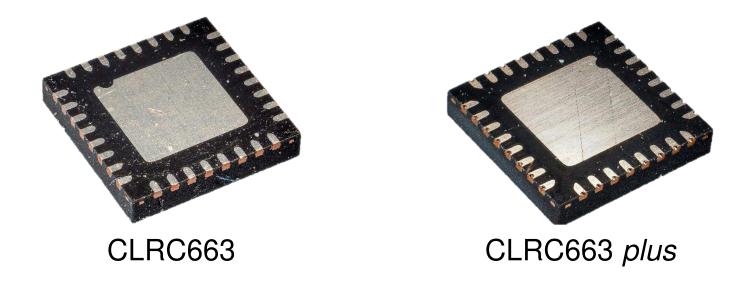

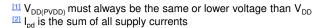

- The **analog interface** handles the modulation and demodulation of the antenna signals for the contactless interface.

- The contactless UART manages the protocol dependency of the contactless interface settings managed by the host

- The FIFO buffer ensures fast and convenient data transfer between host and the contactless UART

- The register bank contains the settings for the analog and digital functionality

| Symbol                | Parameter           | Conditions                                                        | Min | Тур | Max             | Unit |

|-----------------------|---------------------|-------------------------------------------------------------------|-----|-----|-----------------|------|

| V <sub>DD</sub>       | supply voltage      |                                                                   | 2.5 | 5.0 | 5.5             | V    |

| V <sub>DD(PVDD)</sub> | PVDD supply voltage | <u>U</u>                                                          | 2.5 | 5.0 | V <sub>DD</sub> | V    |

| V <sub>DD(TVDD)</sub> | TVDD supply voltage |                                                                   | 2.5 | 5.0 | 5.5             | V    |

| I <sub>pd</sub>       | power-down current  | PDOWN pin pulled HIGH [2]                                         | -   | 8   | 40              | nA   |

| IDD                   | supply current      |                                                                   | -   | 17  | 20              | mA   |

| I <sub>DD(TVDD)</sub> | TVDD supply current | transmitter permanent active                                      | -   | 180 | 350             | mA   |

|                       |                     | short term transmitter current                                    | -   |     | 500             | mA   |

| T <sub>amb</sub>      | ambient temperature | device mounted on PCB which<br>allows sufficient heat dissipation | -40 | +25 | +105            | °C   |

| T <sub>stg</sub>      | storage temperature | no supply voltage applied                                         | -55 | +25 | +150            | °C   |

#### CLRC663 plus – block diagram

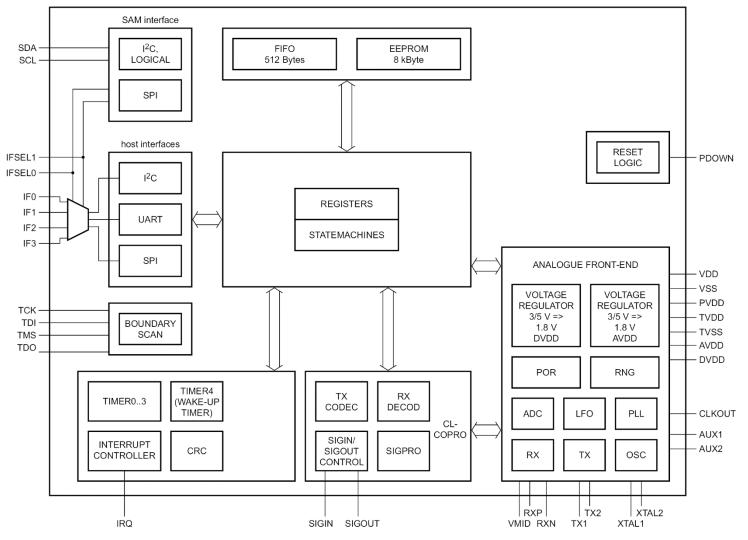

### CLRC663 plus – pinning

| Pin | Symbol        | Туре | Description                                                                                                                                                      |

|-----|---------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | TDO / OUTO    | 0    | test data output for boundary scan interface / general purpose output 0                                                                                          |

| 2   | TDI / OUT1    | 1    | test data input boundary scan interface / general purpose output 1                                                                                               |

| 3   | TMS / OUT2    | I    | test mode select boundary scan interface / general purpose output 2                                                                                              |

| 4   | TCK / OUT3    | I    | test clock boundary scan interface / general purpose output 3                                                                                                    |

| 5   | SIGIN /OUT7   | I    | Contactless communication interface output. / general purpose output 7                                                                                           |

| 6   | SIGOUT        | 0    | Contactless communication interface input.                                                                                                                       |

| 7   | DVDD          | PWR  | digital power supply buffer [1]                                                                                                                                  |

| 8   | VDD           | PWR  | power supply                                                                                                                                                     |

| 9   | AVDD          | PWR  | analog power supply buffer [1]                                                                                                                                   |

| 10  | AUX1          | 0    | auxiliary outputs: Pin is used for analog test signal                                                                                                            |

| 11  | AUX2          | 0    | auxiliary outputs: Pin is used for analog test signal                                                                                                            |

| 12  | RXP           | I    | receiver input pin for the received RF signal.                                                                                                                   |

| 13  | RXN           | I    | receiver input pin for the received RF signal.                                                                                                                   |

| 14  | VMID          | PWR  | internal receiver reference voltage [1]                                                                                                                          |

| 15  | TX2           | 0    | transmitter 2: delivers the modulated 13.56 MHz carrier                                                                                                          |

| 16  | TVSS          | PWR  | transmitter ground, supplies the output stage of TX1, TX2                                                                                                        |

| 17  | TX1           | 0    | transmitter 1: delivers the modulated 13.56 MHz carrier                                                                                                          |

| 18  | TVDD          | PWR  | transmitter voltage supply                                                                                                                                       |

| 19  | XTAL1         | I    | crystal oscillator input: Input to the inverting amplifier of the oscillator. This pin is<br>also the input for an externally generated clock (fosc = 27.12 MHz) |

| 20  | XTAL2         | 0    | crystal oscillator output: output of the inverting amplifier of the oscillator                                                                                   |

| 21  | PDOWN         | I    | Power Down (RESET)                                                                                                                                               |

| 22  | CLKOUT / OUT6 | 0    | clock output / general purpose output 6                                                                                                                          |

| 23  | SCL           | 0    | Serial Clock line                                                                                                                                                |

| 24  | SDA           | I/O  | Serial Data Line                                                                                                                                                 |

| 25  | PVDD          | PWR  | pad power supply                                                                                                                                                 |

| 26  | IFSEL0 / OUT4 | 1    | host interface selection 0 / general purpose output 4                                                                                                            |

| 27  | IFSEL1 / OUT5 | I    | host interface selection 1 / general purpose output 5                                                                                                            |

| 28  | IFO           | I/O  | interface pin, multifunction pin: Can be assigned to host interface RS232, SPI, I <sup>2</sup> C, I <sup>2</sup> C-L                                             |

| 29  | IF1           | I/O  | interface pin, multifunction pin: Can be assigned to host interface SPI, I <sup>2</sup> C, I <sup>2</sup> C-L                                                    |

| 30  | IF2           | I/O  | interface pin, multifunction pin: Can be assigned to host interface RS232, SPI, $l^2C, l^2C\text{-}L$                                                            |

| 31  | IF3           | I/O  | interface pin, multifunction pin: Can be assigned to host interface RS232, SPI, I^2C, I^2C-L                                                                     |

| 32  | IRQ           | 0    | interrupt request: output to signal an interrupt event                                                                                                           |

| 33  | VSS           | PWR  | ground and heat sink connection                                                                                                                                  |

<sup>111</sup> This pin is used for connection of a buffer capacitor. Connection of a supply voltage might damage the device.

## PRODUCT SUPPORT PACKAGE

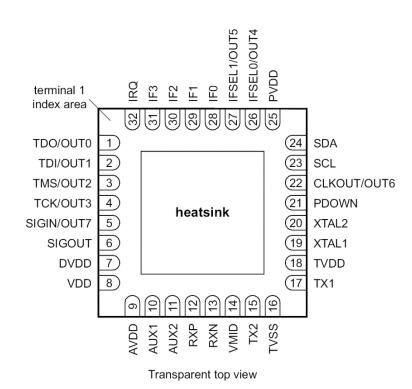

### CLRC663 plus - development kit and board

- The OM26630FDK is a flexible and easy to use frontend development kit for CLRC663 plus

- It contains a CLEV6630B board fully supported by the NFC Cockpit and the NFC Reader Library with a 65\*65mm<sup>2</sup> antenna optimized for EMVCo applications and a 30\*50mm<sup>2</sup> antenna with matching components optimized for Access Management applications

- It also includes, 3 small antenna matching PCBs for implementation of custom antenna matching circuit, NFC sample cards based on NTAG216F (NFC Forum type 2 tag) and DESFire<sup>®</sup> EV2, and 10 CLRC663 *plus* samples in HVQFN package

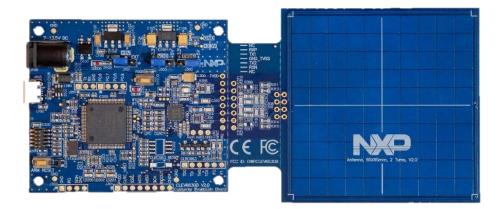

### CLRC663 plus – NFC Cockpit

| egisters/EEProm access                                                                 | Operation              |                           |                | Type Cards LPCD DP                       | C Secondary Firmwa    | re AWC Test Signal |                                    |

|----------------------------------------------------------------------------------------|------------------------|---------------------------|----------------|------------------------------------------|-----------------------|--------------------|------------------------------------|

| X_OVERSHOOT_CON + Read                                                                 | © EEPROM               |                           |                | Type A Type B Type                       | F ISO15693            |                    |                                    |

| legister address: 0x15 Write                                                           | Register               |                           |                | Protocol Laver                           |                       |                    |                                    |

|                                                                                        |                        |                           |                | Layer 14443-3a                           |                       | Load               | Protocol ISO14443-A                |

| t selection:                                                                           |                        |                           |                | Activate Layer3                          | Halt                  | 106 k8d/s •        | Load Protocol                      |

| nory                                                                                   |                        |                           |                | 0 ATOA: 44.03                            |                       | 100 KBB/S          | Load Protocol                      |

| 00000000                                                                               |                        |                           |                | SAK: 0x20                                | Re-Activate L3        |                    | Single/Endless REQ<br>Endless REQA |

| Write Operation                                                                        |                        | 0                         | (FS)           | G Layer 14443-4a                         |                       | Inter-REQ:         | 0 ms                               |

| Single bit                                                                             |                        | RESERVED                  | K, OVERSHOOT   | OHSELAyer 14443-4a<br>Select a baud rate | 106 kBd/s •           | I RFRESET          |                                    |

| j×                                                                                     |                        | 592<br>1                  | X              | Activate Layer4                          | Deselect Card         | Time-out RFQN:     | D ms                               |

|                                                                                        |                        |                           | ······         | ATS:                                     | -                     | Single RECA        |                                    |

| EEPROM Single Byte Access<br>Address 0x00000000 Read EEPROM                            | Load EEProm            | RF Field Control          |                | Laver 14443-4: Data E                    | whange with PICC      | ( -                |                                    |

| Data 0x00 Write EEPROM                                                                 | Dumo EEProm            | Rf Field On Rf Field Off  | Rt Field Reset | Data to be send:                         | and the second second |                    |                                    |

|                                                                                        | (South Coston)         | (Theid On) [Rit Field On] | Mi rield Neset |                                          |                       | 1 2 22 1           |                                    |

| Log Monitor<br>2017.01.03 13:54:10]:INFO:SecureFWUpgr                                  | adePN5180:Entering dov | vnload mode               |                | TXCRC Enable                             | RXCRC Enable          | Send Data          |                                    |

| 2017.01.03 13:54:11]:INFO:SecureFWUpgr<br>2017.01.03 13:54:16]:INFO:BoardConnecti      |                        |                           | nen nort anain | Card response:                           |                       |                    |                                    |

| 017.01.03 13:54:16]:INFO:SecureFWUpgr                                                  | adePN5180:Resetting ch |                           | pen porcagain. | Application Laver                        |                       |                    |                                    |

| 2017.01.03 13:54:16]:INFO:SecureFWUpgr<br>2017.01.03 13:54:16]:INFO:BoardConnecti      |                        | mware Upgrade Operation I | Finished       | Command GetApplds                        | MF DesFire            |                    |                                    |

| 2017.01.03 13:54:40]:INFO:RfFieldControl<br>2017.01.03 13:54:42]:INFO:RfFieldControl   |                        |                           |                | GetApplds<br>Applications on the         |                       |                    |                                    |

| 2017.01.03 13:54:51]:INFO:RFProtocolTuni                                               | ingService_PN5180:Load |                           |                | E                                        | card:                 |                    |                                    |

| 2017.01.03 13:54:51]:INFO:TypeACardViev<br>2017.01.03 13:54:54]:INFO:RfFieldControl    | ervice:RF On           | anneas annas an Arais     |                |                                          |                       |                    |                                    |

| 2017.01.03 13:55:30]:INFO:RegistersServic<br>2017.01.03 13:55:38]:INFO:RegistersServic |                        |                           |                | •                                        | i)                    |                    |                                    |

|                                                                                        | -                      | 2011                      |                |                                          |                       |                    | <                                  |

- **NFC Cockpit** is an intuitive GUI that lets you configure and adapt CLRC663 *plus* settings without writing a single line of software code

- This Windows tool features

- direct register/EEPROM read/write access and backup of EEPROM settings

- RF field control and card operation (Type A, Type B, Type F, ISO15693)

- control of test applications like EMVCo Loopback and test signal configuration

- LPCD configuration

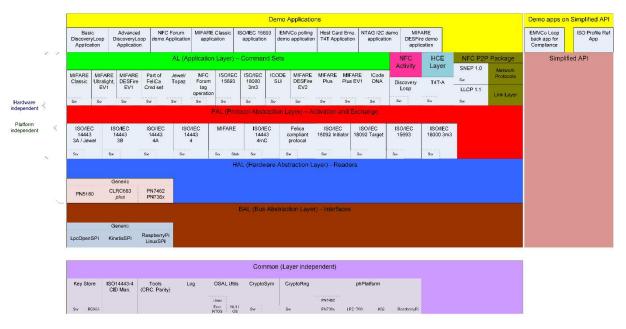

### CLRC663 plus – NFC Reader library

- Scalability enable only required components and protocol implementations

- **Optimum performance** built-in MCU support, interrupt-based event handling, free RTOS support and compilers that produce highly compact and efficient code

- Faster development save time and effort by using the APIs and the rich set of sample applications for most common functions

- Simpler certification get ready for certification with test applications for EMVCO L1, NFC Forum and ISO/IEC10373-6 PICC/PCD

### Find your NFC toolkit at <u>www.nxp.com</u>

# CLRC663 *plus* – best performance at lowest power consumption

- Max. operating transmitter current: 350mA (lim. 500mA)

- Enhanced LPCD performance and options

- Broad temperature range from -40°C to +105°C

- Low supply voltage for battery support down to 2.5V

| Item             | 12NC           | Comment                                                                                                                                                                                                                                                                                 |

|------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLRC66303HN, 551 | 9353 062 08551 | CLRC663 <i>plus</i> on single tray                                                                                                                                                                                                                                                      |

| CLRC66303HN, 518 | 9353 062 08518 | CLRC663 <i>plus</i> on reel                                                                                                                                                                                                                                                             |

| OM26630FDK       | 9353 391 51699 | CLRC663 <i>plus</i> frontend development kit containing a CLEV6630B development board and<br>- an 30*50mm <sup>2</sup> antenna with matching components and 3 PCBs for individual antenna matching<br>- NTAG216F and MIFARE DESFire EV2 sample cards and 10 CLRC663 <i>plus</i> samples |

| CLEV6630B        | 9353 391 49699 | CLRC663 <i>plus</i> frontend development board with 65*65mm <sup>2</sup> antenna                                                                                                                                                                                                        |

www.nxp.com/products/:CLRC66303HN www.nxp.com/products/:OM26630FDK

#### SECURE CONNECTIONS FOR A SMARTER WORLD