# High Speed, Current Feedback Dual Operational Amplifier

**Data Sheet**

Features

450 MHz small signal bandwidth

1500V/μs slew rate

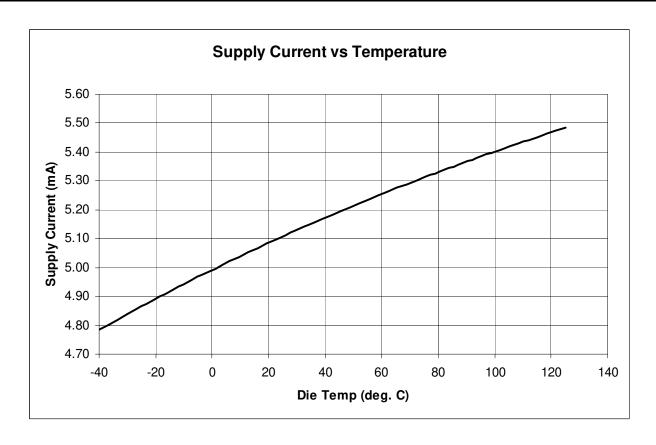

• 5.2 mA/channel static supply current

· 65 mA output current

120 MHz gain flatness to +/- 0.1 dB

8 pin SOIC

#### **Applications**

Video switchers/routers

· Video line drivers

· Twisted pair driver/receiver

Active filters

#### **Description**

The ZL40123 is a high speed, dual, current feedback operational amplifier offering high performance at a low cost. The device has a very high output current drive capability of 65 mA while requiring only 5.2 mA of static supply current. This feature makes the ZL40123

March 2006

#### **Ordering Information**

ZL40123/DCA 8 Pin SOIC Tubes

ZL40123/DCB 8 Pin SOIC Tape & Reel

ZL40123DCE1 8 Pin SOIC\* Tubes, Bake & Drypack

ZL40123DCF1 8 Pin SOIC\* Trays, Bake & Drypack

\*Pb Free Matte Tin

-40°C to +85°C

the ideal choice where a high density of high speed devices is required.

The flat gain response to 120 MHz, 450 MHz small signal bandwidth and 1500V/ $\mu$ s slew rate make the device an excellent solution for video applications such as driving video signals down significant cable lengths.

Other applications which may take advantage of the ZL40123 superior dynamic performance features include low cost high order active filters and twisted pair driver/receivers.

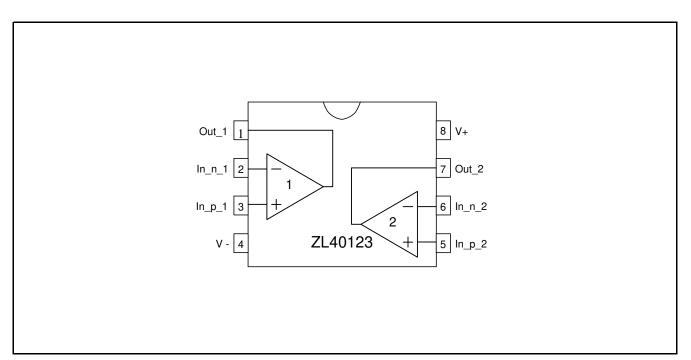

Figure 1 - Functional Block Diagram and Pin Connection

#### **Change Summary**

Changes from January 2005 Issue to March 2006 Issue. Page, section, figure and table numbers refer to this current issue.

| Page | Item | Change                       |

|------|------|------------------------------|

| 1    |      | Updated Ordering Information |

#### **Application Notes**

#### **Current Feedback Op Amps**

Current feedback op amps offer several advantages over voltage feedback amplifiers:

- AC bandwidth not dependent on closed loop gain

- · High Slew Rate

- Fast settling time

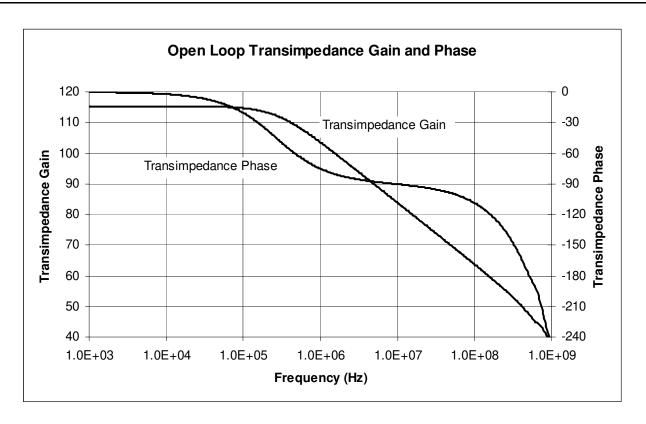

The architecture of the current feedback opamp consists of a high impedance non-inverting input and a low impedance inverting input which is always feedback connected. The error current is amplified by a transimpedance amplifier which can be considered to have gain

$$Z(f) = \frac{Z_o}{1 + j\left(\frac{f}{f_o}\right)}$$

where  $Z_0$  is the DC gain.

It can be shown that the closed loop non-inverting gain is given by

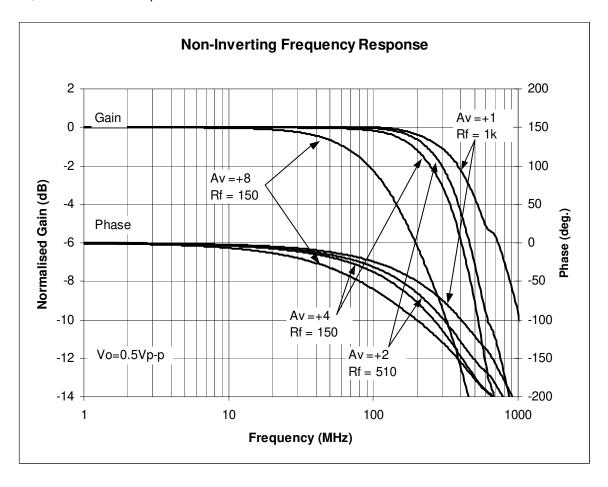

$$\frac{Vout}{Vin} = \frac{Av}{1 + j\left(\frac{fR_f}{f_oZ_o}\right)}$$

where Av is the DC closed loop gain, Rf is the feedback resistor. The closed loop bandwidth is therefore given by

$$BW_{CL} = \frac{f_o Z_o}{R_f} = \frac{GB_{OL}}{R_f}$$

and for low values of closed loop gain Av depends only on the feedback resistor R<sub>f</sub> and not the closed loop gain.

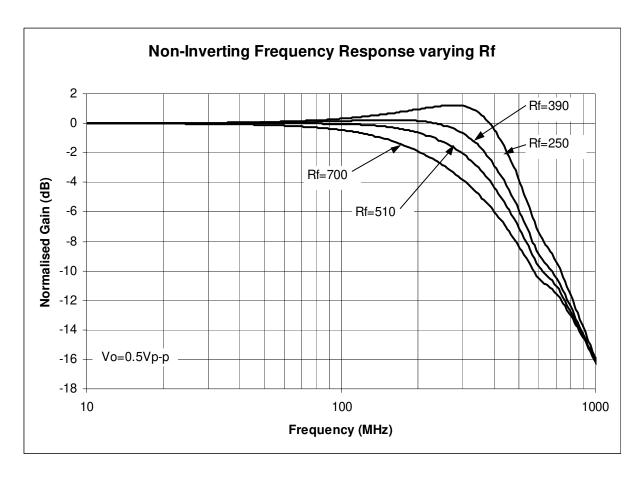

Increasing the value of R<sub>f</sub>

- Increases closed loop stability

- Decreases loop gain

- · Decreases bandwidth

- · Reduces gain peaking

- · Reduces overshoot

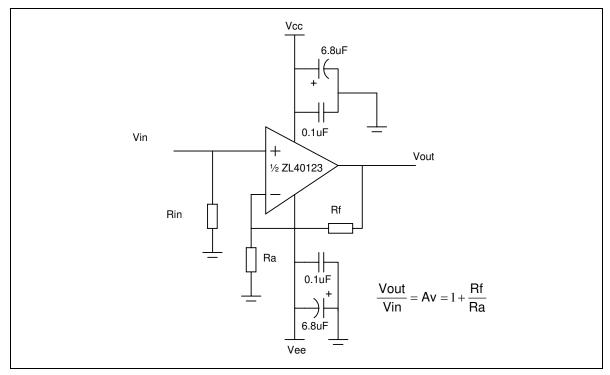

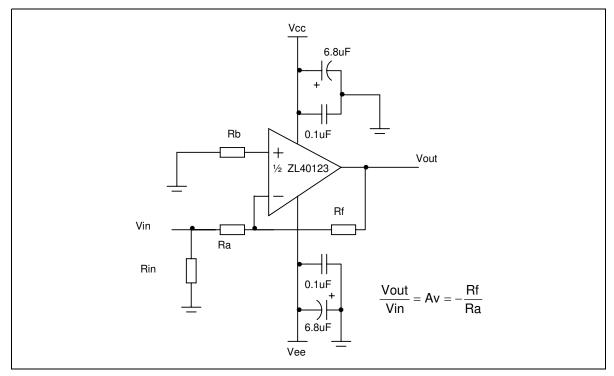

Using a resistor value of  $R_f$ =510  $\Omega$  for Av=+2 V/V gives good stability and bandwidth. However since requirements for stability and bandwidth vary it may be worth experimentation to find the optimal  $R_f$  for a given application.

#### **Layout Considerations**

Correct high frequency operation requires a considered PCB layout as stray capacitances have a strong influence over high frequency operation for this device. The Zarlink evaluation board serves as a good example layout that should be copied. The following guidelines should be followed:

- Include 6.8 uF tantalum and 0.1 uF ceramic capacitors on both positive and negative supplies

- Remove the ground plane under and around the part, especially near the input and output pins to reduce parasitic capacitances

- · Minimize all trace lengths to reduce series inductance

## **Application Diagrams**

Figure 2 - Non-inverting Gain

Figure 3 - Inverting Gain

### **Absolute Maximum Ratings**

|   | Parameter                                                | Symbol                 | Min.                   | Max.                                   | Units |

|---|----------------------------------------------------------|------------------------|------------------------|----------------------------------------|-------|

| 1 | Vin Differential                                         | V <sub>IN</sub>        |                        | ±1.2                                   | V     |

| 2 | Output Short Circuit Protection                          | V <sub>OS/C</sub>      |                        | See Apps<br>Note in this<br>data sheet |       |

| 3 | Supply voltage                                           | V+, V-                 |                        | ±6.5                                   | V     |

| 4 | Voltage at Input Pins                                    | $V_{(+IN)}, V_{(-IN)}$ | V-                     | V+                                     | V     |

| 5 | Voltage at Output Pins                                   | V <sub>O</sub>         | V-                     | V+                                     | V     |

| 6 | EDS Protection<br>(HBM Human Body Model)<br>(see Note 2) |                        | 2                      | (see Note 3)                           | kV    |

| 7 | Storage Temperature                                      |                        | -55                    | +150                                   | °C    |

| 8 | Latch-up test                                            |                        | ±100 mA for 100 ms     | (see Note 4)                           |       |

| 9 | Supply transient test                                    |                        | 20% pulse<br>for 100ms | (see Note 5)                           |       |

- Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical Characteristics.

- Note 2: Human body model, 1.5 k $\Omega$  in series with 100 pF. Machine model, 20  $\Omega$  in series with 100 pF.

- Note 3: 0.8 kV between the pairs of +INA, -INA and +INB pins only. 2kV between supply pins, OUTA or OUTB pins and any input pin.

- Note 4: ±100 mA applied to input and output pins to force the device to go into "latch-up". The device passes this test to JEDEC spec 17.

- Note 5: Positive and Negative supply transient testing increases the supplies by 20% for 100 ms.

## **Operating Range**

| Characteristic                  | Min.     | Тур. | Max. | Units     | Comments |

|---------------------------------|----------|------|------|-----------|----------|

| Supply Voltage (Vcc)            | ±4.0     |      | ±6.0 | V         |          |

| Operating Temperature (Ambient) | -40      |      | +85  | °C        |          |

| Junction to Ambient resistance  | Rth(j-a) | 150  |      | °C        |          |

|                                 |          |      |      | 4 layer   |          |

|                                 |          |      |      | FR4 board |          |

| Junction to Case resistance     | Rth(j-c) | 60   |      | °C        |          |

|                                 |          |      |      | 4 layer   |          |

|                                 |          |      |      | FR4 board |          |

**Electrical Characteristics** - Vcc= $\pm 5$  V,  $T_{amb}=25$ °C(typ.),  $T_{amb}=-40$ °C to +85°C(min-max), Av=+2V/V, Rf=510  $\Omega$ , Rload=100  $\Omega$  unless specified.

| Characteristic                      | Conditions                                | Тур.<br>25°С | Min./<br>Ma.x<br>25°C | Min./<br>Max.<br>-40 to<br>+85°C | Units     | Test<br>Type <sup>1</sup> |

|-------------------------------------|-------------------------------------------|--------------|-----------------------|----------------------------------|-----------|---------------------------|

| Frequency Domain Response           |                                           |              |                       |                                  |           |                           |

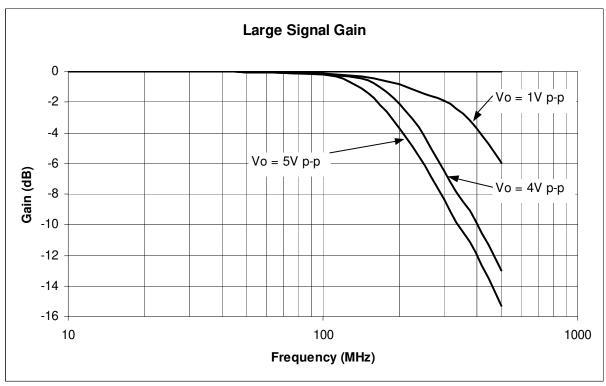

| -3 dB Bandwidth                     | Av=+1; Vo < 0.5Vp-p;<br>Rf=1.5 k $\Omega$ | 450          | -                     | -                                | MHz       | С                         |

|                                     | Av=+2; Vo < 0.5Vp-p;<br>Rf=510 $\Omega$   | 380          | -                     | -                                | MHz       | С                         |

|                                     | Av=+2; Vo < 5V p-p;<br>Rf=510 $\Omega$    | 170          | -                     | -                                | MHz       | С                         |

| +/- 0.1dB Flatness                  | Av=+2; Vo < 0.5Vp-p;<br>Rf=510 $\Omega$   | 120          | -                     | -                                | MHz       | С                         |

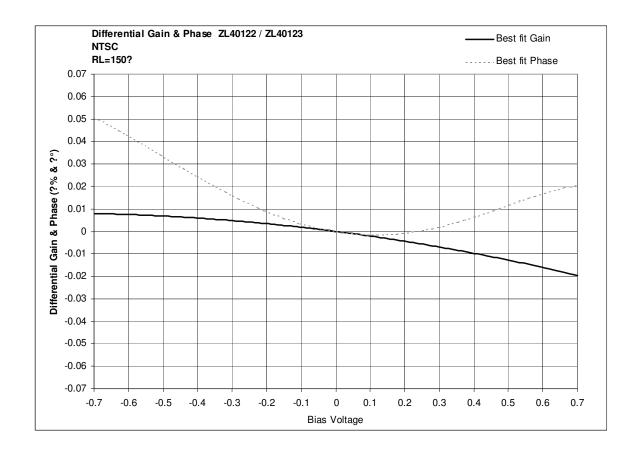

| Differential Gain (NTSC)            | Rload=150 Ω                               | 0.01         | -                     | -                                | %         | С                         |

| Differential Phase (NTSC)           | Rload=150 Ω                               | 0.015        | -                     | -                                | deg.      | С                         |

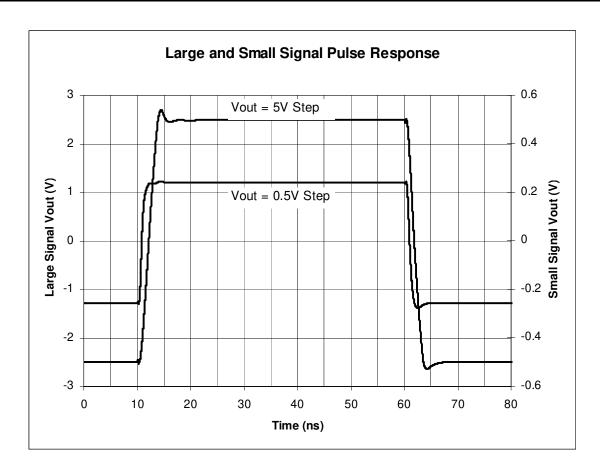

| Time Domain Response                |                                           |              |                       |                                  |           |                           |

| Rise and Fall Time                  | Vout=0.5 V Step                           | 1            | -                     | -                                | ns        | С                         |

|                                     | Vout=5 V Step                             | 2.8          | -                     | -                                | ns        | С                         |

| Settling Time to 0.1%               | Vout=2 V Step                             | 6            | -                     | -                                | ns        | С                         |

| Overshoot                           | Vout=0.5 V Step                           |              | -                     | -                                | %         | С                         |

| Slew Rate                           | Vout=5 V Step                             | 1500         | -                     | -                                | V/μs      | С                         |

| Noise and Distortion                |                                           |              |                       |                                  |           |                           |

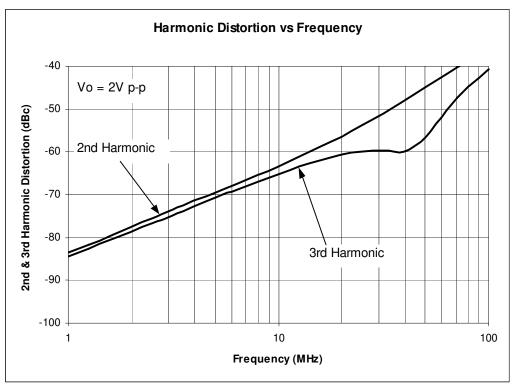

| 2 <sup>nd</sup> Harmonic Distortion | Vout=2Vp-p, 1 MHz                         | -84          | -                     | -                                | dBc       | С                         |

| 3 <sup>nd</sup> Harmonic Distortion | Vout=2Vp-p, 1 MHz                         | -85          | -                     | -                                | dBc       | С                         |

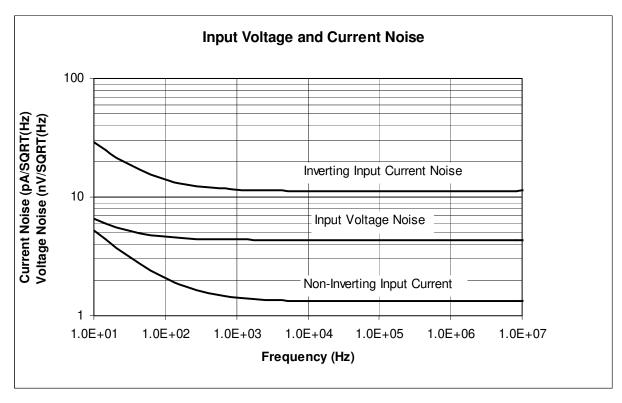

| Equivalent Input Noise              |                                           |              |                       |                                  |           |                           |

| Voltage                             | >1 MHz                                    | 5.5          | -                     | -                                | nV√Hz     | С                         |

| Non-Inverting Current               | verting Current >1 MHz                    |              | -                     | -                                | pV√Hz     | С                         |

| Inverting Current                   | >1 MHz                                    | 11           | -                     | -                                | pA√Hz     | С                         |

| Static, DC Performance              |                                           |              |                       |                                  |           |                           |

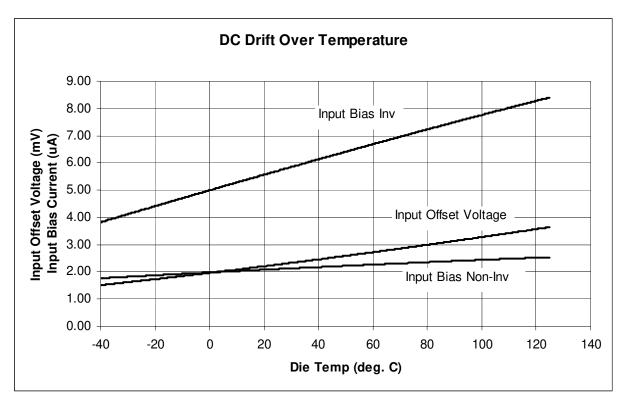

| Input Offset Voltage                |                                           | 2.7          | ±6.3                  | ±7.7                             | mV        | Α                         |

| Average Drift                       |                                           | -            | -                     | 15                               | μV/deg. C | С                         |

| Input Bias Current – Non-inverting  |                                           | 2.6          | ±5.6                  | ±6                               | μΑ        | Α                         |

| Characteristic                     | Conditions  | Typ.<br>25°C | Min./<br>Ma.x<br>25°C | Min./<br>Max.<br>-40 to<br>+85°C | Units     | Test<br>Type <sup>1</sup> |

|------------------------------------|-------------|--------------|-----------------------|----------------------------------|-----------|---------------------------|

| Average Drift                      |             | -            | -                     | 6                                | nA/deg. C | С                         |

| Input Bias Current – Inverting     |             | 7.4          | ±25                   | ±28                              | uA        | Α                         |

| Average Drift                      |             | -            | -                     | 15                               | nA/deg. C | С                         |

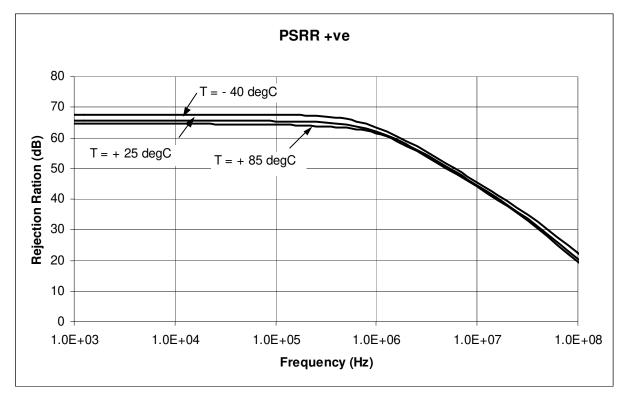

| Power Supply Rejection Ratio (+ve) | DC          | 61           | 58                    | 57                               | dB        | Α                         |

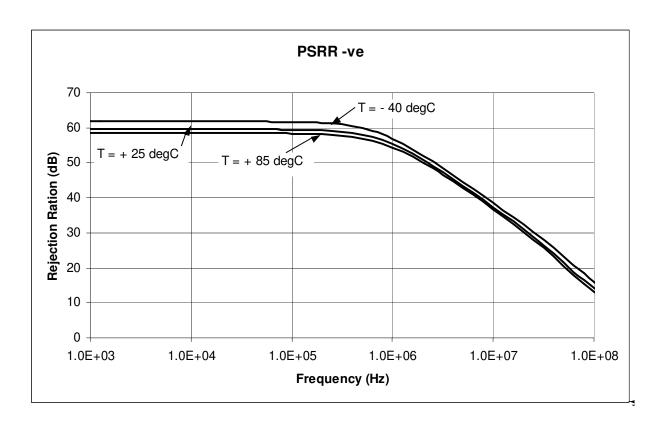

| Power Supply Rejection Ratio (-ve) | DC          | 58           | 56                    | 55                               | dB        | Α                         |

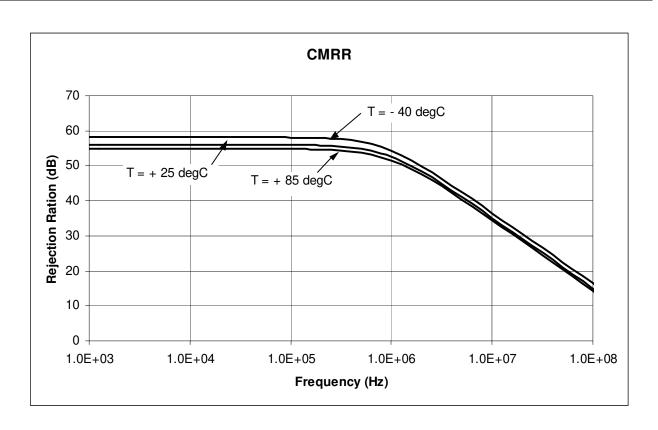

| Common Mode Rejection Ratio        | DC          | 54           | 50                    | 49                               | dB        | Α                         |

| Supply Current (per Channel)       | Quiescent   | 5.2          | 6.5                   | 6.7                              | mA        | Α                         |

| Miscellaneous Performance          |             |              |                       |                                  |           |                           |

| Input Resistance (Non-inverting)   |             | 8            | -                     | -                                | МΩ        | С                         |

| Input Capacitance (Non-inverting)  |             | 1            | -                     | -                                | pF        | С                         |

| Common Mode Input Range            |             | ±2.4         | ±2.2                  | ±2.0                             | V         | Α                         |

| Output Voltage Range               | Rload=100 Ω | ±2.8         | ±2.7                  | ±2.6                             | V         | Α                         |

| Output Current (max)               |             | 65           | -                     | -                                | mA        | С                         |

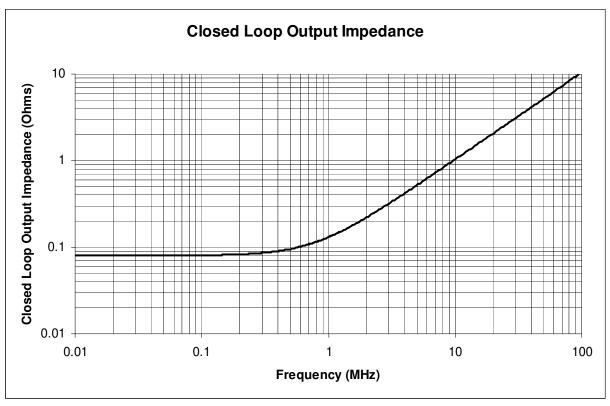

| Output Resistance, Closed Loop     | DC          | 90           | -                     | -                                | mΩ        | С                         |

Note: Test Types:

(A) 100% tested at 25°C. Over temperature limits are set by characterization and simulation.

(B) Limits set by characterization or simulation.

(C) Typical value only for information.

**Typical Performance Characteristics -**  $T_{amb}$ =25°C,  $V_{supply}$ =± 5 V, Rload=100  $\Omega$ , Av=+2V/V, Rf=510  $\Omega$ , unless otherwise specified.

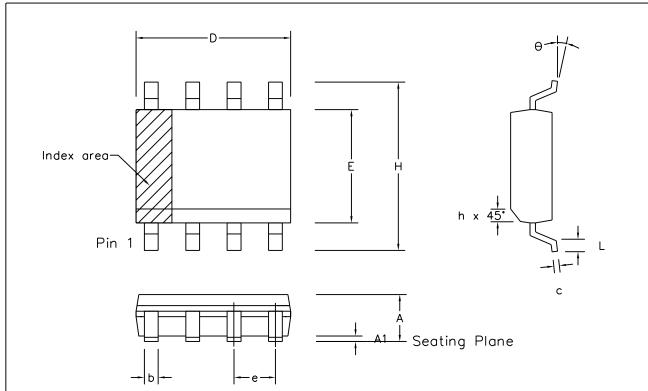

|                                   | Min          | Max  | Min       | Max   |  |  |

|-----------------------------------|--------------|------|-----------|-------|--|--|

|                                   | mm           | mm   | inch      | inch  |  |  |

| Α                                 | 1.35         | 1.75 | 0.053     | 0.069 |  |  |

| A1                                | 0.10         | 0.25 | 0.004     | 0.010 |  |  |

| D                                 | 4.80         | 5.00 | 0.189     | 0.197 |  |  |

| Н                                 | 5.80         | 6.20 | 0.228     | 0.244 |  |  |

| E                                 | 3.80         | 4.00 | 0.150     | 0.157 |  |  |

| L                                 | 0.40         | 1.27 | 0.016     | 0.050 |  |  |

| е                                 | 1.27         | BSC  | 0.050 BSC |       |  |  |

| b                                 | 0.33         | 0.51 | 0.013     | 0.020 |  |  |

| С                                 | 0.19         | 0.25 | 0.008     | 0.010 |  |  |

| 0                                 | 0°           | 8°   | 0°        | 8°    |  |  |

| h                                 | 0.25         | 0.50 | 0.010     | 0.020 |  |  |

|                                   | Pin Features |      |           |       |  |  |

| N                                 | 8 8          |      |           |       |  |  |

| Conforms to JEDEC MS-012AA Iss. C |              |      |           |       |  |  |

#### Notes:

- 1. The chamfer on the body is optional. If not present, a visual index feature, e.g. a dot, must be located within the cross—hatched area.

- 2. Controlling dimensions are in inches.

- 3. Dimension D do not include mould flash, protusion or gate burrs. These shall not exceed 0.006" per side.

- 4. Dimension E1 do not include inter-lead flash or protusion. These shall not exceed 0.010" per side.

- 5. Dimension b does not include dambar protusion / intrusion. Allowable dambar protusion shall be 0.004" total in excess of b dimension.

| © Zarlink | Semiconduc | ctor 2002 All ri | ghts reserved. |        |         |         |                        | Package Code                       |

|-----------|------------|------------------|----------------|--------|---------|---------|------------------------|------------------------------------|

| ISSUE     | 1          | 2                | 3              | 4      | 5       |         | Previous package codes | Package Outline for                |

| ACN       | 6745       | 201936           | 202595         | 203705 | 212424  | ZARLINK | MP / S                 | 8 lead SOIC<br>(0.150" Body width) |

| DATE      | 5Apr95     | 27Feb97          | 12Jun97        | 9Dec97 | 22Mar02 |         | ,                      | ,                                  |

| APPRD.    |            |                  |                |        |         |         |                        | GPD00010                           |

# For more information about all Zarlink products visit our Web Site at www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in and I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE