## **Three-Phase MOSFET Driver System IC**

### FEATURES AND BENEFITS

- 3-phase bridge MOSFET driver

- Bootstrap gate drive for N-channel MOSFET bridge

- Cross-conduction protection with adjustable dead time

- Charge pump for low supply voltage operation

- Programmable gate drive voltage and strength

- 5.5 to 50 V supply voltage operating range

- Integrated logic supply

- Current sense amplifier with programmable gain and offset

- SPI-compatible serial interface

- Bridge control by direct logic inputs or serial interface

- Integrated bemf state comparators

- LIN/PWM physical interface with Wake

- · Programmable logic supply regulator with current limit

- MCU Window watchdog and reset

- Ignition switch interface

- Diagnostics, status, voltage, and temperature feedback

- Developed in accordance with ISO 26262

### APPLICATIONS

- Automotive fuel, oil, and urea pumps

- Automotive fans and blowers

### PACKAGES:

### DESCRIPTION

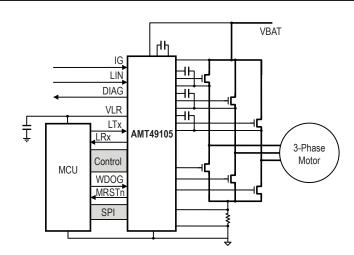

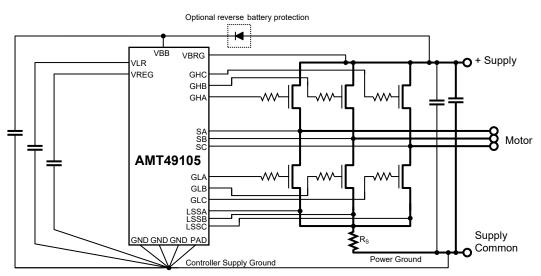

The AMT49105 is an N-channel power MOSFET driver capable of controlling MOSFETs connected in a three-phase bridge arrangement and is specifically designed for automotive applications with high-power inductive loads such as BLDC motors. Full control over all six power MOSFETs in the threephase bridge is provided, allowing motors to be driven with block commutation or sinusoidal excitation.

The AMT49105 is designed to provide the gate drive, supply, and peripheral functions in a system where a small microcontroller provides the motor control, communication interface to a central ECU and intelligent fault and status handling. The AMT49105 provides the supply and watchdog for the microcontroller and the high voltage interfaces between the microcontroller and the central ECU and ignition switch. An ISO17987 (LIN 2.X) and SAE J2602 compliant physical interface is provided for systems using LIN bus communications. This can also operate as a PWM interface for PWM communication systems.

A unique charge pump regulator provides the supply for the MOSFET gate drive for battery voltages down to 7 V and allows the AMT49105 to operate with a reduced gate drive down to 5.5 V. A bootstrap capacitor is used to provide the above-battery supply voltage required for N-channel MOSFETs.

A single sense amplifier with programmable gain and offset provides current sensing using a single low-side resistive shunt.

Integrated diagnostics provide indication of undervoltage, overtemperature, and power bridge faults and can protect the power switches under most short-circuit conditions.

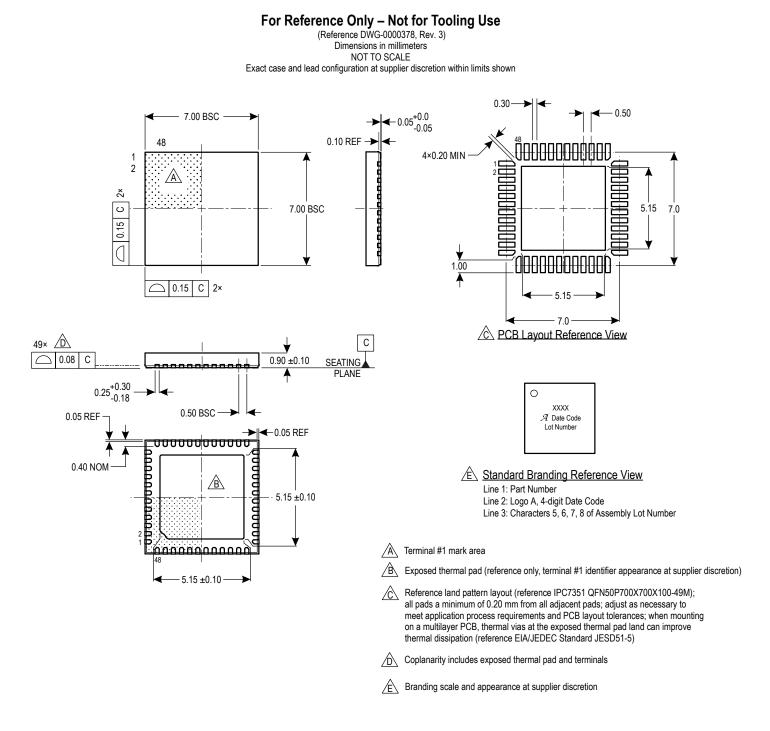

The AMT49105 is supplied in a 48-terminal wettable flank QFN package (suffix EV). This package is lead (Pb) free with 100% matte-tin leadframe plating.

Figure 1: Typical Application

# Three-Phase MOSFET Driver System IC

#### **SELECTION GUIDE**

| Part Number     | Packing                        | Package                                                                                        |

|-----------------|--------------------------------|------------------------------------------------------------------------------------------------|

| AMT49105KEVTR-J | 1000 pieces per<br>7-inch reel | 7 mm × 7 mm, 0.9 mm nominal height 48-terminal QFN with exposed thermal pad and wettable flank |

#### **Table of Contents**

|                                                   | Table |

|---------------------------------------------------|-------|

| Features and Benefits                             |       |

| Description                                       |       |

| Package                                           |       |

| Selection Guide                                   |       |

| Absolute Maximum Ratings                          |       |

| Thermal Characteristics                           |       |

| Pinout Diagram and Terminal List                  |       |

| Functional Block Diagram                          |       |

| Electrical Characteristics                        |       |

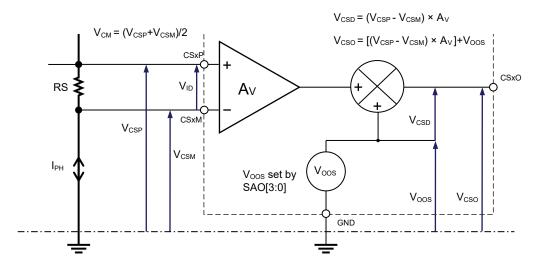

| Sense Amplifier Voltage Definitions               |       |

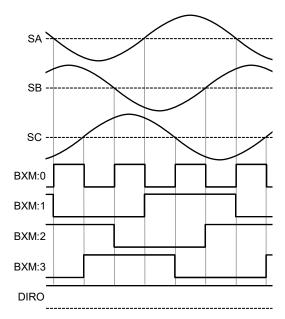

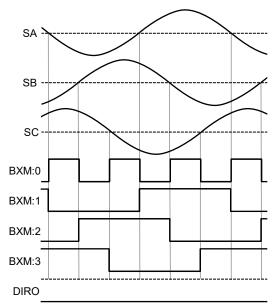

| Timing Diagrams                                   |       |

| Logic Truth Tables                                |       |

| Functional Description                            |       |

| Input and Output Terminal Functions               |       |

| Supplies and Regulators                           |       |

| Main Power Supply                                 |       |

| VLR Regulator                                     |       |

| Pump Regulator                                    |       |

| Operating Modes                                   |       |

| LIN Mode                                          |       |

| PWM Mode                                          |       |

| Programming Mode                                  |       |

| Low Power Sleep State                             |       |

| Microcontroller Reset and Watchdog                |       |

| Microcontroller Reset<br>Microcontroller Watchdog |       |

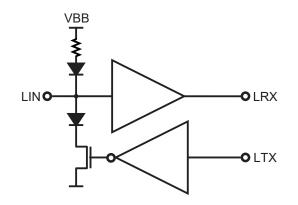

| LIN Physical Interface                            |       |

| Gate Drives                                       |       |

| Gate Drives                                       |       |

| Bootstrap Supply                                  |       |

| Bootstrap Charge Management                       |       |

| Top-Off Charge Pump                               |       |

| High-Side Gate Drive                              |       |

| Low-Side Gate Drive                               |       |

| Gate Drive Passive Pull-Down                      |       |

| Gate Drive Control                                |       |

| Dead Time                                         |       |

| Logic Control Inputs                              |       |

| Output Enable / Disable                           |       |

| Bridge Switch                                     |       |

| BEMF Zero Crossing Multiplex Output               |       |

| Current Sense Amplifiers                          |       |

| Diagnostics                                       |       |

| Serial Status Register                              |      |

|-----------------------------------------------------|------|

| Diagnostics Registers                               |      |

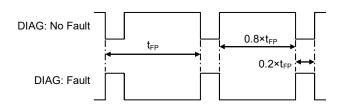

| DIAG Diagnostic Output                              |      |

| Chip-Level Diagnostics                              |      |

| Chip Fault State: Internal Logic Undervoltage (POR) |      |

| Chip Fault State: Overtemperature                   |      |

| Chip Fault State: Serial Error                      | . 37 |

| Chip Fault State: EEPROM                            |      |

| Operational Monitors                                |      |

| Monitor: V <sub>BB</sub> Supply Undervoltage        |      |

| Monitor: V <sub>REG</sub> Undervoltage              | . 37 |

| Monitor: V <sub>LR</sub> Undervoltage               | . 38 |

| Monitor: V <sub>IO</sub> Undervoltage               | . 38 |

| Monitor: Temperature Warning                        | . 38 |

| Monitor: Microcontroller Watchdog                   | . 38 |

| Monitor: ENABLE Timeout                             | . 38 |

| Monitor: IG Input                                   | . 39 |

| Power Bridge Faults                                 | . 40 |

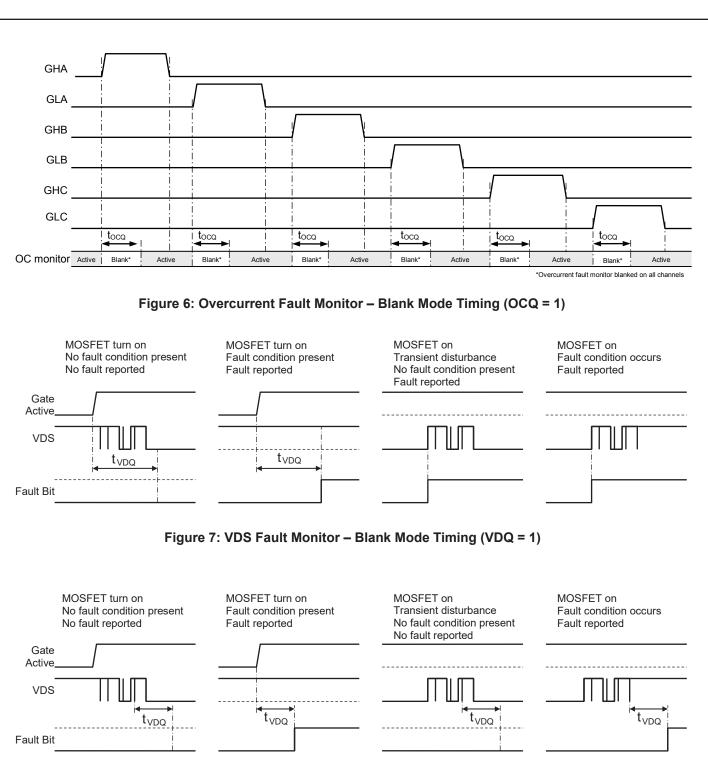

| Bridge: Overcurrent Detect                          | . 40 |

| Bridge: Bootstrap Capacitor Undervoltage Fault      | . 40 |

| Bridge: MOSFET V <sub>DS</sub> Overvoltage Fault    | . 41 |

| Fault Action                                        | . 42 |

| Fault Masks                                         | . 43 |

| Diagnostic and System Verification                  | . 44 |

| On-Line Verification                                | . 44 |

| System Clock Frequency Verification                 | . 44 |

| System Clock Operation Verification                 |      |

| Off-Line Verification                               | . 44 |

| All Gate Drives Off                                 | . 44 |

| MOSFET Active Monitor                               | . 44 |

| Motor Direction                                     | . 45 |

| Serial Interface                                    | . 46 |

| Configuration and Control Registers                 | . 49 |

| Mask Registers                                      | . 50 |

| Verification Register                               | . 50 |

| Status and Diagnostic Registers                     |      |

| Diagnostic Registers                                |      |

| Status Register                                     |      |

| Readback Register                                   |      |

| Nonvolatile Memory                                  |      |

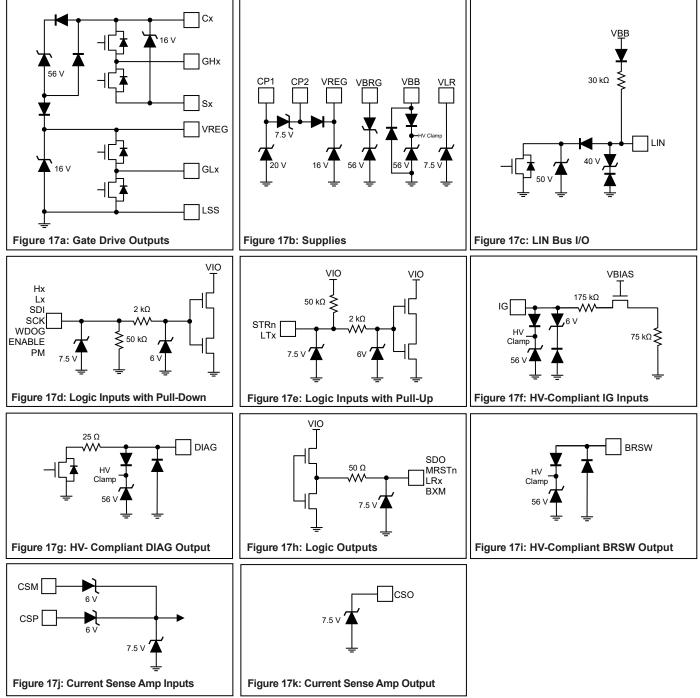

| Input/Output Structures                             |      |

| Layout Recommendations                              |      |

| Package Outline Drawing                             |      |

# Three-Phase MOSFET Driver System IC

#### ABSOLUTE MAXIMUM RATINGS [1][2]

| Characteristic                             | Symbol              | Notes                                                                                                                                   | Rating                                        | Unit |

|--------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------|

| Supply Voltage                             | V <sub>BB</sub>     | VBB                                                                                                                                     | -0.3 to 50                                    | V    |

| Between Ground Terminals                   | _                   | Connect GND terminals together at package                                                                                               | -0.1 to 0.1                                   | V    |

| Pumped Regulator Terminal                  | V <sub>REG</sub>    | VREG                                                                                                                                    | -0.3 to 16                                    | V    |

| Charge Pump Capacitor Terminal             | V <sub>CP1</sub>    | CP1                                                                                                                                     | -0.3 to 16                                    | V    |

| Charge Pump Capacitor Terminal             | V <sub>CP2</sub>    | CP2                                                                                                                                     | -0.3 to 16                                    | V    |

| Logic Regulator Output                     | $V_{LR}$            | VLR                                                                                                                                     | -0.3 to 6                                     | V    |

| LIN Bus Interface                          | V <sub>LIN</sub>    | LIN                                                                                                                                     | -40 to 50                                     | V    |

| Logic Inputs                               | _                   | All logic inputs except IG                                                                                                              | -0.3 to 6                                     | V    |

| Logic Input                                | V <sub>IG</sub>     | IG                                                                                                                                      | -4 to 50                                      | V    |

| Logic Outputs                              | _                   | All logic outputs except DIAG                                                                                                           | -0.3 to 6                                     | V    |

| Logic Output                               | V <sub>DIAG</sub>   | DIAG                                                                                                                                    | -0.3 to 50                                    | V    |

| Bridge Drain Monitor Terminals             | V <sub>BRG</sub>    | VBRG                                                                                                                                    | -5 to 55                                      | V    |

| Switched Bridge Terminal                   | V <sub>BRS</sub>    | BRSW                                                                                                                                    | -0.3 to 55                                    | V    |

| Bootstrap Supply Terminals                 | V <sub>Cx</sub>     | CA, CB, CC                                                                                                                              | -0.3 to V <sub>REG</sub> +50                  | V    |

| Llink Side Cote Drive Outruit Terminele    | N/                  | GHA, GHB, GHC                                                                                                                           | $V_{CX}$ - 16 to $V_{Cx}$ + 0.3               | V    |

| High-Side Gate Drive Output Terminals      | V <sub>GHx</sub>    | GHA, GHB, GHC (Transient)                                                                                                               | -18 to V <sub>Cx</sub> + 0.3                  | V    |

|                                            |                     | SA, SB, SC                                                                                                                              | V <sub>CX</sub> - 16 to V <sub>Cx</sub> + 0.3 | V    |

| Motor phase terminals                      | V <sub>Sx</sub>     | SA, SB, SC (Transient)                                                                                                                  | -18 to V <sub>Cx</sub> + 0.3                  | V    |

|                                            | N/                  | GLA, GLB, GLC                                                                                                                           | V <sub>REG</sub> – 16 to 18                   | V    |

| Low-side gate drive output terminals       | V <sub>GLx</sub>    | GLA, GLB, GLC (Transient)                                                                                                               | -18 to V <sub>Cx</sub> + 0.3                  | V    |

| Deider han eider anne familie de           |                     | LSSA, LSSB, LSSC                                                                                                                        | V <sub>REG</sub> – 16 to 18                   | V    |

| Bridge low-side source terminals           | $V_{LSS}$           | LSSA, LSSB, LSSC (Transient)                                                                                                            | -8 to 18                                      | V    |

| Sense Amplifier Inputs                     | V <sub>CSI</sub>    | CSP, CSM                                                                                                                                | -4 to 6.5                                     | V    |

| Sense Amplifier Output                     | V <sub>CSI</sub>    | CSO                                                                                                                                     | -0.3 to 6.5                                   | V    |

| Ambient Operating Temperature Range        | T <sub>A</sub>      |                                                                                                                                         | -40 to 150                                    | °C   |

| Maximum Continuous Junction<br>Temperature | T <sub>J(max)</sub> |                                                                                                                                         | 165                                           | °C   |

| Transient Junction Temperature             | T <sub>Jt</sub>     | Over temperature event not exceeding 10 seconds,<br>lifetime duration not exceeding 10 hours,<br>guaranteed by design characterization. | 180                                           | °C   |

| Storage Temperature Range                  | T <sub>stg</sub>    |                                                                                                                                         | -55 to 150                                    | °C   |

<sup>[1]</sup> With respect to GND. Ratings apply when no other circuit operating constraints are present. <sup>[2]</sup> Lowercase "x" in terminal names and symbols indicates a variable sequence character.

#### THERMAL CHARACTERISTICS: May require derating at maximum conditions

| Characteristic                | Symbol                | Test Conditions <sup>[4]</sup>                                 | Value | Unit |

|-------------------------------|-----------------------|----------------------------------------------------------------|-------|------|

|                               | D                     | 4-layer PCB based on JEDEC standard                            | 24    | °C/W |

| EV Package Thermal Resistance | $R_{	extsf{	heta}JA}$ | 2-layer PCB with 3.8 in. <sup>2</sup> of copper area each side | 44    | °C/W |

|                               | R <sub>θJP</sub>      |                                                                | 2     | °C/W |

<sup>[4]</sup> Additional thermal information available on the Allegro website.

# Three-Phase MOSFET Driver System IC

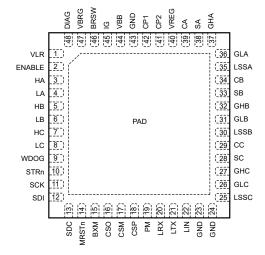

#### QFN-48 (EV) Package Pinout Diagram

#### **Terminal List Table**

| Name   | Number | Function                       | Name  | Number | Function                          |

|--------|--------|--------------------------------|-------|--------|-----------------------------------|

| BRSW   | 46     | Switched Bridge connection     | IG    | 45     | Ignition Input                    |

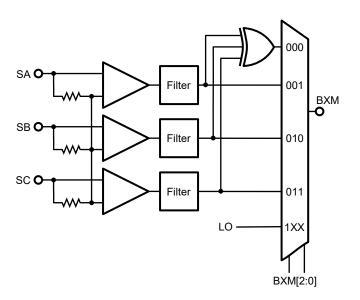

| BXM    | 15     | Multiplexed bemf output        | LA    | 4      | Control Input A Low Side          |

| CA     | 39     | Bootstrap Capacitor Phase A    | LB    | 6      | Control Input B Low Side          |

| CB     | 34     | Bootstrap Capacitor Phase B    | LC    | 8      | Control Input C Low Side          |

| CC     | 29     | Bootstrap Capacitor Phase C    | LIN   | 22     | LIN Bus connection                |

| CP1    | 42     | Pump Capacitor                 | LRX   | 20     | LIN Receive output                |

| CP2    | 41     | Pump Capacitor                 | LTX   | 21     | LIN Transmit input                |

| CSM    | 17     | Current Sense Amp 1 –Input     | LSSA  | 35     | Low-side Source Phase A           |

| CSO    | 16     | Current Sense Amp 1 Output     | LSSB  | 30     | Low-side Source Phase B           |

| CSP    | 18     | Current Sense Amp 1 +Input     | LSSC  | 25     | Low-side Source Phase C           |

| DIAG   | 48     | Programmable diagnostic output | MRSTn | 14     | MCU Reset output                  |

| ENABLE | 2      | Direct Output Activity Control | PM    | 19     | Program mode input                |

| GHA    | 37     | High-side Gate Drive Phase A   | SA    | 38     | Motor Connection Phase A          |

| GHB    | 32     | High-side Gate Drive Phase B   | SB    | 33     | Motor Connection Phase B          |

| GHC    | 27     | High-side Gate Drive Phase C   | SC    | 28     | Load Connection Phase C           |

| GLA    | 36     | Low-side Gate Drive Phase A    | SCK   | 11     | Serial Clock Input                |

| GLB    | 31     | Low-side Gate Drive Phase B    | SDI   | 12     | Serial Data Input                 |

| GLC    | 26     | Low-side Gate Drive Phase C    | SDO   | 13     | Serial Data output                |

| GND    | 43     | Ground                         | STRn  | 10     | Serial Strobe (chip select) Input |

| GND    | 23     | Ground                         | VBB   | 44     | Main Power Supply                 |

| GND    | 24     | Ground                         | VBRG  | 47     | High-side Drain voltage sense     |

| HA     | 3      | Control Input A High Side      | VREG  | 40     | Gate Drive Supply Output          |

| HB     | 5      | Control Input B High Side      | VLR   | 1      | LDO Regulator Output              |

| HC     | 7      | Control Input C High Side      | WDOG  | 9      | Watchdog Input                    |

| PAD    | Pad    | Connect To Ground              |       |        |                                   |

## **Three-Phase MOSFET Driver System IC**

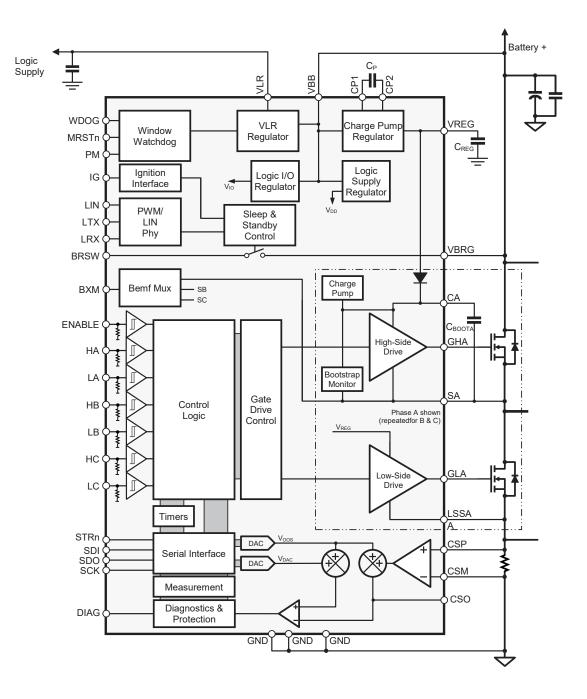

FUNCTIONAL BLOCK DIAGRAM

# Three-Phase MOSFET Driver System IC

### **ELECTRICAL CHARACTERISTICS:** Valid at $T_J = -40^{\circ}$ C to $150^{\circ}$ C, $V_{BB} = 5.5$ to 50 V, unless otherwise specified

| Characteristic                                 | Symbol             | Test Conditions                                                                                  | Min. | Тур. | Max.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Unit |

|------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| SUPPLY AND REFERENCE                           |                    |                                                                                                  |      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

|                                                |                    | Operating; outputs active                                                                        | 5.5  | _    | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | V    |

| VBB Functional Operating Range                 | V <sub>BB</sub>    | Functional; no POR, outputs disabled                                                             | 3.5  | _    | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | V    |

|                                                |                    | No unsafe states                                                                                 | 0    | _    | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | V    |

|                                                | I <sub>BBQ</sub>   | V <sub>BB</sub> = 12 V, all gate drive outputs low                                               | _    | 25   | 50         50         50         28         10         8.5         8.5         8.5         8.5         11.7         11.7         11.7         3.5         5.2         3.5         5.2         3.5         5.2         3.5         5.2         3.5         5.16         300         1.5         -         250         -8         1         1.0         2.8         24                                                                                                                                                                                                                     | mA   |

| VBB Quiescent Current                          | I <sub>BBS</sub>   | V <sub>LIN</sub> = V <sub>BB</sub> = 12 V, in sleep state                                        | _    | _    | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | μA   |

|                                                |                    | VRG = 0, V <sub>BB</sub> ≥ 8.5 V, I <sub>VREG</sub> = 0 to 35 mA                                 | 7.5  | 8    | 50         50         50         28         10         8.5         8.5         8.5         8.5         11.7         11.7         3.5         5.2         3.5         5.2         3.5         5.16         300         1.5         -         -         2.8         1.0         2.8         24                                                                                                                                                                                                                                                                                             | V    |

|                                                |                    | VRG = 0, 7.5 V $\leq$ V <sub>BB</sub> $<$ 8.5 V, I <sub>VREG</sub> = 0 to 30 mA                  | 7.5  | 8    | 8.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V    |

|                                                |                    | VRG = 0, 6 V $\leq_{VBB}$ < 7.5 V, I <sub>VREG</sub> = 0 to 13 mA                                | 7.5  | 8    | 8.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V    |

|                                                | . /                | VRG = 0, 5.5 V ≤ V <sub>BB</sub> < 6 V, I <sub>VREG</sub> ≤ 8 mA                                 | 7.5  | 8    | 10         8.5         8.5         8.5         8.5         8.5         11.7         11.7         -         5         -         3         3.5         3         3.5         3         3.5         3         1.5         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         250 | V    |

| VREG Output Voltage                            | V <sub>REG</sub>   | VRG = 1, $V_{BB} \ge 9$ V, $I_{VREG} = 0$ to 33 mA                                               | 9    | 11   | 11.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V    |

|                                                |                    | VRG = 1, 7.5 V $\leq$ V <sub>BB</sub> $<$ 9 V, I <sub>VREG</sub> = 0 to 23 mA                    | 9    | 11   | 50         50         28         10         8.5         8.5         8.5         8.5         8.5         11.7         11.7            3.5         5.2         3.5         5.2         3.5         5.2         3.5         5.16         300         1.5         -         250         -8         1         1.0         2.8         24                                                                                                                                                                                                                                                      | V    |

|                                                |                    | $VRG = 1, 6 V \le V_{BB} < 7.5 V, I_{VREG} = 0 \text{ to } 13 \text{ mA}$                        | 7.9  | _    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V    |

|                                                |                    | VRG = 1, 5.5 V ≤ V <sub>BB</sub> < 6 V, I <sub>VREG</sub> ≤ 5 mA                                 | 7.9  | 9.5  | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V    |

|                                                |                    | VLR = 0, V <sub>BB</sub> > 4.5 V                                                                 | 3.1  | 3.3  | 3.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V    |

| Logic I/O Regulator Voltage                    | V <sub>IO</sub>    | VLR = 1, V <sub>BB</sub> > 6 V                                                                   | 4.8  | 5.0  | 5.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V    |

|                                                | V <sub>LR</sub>    | VLR = 0, I <sub>VLR</sub> < 70 mA, V <sub>BB</sub> > 6 V                                         | 3.1  | 3.3  | 3.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V    |

| VLR Output Voltage                             |                    | $VLR = 0,25 \text{ mA} \le I_{VLR} \le 50 \text{ mA}, 6.5 \text{ V} \le V_{BB} \le 20 \text{ V}$ | 3.2  | 3.3  | 3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V    |

|                                                |                    | VLR = 1, I <sub>VLR</sub> < 70 mA, V <sub>BB</sub> > 6.5 V                                       | 4.8  | 5.0  | 5.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V    |

|                                                |                    | VLR = 1, 25 mA $\leq$ I <sub>VLR</sub> $\leq$ 50 mA, 6.5 V $\leq$ V <sub>BB</sub> $\leq$ 20 V    | 4.84 | 5.0  | 5.16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V    |

| VLR Regulator Current Limit                    | I <sub>LROC</sub>  |                                                                                                  | 130  | _    | 300                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | mA   |

| VLR Regulator Enable<br>Voltage Threshold      | V <sub>LROE</sub>  | V <sub>LR</sub> rising                                                                           | -    | _    | 1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V    |

| VLR Regulator Shutdown<br>Voltage Threshold    | V <sub>LROSD</sub> | V <sub>LR</sub> falling                                                                          | 1.2  | -    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V    |

| VLR Regulator Shutdown<br>Lockout Period       | t <sub>LRLO</sub>  |                                                                                                  | -    | 2    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ms   |

| VLR Regulator Pilot Current                    | ILROP              |                                                                                                  | _    | 2    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | mA   |

| BRSW Switch Impedance [1]                      | R <sub>BRSW</sub>  | I <sub>BRSW</sub> = -5 mA                                                                        | 50   | -    | 250                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Ω    |

| BRSW Current Limit [1][8]                      | I <sub>BRLIM</sub> | V <sub>BRSW</sub> = 0 V, V <sub>BRG</sub> = 50 V                                                 | -30  | _    | -8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | mA   |

| BRSW Switched Bridge Output Leakage            | I <sub>BRSWL</sub> | Switch disabled, 0 < V <sub>BRS</sub> < V <sub>BRG</sub>                                         | -1   | _    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | μA   |

|                                                |                    | I <sub>D</sub> = 10 mA                                                                           | 0.4  | 0.7  | 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V    |

| Bootstrap Diode Forward Voltage                | V <sub>fBOOT</sub> | I <sub>D</sub> = 100 mA                                                                          | 1.5  | 2.2  | 2.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V    |

| Bootstrap Diode Resistance                     | r <sub>D</sub>     | r <sub>D(100 mA)</sub> = (V <sub>fBOOT(150 mA)</sub> - V <sub>fBOOT(50mA)</sub> ) / 100 mA       | 6    | 11   | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Ω    |

| Bootstrap Diode Current Limit                  | I <sub>DBOOT</sub> |                                                                                                  | 250  | 500  | 850                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | mA   |

| Top-Off Charge Pump Current Limit              | I <sub>TOCPM</sub> |                                                                                                  | 35   | 100  | 550                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | μA   |

| High-Side Gate Drive Static Load<br>Resistance | R <sub>GSH</sub>   | V <sub>REG</sub> > 7 V                                                                           | 300  | _    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | kΩ   |

| System Clock Period                            | t <sub>osc</sub>   |                                                                                                  | 47.5 | 50   | 52.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ns   |

# Three-Phase MOSFET Driver System IC

### **ELECTRICAL CHARACTERISTICS** (continued): Valid at $T_J = -40$ °C to 150 °C, $V_{BB} = 5.5$ to 50 V, unless otherwise specified

| Characteristic                                 | Symbol                | Test Conditions                                                                                | Min.                   | Тур.  | Max.                  | Unit |

|------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------|------------------------|-------|-----------------------|------|

| GATE OUTPUT DRIVE                              |                       |                                                                                                |                        |       |                       |      |

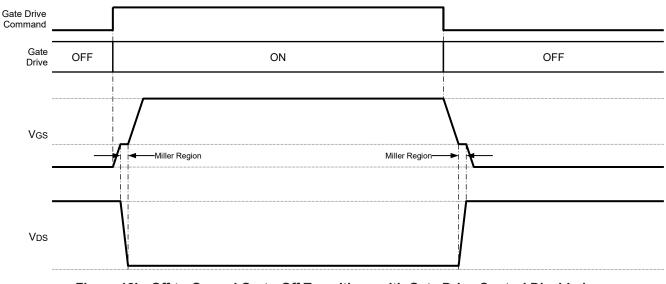

| Turn-On Time                                   | t <sub>r</sub>        | Switched mode, C <sub>LOAD</sub> = 10 nF, 20% to 80%                                           | _                      | 190   | _                     | ns   |

| Turn-Off Time                                  | t <sub>f</sub>        | Switched mode, C <sub>LOAD</sub> = 10 nF, 80% to 20%                                           | -                      | 120   | _                     | ns   |

| Dull the Or Devictory                          |                       | T <sub>J</sub> = 25°C, I <sub>GH</sub> = -150 mA <sup>[1]</sup>                                | 5                      | 8     | 11                    | Ω    |

| Pull-Up On-Resistance                          | R <sub>DS(on)UP</sub> | T <sub>J</sub> = 150°C, I <sub>GH</sub> = -150 mA <sup>[1]</sup>                               | 10                     | 15    | 20                    | Ω    |

| Pull-Up Peak Source Current [1][8]             | I <sub>PUPK</sub>     | V <sub>GS</sub> = 0 V                                                                          | -1500                  | -450  | -200                  | mA   |

| Pull Down On Resistance                        | Р                     | T <sub>J</sub> = 25°C, I <sub>GL</sub> = 150 mA                                                | 1.5                    | 2.4   | 3.1                   | Ω    |

| Pull-Down On-Resistance                        | R <sub>DS(on)DN</sub> | T <sub>J</sub> = 150°C, I <sub>GL</sub> = 150 mA                                               | 2.9                    | 4     | 5                     | Ω    |

| Pull-Down Peak Sink Current <sup>[8]</sup>     | I <sub>PDPK</sub>     | V <sub>GS</sub> > 9 V                                                                          | 425                    | 800   | 1330                  | mA   |

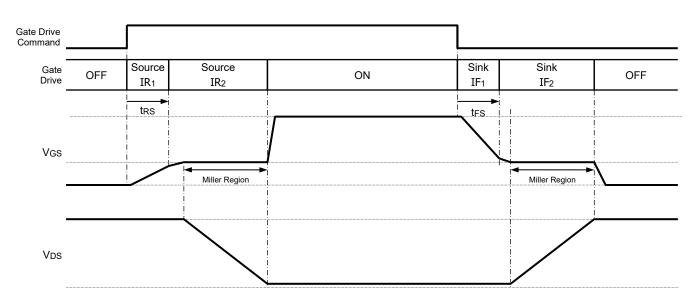

| T                                              | , T                   | V <sub>GS</sub> = 0 V, VRG = 1, IR1 = 15                                                       | -144                   | -82.5 | -48                   | mA   |

| Turn-On Current 1                              | I <sub>R1</sub>       | Programmable Range, DT[5:0] > 0                                                                | -5.5                   | _     | -82.5                 | mA   |

| T 0 0 10                                       |                       | V <sub>GS</sub> = 0 V, VRG = 1, IR2 = 15                                                       | -144                   | -82.5 | -48                   | mA   |

| Turn-On Current 2                              | I <sub>R2</sub>       | Programmable Range DT[5:0] > 0                                                                 | -5.5                   | _     | -82.5                 | mA   |

| T                                              | Ţ                     | V <sub>GS</sub> = 9 V, VRG = 1, IF1 = 15                                                       | 48                     | 79.5  | 136                   | mA   |

| Turn-Off Current 1                             | I <sub>F1</sub>       | Programmable Range DT[5:0] > 0                                                                 | 5.3                    | _     | 79.5                  | mA   |

| Irn-Off Current 2                              |                       | V <sub>GS</sub> = 9 V, VRG = 1, IF2 = 15                                                       | 48                     | 79.5  | 136                   | mA   |

|                                                | I <sub>F2</sub>       | Programmable Range DT[5:0] > 0                                                                 | 5.3                    | _     | 79.5                  | mA   |

| GHx Output Voltage High                        | V <sub>GHH</sub>      | Bootstrap capacitor fully charged                                                              | V <sub>Cx</sub> - 0.2  | _     | _                     | V    |

| GHx Output Voltage Low                         | V <sub>GHL</sub>      | –10 μA < I <sub>GH</sub> < 10 μA                                                               | _                      | _     | V <sub>Sx</sub> + 0.3 | V    |

| GLx Output Voltage High                        | V <sub>GLH</sub>      |                                                                                                | V <sub>REG</sub> - 0.2 | _     | _                     | V    |

| GLx Output Voltage Low                         | V <sub>GLL</sub>      | –10 μA < I <sub>GL</sub> < 10 μA                                                               | _                      | _     | V <sub>LSS</sub> +0.3 | V    |

| GHx Passive Pull-Down                          | R <sub>GHPD</sub>     | V <sub>BB</sub> = 0 V, I <sub>GHx</sub> = 500 µA                                               | _                      | 4     | 10                    | kΩ   |

| GLx Passive Pull-Down                          | R <sub>GLPD</sub>     | V <sub>BB</sub> = 0 V, I <sub>GLx</sub> = 500 µA                                               | _                      | 4     | 10                    | kΩ   |

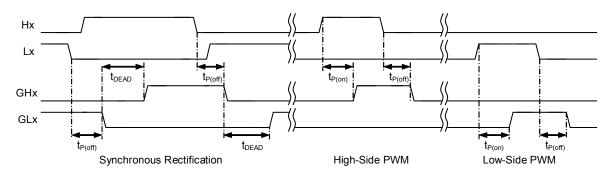

|                                                |                       | Input change to unloaded gate output change;<br>DT[5:0] = 0                                    | 60                     | 90    | 140                   | ns   |

| Turn-Off Propagation Delay <sup>[2]</sup>      | t <sub>P(off)</sub>   | Input change to unloaded gate output change,<br>excluding jitter <sup>[12]</sup> ; DT[5:0] > 0 | 135                    | 165   | 215                   | ns   |

|                                                |                       | Input change to unloaded gate output change;<br>DT[5:0] = 0                                    | 50                     | 80    | 130                   | ns   |

| Turn-On Propagation Delay <sup>[2]</sup>       | t <sub>P(on)</sub>    | Input change to unloaded gate output change,<br>excluding jitter <sup>[12]</sup> ; DT[5:0] > 0 | 125                    | 155   | 205                   | ns   |

| Propagation Delay Matching<br>(Phase-to-Phase) | Δt <sub>PP</sub>      | Same state change, DT[5:0] = 0                                                                 | -                      | 5     | 15                    | ns   |

| Propagation Delay Matching<br>(On-to-Off)      | Δt <sub>OO</sub>      | Single phase, DT[5:0] = 0                                                                      | _                      | 15    | 30                    | ns   |

| Propagation Delay Matching<br>(GHx-to-GLx)     | $\Delta t_{HL}$       | Same state change, DT[5:0] = 0                                                                 | -                      | _     | 20                    | ns   |

| Dead Time                                      |                       | Default power-up value                                                                         | 1.52                   | 1.6   | 1.68                  | μs   |

| (Turn-Off To Turn-On Delay) <sup>[2]</sup>     | t <sub>DEAD</sub>     | Programmable Range                                                                             | 0.1                    | _     | 3.15                  | μs   |

# Three-Phase MOSFET Driver System IC

#### **ELECTRICAL CHARACTERISTICS** (continued): Valid at $T_J = -40$ °C to 150°C, $V_{BB} = 5.5$ to 50 V, unless otherwise specified

| Characteristic                                                                                                                              | Symbol             | Test Conditions                                              | Min.                  | Тур. | Max. | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------------------------------------|-----------------------|------|------|------|

| LOGIC INPUTS & OUTPUTS                                                                                                                      | · · ·              | <u>`</u>                                                     | `                     |      |      |      |

| Input Low Voltogo                                                                                                                           | V                  | All digital inputs except IG, VIO = 0                        | -                     | _    | 1.05 | V    |

| out Pull-Down Resistor<br>out Pull-Up Resistor<br>out Low Voltage<br>out High Voltage<br>out Hysteresis<br>out Current<br>utput Low Voltage | V <sub>IL</sub>    | All digital inputs except IG, VIO = 1                        | -                     | _    | 1.56 | V    |

|                                                                                                                                             |                    | All digital inputs except IG, VIO = 0                        | 2.17                  | _    | -    | V    |

| Input High voltage                                                                                                                          | V <sub>IH</sub>    | All digital inputs except IG, VIO = 1                        | 3.36                  | _    | -    | V    |

| Input Hysteresis                                                                                                                            | V <sub>lhys</sub>  | All digital inputs except IG                                 | 250                   | 550  | -    | mV   |

|                                                                                                                                             |                    | SCK, SDI, WDOG, Hx, Lx, ENABLE, PM                           | 30                    | 50   | 75   | kΩ   |

| •                                                                                                                                           | R <sub>PD</sub>    | IG                                                           | -                     | 300  | -    | kΩ   |

| Input Pull-Up Resistor                                                                                                                      | R <sub>PU</sub>    | STRn, LTX                                                    | 30                    | 50   | 75   | kΩ   |

| Input Low Voltage                                                                                                                           | VIL                | IG                                                           | -                     | _    | 2.5  | V    |

| Input High Voltage                                                                                                                          | V <sub>IH</sub>    | IG                                                           | 4.8                   | _    | -    | V    |

| Input Hysteresis                                                                                                                            | V <sub>lhys</sub>  | IG                                                           | 250                   | _    | -    | mV   |

| Input Current                                                                                                                               | I <sub>G</sub>     | IG                                                           | -                     | _    | 100  | μA   |

| Output Low Voltage                                                                                                                          | V <sub>OL</sub>    | SDO, MRSTn, BXM, LRX, I <sub>OL</sub> = 1 mA                 | -                     | _    | 0.4  | V    |

| Output High Voltage                                                                                                                         | V <sub>OH</sub>    | SDO, MRSTn, BXM, LRX, I <sub>OL</sub> = -1 mA <sup>[1]</sup> | V <sub>IO</sub> - 0.4 | _    | -    | V    |

| Output Leakage <sup>[1]</sup>                                                                                                               | IO                 | SDO, 0 V < V <sub>O</sub> < V <sub>IO</sub> , STRn = 1       | -1                    | _    | 1    | μA   |

| Output Low Voltage                                                                                                                          | V <sub>OLD</sub>   | DIAG, I <sub>OD</sub> = 3 mA, DIAG active                    | -                     | 0.2  | 0.4  | V    |

| Output Current Limit                                                                                                                        | т                  | DIAG, 0 V < V <sub>OD</sub> < 18 V, DIAG active              | -                     | 10   | 17   | mA   |

| Output Current Limit                                                                                                                        | I <sub>ODLIM</sub> | DIAG, 18 V $\leq$ V <sub>OD</sub> $<$ 50 V, DIAG active      | -                     | _    | 2.5  | mA   |

| Output Lookage Current [1]                                                                                                                  | т                  | DIAG, 0 V < V <sub>OD</sub> < 6 V, DIAG inactive             | -1                    | _    | 1    | μA   |

| Output Leakage Current [1]                                                                                                                  | I <sub>OD</sub>    | DIAG, 6 V $\leq$ V <sub>OD</sub> $<$ 50, DIAG inactive       | -                     | _    | 2.5  | mA   |

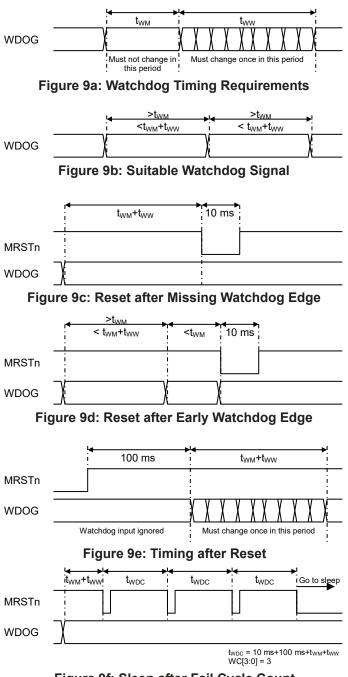

| WATCHDOG – TIMING PARAMET                                                                                                                   | ERS                |                                                              |                       |      |      |      |

| Minimum Watabdag Tima                                                                                                                       | +                  | Default power-up value                                       | 0.95                  | 1    | 1.05 | ms   |

| Minimum Watchdog Time                                                                                                                       | t <sub>WM</sub>    | Programmable range                                           | 1                     | _    | 63   | ms   |

| Watabdag Window Time                                                                                                                        | +                  | Default power-up value                                       | 9.5                   | 10   | 10.5 | ms   |

| Watchdog Window Time                                                                                                                        | t <sub>WW</sub>    | Programmable range                                           | 10                    | _    | 320  | ms   |

| Watchdog Detect to MRSTn Low                                                                                                                | t <sub>WDET</sub>  |                                                              | 100                   | _    | 200  | ms   |

| MRSTn Low                                                                                                                                   | t <sub>MRST</sub>  |                                                              | 9.5                   | 10   | 10.5 | ms   |

# Three-Phase MOSFET Driver System IC

| Characteristic                           | Symbol                   | Test Conditions                                                                                     | Min.                    | Тур.                  | Max.                    | Unit |

|------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------|-------------------------|-----------------------|-------------------------|------|

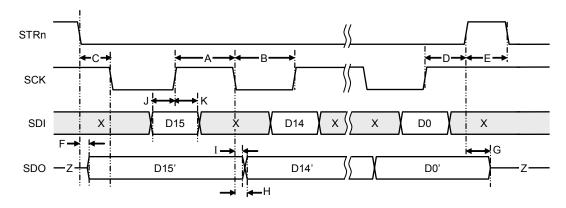

| SERIAL INTERFACE – TIMING PAR            | AMETERS                  | [11]                                                                                                |                         |                       |                         |      |

| Clock High Time                          | t <sub>SCKH</sub>        | A in Figure 4                                                                                       | 50                      | _                     | _                       | ns   |

| Clock Low Time                           | t <sub>SCKL</sub>        | B in Figure 4                                                                                       | 50                      | _                     | -                       | ns   |

| Strobe Lead Time                         | t <sub>STLD</sub>        | C in Figure 4                                                                                       | 100                     | _                     | -                       | ns   |

| Strobe Lag Time                          | t <sub>STLG</sub>        | D in Figure 4                                                                                       | 30                      | _                     | -                       | ns   |

| Strobe High Time                         | t <sub>STRH</sub>        | E in Figure 4                                                                                       | 350                     | _                     | -                       | ns   |

| Data Out Enable Time                     | t <sub>SDOE</sub>        | F in Figure 4                                                                                       | -                       | _                     | 40                      | ns   |

| Data Out Disable Time                    | t <sub>SDOD</sub>        | G in Figure 4                                                                                       | -                       | _                     | 30                      | ns   |

| Data Out Valid Time From Clock Falling   | t <sub>SDOV</sub>        | H in Figure 4                                                                                       | -                       | _                     | 40                      | ns   |

| Data Out Hold Time From Clock Falling    | t <sub>SDOH</sub>        | I in Figure 4                                                                                       | 5                       | _                     | -                       | ns   |

| Data In Set-Up Time To Clock Rising      | t <sub>SDIS</sub>        | J in Figure 4                                                                                       | 15                      | _                     | -                       | ns   |

| Data In Hold Time From Clock Rising      | t <sub>SDIH</sub>        | K in Figure 4                                                                                       | 10                      | _                     | -                       | ns   |

| STRn Delay From POR                      | t <sub>EN</sub>          | V <sub>BB</sub> > V <sub>BBR</sub> to STRn low                                                      | 500                     | _                     | -                       | μs   |

| LIN/PWM INTERFACE LOGIC I/O [11]         | ]                        |                                                                                                     | ·                       |                       | ·                       |      |

| <b>T</b>                                 |                          | VIO = 0                                                                                             | _                       | _                     | 1.05                    | V    |

| Transmitter Input Low Voltage (LTX)      | V <sub>IL</sub>          | VIO = 1                                                                                             | _                       | _                     | 1.56                    | V    |

| T                                        |                          | VIO = 0                                                                                             | 2.17                    | _                     | -                       | V    |

| Transmitter Input High Voltage (LTX)     | V <sub>IH</sub>          | VIO = 1                                                                                             | 3.36                    | _                     | -                       | V    |

| Transmitter Input Hysteresis (LTX)       | V <sub>lhys</sub>        |                                                                                                     | 250                     | 550                   | -                       | mV   |

| Transmitter Input Pull-Up Resistor (LTX) | R <sub>PU</sub>          |                                                                                                     | 30                      | 50                    | 75                      | kΩ   |

| Receiver Output Low Voltage (LRX)        | V <sub>OL</sub>          | I <sub>OL</sub> = 1 mA, V <sub>BUS</sub> = 0 V                                                      | -                       | _                     | 0.4                     | V    |

| Receiver Output High Voltage (LRX)       | V <sub>OH</sub>          | $I_{OL} = -1 \text{ mA}^{[1]}, V_{BUS} = V_{BB}$                                                    | V <sub>IO</sub> – 0.4   | _                     | -                       | V    |

| LIN/PWM INTERFACE BUS TRANSI             | MITTER [11]              |                                                                                                     |                         |                       |                         |      |

| Bus Recessive Output Voltage             | V <sub>BUSRO</sub>       | LTX High, Bus open load                                                                             | 0.8 × V <sub>BB</sub>   | _                     | _                       | V    |

|                                          | N                        | LTX Low, R <sub>LIN</sub> = 500 Ω, V <sub>BB</sub> = 7 V                                            | -                       | _                     | 1.4                     | V    |

| Bus Dominant Output Voltage              | V <sub>BUSDO</sub>       | LTX Low, R <sub>LIN</sub> = 500 Ω, V <sub>BB</sub> = 18 V                                           | -                       | _                     | 2.0                     | V    |

| Bus Short Circuit Current                | I <sub>BUSLIM</sub>      | V <sub>BUS</sub> = 13.5 V                                                                           | 40                      | _                     | 100                     | mA   |

| Leakage Current – Dominant               | I <sub>BUS_PAS_dom</sub> | V <sub>BB</sub> = 12 V, V <sub>BUS</sub> = 0 V                                                      | -1                      | _                     | -                       | mA   |

| Leakage Current – Recessive              | I <sub>BUS_PAS_rec</sub> | 7 V < V <sub>BB</sub> < 18 V, 7 V < V <sub>BUS</sub> < 18 V, V <sub>BUS</sub> $\ge$ V <sub>BB</sub> | -                       | _                     | 20                      | μA   |

| Leakage Current – Ground Disconnect      | I <sub>BUS_NO_GND</sub>  | V <sub>BB</sub> = 12 V, 0 V < V <sub>BUS</sub> < 18 V                                               | -1                      | _                     | 1                       | mA   |

| Leakage Current – Supply Disconnect      | I <sub>BUS_NO_BAT</sub>  | V <sub>BB</sub> = 0 V, 0 V < V <sub>BUS</sub> < 18 V                                                | -                       | _                     | 100                     | μA   |

|                                          |                          | Normal operation                                                                                    | 20                      | 30                    | 60                      | kΩ   |

| Bus Pull-Up Resistance                   | R <sub>SLAVE</sub>       | Sleep state                                                                                         | _                       | 2                     | -                       | MΩ   |

| Termination Diode Forward Voltage        | V <sub>SerDiode</sub>    |                                                                                                     | 0.4                     | 0.7                   | 1                       | V    |

| LIN/PWM INTERFACE BUS RECEIV             |                          | ·                                                                                                   | ·                       |                       | l                       |      |

| Receiver Center Voltage                  | V <sub>BUSCNT</sub>      |                                                                                                     | 0.475 × V <sub>BB</sub> | 0.5 × V <sub>BB</sub> | 0.525 × V <sub>BB</sub> | V    |

| Receiver Dominant State                  | V <sub>BUSdom</sub>      |                                                                                                     | -                       |                       | 0.4 × V <sub>BB</sub>   | V    |

| Receiver Recessive State                 | V <sub>BUSrec</sub>      |                                                                                                     | 0.6 × V <sub>BB</sub>   | _                     | _                       | V    |

| Receiver Hysteresis                      | V <sub>HYS</sub>         |                                                                                                     | 0.05 × V <sub>BB</sub>  | _                     | 0.175 × V <sub>BB</sub> | V    |

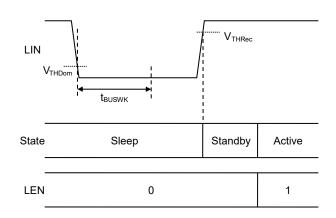

| Receiver Wake-Up Threshold Voltage       | V <sub>BUSwk</sub>       |                                                                                                     | 0.4 × V <sub>BB</sub>   | 0.5 × V <sub>BB</sub> | 0.6 × V <sub>BB</sub>   | V    |

## Three-Phase MOSFET Driver System IC

### **ELECTRICAL CHARACTERISTICS** (continued): Valid at $T_J = -40$ °C to 150 °C, $V_{BB} = 5.5$ to 50 V, unless otherwise specified

| Characteristic                                         | Symbol              | Test Conditions                                                                                                                                                                                                                              | Min.  | Тур. | Max.  | Unit |

|--------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

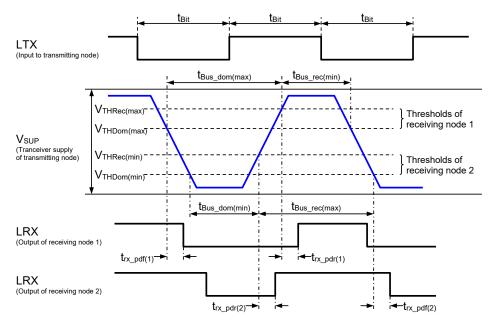

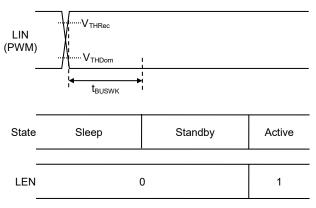

| LIN/PWM INTERFACE – TIMING PA                          | RAMETER             | S [11]                                                                                                                                                                                                                                       |       |      |       |      |