### Single and Dual High-Side Current-Sense Monitor with Power Calculation

#### Features

- · Single and Dual High-Side Current Sensor

- Current measurement is integrated over 2.5 ms to 2.6 seconds with up to 11-bit resolution

- 1% current measurement accuracy in positive range

- Measures V<sub>SOURCE</sub> voltages

- Calculates Power

- V<sub>SOURCE</sub> Voltage Range 0V to 40V

- Bidirectional Current Sensing

- Auto-Zero Input Offset Voltage

- Digital Averaging

- Adjustable sampling time and resolution

- 5 µA Typical Standby Current

- Programmable Sense Voltage Range

- ±10 mV, ±20 mV, ±40 mV, and ±80 mV

- Power Supply Range 3.0V to 5.5V

- Wide Temperature Operating Range: -40°C to +85°C

- ALERT Output for Voltage and Current out of Limit Transients Between Sampling Interval

- SMBus 2.0 Communications Interface

- Block Read and Block Write

- Address selectable by resistor decode

- Sample Time Configurable from 2.5 ms to 320 ms

- With averaging effective sampling times up to 2.6 seconds

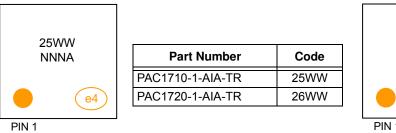

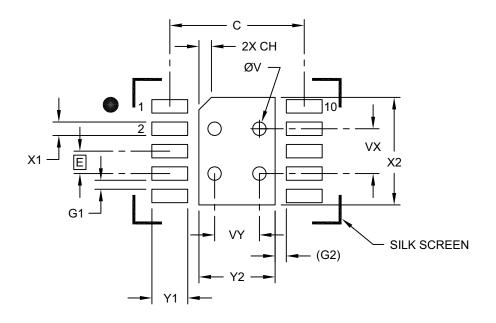

- 10-Lead 3 x 3 mm VDFN package

#### Applications

- Notebook and Desktop Computers

- Industrial

- Power Management Systems

- Embedded Applications

- · Servers

#### Description

The PAC1710/20 are single and dual high-side bidirectional current sensing monitors with precision voltage measurement capabilities. Each sensor measures the voltage developed across an external sense resistor to represent the high-side current of a battery or voltage regulator. The PAC1710/20 also measures the SENSE+ pin voltage and calculates average power over the integration period. The PAC1710/20 can be programmed to assert the ALERT pin when high and low limits are exceeded for Current Sense and Bus Voltage.

The PAC1710/20 device is good for measuring dynamic power. The long integration time allows for extending system polling cycles without losing any power consumption information. In addition the alert ensures that transient events are captured between the polling cycles.

Available in a RoHS compliant 3 x 3 mm 10-pin VDFN package.

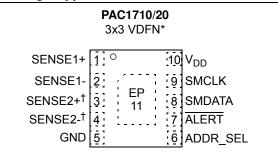

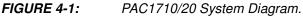

#### **Package Types**

\*Includes Exposed Thermal Pad (EP), see Table 3-1 †PAC1720 only.

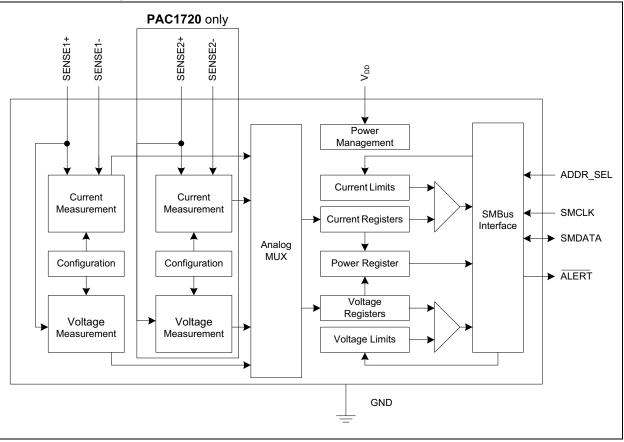

#### **Device Block Diagram**

### 1.0 ELECTRICAL CHARACTERISTICS

#### 1.1 Electrical Specifications

#### Absolute Maximum Ratings<sup>(†)</sup>

| V <sub>DD</sub> pin                              | 0.3 to 6.0V                      |

|--------------------------------------------------|----------------------------------|

| Voltage on SENSE- and SENSE+ pins                | 42 to 42V                        |

| Voltage on any other pin to GND                  | GND-0.3 to V <sub>DD</sub> +0.3V |

| Voltage between Sense pins ( (SENSE+ – SENSE-) ) | 40V                              |

| Input current to any pin except V <sub>DD</sub>  | +10 mA                           |

| Output short-circuit current                     | Continuous                       |

| Package Power Dissipation (Note)                 | 0.5W up to $T_A = 85^{\circ}C/W$ |

| Junction to Ambient $(\theta_{J-A})$             | 78°C/W                           |

| Operating Ambient Temperature Range              | 40 to 85°C                       |

| Storage Temperature Range                        | 55 to 150°C                      |

| ESD Rating – SMCLK, SMDATA, and ALERT pins – HBM | 8000V                            |

| SD Rating – all other pins – HBM                 | 2000V                            |

**† Notice**: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

**Note:** The Package Power Dissipation specification assumes a recommended thermal via design consisting of a 2 x 3 matrix of 0.3 mm (12 mil) vias at 0.9 mm pitch connected to the ground plane with a 1.6 mm x 2.3 mm thermal landing.

#### TABLE 1-1: DC CHARACTERISTICS

|                                                        | <sub>JRCE</sub> = 0V to 40V; t | ypical val | ues are at | $T_A = +25$ | 5°C, V <sub>DD</sub> | at T <sub>A</sub> = -40°C to +85°C,<br>, = 3.3V, V <sub>SOURCE</sub> = 24V,<br>V unless otherwise noted                                                            |

|--------------------------------------------------------|--------------------------------|------------|------------|-------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Characteristic                                         | Symbol                         | Min.       | Тур.       | Max.        | Unit                 | Conditions                                                                                                                                                         |

| Power Supply                                           |                                |            | •          |             |                      | •                                                                                                                                                                  |

| Voltage on SENSE+                                      | V <sub>SOURCE</sub>            | 0          | —          | 40          | V                    |                                                                                                                                                                    |

| V <sub>DD</sub> Range                                  | V <sub>DD</sub>                | 3.0        | _          | 5.5         | V                    |                                                                                                                                                                    |

| V <sub>DD</sub> Pin Supply<br>Current (PAC1720)        | I <sub>DD</sub>                |            | 0.525      | 1.3         | mA                   | Both measurement channels<br>enabled. Continuous conversions<br>(see Table 4-1)                                                                                    |

|                                                        |                                | _          | 13         | 50          | μA                   | Both measurement channels<br>enabled. One conversion per<br>second (see Table 4-1).<br>VSRC_SAMP_TIME = 2.5 ms<br>CS_SAMP_TIME = 2.5 ms<br>No SMBus communications |

| V <sub>DD</sub> Pin Supply<br>Current (PAC1710)        | I <sub>DD</sub>                | —          | 360        | 900         | μA                   | Continuous Conversions (see Table 4-1)                                                                                                                             |

|                                                        |                                | _          | 10         | 35          | μA                   | One conversion per second<br>(see Table 4-1).<br>VSRC_SAMP_TIME = 2.5 ms<br>CS_SAMP_TIME = 2.5 ms<br>No SMBus communications                                       |

| V <sub>DD</sub> Rise Rate                              | V <sub>DD_RISE</sub>           | 0.03       |            |             | V/ms                 | 0 to 3V in 100 ms                                                                                                                                                  |

| V <sub>DD</sub> Standby Current                        | I <sub>DD_STBY</sub>           | —          | 5.5        | 15          | μA                   | Standby state                                                                                                                                                      |

| Analog Input Characte                                  | eristics                       |            |            |             |                      |                                                                                                                                                                    |

| SENSE+/SENSE-<br>Pins Common-Mode<br>Voltage Range     | V <sub>CM</sub>                | 0          |            | 40          | V                    | Common-mode voltage on SENSE pins, referenced to ground                                                                                                            |

| V <sub>SENSE</sub> Differential<br>Input Voltage Range | V <sub>DIFF</sub>              | -80        | —          | +80         | mV                   | Voltage between SENSE+ and SENSE- pins                                                                                                                             |

| Current-Sense Power<br>Supply Rejection<br>Ratio       | PSRR_CS                        | _          | 10         | _           | μV/V                 | 3.0V < V <sub>DD</sub> < 5.5V                                                                                                                                      |

| Full-Scale Range (±)<br>(see Section 4.4               | FSR                            | -10        | —          | 10          | mV                   | 1 LSB = 4.885 μV<br>11-bit data resolution                                                                                                                         |

| "Current<br>Measurement")                              |                                | -20        | —          | 20          | mV                   | 1 LSB = 9.77 μV<br>11-bit data resolution                                                                                                                          |

|                                                        |                                | -40        | —          | 40          | mV                   | 1 LSB = 19.54 μV<br>11-bit data resolution                                                                                                                         |

|                                                        |                                | -80        | —          | 80          | mV                   | 1 LSB = 39.08 μV<br>11-bit data resolution                                                                                                                         |

| Common-Mode<br>Rejection                               | V <sub>SENSE</sub> _CMRR       | 80         | 100        | —           | dB                   | Common-Mode Rejection,<br>0V < V <sub>SOURCE</sub> < 40V                                                                                                           |

| SENSE+/SENSE-<br>Pins Common-Mode<br>Voltage Range     | V <sub>CM</sub>                | 0          | —          | 40          | V                    | Common-mode voltage on SENSE pins, referenced to ground                                                                                                            |

|                                                        |                                |            |            |             |                      |                                                                                                                                                                    |

#### TABLE 1-1: DC CHARACTERISTICS (CONTINUED)

**Electrical Characteristics**: Unless otherwise specified, maximum values are at  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ ,  $V_{DD} = 3V$  to 5.5V,  $V_{SOURCE} = 0V$  to 40V; typical values are at  $T_A = +25^{\circ}C$ ,  $V_{DD} = 3.3V$ ,  $V_{SOURCE} = 24V$ ,  $V_{SENSE} = (SENSE+ - SENSE-) = 0V$ ; Current Sense Full Scale Range = 80 mV unless otherwise noted

| Characteristic                                                                   | Symbol                                     | Min. | Тур. | Max. | Unit     | Conditions                                                     |

|----------------------------------------------------------------------------------|--------------------------------------------|------|------|------|----------|----------------------------------------------------------------|

| SENSE+, SENSE-Pin<br>Leakage Current                                             | I <sub>SENSE</sub> +, I <sub>SENSE</sub> - | —    | —    | 1.0  | μA       | V <sub>BUS</sub> = 24V, V <sub>SENSE</sub> = 0V<br>Sleep state |

| SENSE+, SENSE-Pin<br>Leakage Current                                             | I <sub>SENSE</sub> +, I <sub>SENSE</sub> - | —    | _    | 1.0  | μA       | $V_{DD} = 0V$                                                  |

| SENSE+ Pin Bias<br>Current                                                       | I <sub>SENSE</sub> +                       | —    | 100  | 150  | μA       | -80 mV < V <sub>SENSE</sub> < 80 mV<br>Active state            |

| SENSE- Pin Bias<br>Current                                                       | I <sub>SENSE-</sub>                        | —    | 0.1  | 1    | μA       | -80 mV < V <sub>SENSE</sub> < 80 mV<br>Active state            |

| Current-Sense Offset                                                             | Error Voltage                              |      |      |      |          |                                                                |

| Offset Error Voltage                                                             | V <sub>OS</sub>                            |      | ±15  |      | μV       | FSR = ±10 mV                                                   |

| (referred to input)                                                              |                                            |      | ±15  |      | μV       | FSR = ±20 mV                                                   |

|                                                                                  |                                            | _    | ±20  | _    | μV       | FSR = ±40 mV                                                   |

|                                                                                  |                                            | _    | ±40  | —    | μV       | FSR = ±80 mV                                                   |

| Current-Sense Total M                                                            | leasurement Erro                           | r    |      |      |          |                                                                |

| Total Error<br>(positive range)<br>(see Section 4.4<br>"Current<br>Measurement") | V <sub>SENSE</sub> _TOT_ERR                |      | ±0.5 | ±1   | %<br>FSR | FSR = 0 to +10 mV                                              |

|                                                                                  |                                            | —    | ±0.3 | ±0.6 | %<br>FSR | FSR = 0 to +20 mV                                              |

|                                                                                  |                                            | _    | ±0.2 | ±0.4 | %<br>FSR | FSR = 0 to +40 mV                                              |

|                                                                                  |                                            | —    | ±0.2 | ±0.4 | %<br>FSR | FSR = 0 to +80 mV                                              |

| Total Error<br>(negative range)<br>(see Section 4.4<br>"Current<br>Measurement") | V <sub>SENSE</sub> _TOT_ERR                | -1   | -1.3 | -1.6 | %<br>FSR | FSR = -10 mV to 0                                              |

|                                                                                  |                                            | -1   | -1.3 | -1.6 | %<br>FSR | FSR = -20 mV to 0                                              |

|                                                                                  |                                            | -1   | -1.3 | -1.6 | %<br>FSR | FSR = -40 mV to 0                                              |

|                                                                                  |                                            | -1.6 | -2   | -2.4 | %<br>FSR | FSR = -80 mV to 0                                              |

| V <sub>SOURCE</sub> Voltage Mea                                                  | surement                                   |      |      |      |          |                                                                |

| Power Supply<br>Rejection Ratio                                                  | PSRR                                       |      | 10   |      | mV/V     | 3.0V < V <sub>DD</sub> < 5.5V                                  |

| V <sub>SOURCE</sub> Error (±)                                                    | V <sub>SOURCE_ERR</sub>                    | _    | 0.15 | 0.3  | %<br>FSV |                                                                |

#### TABLE 1-1: DC CHARACTERISTICS (CONTINUED)

**Electrical Characteristics**: Unless otherwise specified, maximum values are at  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ ,  $V_{DD} = 3V$  to 5.5V,  $V_{SOURCE} = 0V$  to 40V; typical values are at  $T_A = +25^{\circ}C$ ,  $V_{DD} = 3.3V$ ,  $V_{SOURCE} = 24V$ ,  $V_{SENSE} = (SENSE+ - SENSE-) = 0V$ ; Current Sense Full Scale Range = 80 mV unless otherwise noted

| Characteristic                                                    | Symbol                  | Min. | Тур. | Max. | Unit     | Conditions                                                     |

|-------------------------------------------------------------------|-------------------------|------|------|------|----------|----------------------------------------------------------------|

| Power Ratio                                                       | Cymbol                  |      | 196. | mux. | onit     | Conditions                                                     |

| Total Power Ratio<br>Measurement Error<br>(±)<br>(positive range) | P <sub>RATIO</sub> _ERR | -    | —    | 1    | %<br>FSR | FSR = 0 to +10 mV, 0 to +20 mV,<br>0 to +40 mV, or 0 to +80 mV |

| Total Power Ratio<br>Measurement Error<br>(±)<br>(negative range) | t Error                 |      | —    | 2    | %<br>FSR | FSR = -10 mV to 0, -20 mV to 0,<br>-40 mV to 0, or -80 mV to 0 |

| First Power Ratio<br>Ready                                        | t <sub>CONV_P</sub>     | —    | —    | 220  | ms       | Time after power-up before P <sub>RATIO</sub> updated          |

| Digital I/O Pins (SMCL                                            | K, SMDATA, ALE          | RT)  |      |      |          |                                                                |

| Pull-up Voltage Range                                             | V <sub>PULLUP</sub>     | 3.0  | _    | 5.5  | V        | Pull-up voltage for SMBus and ALERT pins                       |

| Time to First<br>Communications                                   | t <sub>COMM</sub>       | —    | —    | 25   | ms       |                                                                |

| Input High Voltage                                                | V <sub>IH</sub>         | 2.0  | _    | —    | V        | SMCLK, SMDATA<br>OD pins pulled up to V <sub>PULLUP</sub>      |

| Input Low Voltage                                                 | V <sub>IL</sub>         | _    |      | 0.8  | V        |                                                                |

| Output Low Voltage                                                | V <sub>OL</sub>         | _    | _    | 0.4  | V        | OD pin pulled to V <sub>PULLUP</sub><br>3 mA current sink      |

| Leakage Current (±)                                               | I <sub>LEAK</sub>       |      |      | 5    | μA       | Powered or unpowered<br>T <sub>A</sub> < +85°C                 |

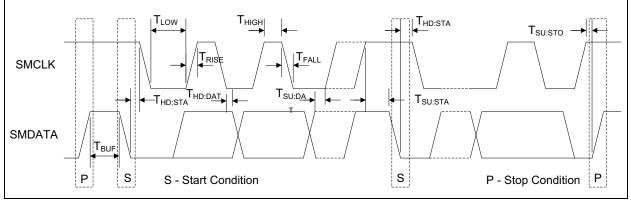

| <b>Electrical Characteristics</b> : Unless otherwise specified, maximum values are at $T_A = -40^{\circ}C$ to +85°C, $V_{DD} = 3V$ to 5.5V, $V_{BUS} = 0V$ to 32V; Typical values are at $T_A = +25^{\circ}C$ , $V_{DD} = 3.3V$ , $V_{BUS} = 24V$ , $V_{SENSE} = (SENSE+ - SENSE-) = 0V$ |                     |      |      |      |       |                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|------|------|-------|-------------------------------------|

| Characteristic                                                                                                                                                                                                                                                                           | Sym.                | Min. | Тур. | Max. | Units | Conditions                          |

| SMBus Interface                                                                                                                                                                                                                                                                          | <u> </u>            |      | 1    | 1    |       |                                     |

| Input Capacitance                                                                                                                                                                                                                                                                        | C <sub>IN</sub>     | _    | 4    | 10   | pF    |                                     |

| SMBus Timing                                                                                                                                                                                                                                                                             |                     |      |      |      |       |                                     |

| Clock Frequency                                                                                                                                                                                                                                                                          | f <sub>SMB</sub>    | 10   | —    | 400  | kHz   |                                     |

| Spike Suppression                                                                                                                                                                                                                                                                        | t <sub>SP</sub>     |      | —    | 100  | ns    |                                     |

| Bus Free Time Stop to<br>Start                                                                                                                                                                                                                                                           | t <sub>BUF</sub>    | 1.3  | —    | _    | μs    |                                     |

| Start Setup Time                                                                                                                                                                                                                                                                         | t <sub>SU:STA</sub> | 0.6  | —    | —    | μs    |                                     |

| Start Hold Time                                                                                                                                                                                                                                                                          | t <sub>HD:STA</sub> | 0.6  | —    | —    | μs    |                                     |

| Stop Setup Time                                                                                                                                                                                                                                                                          | t <sub>SU:STO</sub> | 0.6  | —    | —    | μs    |                                     |

| Data Hold Time                                                                                                                                                                                                                                                                           | t <sub>HD:DAT</sub> | 0    | —    | —    | μs    | When transmitting to the master     |

| Data Hold Time                                                                                                                                                                                                                                                                           | t <sub>HD:DAT</sub> | 0.3  |      | —    | μs    | When receiving from the master      |

| Data Setup Time                                                                                                                                                                                                                                                                          | t <sub>SU:DAT</sub> | 0.6  | —    | —    | μs    |                                     |

| Clock Low Period                                                                                                                                                                                                                                                                         | t <sub>LOW</sub>    | 1.3  | —    | —    | μs    |                                     |

| Clock High Period                                                                                                                                                                                                                                                                        | t <sub>HIGH</sub>   | 0.6  |      | —    | μs    |                                     |

| Clock/Data Fall Time                                                                                                                                                                                                                                                                     | t <sub>FALL</sub>   | —    |      | 300  | ns    | $Min = 20 + 0.1 C_{LOAD} ns$        |

| Clock/Data Rise Time                                                                                                                                                                                                                                                                     | t <sub>RISE</sub>   | _    | _    | 300  | ns    | Min = 20 + 0.1 C <sub>LOAD</sub> ns |

| Capacitive Load                                                                                                                                                                                                                                                                          | C <sub>LOAD</sub>   | —    |      | 400  | pF    | Total per bus line                  |

#### TABLE 1-2: SMBUS MODULE SPECIFICATIONS

FIGURE 1-1:

NOTES:

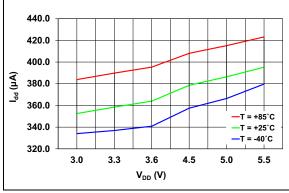

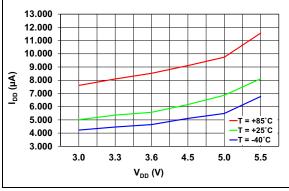

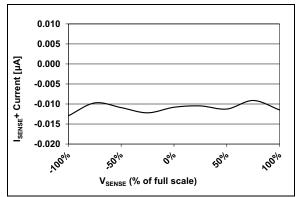

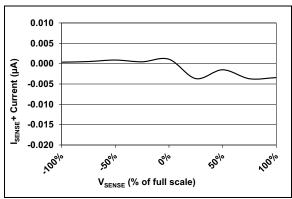

### 2.0 TYPICAL OPERATING CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

**Note:** Unless otherwise indicated, maximum values are at  $T_A = -40^{\circ}C$  to +85°C,  $V_{DD} = 3V$  to 5.5V,  $V_{SOURCE} = 0V$  to 40V; typical values are at  $T_A = +25^{\circ}C$ ,  $V_{DD} = 3.3V$ ,  $V_{SOURCE} = 24V$ ,  $V_{SENSE} = (SENSE+ - SENSE-) = 0V$ .

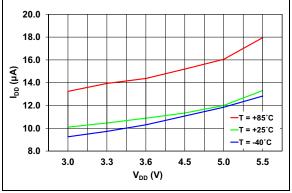

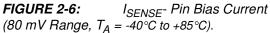

FIGURE 2-1: I<sub>DD</sub> vs. V<sub>DD</sub>, Continuous Conversions (PAC1710).

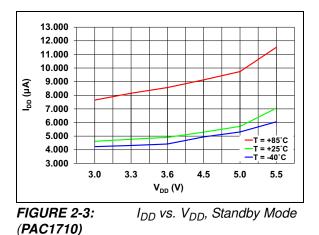

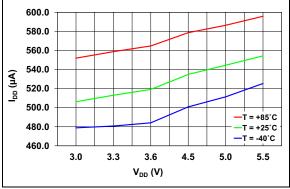

**FIGURE 2-2:** I<sub>DD</sub> vs. V<sub>DD</sub>, One Conversion per Second, Lowest Resolution (**PAC1710**).

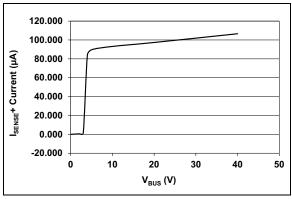

**FIGURE 2-4:**  $I_{SENSE}$ + Pin Current vs.  $V_{BUS}$  ( $T_A$  = -40°C to +85°C).

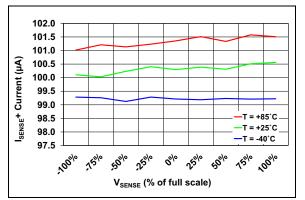

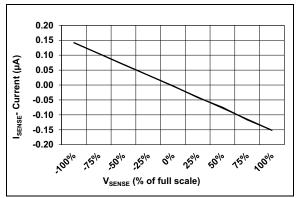

*FIGURE 2-5: I*<sub>SENSE</sub>+ Pin Bias Current (80 mV Range).

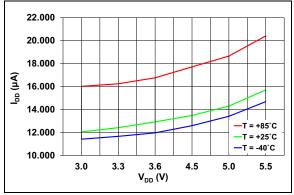

*FIGURE 2-7:* I<sub>DD</sub> vs. V<sub>DD</sub>, Continuous Conversions (**PAC1720**).

FIGURE 2-8: I<sub>DD</sub> vs. V<sub>DD</sub>, One Conversion per Second, Lowest Resolution (PAC1720).

FIGURE 2-9: (PAC1720).

I<sub>DD</sub> vs. V<sub>DD</sub>, Standby Mode

**FIGURE 2-10:**  $I_{SENSE}$ + Pin Leakage Current,  $T_A$  = -40°C to +85°C.

**FIGURE 2-11:**  $I_{SENSE}$ - Pin Leakage Current,  $T_A = -40$  °C to +85 °C.

#### 3.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 3-1.

| TADLE 5-1.             | FIN DESCRIPTIONS |                         |                                                    |

|------------------------|------------------|-------------------------|----------------------------------------------------|

| PAC1710/20<br>3x3 VDFN | Symbol           | Type<br>(See Table 3-2) | Description                                        |

| 1                      | SENSE1+          | AIO40                   | VBUS1/VSENSE1+ input                               |

| 2                      | SENSE1-          | AIO40                   | VSENSE1- input                                     |

| 3                      | SENSE2+          | AIO40                   | VBUS2/VSENSE2+ input                               |

| 4                      | SENSE2-          | AIO40                   | VSENSE2- input                                     |

| 5                      | GND              | Power                   | Ground                                             |

| 6                      | ADDR_SEL         | AIO                     | Selects SMBus/I <sup>2</sup> C™ address            |

| 7                      | ALERT            | DO                      | SMBus Alert Pin                                    |

| 8                      | SMDATA           | DIOD                    | SMDATA: SMBus - requires pull-up resistor          |

| 9                      | SMCLK            | DI                      | SMCLK: SMBus - requires pull-up resistor           |

| 10                     | V <sub>DD</sub>  | Power                   | Positive power supply voltage                      |

| 11                     | EP               |                         | Not internally connected, but recommend grounding. |

#### TABLE 3-2: PIN TYPES DESCRIPTION

| Pin Type | Description                                                                                        |

|----------|----------------------------------------------------------------------------------------------------|

| Power    | This pin is used to power the device                                                               |

| AIO40    | Analog Input/Output – this pin is used as<br>an I/O for analog signals.<br>Maximum voltage is 40V. |

| AIO5     | Analog Input/Output – this pin is used as<br>an I/O for analog signals.<br>Maximum voltage is 5V.  |

| DI       | Digital Input – this pin is used for digital inputs                                                |

| DIOD     | Digital Input/Output Open Drain – this pin is used for digital I/O and is open drain               |

#### 3.1 Sense1+/Sense1-

These two pins form the differential input for measuring voltage across a sense resistor in the application. The positive input (Sense1+) also acts as the input pin for bus voltage.

#### 3.2 Sense2+/Sense2- (PAC1720 only)

These two pins form the differential input for measuring voltage across a sense resistor in the application. The positive input (Sense2 +) also acts as the input pin for bus voltage.

#### 3.3 Ground (GND)

System ground.

#### 3.4 Address Selection (ADDR\_SEL)

Address selection for the SMBus Slave address, based on the pull-down resistor.

#### 3.5 SMBus ALERT (ALERT)

This pin is the SMBus ALERT pin that is asserted under fault conditions.

#### 3.6 SMBus Data (SMDATA)

This is the bidirectional SMBus data pin. This pin is open drain, and requires a pull-up resistor.

#### 3.7 SMBus Clock (SMCLK)

This is the SMBus clock pin. This pin is open drain, and requires a pull-up resistor.

## 3.8 Positive Power Supply Voltage (V<sub>DD</sub>)

Power supply input pin for the device.

#### 3.9 Exposed Thermal Pad (EP)

This pad should be connected to ground for noise immunity.

NOTES:

#### 4.0 GENERAL DESCRIPTION

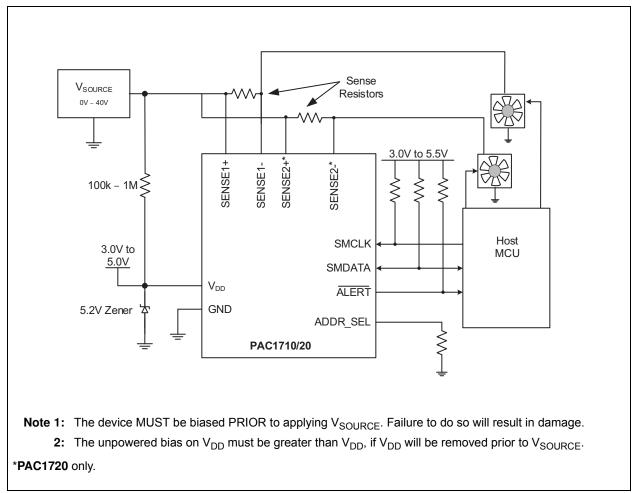

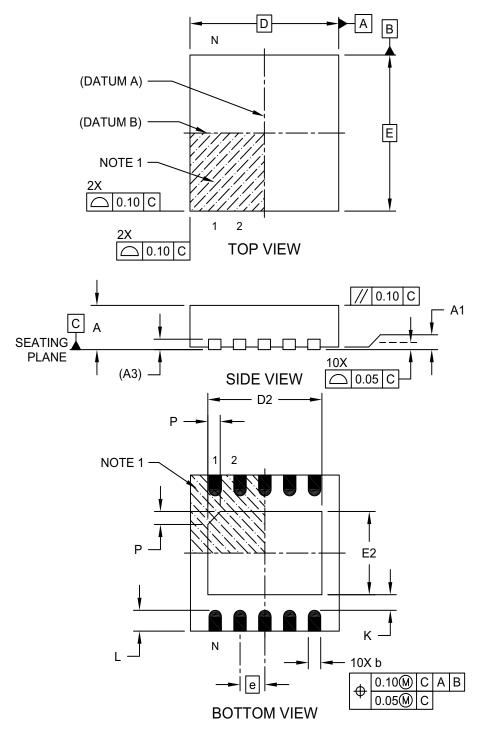

The PAC1710/20 is a bidirectional high-side current-sensing device with precision voltage measurement capabilities. It measures the voltage developed across an external sense resistor to represent the high-side current of a battery or voltage regulator. The PAC1710/20 also measures the SENSE1+ and SENSE2+ pin voltages ( $V_{SOURCE}$ ) and calculates average power over the integration period.

The PAC1710/20 measures the differential voltage across an external sense resistor, digitizes it with a variable resolution (6-bit to 11-bit plus sign) Sigma-Delta ADC, and transmits via the SMBus or the  $I^2C^{TM}$  protocol. The current range allows for large variations in measured current with high accuracy and low voltage drop across the resistor.

The PAC1710/20 has programmable high and low limits for <u>current</u> sense and bus voltage with a maskable ALERT signal to the host when an out-of-limit measurement occurs.

A system diagram is shown in Figure 4-1.

#### 4.1 Power States

The PAC1710/20 has three states of operation:

- Active The PAC1710/20 initiates conversion cycles for the programmed conversion rate.

- Standby This is the lowest power state. There are no conversion cycles. The majority of circuitry is powered-down to reduce supply current to a minimum. The SMBus is active and the part will return requested data. To enter the Standby state, disable all measurements (see Register 6-1).

- One-Shot While the device is in the Standby state, the host can initiate a conversion cycle on demand (see Register 6-3). After the conversion cycle is complete, the device will return to the Standby state.

#### 4.2 Conversion Cycle

The conversion cycle is the period of time in which the measurements are taken and the data is updated. In the Active state, individual measurement can be disabled. In the Standby state, all measurements are updated.

During the conversion cycle, both channels on the PAC1720 begin taking measurements at the same time. In both devices, the V<sub>SENSE</sub> sample is taken first for its programmed sample time. Then, the V<sub>SOURCE</sub> sample is taken for its programmed sample time. Digital averaging may be applied to average the last 2-8 samples. Sample time and digital averaging have separate controls for V<sub>SENSE</sub> and V<sub>SOURCE</sub> as well as for each channel, in the case of PAC1720. (see Register 6-7 and Register 6-8).

At the end of the conversion cycle, the enabled measurements are updated. The Power Ratio, High Limit Status (which includes a CONV\_DONE status bit), and Low Limit Status registers are always updated. The ALERT pin will be asserted, by default, if any out-of-limit conditions exist (see Section 4.7 "ALERT Output").

#### 4.3 Conversion Rate

For power management in the Active state, a conversion rate can be programmed. Conversion rate specifies how often measurement data should be updated. Once per second is the lowest setting (see Register 6-2).

If the actual sampling time for both measurements (V<sub>SOURCE</sub> and V<sub>SENSE</sub>) is greater than 1/conversion rate for either channel, the PAC1710/20 will override the programmed conversion rate and operate in continuous mode.

#### 4.4 Current Measurement

The PAC1710/20 includes one or two high-side current sensing circuits. These circuits measure the voltage ( $V_{SENSE}$ ) induced across a fixed external current sense resistor ( $R_{SENSE}$ ) and stores the voltage as a signed 11-bit (by default) number in the Sense Voltage registers.

The PAC1710/20 current sensing operates in one of four bipolar Full-Scale Ranges (FSR): ±10 mV, ±20 mV, ±40 mV, or ±80 mV (see Section 4.4 "Current Measurement"). The default FSR is ±80 mV.

Full-Scale Current (FSC) can be calculated from Equation 4-1.

$FSC = \frac{FSR}{R_{SENSE}}$

Where:

| FSC         | = | Full-scale current                                                    |

|-------------|---|-----------------------------------------------------------------------|

| FSR         | = | $\pm 10$ mV, $\pm 20$ mV, $\pm 40$ mV, or $\pm 80$ mV (see Table 4-6) |

| $R_{SENSE}$ | = | External sense resistor value                                         |

The actual current through  $R_{SENSE}$  can then be calculated using Equation 4-2.

#### EQUATION 4-2: BUS CURRENT

$$I_{BUS} = FSC \times \frac{V_{SENSE}}{Denominator}$$

Where:

$I_{BUS}$  = Actual bus current

- FSC = Full-scale current value (from Equation 4-1)

- V<sub>SENSE</sub> = The value read from the Sense Voltage Registers (in decimal), ignoring the four lowest bits which are always zero (see Register 6-10 and Register 6-11 for PAC1720) Denominator = Determined by the sample time, as shown in Table 4-5.

As an example, suppose the system is drawing 1.65A through a 10 m $\Omega$  resistor, the FSR is set for ±20 mV, and sample time is 80 ms. Using Equation 4-1, the FSC is 2A. The measured V<sub>SENSE</sub> is 1.65A \* 10 m $\Omega$  = 16.5 mV. This value of V<sub>SENSE</sub> is represented in the Sense Voltage Registers as 69\_8h (0110\_1001\_1000b or 1688d) ignoring the 4 lower bits of the low byte as these are always 0. This value, when applied to Equation 4-2, results in an I<sub>BUS</sub> current of 1.649A.

For a negative voltage, the Sense Voltage Registers are read as 96 0h (again ignoring the lower 4 bits of the low byte as these are always 0). To calculate current, the binary value is first converted from two's complement by inverting the bits and adding one:

**96 80h =** 1001\_0110\_1000b. Inverting equals 0110 1001 0111b (69 7h) and adding one gives 0110\_1001\_1000b (69 8h).

This results in the same calculated value as in the positive voltage case.

#### 4.5 **Voltage Measurement**

The pin voltage is measured on the supply side of the appropriate SENSE+ pin and stored as an unsigned 11-bit number in the V<sub>SOURCE</sub> Voltage Registers as V<sub>SOURCE</sub> (see Register 6-12).

Full-Scale Voltage (FSV) is given by the maximum value of the V<sub>SENSE</sub> Voltage Registers:

$FSV = 40 - \frac{40}{Denominator}$

40

Where:

FSV = Full scale voltage

Denominator = determined by the sample time, as shown in Table 4-2

Actual voltage at SENSE+ can be calculated using Equation 4-4.

#### **EQUATION 4-4: BUS VOLTAGE**

| $V_{SOURCE_PIN} = FSV \times \frac{V_{SOURCE}}{Denominator}$<br>Where: |   |                                                                                                                                                                                                  |  |  |  |

|------------------------------------------------------------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                        |   |                                                                                                                                                                                                  |  |  |  |

| V <sub>SOURCE_PIN</sub>                                                | = | The actual voltage on the<br>SENSE1+/SENSE2+ pin                                                                                                                                                 |  |  |  |

| FSV                                                                    | = | The full-scale voltage (from Equation 4-3)                                                                                                                                                       |  |  |  |

| V <sub>SOURCE</sub>                                                    | = | The value read from the<br>V <sub>SOURCE</sub> Voltage Registers (in<br>decimal), ignoring the lowest<br>five bits which are always zero<br>(see Section 4.11 "VSOURCE<br>Data representation"). |  |  |  |

| Denominator                                                            | = | Determined by the sample time, as shown in Table 4-2                                                                                                                                             |  |  |  |

As an example using 10-bit resolution, suppose that the actual pin voltage is 24V. The V<sub>SOURCE</sub> Voltage Registers will report a value of 99 80h (1001\_1001\_10XX\_XXXb) in 10-bit resolution (default). When reading the data, the lower 5 bits are always ignored. Because the default operation is to measure the  $V_{\text{SOURCE}}$  voltage with 10-bit resolution, the sixth bit is likewise ignored. Therefore, decoding the upper 10 bits results in a decimal value of 614. This value, when applied in Equation 4-3, results in V<sub>SOURCE PIN</sub> equal to 23.98V.

As an example using 11-bit resolution, suppose that the actual pin voltage is 10.65V. The  $V_{\ensuremath{\mathsf{SOURCE}}}$  Voltage Registers will report a value of 44\_10h (0100\_0100\_001x\_xxxxb). Because the lower 5 bits are ignored, the decimal result is 545d. This value, when applied in Equation 4-4, results in V<sub>SOURCE PIN</sub> equal to 10.64V.

The V<sub>SOURCE</sub> voltage may also be determined by scaling each bit set by the indicated bit weighting as described in Section 4.11 "VSOURCE Data representation".

#### 4.6 **Power Calculation**

The PAC1710/20 may be used to determine the average power provided at the source side of SENSE+ (SENSE1+ and SENSE2+) using the value P<sub>RATIO</sub>, contained in the Power Ratio Registers (see Register 6-14). The value represents the percentage of maximum calculable power.

PRATIO is mathematically generated by multiplying the absolute values of V<sub>SENSE</sub> and V<sub>SOURCE</sub> (see "Current Measurement" Section 4.4 and Section 4.5 "Voltage Measurement") and is stored as a 16-bit number.  $\mathsf{P}_{\mathsf{RATIO}}$  is updated whenever either V<sub>SENSE</sub> or V<sub>SOURCE</sub> is updated.

Full-scale power can be calculated from Equation 4-5.

#### **FULL-SCALE POWER** EQUATION 4-5:

| $FSP = FSC \times FSV$ |   |                                            |  |  |  |

|------------------------|---|--------------------------------------------|--|--|--|

| Where                  | : |                                            |  |  |  |

|                        |   |                                            |  |  |  |

| FSP                    | = | The full-scale power                       |  |  |  |

| FSC                    | = | The full-scale current (from Equation 4-1) |  |  |  |

| FSV                    | = | The full-scale voltage (from Equation 4-3) |  |  |  |

Actual power drawn from the source can be calculated using Equation 4-6.

#### EQUATION 4-6: BUS POWER

Whe

P

$$P_{BUS} = FSP \times \frac{P_{RATIO}}{65, 535}$$

re:

BUS = The actual power provided by the source measured at SENSE+

| FSP                | = | the full-scale power (from          |  |  |

|--------------------|---|-------------------------------------|--|--|

|                    |   | Equation 4-5)                       |  |  |

| P <sub>RATIO</sub> | = | the value read from the Power Ratio |  |  |

|                    |   | Registers (in decimal). See         |  |  |

|                    |   | Register 6-14 and Register 6-15     |  |  |

As an example, suppose that the actual pin voltage is 10.65V, the current through a 10 m $\Omega$  resistor is 1.65A, the FSR is set for ±20 mV, and the sample times are the defaults. The FSC value is 2A per Equation 4-1. The FSV value is 39.96V per Equation 4-4. Using Equation 4-5, the FSP value is 79.92W. Applying P = V \* I, the expected power is 17.57W which is 21.98% of the FSP value.

Reading the Power Ratio Registers will report  $P_{RATIO}$  as 38\_47h (0011\_1000\_0100\_0111b or 14,407d). Using Equation 4-6, this value results in a calculated bus power of 17.57W which is ~21.98% of the FSP value.

### 4.7 ALERT Output

The  $\overline{\text{ALERT}}$  pin is an open-drain output and requires a pull-up resistor to  $V_{\text{PULLUP}}$

The ALERT pin is used as an interrupt signal or as an SMBus Alert signal that allows an SMBus slave to communicate an error condition to the master. One or more SMBus Alert outputs can be hardwired together.

The ALERT pin will be asserted (by default) if the measured V<sub>SOURCE</sub> voltage or V<sub>SENSE</sub> voltage are out of limit ( $\geq$  high limit or < low limit). The ALERT pin will remain asserted as long as an out-of-limit condition remains. Once the out-of-limit condition has been removed, the ALERT pin will remain asserted until the appropriate status bits are cleared.

The ALERT pin can be masked for all out-of-limit measurements by setting the MASK\_ALL bit (see Register 6-1) or for an individual <u>out-of-limit</u> measurement (see Register 6-5). Once the ALERT pin has been masked, it will be de-asserted if no unmasked out-of-limit conditions exist. Any interrupt conditions that occur while the ALERT pin is masked will update the status registers normally.

The  $\overline{\text{ALERT}}$  pin can be asserted for 5 µs when all measurements are finished (if enabled by setting CONV\_DONE\_EN, see Register 6-1).

#### 4.8 Conversion Rate

The Conversion Rate controls how often  $V_{SENSE}$ ,  $V_{SOURCE}$ ,  $P_{RATIO}$  and the status bits are updated in the Active state (see Table 4-1). The conversion rate should only be updated when the PAC1710/20 is in the Standby state. To do this, disable the measurements in the Configuration Register 00h, wait for the conversion cycle to complete by monitoring the XMEAS\_DIS bits in 00h until they stay set to '1', change the conversion rate, and then enable the desired measurements.

| TABLE 4-1: | <b>CONVERSION RATE FOR</b> |

|------------|----------------------------|

|            | MEASUREMENT                |

| CONV_R | ATE<2:0> | Conversion Bate      |  |

|--------|----------|----------------------|--|

| 1      | 0        | Conversion Rate      |  |

| 0      | 0        | 1 per sec            |  |

| 0      | 1        | 2 per sec            |  |

| 1      | 0        | 4 per sec            |  |

| 1      | 1        | Continuous (default) |  |

#### 4.9 Sampling Time and Resolution

The PAC1710/20 sampling interval and resolution for measuring V<sub>SOURCE</sub> and V<sub>SENSE</sub> are register controlled. The V<sub>SOURCE</sub> settings based on register values are shown in Table 4-2 and Table 4-3. The V<sub>SENSE</sub> measurements have an additional parameter: Full-Scale Resolution of the differential input. The V<sub>SENSE</sub> settings based on register values are shown in Table 4-4, Table 4-5 and Table 4-6.

#### TABLE 4-2: VOLTAGE SOURCE SAMPLING TIME SETTINGS

|                |   | •••••••••••••••••                   |                             |                             |  |  |  |

|----------------|---|-------------------------------------|-----------------------------|-----------------------------|--|--|--|

| VSRC_SAMP_TIME |   | Vsounce<br>Sample Time              | Equation 4-3<br>Denominator | Equation 4-4<br>Denominator |  |  |  |

| 0              | 0 | 2.5 ms (data = 8 bits)              | 256                         | 255                         |  |  |  |

| 0              | 1 | 5 ms (data = 9 bits)                | 512                         | 511                         |  |  |  |

| 1              | 0 | 10 ms (data = 10 bits)<br>(Default) | 1024                        | 1023                        |  |  |  |

| 1              | 1 | 20 ms (data = 11 bits)              | 2048                        | 2047                        |  |  |  |

### TABLE 4-3:VOLTAGE SOURCEAVERAGING SETTINGS

| VSRC | _AVG | Samples to Average |

|------|------|--------------------|

| 0 0  |      | Disabled (default) |

| 0    | 1    | 2                  |

| 1    | 0    | 4                  |

| 1    | 1    | 8                  |

### TABLE 4-4:CURRENT-SENSINGAVERAGING SETTINGS

| CS_SAMP | _AVG<1:0> | Samples to Average |

|---------|-----------|--------------------|

| 0       | 0         | Disabled (default) |

| 0       | 1         | 2                  |

| 1       | 0         | 4                  |

| 1       | 1         | 8                  |

TABLE 4-5:CURRENT-SENSING<br/>SAMPLING TIME SETTINGS

| cs_samp_time<2:0> |   |   | Current Sensor<br>Sample Time  | Equation 4-2<br>Denominator |

|-------------------|---|---|--------------------------------|-----------------------------|

| 0                 | 0 | 0 | 2.5 ms (Data = sign + 6 bits)  | 63                          |

| 0                 | 0 | 1 | 5 ms (Data = sign + 7 bits)    | 127                         |

| 0                 | 1 | 0 | 10 ms (Data = sign + 8 bits)   | 255                         |

| 0                 | 1 | 1 | 20 ms (Data = sign + 9 bits)   | 511                         |

| 1                 | 0 | 0 | 40 ms (Data = sign + 10 bits)  | 1023                        |

| 1                 | 0 | 1 | 80 ms (Data = sign + 11 bits)  | 2047                        |

|                   |   |   | (default)                      |                             |

| 1                 | 1 | 0 | 160 ms (Data = sign + 11 bits) | 2047                        |

| 1                 | 1 | 1 | 320 ms (Data = sign + 11 bits) | 2047                        |

**Note 1:** 160 ms sampling time has built-in 2X analog oversampling using ADC at 12-bit resolution.

TABLE 4-6: CURRENT-SENSING RANGE SETTINGS

| CS_RN | G<1:0> | Full Scale Range          |

|-------|--------|---------------------------|

| 0     | 0      | -10 mV to 10 mV           |

| 0     | 1      | -20 mV to 20 mV           |

| 1     | 0      | -40 mV to 40 mV           |

| 1     | 1      | -80 mV to 80 mV (default) |

#### 4.10 Sense Voltage measurement Resolution

The Sense Voltage Registers store the measured  $V_{SENSE}$  value (see Section 4.4 "Current Measurement"). Note that the bit weighting values are for representation of the voltage relative to full scale. There is no internal scaling of data and all normal binary bit weightings still apply.

The Sense Voltage Registers data format is standard two's complement format with the positive full-scale value (7F\_Fh) and negative full-scale value (80\_0h) equal to the programmed FSR.

The Sign bit indicates the direction of current flow. If the Sign bit is '0', the current is flowing through  $R_{SENSE}$  from the SENSE+ pin to the SENSE- pin. If the Sign bit is '1', the current is flowing through  $R_{SENSE}$  from the SENSE- pin to the SENSE+ pin.

Data resolution is dependent upon sampling time as shown in Table 4-8. The data format (assuming 11-bit resolution) is shown in Table 4-7. This data will scale directly with the sampling time.

TABLE 4-7: V<sub>SENSE</sub> DATA FORMAT

| V <sub>SENSE</sub>    | Binary         | Hex<br>(as read by<br>registers) |

|-----------------------|----------------|----------------------------------|

| - Full-Scale          | 1000_0000_0000 | 80_0h                            |

| -2 LSB                | 1111_1111_1110 | FF_Eh                            |

| -1 LSB                | 1111_1111_1111 | FF_Fh                            |

| 0                     | 0000_0000_0000 | 00_0h                            |

| +1 LSB                | 0000_0000_0001 | 00_1h                            |

| +2 LSB                | 0000_0000_0010 | 00_2h                            |

| +Full-Scale<br>-1 LSB | 0111_1111_1111 | 7F_Fh                            |

TABLE 4-8: V<sub>SENSE</sub> DATA RESOLUTION

| Sampling | Resolution (±) |          |          |          |  |

|----------|----------------|----------|----------|----------|--|

| Time     | ±10 mV         | ±20 mV   | ±40 mV   | ±80 mV   |  |

| 2.5 ms   | 156.3 µV       | 312.5 µV | 625.0 µV | 1.250 mV |  |

| 5 ms     | 78.13 µV       | 156.3 µV | 312.5 µV | 625.0 µV |  |

| 10 ms    | 39.06 µV       | 78.13 µV | 156.3 µV | 312.5 µV |  |

| 20 ms    | 19.53 µV       | 39.06 µV | 78.13 µV | 156.3 µV |  |

| 40 ms    | 9.76 µV        | 19.53 µV | 39.06 µV | 78.13 µV |  |

| ≥ 80 ms  | 4.88 µV        | 9.76 µV  | 19.53 µV | 39.06 µV |  |

**<sup>2:</sup>** 320 mx sampling time has built-in 4X analog oversampling using ADC at 13-bit resolution.

#### 4.11 V<sub>SOURCE</sub> Data representation

The V<sub>SOURCE</sub> Voltage Registers store the measured V<sub>SOURCE</sub> value (see Section 4.5 "Voltage Measurement"). The measured voltage is determined by summing the bit weights of each bit set. For example, if V<sub>SOURCE</sub> was 7.4V, the V<sub>SOURCE</sub> Voltage Registers would read 0010\_1111 for the high byte and 0100\_0000b for the low byte corresponding to 5V + 1.25V + 0.625V + 0.3125V + 0.1563V + 0.0390V = 7.3828V.

The bit weightings are assigned for human interpretation. They should be disregarded when translating the information via a computing system, as shown in **Section 4.5** "Voltage Measurement".

The  $V_{SOURCE}$  Voltage Registers cannot support negative values, so all values less than 0V will be recorded as 0V.

#### 4.12 Power Ratio Data Representation

The Power Ratio Registers store a power factor value,  $P_{RATIO}$ , that is used to determine the final average power delivered to the system (see Section 4.6 "Power Calculation").  $P_{RATIO}$  is the result of the multiplication of the V<sub>SENSE</sub> reading and the V<sub>SOURCE</sub> reading values shifted to a 16-bit number. It represents the ratio of delivered power with respect to maximum power.

#### 4.13 Limit Registers

$\frac{\text{These}}{\text{ALERT}} \text{ registers are used in concordance with the} \\ \frac{\text{ALERT}}{\text{ALERT}} \text{ pin to indicate when high or low limits have been exceeded.}$

#### 4.13.1 V<sub>SENSE</sub> LIMITS

The V<sub>SENSE</sub> Limit Registers store a high and low limit for V<sub>SENSE</sub>. V<sub>SENSE</sub> is compared against both limits after each conversion cycle.

The data format for the limit is a raw binary form that is relative to the maximum  $\mathsf{V}_{\mathsf{SENSE}}$  that has been programmed.

If the measured sense voltage meets or exceeds the high limit or drops below the low limit, the ALERT pin is asserted (by default, see Section 4.7 "ALERT Output") and the VSENSE\_HIGH or VSENSE\_LOW status bits are set in the High Limit Status or Low Limit Status registers (see Register 6-16 and Register 6-18).

#### 4.13.2 V<sub>SOURCE</sub> LIMITS

The V<sub>SOURCE</sub> Voltage Limit registers store the high and low limits for V<sub>SOURCE</sub>. V<sub>SOURCE</sub> is compared against both limits after each conversion cycle.

If V<sub>SOURCE</sub> meets or exceeds the corresponding high limit or drops below the low limit, the ALERT pin is asserted (by default, see **Section 4.7** "**ALERT Output**") and the VSRC\_HIGH or VSRC\_LOW status bits are set in the High Limit Status or Low Limit Status registers (see Register 6-20 and Register 6-22).

#### 5.0 SMBUS COMMUNICATION

#### 5.0.1 SMBus START BIT

The SMBus Start bit is defined as a transition of the SMBus Data line from a logic '1' state to a logic '0' state while the SMBus Clock line is in a logic '1' state.

#### 5.0.2 SMBus ADDRESS AND RD/WR BIT

The SMBus Address Byte consists of the 7-bit client address followed by a 1-bit RD/WR indicator. If this RD/WR bit is a logic '0', the SMBus host is writing data to the client device. If this RD/WR bit is a logic '1', the SMBus host is reading data from the client device.

The PAC1710/20 SMBus address is determined by a single resistor connected between ground and the ADDR\_SEL pin as shown in Table 5-1.

#### TABLE 5-1: ADDR\_SEL RESISTOR SETTING

| RES<br>(5%) | SMBus Address | RES<br>(5%) | SMBus Address |  |

|-------------|---------------|-------------|---------------|--|

| 0           | 1001_100(r/w) | 1600        | 0101_000(r/w) |  |

| 100         | 1001_101(r/w) | 2000        | 0101_001(r/w) |  |

| 180         | 1001_110(r/w) | 2700        | 0101_010(r/w) |  |

| 300         | 1001_111(r/w) | 3600        | 0101_011(r/w) |  |

| 430         | 1001_000(r/w) | 5600        | 0101_100(r/w) |  |

| 560         | 1001_001(r/w) | 9100        | 0101_101(r/w) |  |

| 750         | 1001_010(r/w) | 20000       | 0101_110(r/w) |  |

| 1270        | 1001_011(r/w) | Open        | 0011_000(r/w) |  |

All SMBus Data bytes are sent most significant bit first and composed of 8 bits of information.

#### 5.0.3 SMBus ACK AND NACK BITS

The SMBus client will acknowledge all data bytes that it receives (as well as the <u>client</u> address if it matches and the ARA address if the ALERT pin is asserted). This is done by the client device pulling the SMBus Data line low after the eigth bit of each byte that is transmitted.

The host will not acknowledge (NACK) the data received from the client by holding the SMBus data line high after the eigth data bit has been sent.

#### 5.0.4 SMBus STOP BIT

The SMBus Stop bit is defined as a transition of the SMBus Data line from a logic '0' state to a logic '1' state while the SMBus clock line is in a logic '1' state. When the PAC1710/20 detects an SMBus Stop bit, and it has been communicating with the SMBus protocol, it will reset its client interface and prepare to receive further communications.

#### 5.0.5 SMBus TIMEOUT

The PAC1710/20 includes an SMBus timeout feature. Following a 30 ms period of inactivity on the SMBus, the device will time out and reset the SMBus interface.

The time-out functionality defaults to disabled and can be enabled by writing to the TIMEOUT bit (see Register 6-1).

#### 5.1 SMBus and I<sup>2</sup>C Compliance

The major differences between SMBus and  $I^2C$  devices are highlighted below. For more information, refer to the SMBus 2.0 and  $I^2C$  specifications.

- PAC1710/20 supports I<sup>2</sup>C fast mode at 400 kHz. This covers the SMBus maximum time of 100 kHz.

- Minimum frequency for SMBus communications is 10 kHz.

- The SMBus client protocol will reset if the clock is held at a logic '0' for longer than 30 ms. This timeout functionality is disabled by default in the PAC1710/20 and can be enabled by writing to the TIMEOUT bit. I<sup>2</sup>C does not have a timeout.

- The SMBus client protocol will reset if both the clock and data lines are held at a logic '1' for longer than 200  $\mu$ s (idle condition). This function is disabled by default in the PAC1710/20 and can be enabled by setting the TIMEOUT bit. I<sup>2</sup>C does not have an idle condition.

- I<sup>2</sup>C devices do not support the Alert Response Address functionality (which is optional for SMBus).

- I<sup>2</sup>C devices support Block Read and Block Write differently. I<sup>2</sup>C protocol allows for unlimited number of bytes to be sent in either direction. The SMBus protocol requires that an additional data byte indicating number of bytes to read/write is transmitted. The PAC1710/20 supports I<sup>2</sup>C formatting only.

#### 5.2 SMBUS PROTOCOLS

The PAC1710/20 communicates with a host controller through the SMBus. The SMBus is a two-wire serial communication protocol between a computer host and its peripheral devices. A detailed timing diagram is shown in Figure 1-1. Stretching of the SMCLK signal is supported; however, the PAC1710/20 will not stretch the clock signal.

All of the below protocols use the convention in Table 5-2.

#### TABLE 5-2: PROTOCOL FORMAT

| Data Sent to Device | Data Sent to the Host |

|---------------------|-----------------------|

| # of bits sent      | # of bits sent        |

5.2.1 WRITE BYTE

The Write Byte is used to write one byte of data to the registers, as shown in Table 5-3.

#### TABLE 5-3: WRITE BYTE PROTOCOL

| START             | Slave Address | WR | ACK | Register Address | ACK | Register Data | ACK | STOP  |

|-------------------|---------------|----|-----|------------------|-----|---------------|-----|-------|

| $1 \rightarrow 0$ | YYYY_YYY      | 0  | 0   | XXh              | 0   | XXh           | 0   | 0 → 1 |

#### 5.2.2 READ BYTE

The Read Byte protocol is used to read one byte of data from the registers as shown in Table 5-4.

#### TABLE 5-4: READ BYTE PROTOCOL

| START             | Slave<br>Address | WR | АСК | Register<br>Address | ACK | START             | Slave<br>Address | RD | АСК | Register<br>Data | NACK | STOP              |

|-------------------|------------------|----|-----|---------------------|-----|-------------------|------------------|----|-----|------------------|------|-------------------|

| $1 \rightarrow 0$ | YYYY_YYY         | 0  | 0   | XXh                 | 0   | $1 \rightarrow 0$ | YYYY_YYY         | 1  | 0   | XXh              | 1    | $0 \rightarrow 1$ |

#### 5.2.3 SEND BYTE

The Send Byte protocol is used to set the internal address register pointer to the correct address location. No data is transferred during the Send Byte protocol as shown in Table 5-5.

#### TABLE 5-5: SEND BYTE PROTOCOL

| START             | Slave Address | WR | ACK | Register Address | ACK | STOP              |

|-------------------|---------------|----|-----|------------------|-----|-------------------|

| $1 \rightarrow 0$ | YYYY_YYY      | 0  | 0   | XXh              | 0   | $0 \rightarrow 1$ |

#### 5.2.4 RECEIVE BYTE

The Receive Byte protocol is used to read data from a register when the internal register address pointer is known to be at the right location (e.g. set via Send Byte). This is used for consecutive reads of the same register as shown in Table 5-6.

#### TABLE 5-6: RECEIVE BYTE PROTOCOL

| START | Slave Address | RD | ACK | Register Address | NACK | STOP  |

|-------|---------------|----|-----|------------------|------|-------|

| 1 → 0 | YYYY_YYY      | 1  | 0   | XXh              | 1    | 0 → 1 |

#### 5.2.5 ALERT RESPONSE ADDRESS

The ALERT output can be used as a processor interrupt or as an SMBus Alert when configured to operate as an interrupt.

When it detects that the  $\overline{\text{ALERT}}$  pin is asserted, the host will send the Alert Response Address (ARA) to the general address of 0001\_100xb. All devices with active interrupts will respond with their client address, as shown in Table 5-7.

#### TABLE 5-7:ALERT RESPONSE ADDRESS PROTOCOL

| START             | Alert Response Address | RD | ACK | Device Address | NACK | STOP              |

|-------------------|------------------------|----|-----|----------------|------|-------------------|

| $1 \rightarrow 0$ | 0001_100               | 1  | 0   | YYYY_YYY       | 1    | $0 \rightarrow 1$ |

The PAC1710/20 will respond to the ARA in the following way if the ALERT pin is asserted:

- Send Slave Address and verify that full slave address was sent (i.e. the SMBus communication from the device was not prematurely stopped due to a bus contention event).

- Set the MASK bit to clear the ALERT pin.

#### 5.3 I<sup>2</sup>C Protocols

The PAC1710/20 supports  $\mathsf{I}^2\mathsf{C}$  Block Read and Block Write.

The protocols listed below use the convention in Table 5-1.

#### 5.3.1 BLOCK WRITE

The Block Write is used to write multiple data bytes to a group of contiguous registers, as shown in Table 5-8.

#### TABLE 5-8: BLOCK WRITE PROTOCOL

| START             | Slave<br>Address | WR               | ACK | Register<br>Address | ACK              | Register Data | ACK               |

|-------------------|------------------|------------------|-----|---------------------|------------------|---------------|-------------------|

| $1 \rightarrow 0$ | YYYY_YYY         | 0                | 0   | XXh                 | 0                | XXh           | 0                 |

| Register<br>Data  | ACK              | Register<br>Data | ACK | Register<br>Address | Register<br>Data | ACK           | STOP              |

| XXh               | 0                | XXh              | 0   |                     | XXh              | 0             | $0 \rightarrow 1$ |

#### 5.3.2 BLOCK READ

The Block Read is used to read multiple data bytes from a group of contiguous registers, as shown in Table 5-9.

| START | Slave<br>Address | WR  | АСК              | Register<br>Address | АСК              | START             | Slave<br>Address | RD               | ACK  | Register<br>Data  |

|-------|------------------|-----|------------------|---------------------|------------------|-------------------|------------------|------------------|------|-------------------|

| 1→0   | YYYY_YYY         | 0   | 0                | XXh                 | 0                | $1 \rightarrow 0$ | YYYY_YYY         | 1                | 0    | XXh               |

| АСК   | Register<br>Data | ACK | Register<br>Data | ACK                 | Register<br>Data | ACK               |                  | Register<br>Data | NACK | STOP              |

| 0     | XXh              | 0   | XXh              | 0                   | XXh              | 0                 |                  | XXh              | 1    | $0 \rightarrow 1$ |

#### TABLE 5-9:BLOCK READ PROTOCOL

#### 6.0 REGISTERS IN HEXADECIMAL ORDER

The registers shown in Table 6-1 are accessible through the SMBus. In the individual register tables that follow, an entry of '—' indicates that the bit is not used and will always read '0'.

#### TABLE 6-1: REGISTER SET IN HEXADECIMAL ORDER

| Register<br>Address | Register<br>Name                                 | Bit7   | Bit6   | Bit5  | Bit4  | Bit3  | Bit2  | Bit1  | Bit0  | Default<br>Value |

|---------------------|--------------------------------------------------|--------|--------|-------|-------|-------|-------|-------|-------|------------------|

| 00h                 | Configuration                                    | _      | CDEN   | MSKAL | C2IDS | C2VDS | TOUT  | C1IDS | C1VDS | 00h              |

| 01h                 | Conversion Rate                                  |        | —      | —     | _     | —     | —     | CONV1 | CONV0 | 03h              |

| 02h                 | One-Shot                                         | OS7    | OS6    | OS5   | OS4   | OS3   | OS2   | OS1   | OS0   | 00h              |

| 03h                 | Channel Mask Register                            |        | _      | _     | _     | C2VS  | C2VSR | C1VS  | C1VSR | 00h              |

| 04h                 | High-Limit Status                                | CVDN   | _      | _     | —     | C2VSH | C2VRH | C1VSH | C1VRH | 00h              |

| 05h                 | Low-Limit Status                                 | —      | —      | —     | —     | C2VSL | C2VRL | C1VSL | C1VRL | 00h              |

| 0Ah                 | V <sub>SOURCE</sub> Sampling<br>Configuration    | C2RS1  | C2RS0  | C2RA1 | C2RA0 | C1RS1 | C1RS0 | C1RA1 | C1RA0 | 88h              |

| 0Bh                 | CH1 V <sub>SENSE</sub> Sampling<br>Configuration | —      | C1SS2  | C1SS1 | C1SS0 | C1SA1 | C1SA0 | C1SR1 | C1SR0 | 53h              |

| 0Ch                 | CH2 V <sub>SENSE</sub> Sampling<br>Configuration | _      | C2SS2  | C2SS1 | C2SS0 | C2SA1 | C2SA0 | C2SR1 | C2SR0 | 53h              |

| 0Dh                 | CH1 Sense Voltage<br>High Byte                   | C1SR11 | C1SR10 | C1SR9 | C1SR8 | C1SR7 | C1SR6 | C1SR5 | C1SR4 | 00h              |

| 0Eh                 | CH1 Sense Voltage<br>Low Byte                    | C1SR3  | C1SR2  | C1SR1 | C1SR0 | —     | —     | —     | —     | 00h              |

| 0Fh                 | CH2 Sense Voltage<br>High Byte                   | C2SR11 | C2SR10 | C2SR9 | C2SR8 | C2SR7 | C2SR6 | C2SR5 | C2SR4 | 00h              |

| 10h                 | CH2 Sense Voltage<br>Low Byte                    | C2SR3  | C2SR2  | C2SR1 | C2SR0 | —     | —     | —     | —     | 00h              |

| 11                  | CH1 V <sub>SOURCE</sub> Voltage<br>High Byte     | C1VR10 | C1VR9  | C1VR8 | C1VR7 | C1VR6 | C1VR5 | C1VR4 | C1VR3 | 00h              |

| 12                  | CH1 V <sub>SOURCE</sub> Voltage<br>Low Byte      | C1VR2  | C1VR1  | C1VR0 | -     | —     | —     | —     | _     | 00h              |

| 13h                 | CH2 V <sub>SOURCE</sub> Voltage<br>High Byte     | C2VR10 | C1VR9  | C2VR8 | C2VR7 | C2VR6 | C2VR5 | C2VR4 | C2VR3 | 00h              |

| 14h                 | CH2 V <sub>SOURCE</sub> Voltage<br>Low Byte      | C2VR2  | C2VR1  | C2VR0 | _     | —     | —     | _     |       | 00h              |

#### TABLE 6-1: REGISTER SET IN HEXADECIMAL ORDER (CONTINUED)

| Register<br>Address | Register<br>Name                              | Bit7  | Bit6  | Bit5  | Bit4  | Bit3  | Bit2  | Bit1  | Bit0  | Default<br>Value |

|---------------------|-----------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|------------------|

| 15h                 | CH1 Power Ratio<br>High Byte                  | C1P15 | C1P14 | C1P13 | C1P12 | C1P11 | C1P10 | C1P8  | C1P7  | 00h              |

| 16h                 | CH1 Power Ratio<br>Low Byte                   | C1P7  | C1P6  | C1P5  | C1P4  | C1P3  | C1P2  | C1P1  | C1P0  | 00h              |

| 17h                 | CH2 Power Ratio<br>High Byte                  | C2P15 | C2P14 | C2P13 | C2P12 | C2P11 | C2P10 | C2P8  | C2P7  | 00h              |

| 18h                 | CH2 Power Ratio<br>Low Byte                   | C2P7  | C2P6  | C2P5  | C2P4  | C2P3  | C2P2  | C2P1  | C2P0  | 00h              |

| 19h                 | CH1 Sense Voltage<br>High Limit               | C1SH7 | C1SH6 | C1SH5 | C1SH4 | C1SH3 | C1SH2 | C1SH1 | C1SH0 | 7Fh              |

| 1Ah                 | CH2 Sense Voltage<br>High Limit               | C2SH7 | C2SH6 | C2SH5 | C2SH4 | C2SH3 | C2SH2 | C2SH1 | C2SH0 | 7Fh              |

| 1Bh                 | CH1 Sense Voltage<br>Low Limit                | C1SL7 | C1SL6 | C1SL5 | C1SL4 | C1SL3 | C1SL2 | C1SL1 | C1SL0 | 80h              |

| 1Ch                 | CH2 Sense Voltage<br>Low Limit                | C2SL7 | C2SL6 | C2SL5 | C2SL4 | C2SL3 | C2SL2 | C2SL1 | C2SL0 | 80h              |

| 1Dh                 | CH1 V <sub>SOURCE</sub> Voltage<br>High Limit | C1VH7 | C1VH6 | C1VH5 | C1VH4 | C1VH3 | C1VH2 | C1VH1 | C1VH0 | FFh              |

| 1Eh                 | CH2 V <sub>SOURCE</sub> Voltage<br>High Limit | C2VH7 | C2VH6 | C2VH5 | C2VH4 | C2VH3 | C2VH2 | C2VH1 | C2VH0 | FFh              |

| 1Fh                 | CH1 V <sub>SOURCE</sub> Voltage<br>Low Limit  | C1VL7 | C1VL6 | C1VL5 | C1VL4 | C1VL3 | C1VL2 | C1VL1 | C1VL0 | 00h              |

| 20h                 | CH2 V <sub>SOURCE</sub> Voltage<br>Low Limit  | C2VL7 | C2VL6 | C2VL5 | C2VL4 | C2VL3 | C2VL2 | C2VL1 | C2VL0 | 00h              |

| FDh                 | Product ID                                    | PID7  | PID6  | PID5  | PID4  | PID3  | PID2  | PID1  | PID0  | 57h/58           |

| FEh                 | Manufacturer ID                               | MID7  | MID6  | MID5  | MID4  | MID3  | MID2  | MID1  | MID0  | 5Dh              |

| FFh                 | Revision                                      | REV7  | REV6  | REV5  | REV4  | REV3  | REV2  | REV1  | REV0  | 81h              |

#### 6.1 Read Multiple Data Bytes

When any measurement high-byte register is read ( $V_{SOURCE}$  or  $V_{SENSE}$ ), the corresponding low byte is copied into an internal "shadow" register. The user is free to read the low byte at any time and be guaranteed that it will correspond to the previously read high byte. Regardless if the low byte is read or not, reading from the same high byte register again will automatically refresh this stored low byte data.

#### 6.2 Detailed Register Description

#### REGISTER 6-1: CONFIGURATION REGISTER (ADDRESS 00H)

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| —     | CDEN  | MSKAL | C2IDS | C2VDS | TOUT  | C1IDS | C1VDS |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:       |                                          |                              |                                   |                                                  |

|---------------|------------------------------------------|------------------------------|-----------------------------------|--------------------------------------------------|

| R = Read bit  | W =                                      | Writable bit                 | U = Unimplemented bit,            | read as '0'                                      |

| -n = Value at |                                          | bit is set                   | '0' = Bit is cleared              | x = Bit in unknown                               |

|               |                                          |                              |                                   |                                                  |

| bit 7         | Unimplemented: F                         | Read as '0'                  |                                   |                                                  |

| bit 6         |                                          |                              | asserted when the conversion      |                                                  |

|               |                                          |                              | is when the conversion cycle is   |                                                  |

| L:1 F         |                                          | -                            |                                   | et, the ALERT pin will be asserted               |

| bit 5         |                                          |                              | asserting due to out-of-limit con | nditions.<br>Indition. The Status Registers will |

|               | be updated normall                       |                              |                                   | Inition. The olards registers will               |

|               |                                          |                              | e asserted for any interrupt cor  | ndition not masked by                            |

|               | •                                        | •                            | l be updated normally.            |                                                  |

| bit 4         | C2IDS: Disables the                      | e V <sub>SENSE</sub> measure | ement for channel 2 (PAC1720)     |                                                  |

|               | 1 = The device is no<br>a One-Shot comma |                              | ense voltage. It will update CH   | 2 Sense Voltage Registers when                   |

|               | 0 = The device is m                      |                              | oltage for CH2                    |                                                  |

|               | Unimplemented: F                         |                              |                                   |                                                  |

| bit 3         |                                          |                              | urement for channel 2 (PAC172     |                                                  |

|               |                                          | •                            | Source voltage. It will update Cl | H2 Source Voltage Registers                      |

|               | when a One-Shot c<br>0 = The device is m |                              | voltage for CH2                   |                                                  |

|               | Unimplemented: F                         |                              |                                   |                                                  |

| bit 2         | •                                        | •                            | eset functionality of the commu   | unications protocol (see                         |

|               | Section 5.0.5 "SMI                       |                              | 5                                 |                                                  |

|               | 1 = Time out enable                      |                              |                                   |                                                  |