# Crystal Clock Oscillator Module Evaluation Board User's Manual for NBX Family in 6 Pin CLCC 5 mm x 7 mm Package

Generic Evaluation Board: XOCLCC6EVB

**Devices: NBXxxxx**

ON Semiconductor®

http://onsemi.com

## **EVAL BOARD USER'S MANUAL**

## Description

This Evaluation Board user's manual is a guide for using the XOCLCC6EVB Evaluation Board to provide a convenient platform for quickly evaluating, characterizing and verify performance and operation of a device in the NBXxxxx family of Clock Oscillator Modules packaged in the 6 pin CLCC, 5mm by 7 mm, CASE 848AB (see Appendix).

This family of devices offer an internal crystal and PLL IC. This Evaluation Board Manual and Evaluation Board should be used in conjunction with a specific device data sheet, which contains full technical details on specifications and operation.

An NBXxxxx Clock Oscillator Module device may be directly solder mounted onto the available evaluation board footprint; or multiple units may be inserted and tested by solder mounting a separate insertion socket (P/N AM0393–320R from SER Electronics) onto the available footprint.

### **Evaluation Board Features**

- 6 pin CLCC solder footprint for solder mounting a device or test socket

- Incorporates jumper headers to conveniently and manually control the levels for the 'Output Enable' (Pin 1) and 'Frequency Select' (Pin 2) pins.

- Enable single or split-power supply operation.

LVPECL differential outputs are accessed via SMA connectors offering different output load configurations.

### **Evaluation Board Manual Document Features**

- Information on the XOCLCC6EVB Evaluation Board

- Appropriate Lab Setup and Procedures

- Board build Bill of Materials (Table 5)

- Evaluation Board schematic (Figure 7)

- Evaluation Board Lamination Stackup (Figure 8)

- Evaluation Board Fabrication Notes

- Appendix:

- Mechanical Case Outline

- Generic Marking Diagram

- Soldering Footprint

## What measurements can you expect to make?

With this evaluation board, the following measurements could be performed in single-ended or differential modes of operation.

- DC Characteristics

- Frequency Performance

- Output Rise and Fall Time

- Phase Noise

- Jitter

Front

Back

Figure 1. Evaluation Board Images (Front and Back)

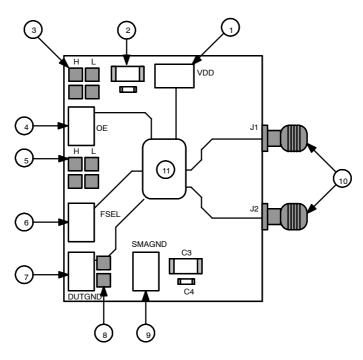

# **EVALUATION BOARD MAP**

Figure 2. Evaluation Board Layout

**Table 1. EVALUATION BOARD MAP DESCRIPTION**

| Number | Description                                                                                                                                                                                                |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1      | DUT PIN6 Positive supply connection anvil and test point.                                                                                                                                                  |  |  |

| 2      | Decoupling capacitors. See BOM/board schematic for details.                                                                                                                                                |  |  |

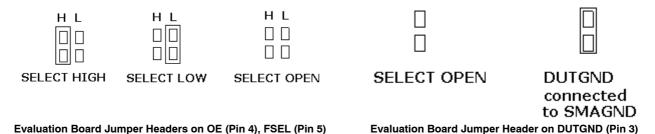

| 3      | DUT PIN 4 OE jumper header to force logic HIGH (Active) or LOW (Outputs Disabled to High Impedance). Leave open or use jumper to force HIGH (OE Pin defaults HIGH when left floating) (see Figure 3 below) |  |  |

| 4      | OE connection anvil and test point.                                                                                                                                                                        |  |  |

| 5      | DUT PIN 2 FSEL jumper header to force logic HIGH or LOW. FSEL Pin defaults HIGH when left floating. (see Figure 3 below)                                                                                   |  |  |

| 6      | FSEL connection anvil and test point.                                                                                                                                                                      |  |  |

| 7      | Device ground (DUTGND) connection anvil and test point.                                                                                                                                                    |  |  |

| 8      | DUT PIN 3 GND/SMAGND jumper header to force DUTGND connection to SMAGND. (see Figure 3 below)                                                                                                              |  |  |

| 9      | SMAGND connection anvil and test point.                                                                                                                                                                    |  |  |

| 10     | SMA outputs (CLK/CLK).                                                                                                                                                                                     |  |  |

| 11     | 6 pin CLCC 5mmX7mm DUT (Device under test).                                                                                                                                                                |  |  |

Figure 3. Select Positions for Evaluation Board Jumper Headers on OE (Pin 4), FSEL (Pin 5), and DUTGND (Pin 3)

## TIME DOMAIN MEASUREMENTS

#### **Equipment**

Table 2 indicates the recommended equipment for making characterization and performance measurements.

**Table 2. BASIC EQUIPMENT**

| Description                                         | Example Equipment          | Qty |

|-----------------------------------------------------|----------------------------|-----|

| Power Supply with 4 outputs                         | HP6624A or similar         | 1   |

| Real-Time Oscilloscope                              | DPO70804 or similar        | 1   |

| Matched High Speed<br>Cables with SMA<br>Connectors | Storm, Semflex, or similar | 2   |

| Power supply cables                                 |                            | 4   |

## Setup

The following steps should be followed for proper equipment setup.

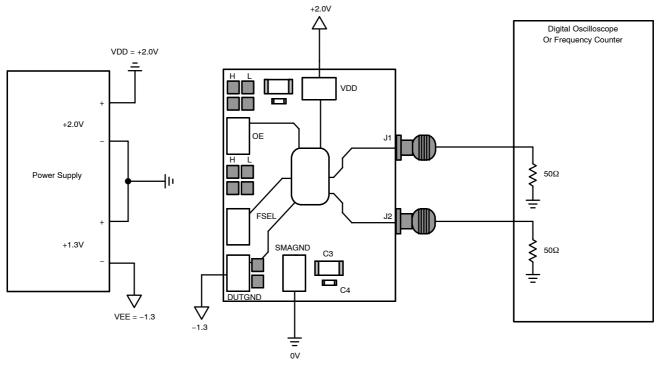

### Step 1: Connect Power (split power supply mode)

Three power levels must be provided to the board:  $V_{DD}$ , DUTGND, and SMAGND via the test point anvils at the edges of the board. Bypass capacitors are installed from  $V_{DD}$  to SMAGND and DUTGND to SMAGND near the test points (see BOM). Devices may be tested in one of three supply modes (see Table 3):

## A). Single (Positive) +3.3 V Setup

No offset to supplies or output levels

## B). Split 3.3 V Setup

Offsets the  $V_{DD}$ , DUTGND, and output voltage levels by -1.3~V and avoids an additional, separate  $V_{TT}$  supply and allows a direct connection to test equipment such as an oscilloscope or counter with  $50~\Omega$  impedance to GND inputs. SMAGND =  $V_{TT} = V_{DD} - 2.0~V = 0.0~V$ .

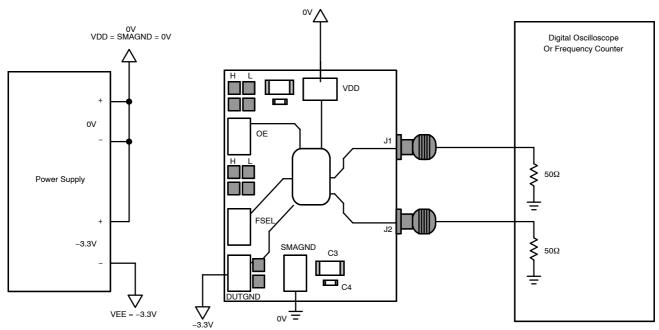

## C). Single (Negative) -3.3 V Setup

Offsets the  $V_{DD}$ , DUTGND, and output voltage levels by  $-3.3~\mathrm{V}$

# Table 3. XOCLCC6EVB POWER SUPPLY CONNECTION VOLTAGES

| A). Single<br>Positive<br>+3.3 V Setup                  | B). Split 3.3 V<br>Setup                            | C). Single<br>Negative<br>-3.3 V Setup                       |

|---------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------|

| V <sub>DD</sub> = 3.3 V                                 | V <sub>DD</sub> = 2.0 V                             | V <sub>DD</sub> = 0 V                                        |

| V <sub>TT</sub><br>= V <sub>DD</sub> - 2.0 V<br>= 1.3 V | $V_{TT}$<br>= $V_{DD}$ – 2.0 V<br>= SMAGND<br>= 0 V | $V_{TT}$ = $V_{DD}$ - 2.0 V = -2.0 V SMAGND = $V_{DD}$ = 0 V |

| DUTGND<br>= SMAGND<br>= 0 V                             | DUTGND<br>= -1.3 V                                  | DUTGND = -3.3 V                                              |

NOTE: SMAGND is the SMA cable shield reference for the inputs and outputs only, not to be confused with the device ground pin (DUTGND).

## **Step 2: Connect Output Signals**

Table 4 gives a list of specific **LOGIC Levels** and their appropriate **Power Supply** and **Typical Lab Setup** conditions

**LVPECL**: The LVPECL outputs have standard, open emitter outputs and must be externally DC loaded and AC terminated. A split power supply technique takes advantage of terminating the LVPECL outputs into 50  $\Omega$  of an oscilloscope or a frequency counter. Since  $V_{TT} = V_{DD} - 2 V$ , offsetting  $V_{DD}$  to +2.0 V yields  $V_{TT} = 0$  V or Ground (SMAGND). The  $V_{TT}$  terminal connects to the isolated SMAGND connector ground plane, and is not to be confused with the device ground pin (DUTGND). (See Application Note AN8020/D for details on ECL termination).

**CML**: For CML lab setup and test, operation with negative supply voltage is recommended to enable the  $50 \Omega$  internal impedance in the oscilloscope to be used as a termination of the CML signals ( $V_{DD} = 0.0 \text{ V}$ , SMAGND = 0.0 V, and DUTGND = -3.3 V (See Application Note AN8173/D for details on CML termination).

**LVDS**: Driver termination is a 100  $\Omega$  resistor across the differential lines located at the receiver input.

**Table 4. TYPICAL LAB SETUP**

| LOGIC Levels | Power Supply  | Typical Lab<br>Setup |

|--------------|---------------|----------------------|

| LVPECL       | Split 3.3 V   | See Figure 4         |

| CML          | Single –3.3 V | See Figure 5         |

| LVDS         | Single 3.3 V  | See Figure 6         |

## Step 3: Configure FSEL and OE

The FSEL and OE control pins can be controlled from an external source via the appropriate test point, or via the jumper headers located on the evaluation board, as indicated in Figures 2 and 7. Refer to the specific device datasheet for details on the proper settings for these pins.

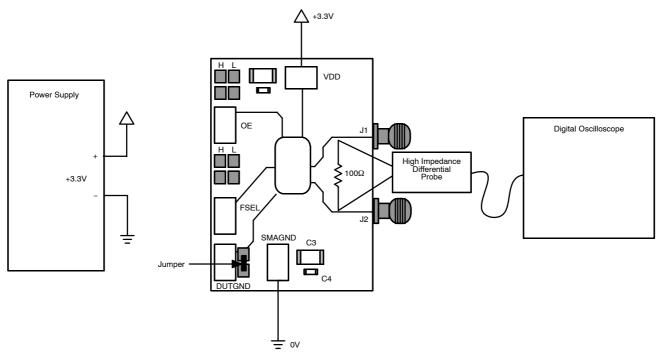

Figure 4. Split Power Supply Lab Setup for LVPECL Outputs (DO NOT JUMPER DUTGND and SMAGND)

Note: For CML outputs, 50  $\Omega$  to  $V_{DD}$  is needed for proper termination. See application note AND8173/D.

Figure 5. Typical Lab Setup for CML Outputs (DO NOT JUMPER DUTGND and SMAGND)

Figure 6. Typical Lab Setup for LVDS Outputs (JUMPER DUTGND and SMAGND)

Table 5. XOCLCC6EVB EVALUATION BOARD BILL OF MATERIALS

| Components            | Manufacturer    | Description               | Part Number                | Qty |

|-----------------------|-----------------|---------------------------|----------------------------|-----|

| Jumper Header         | Berg            | 100 mil                   | In House                   | 5   |

| Test Point            | Keystone        | Anvil SMD                 | 5016                       | 3   |

| Shunt                 |                 |                           |                            |     |

| Connector             | Johanson        | SMA, Edge Mount           | 142-0711-821               | 2   |

| Capacitor             | Kemet           | 22 μF, 10%                | T491D22K016AS, Case C or D | 2   |

| Capacitor             | Kemet           | 0.1 μF, 10%               | C0603C104K4RAC             | 2   |

| Socket (Not Supplied) | SER Electronics | Socket – 6-Lead 5mm x 7mm | AM0393-320R                | 1   |

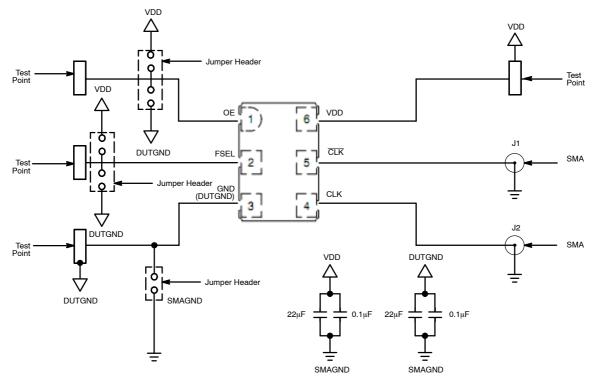

Figure 7. XOCLCC6EVB Evaluation Board Schematic

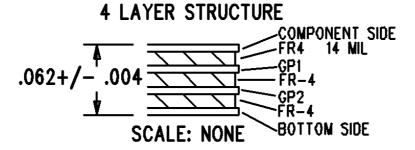

Figure 8. XOCLCC6EVB Evaluation Board Layer Lamination Stackup

## **Evaluation Board Fabrication Notes**

- 1. Material: FR-4

- 2. Finished copper to be loz. (0.0014) external layers

- 3. Minimum copper plating 0.0007" thick for plated thru holes annular ring to be 0.0002" minimum

- 4. LPI soldermask green

- 5. Soldermask registration  $\pm 0.002$ " N/A

- 6. All exposed copper areas to be gold plated (0.000030" gold over 0.000100" nickel)

- 7. If specified, silkscreen is to be white epoxy ink.

- 8. Hole diameter tolerance is  $\pm 0.002$ ", maximum layer to layer misregistration shall be 0.004", measurement method must comply with MIL-P-55110D, Figure 1.

- 9. Finished conductor width shall not vary more than  $\pm\,0.001$ " from artwork master 50  $\Omega$  traces are 0.024" wide.

- 10. Warp and twist of single sided boards shall not exceed 0.002"per inch, warp and twist of multi-layer boards shall not exceed 0.010" per inch.

- 11. All dimensions are in inches unless otherwise specified tolerances. XX  $\pm 0.010^{\circ}$  XXX  $\pm 0.004^{\circ}$ .

- 12. Acceptability requirements per IPC-A-600E.

- 13. Drawing is viewed from component or primary side.

- 14. This is a 4 layer board.

- 15. All holes are plated thru unless otherwise specified.

- 16. Drill size units are thousandths of an inch.

- 17. Trim all silkscreen which flows over via holes or SMD pads.

- 18. Break all sharp edges, PCB edges should be smooth and even.

## Appendix:

Mechanical Case Outline Generic Marking Diagram Soldering Footprint

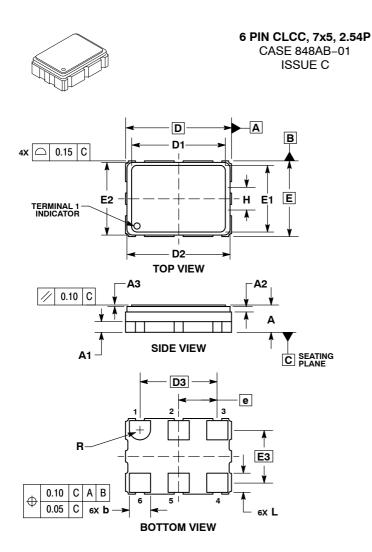

## PACKAGE DIMENSIONS

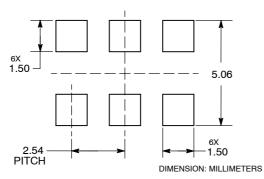

## **SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### NOTES:

- DIMENSIONING AND TOLERANCING PER

ASME V14 5M 1994

- ASME Y14.5M, 1994. 2. CONTROLLING DIMENSION: MILLIMETERS.

|     | MILLIMETERS |          |      |  |

|-----|-------------|----------|------|--|

| DIM | MIN         | NOM      | MAX  |  |

| Α   | 1.70        | 1.80     | 1.90 |  |

| A1  |             | 0.70 REF |      |  |

| A2  |             | 0.36 REF |      |  |

| АЗ  | 0.08        | 0.10     | 0.12 |  |

| b   | 1.30        | 1.40     | 1.50 |  |

| D   | 7.00 BSC    |          |      |  |

| D1  | 6.17        | 6.20     | 6.23 |  |

| D2  | 6.66        | 6.81     | 6.96 |  |

| D3  | 5.08 BSC    |          |      |  |

| E   | 5.00 BSC    |          |      |  |

| E1  | 4.37        | 4.40     | 4.43 |  |

| E2  | 4.65        | 4.80     | 4.95 |  |

| E3  | 3.49 BSC    |          |      |  |

| е   | 2.54 BSC    |          |      |  |

| Н   | 1.80 REF    |          |      |  |

| L   | 1.17        | 1.27     | 1.37 |  |

| R   | 0.70 REF    |          |      |  |

# GENERIC MARKING DIAGRAM\*

XXXXX = Specific Device Code A = Assembly Location

WL = Wafer Lot

YY = Year

WW = Work Week

G = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking

Pb–Free indicator, "G" or microdot " ■", may or may not be present.

ON Semiconductor and un are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice on semiconductor and are registered readerlands of semiconductor Components industries, Ite (SCILLC) solicit esserves the right to make changes without further holice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

## **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative