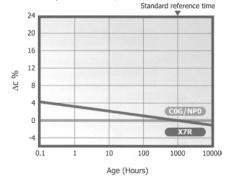

Dielectric

X7R or C0G/NP0

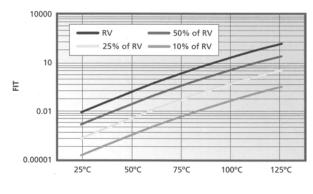

At 1000hr point

Multiple capacitance

Electrical configuration

Capacitance measurement

# Surface Mount EMI Filters X2Y

#### X2Y Integrated Passive Components

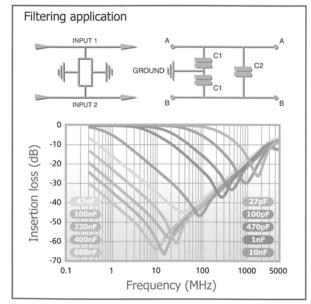

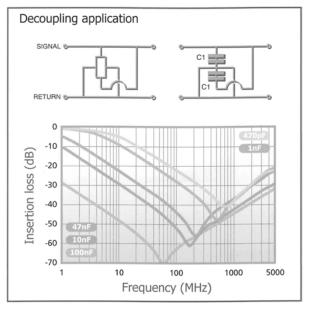

The Syfer X2Y Integrated Passive Component is a 3 terminal EMI chip device.

When used in balanced line applications, the revolutionary design provides simultaneous line-to-line and line-to-ground filtering, using a single ceramic chip. In this way, differential and common mode filtering are provided in one device.

For unbalanced applications, it provides ultra low ESL (equivalent series inductance). Capable of replacing 2 or more conventional devices, it is ideal for balanced and unbalanced lines, twisted pairs and dc motors, in automotive, audio, sensor and other applications.

Available in sizes from 0805 to 1812, these filters can prove invaluable in meeting stringent EMC demands.

| EI                                 | l Details |                                                                    |

|------------------------------------|-----------|--------------------------------------------------------------------|

| Capacitance Range                  |           | 1pF to 100nF                                                       |

| Temperature Coefficient of         | C0G/NP0   | 0 ± 30ppm/°C                                                       |

| Capacitance (TCC)                  | X7R       | ±15% from -55°C to +125°C                                          |

|                                    | C0G/NP0   | Cr > 50pF ≤0.0015                                                  |

| Dissipation Factor                 | CUG/INPU  | $Cr \le 50pF = 0.0015(15 \div Cr + 0.7)$                           |

|                                    | X7R       | ≤ 0.025                                                            |

| Insulation Resistance (IR)         |           | 100G $\Omega$ or 1000secs (whichever is the less)                  |

| Dielectric Withstand Voltage (DWV) |           | Voltage applied for 5 ±1 seconds, 50mA<br>charging current maximum |

| Ageing Rate                        | C0 G/ NP0 | Zero                                                               |

|                                    | X7R       | <2% per time decade                                                |

Typical capacitance matching Better than 5% (down to 1% available on request) Temperature rating -55°C to 125°C Insulation resistance 100Gohms or 1000s (whichever is the less) Dielectric withstand voltage ≤200V 2.5 times rated Volts for 5 secs 500V 1.5 times rated Volts for 5 secs Charging current limited to 50mA Max.

| Ту               | pe         | E03           |               |               |               |

|------------------|------------|---------------|---------------|---------------|---------------|

| Chip             | Chip Size  |               | 1206          | 1410          | 1812          |

| Rated<br>Voltage | Dielectric | Minimu        | ım and maximu | m capacitance | values        |

| 10)/11           | COG/NP0    | -             | -             | -             | -             |

| 16Vdc            | X7R        | -             | -             | -             | -             |

| 25Vdc            | C0G/NP0    | 560pF - 820pF | 1.8nF - 3.3nF | 6.8nF - 8.2nF | 12nF - 15nF   |

| 25 Vuc           | X7R        | 56nF - 68nF   | -             | 470nF         | 820nF         |

| 50Vdc            | C0G/NP0    | 390pF - 470pF | 1.2nF - 1.5nF | 4.7nF - 5.6nF | 8.2nF - 10nF  |

| 50 Vuc           | X7R        | 18nF - 47nF   | 56nF - 220nF  | 180nF - 400nF | 390nF - 680nF |

| 100Vdc           | C0G/NP0    | 10pF - 330pF  | 22pF - 1.0nF  | 100pF - 3.9nF | 820pF - 6.8nF |

| 100 vac          | X7R        | 470pF - 15nF  | 1.5nF - 47nF  | 4.7nF - 150nF | 8.2nF - 330nF |

| 200Vdc           | C0G/NP0    | -             | 22pF - 1.0nF  | 100pF - 3.3nF | 820pF - 5.6nF |

| 200 Vuc          | X7R        | -             | 820pF - 33nF  | 1.2nF - 120nF | 2.7nF - 180nF |

| 500)/do          | C0G/NP0    | -             | -             | -             | 820pF - 3.9nF |

| 500Vdc           | X7R        | -             | -             | -             | 2.7nF - 100nF |

Notes: 1)

1) For some lower capacitance parts, higher voltage rated parts may be supplied.

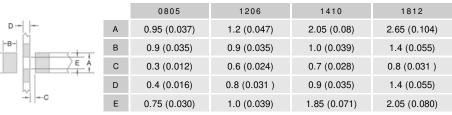

|         |    | 0805                         | 1206                      | 1410                      | 1812                               |

|---------|----|------------------------------|---------------------------|---------------------------|------------------------------------|

|         | L  | 2.0±0.3<br>(0.08±0.012)      | 3.2±0.3<br>(0.126±0.012)  | 3.6±0.3<br>(0.14±0.012)   | 4.5±0.35<br>(0.18±0.014)           |

|         | W  | 1.25±0.2<br>(0.05±0.008)     | 1.6±0.2<br>(0.063±0.008)  | 2.5±0.3<br>(0.1±0.012)    | 3.2±0.3<br>(0.126±0.012)           |

| # B2 B1 | Т  | $1.0\pm0.15$<br>(0.04±0.006) | 1.1±0.2<br>(0.043±0.008)  | 2.0 max.<br>(0.08 max.)   | 0.5±0.25<br>(0.02±0.01)            |

|         | B1 | 0.5±0.25<br>(0.02±0.01)      | 0.95±0.3<br>(0.037±0.012) | 1.20±0.3<br>(0.047±0.012) | $1.4 \pm 0.35$<br>(0.06 \pm 0.014) |

|         | B2 | 0.3±0.15<br>(0.012±0.006)    | 0.5±0.25<br>(0.02±0.01)   | 0.5±0.25<br>(0.02±0.01)   | 0.75±0.25<br>(0.03±0.01)           |

Notes: 1) All dimensions mm (inches).

2) Pad widths less than chip width gives improved mechanical performance.

- The solder stencil should place 4 discrete solder pads. The un-printed distance between ground pads is shown as dimension E.

- 4) Insulating the earth track underneath the filters is acceptable and can help avoid displacement of filter during soldering but can result in residue entrapment under the chip.

# AEC-Q200 range (E03) capacitance values

| Chip Size |         | 0805          | 1206          | 1410          | 1812          |

|-----------|---------|---------------|---------------|---------------|---------------|

| E O V d o | C0G/NP0 | 390pF - 470pF | 1.2nF - 1.5nF | 4.7nF - 5.6nF | 8.2nF - 10nF  |

| 50Vdc     | X7R     | 18nF - 33nF   | 56nF - 150nF  | 180nF - 330nF | 390nF- 560nF  |

| 100Vdc    | C0G/NP0 | 10pF - 330pF  | 22pF - 1.0nF  | 100pF - 3.9nF | 820pF - 6.8nF |

|           | X7R     | 470pF - 15nF  | 1.5nF - 47nF  | 4.7nF - 150nF | 8.2nF - 330nF |

| Component                                 | Advantages                                                                                                                                                                                                                                  | Disadvantages                                                              | Applications                                                                                                        |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Chip capacitor                            | Industry standard                                                                                                                                                                                                                           | Requires 1 per line<br>High inductance<br>Capacitance matching<br>problems | By-pass<br>Low frequency                                                                                            |

| 3 terminal feedthrough                    | Feedthrough<br>Lower inductance                                                                                                                                                                                                             | Current limited                                                            | Feedthrough<br>Unbalanced lines<br>High frequency                                                                   |

| Syfer X2Y Integrated<br>Passive Component | Very low inductance<br>Replaces 2 (or 3) components<br>Negates the effects of<br>temperature, voltage and<br>ageing<br>Provides both common mode<br>and differential mode<br>attenuation<br>Can be used on balanced and<br>unbalanced lines | Care must be taken to<br>optimise circuit design                           | By-pass<br>Balanced lines<br>High frequency<br>dc electric motors<br>Unbalanced lines<br>Audio amplifiers<br>CANBUS |

# Ordering information

| 1812                         | Y                                                                                                                                                             | 100                                                                           | 0334                                                                                                                                                                                         | Μ                                                                     | Х                                                                        | Т                                                                                     | E03                                             |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------|

| Chip Size                    | Termination                                                                                                                                                   | Rated Voltage                                                                 | Capacitance in Pico<br>farads (pF)                                                                                                                                                           | Capacitance<br>Tolerance                                              | Dielectric<br>Codes                                                      | Packaging                                                                             | Туре                                            |

| 0805<br>1206<br>1410<br>1812 | J = Nickel Barrier (Tin)<br>*Y = FlexiCap™ (Tin -<br>X7R only)<br>A = (Tin/Lead) Not<br>RoHS compliant.<br>*H = FlexiCap™<br>(Tin/Lead) Not RoHS<br>compliant | 016 = 16V<br>025 = 25V<br>050 = 50V<br>100 = 100V<br>200 = 200V<br>500 = 500V | First digit is 0. Second and<br>third digits are significant<br>figures of capacitance code.<br>The fourth digit is number of<br>zeros following<br>Example: 0334 = 330nF.<br>Note: C1 = 2C2 | <pre>M = ±20% (Tighter tolerances may be available on request).</pre> | A = C0G/NP0<br>AEC-Q200<br>C = C0G/NP0<br>E = X7R<br>AEC-Q200<br>X = X7R | T = 178mm<br>(7") reel<br>R = 330mm<br>(13") reel<br>B = Bulk pack<br>- tubs or trays | Syfer X2Y<br>Integrated<br>Passive<br>Component |

Note: \* FlexiCap™ termination only available in X7R material. Please contact the sales office for any special requirements.

### Soldering Information

Syfer MLCCs are compatible with all recognised soldering/mounting methods for chip capacitors. A detailed application note is available at <u>syfer.com</u>

#### Reflow Soldering

Syfer recommend reflow soldering as the preferred method for mounting MLCCs. Syfer MLCCs can be reflow soldered using a reflow profile generally defined in IPC/FEDEC J-STD-020. Sn plated termination chip capacitors are compatible with both conventional and lead free soldering with peak temperatures of 260 to 270°C acceptable.

The heating ramp rate should be such that components see a temperature rise of 1.5 to  $4^{\circ}$ C per second to maintain temperature uniformity through the MLCC.

The time for which the solder is molten should be maintained at a minimum, so as to prevent solder leaching. Extended times above 230 °C can cause problems with oxidation of Sn plating. Use of an inert atmosphere can help if this problem is encountered. Palladium/Silver (Pd/Ag) terminations can be particularly susceptible to leaching with free lead, tin rich solders and trials are recommended for this combination.

Cooling to ambient temperature should be allowed to occur naturally, particularly if larger chip sizes are being soldered. Natural cooling allows a gradual relaxation of thermal mismatch stresses in the solder joints. Forced cooling should be avoided as this can induce thermal breakage.

#### Wave Soldering

Wave soldering is generally acceptable, but the thermal stresses caused by the wave have been shown to lead to potential problems with larger or thicker chips. Particular care should be taken when soldering SM chips larger than size 1210 and with a thickness greater than 1.0mm for this reason.

Maximum permissible wave temperature is 270°C for SM chips.

The total immersion time in solder should be kept to a minimum. It is strongly recommended that Sn/Ni plated terminations are specified for wave soldering applications.

#### Solder Leaching

Leaching is the term for the dissolution of silver into the solder causing a failure of the termination system which causes increased ESR, tan  $\delta$  and open circuit faults, including ultimately the possibility of the chip becoming detached.

Leaching occurs more readily with higher temperature solders and solders with a high tin content. Pb free solders can be very prone to leaching certain termination systems. To prevent leaching, exercise care when choosing solder allows and minimize both maximum temperature and dwell time with the molten solder.

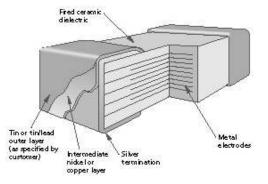

Plated terminations with nickel or copper anti-leaching barrier layers are available in a range of top coat finishes to prevent leaching occurring. These finishes also include Syfer FlexiCap<sup>™</sup> for improved stress resistance post soldering.

Multilayer ceramic chip with nickel or copper barrier termination

#### **Rework of Chip Capacitors**

Syfer recommend hot air/gas as the preferred method of applying heat for rework. Apply even heat surrounding the component to minimise internal thermal gradients. Soldering irons or other techniques that apply direct heat to the chip or surrounding area should not be used as these can result in micro cracks being generated.

Minimise the rework heat duration and allow components to cool naturally after soldering.

Use of Silver Loaded Epoxy Adhesives

Chip capacitors can be mounted to circuit boards using silver loaded adhesive provided the termination material of the capacitor is selected to be compatible with the adhesive. This is normally PdAg. Standard tin finishes are often not recommended for use with silver loaded epoxies as there can be electrical and mechanical issues with the joint integrity due to material mismatch.

#### Handling & Storage

Components should never be handled with fingers; perspiration and skin oils can inhibit solderability and will aggravate cleaning.

Chip capacitors should never be handled with metallic instruments. Metal tweezers should never be used as these can chip the product and leave abraded metal tracks on the product surface. Plastic or plastic coated metal types are readily available and recommended – these should be used with an absolute minimum of applied pressure.

Incorrect storage can lead to problems for the user. Rapid tarnishing of the terminations, with an associated degradation of solderability, will occur if the product comes into contact with industrial gases such as sulphur dioxide and chlorine. Storage in free air, particularly moist or polluted air, can result in termination oxidation.

Packaging should not be opened until the MLCs are required for use. If opened, the pack should be re-sealed as soon as practicable. Alternatively, the contents could be kept in a sealed container with an environmental control agent.

Long term storage conditions, ideally, should be temperature controlled between -5 and +40 $^{\circ}$ C and humidity controlled between 40% and 60% R.H.

Taped product should be stored out of direct sunlight, which might promote deterioration in tape or adhesive performance.

Product, stored under the conditions recommended above, in its "as received" packaging, has a minimum shelf life of 2 years.

#### SM Pad Design

Syfer conventional 2-terminal chip capacitors can generally be mounted using pad designs in accordance with IPC-7351, Generic Requirements for Surface Mount Design and Land Pattern Standards, but there are some other factors that have been shown to reduce mechanical stress, such as reducing the pad width to less than the chip width. In addition, the position of the chip on the board should also be considered.

3-terminal components are not specifically covered by IPC-7351, but recommended pad dimensions are included in the Syfer catalogue/website for these components.

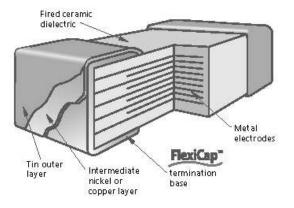

# FlexiCap<sup>™</sup> Termination

FlexiCap<sup>™</sup> has been developed as a result of listening to customer's experiences of stress damage to MLCCs from many manufacturers, often caused by variations in production processes.

Our answer is a proprietary flexible epoxy polymer termination material that is applied to the device under the usual nickel barrier finish. FlexiCap<sup>™</sup> will accommodate a greater degree of board bending than conventional capacitors.

Ranges are available with FlexiCap<sup>™</sup> termination material offering increased reliability and superior mechanical performance (board flex and temperature cycling) when compared with standard termination materials. Refer to Syfer application note reference AN0001. FlexiCap<sup>™</sup> capacitors enable the board to be bent almost twice as much as before mechanical cracking occurs. Refer to application note AN0002.

FlexiCap<sup>™</sup> is also suitable for space applications having passed thermal vacuum outgassing tests. Refer to Syfer application note reference AN0026.

FlexiCap<sup>®</sup> MLCC cross section

Syfer has delivered millions of FlexiCap<sup>™</sup> components and during that time has collected substantial test and reliability data, working in partnership with customers world wide, to eliminate mechanical cracking.

An additional benefit of FlexiCap<sup>™</sup> is that MLCCs can withstand temperature cycling from -55 to 125°C in excess of 1,000 times without cracking.

FlexiCap<sup>™</sup> termination has no adverse effect on any electrical parameters, nor affects the operation of the MLCC in any way.

# **Application Notes**

FlexiCap<sup>™</sup> may be handled, stored and transported in the same manner as standard terminated capacitors. The requirements for mounting and soldering FlexiCap<sup>™</sup> are the same as for standard SMD capacitors.

For customers currently using standard terminated capacitors there should be requirement to change the assembly process when converting to  $FlexiCap^{TM}$ .

Based upon the board bend tests in accordance with IEC 60384-1 the amount of board bending required to mechanically crack a FlexiCap<sup>™</sup> terminated capacitor is significantly increased compared with standard terminated capacitors.

| Product: X7R            | Typical bend performance under<br>AEC-Q200 test conditions |

|-------------------------|------------------------------------------------------------|

| Standard<br>Termination | 2mm to 3mm                                                 |

| FlexiCap™               | Typically 8mm to 10mm                                      |

REACH (Registration, Evaluation, Authorisation and restriction of Chemicals) Statement

The main purpose of REACH is to improve the protection of human health and the environment from the risks arising from the use of chemicals.

Syfer Technology Ltd maintains both ISO 14001, Environmental Management System and OHSAS 18001 Health & Safety Management System approvals that require and ensure compliance with corresponding legislation such as REACH.

For further information, please contact the sales office at <u>SyferSales@knowles.com</u>

#### RoHS Compliance

Syfer routinely monitors world wide material restrictions (e.g., EU/China and Korea RoHS mandates) and is actively involved in shaping future legislation.

All standard COG/NPO, X7R, X5R and High Q Syfer MLCC products are compliant with the EU RoHS directive (see below for special exemptions) and those with plated terminations are suitable for soldering common lead free solder alloys (refer to 'Soldering Information' for more details on soldering limitations). Compliance with EU RoHS directive automatically signifies compliance with some other legislation (e.g., Korea RoHS). Please refer to the Sales Office for details of compliance with other materials legislation.

Breakdown of material content, SGS analysis reports and tin whisker test results are available on request.

Most Syfer MLCC components are available with non-RoHS compliant tin/lead (SnPb) Solderable termination finish for exempt applications and where pure tin is not acceptable. Other tin free termination finishes may also be available – please refer to the Sales Office for further details.

X8R ranges < 250Vdc are not RoHS 2011/65/EU compliant.

Check the website, <u>www.knowlescapacitors.com/syfer</u> for latest RoHS update.

# Export Controls and Dual-use Regulations

Certain Syfer catalogue components are defined as 'dual-use' items under international export controls – those that can be used for civil and military purposes which meet certain specified technical standards.

The defining criteria for a dual-use component with respect to Syfer products is one with a voltage rating of >750V and a capacitance value > 250nF and a series inductance < 10nH.

Components defined as 'dual-use' under the above criteria automatically require a licence for export outside the EU, and may require a licence for export with the EU.

The application for a licence is routine, but customers for these products will be asked to supply further information.

Please refer to the sales office if you require any further information on export restrictions.

Other special components may additionally need to comply with export regulations.

### Ageing of Ceramic Capacitors

Capacitor ageing is a term used to describe the negative, logarithmic capacitance change which takes place in ceramic capacitors with time. The crystalline structure for barium titanate based ceramics changes on passing through its Curie temperature (known as the Curie Point) at about 125°C. The domain structure relaxes with time and in doing so, the dielectric constant reduces logarithmically; this is known as the ageing mechanism of the dielectric constant. The more stable dielectrics have the lowest ageing rates.

The ageing process is reversible and repeatable. Whenever the capacitor is heated to a temperature above the Curie Point the ageing process starts again from zero.

The ageing constant, or ageing rate, is defined as the percentage loss of capacitance due to the ageing process of the dielectric which occurs during a decade of time (a tenfold increase in age) and is expressed as percent per logarithmic decade of hours. As the law of decrease of capacitance is logarithmic, this means that for a capacitor with an ageing rate of 1% per decade of time, the capacitance will decrease at a rate of:

- a) 1% between 1 and 10 hours

- b) An additional 1% between the following 10 and 100 hours

- c) An additional 1% between the following 100 and 1000 hours

- An additional 1% between the following 1000 and 10000 hours

- e) The ageing rate continues in this manner throughout the capacitor's life.

Typical values of the ageing constant for our MLCCs are

| Dielectric Class      | Typical Values                             |

|-----------------------|--------------------------------------------|

| Ultra Stable C0G/ NP0 | Negligible capacitance loss through ageing |

| Stable X7R            | <2% per decade of time                     |

# Capacitance Measurements

Because of ageing it is necessary to specify an age for reference measurements at which the capacitance shall be within the prescribed tolerance. This is fixed at 1000 hours, since for all practical purposes there is not much further loss of capacitance after this time.

All capacitors shipped are within their specified tolerance at the standard reference age of 1000 hours after having cooled through their Curie temperature.

The ageing curve for any ceramic dielectric is a straight line when plotted on semi-log paper.

# Capacitance vs. Time

(Ageing X7R @ 1% per decade)

#### **Tight Tolerance**

One of the advantages of Syfer's unique 'wet process' of manufacture is the ability to offer capacitors with exceptionally tight capacitance tolerances.

The accuracy of the printing screens used in the fully automated, computer controlled manufacturing process allows for tolerance as close as  $\pm$  1% on C0G/NP0 parts greater than or equal to 10pF. For capacitance value less than 4.7pF tolerances can be as tight as  $\pm$  0.05pF.

Periodic Tests Conducted and Reliability Data

For standard surface mount capacitors components are randomly selected on a sample basis and the following routine tests conducted:

- Load Test. 1,000 hours @ 125°C (150°C for X8R). Applied voltage depends on components tested

- Humidity Test. 168 hours @ 85°C/85%RH

- Board Deflection (bend test)

Test results are available on request.

Conversion Factors

| From | То           | Operation                       |

|------|--------------|---------------------------------|

| FITs | MTBF (hours) | 10 <sup>9</sup> ÷ FITs          |

| FITs | MTBF (years) | 10 <sup>9</sup> ÷ (FITs × 8760) |

FIT = Failures In Time. 1 FIT = 1 failure in 10<sup>9</sup> hoursMTBF = Mean Time Between Failure

# Example of FIT Data Available

Component type: Testing Location: Results based on: 0805 (C0G/NP0 and X7R) Syfer reliability test department 16,622,000 component test hours

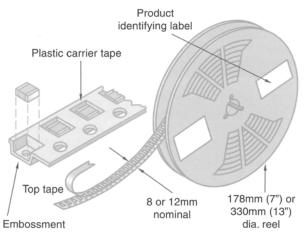

# Packaging Information

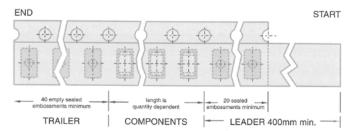

Tape and reel packing of surface mounting chip capacitors for automatic placement are in accordance with IEC60286-3.

# Peel Force

The peel force of the top sealing tape is between 0.2 and 1.0 Newton at  $180^{\circ}$ . The breaking force of the carrier and sealing tape in the direction of unreeling is greater than 10 Newton.

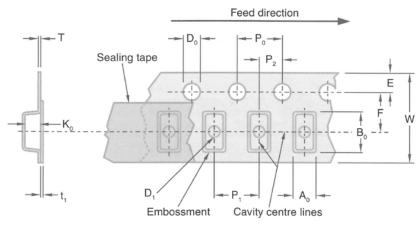

# Tape Dimensions

|                                                    |                                                              | Dimensions                   | mm (inches)                  |  |

|----------------------------------------------------|--------------------------------------------------------------|------------------------------|------------------------------|--|

| Symbol                                             | Description                                                  | 8mm Tape                     | 12mm Tape                    |  |

| A <sub>0</sub><br>B <sub>0</sub><br>K <sub>0</sub> | Width of cavity<br>Length of cavity<br>Depth of cavity       | Dependent on chip siz        | e to minimize rotation       |  |

| W                                                  | Width of tape                                                | 8.0 (0.315)                  | 12.0 (0.472)                 |  |

| F                                                  | Distance between drive hole centres and cavity centres       | 3.5 (0.138)                  | 5.5 (0.213)                  |  |

| E                                                  | Distance between drive hole centres and tape edge            | 1.75 (0.069)                 |                              |  |

| P <sub>1</sub>                                     | Distance between cavity centres                              | 4.0 (0.156)                  | 8.0 (0.315)                  |  |

| P <sub>2</sub>                                     | Axial distance between drive hole centres and cavity centres | 2.0 (0                       | 0.079)                       |  |

| P <sub>0</sub>                                     | Axial distance between drive hole centres                    | 4.0 (0                       | 0.156)                       |  |

| Do                                                 | Drive hole diameter                                          | 1.5 (0.059)                  |                              |  |

| D <sub>1</sub>                                     | Diameter of cavity piercing                                  | 1.0 (0.039)                  | 1.5 (0.059)                  |  |

| Т                                                  | Carrier tape thickness                                       | $0.3 (0.012) \pm 0.1 (0.04)$ | $0.4 (0.016) \pm 0.1 (0.04)$ |  |

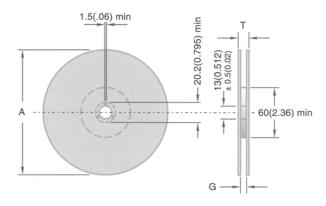

#### **Reel Dimensions**

| Symbol | Description           | 178mm<br>Reel      | 330mm<br>Reel      |

|--------|-----------------------|--------------------|--------------------|

| A      | Reel diameter         | 178<br>(7)         | 330<br>(13)        |

| G      | Reel inside width     | 8.4<br>(0.33)      | 12.4<br>(0.49)     |

| т      | Reel outside<br>width | 14.4<br>(0.56) max | 18.4<br>(0.72) max |

| +. | Ton tang thickness | 0.1(0.004) max  |

|----|--------------------|-----------------|

| L1 | Top tape thickness | 0.1 (0.004) max |

# Packing Information

#### Missing Components

The number of missing components in the tape may not exceed 0.25% of the total quantity with not more than three consecutive components missing. This must be followed by at least six properly placed components

#### Identification

Each reel is labelled with the following information: manufacturer, chip size, capacitance, tolerance, rated voltage, dielectric type, batch number, date code and quantity of components.

### Component Orientation

Tape and reeling is in accordance with IEC 60286 part 3, which defines the packaging specifications for leadless components on continuous tapes.

#### Notes: 1) IEC60286-3 states A0 < B0

Regarding the orientation of 1825 and 2225 components, the termination bands are right to left, NOT front to back. Please see diagram.

# Leader Trailer

Orientation of 1825 & 2225 components

# Outer Packaging

### Outer carton dimensions mm (inches) max

| Reel Size | No. of Reels | L       | W       | т      |  |

|-----------|--------------|---------|---------|--------|--|

| 178       | 1            | 185     | 185     | 25     |  |

| (7)       |              | (7.28)  | (7.28)  | (0.98) |  |

| 178       | 4            | 190     | 195     | 75     |  |

| (7)       |              | (7.48)  | (7.76)  | (2.95) |  |

| 330       | 1            | 335     | 335     | 25     |  |

| (13)      |              | (13.19) | (13.19) | (0.98) |  |

# Reeled quantities

| 178mm   | 0805 | 1206 | 1410 | 1812 | 330 m m    | 0805  | 1206  | 1410 | 1812 |

|---------|------|------|------|------|------------|-------|-------|------|------|

| 7" reel | 3000 | 2500 | 2000 | 1000 | (13") reel | 12000 | 10000 | 8000 | 4000 |

# Bulk Packing - Tubs

Chips are supplied in rigid re-sealable plastic tubs together with impact cushioning wadding. Tubs are labelled with the details: chip size, capacitance, tolerance, rated voltage, dielectric type, batch number, date code and quantity of components.

#### Dimensions mm (inches)

| Н | 60mm (2.36") |

|---|--------------|

| D | 50mm (1.97") |